Did you find this useful? Give us your feedback

![Figure 2.15 Detail view of source or drain junction of MOSFET [55].](/figures/figure-2-15-detail-view-of-source-or-drain-junction-of-3a7uwhk9.png)

15 citations

13 citations

11 citations

2 citations

2,744 citations

...1) Repeater Model: Rabaey’s approach [45] is adopted for the repeater model in 3D-DATE....

[...]

...For the energy calculation of the gate, 3D-DATE accounts for the consumed charge by adding the capacitance of every node since the dissipated energy is given by the equation [45]:...

[...]

1,693 citations

...By using Elmore delay approach [61], propagation delay of the interconnect is given as: tp ,c r i t =m (0....

[...]

[...]

1,486 citations

...3D-DATE adopts Horowitz wire model [43] for calculating resistance and capacitance of wire....

[...]

845 citations

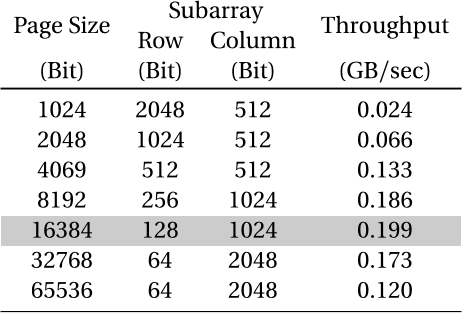

...1 [46] and described in Rambus model [10]....

[...]

...1 and Horowitz to analyze delay of bitline, sense amplifier, and write-back driver [46], [48]....

[...]

...Nine bit row address decoding path [10], [46]....

[...]

829 citations

There are several interesting directions in future research. It would also be interesting to extend DATE model for evaluating the finegrained 3D DRAM design by adding high-performance transistor roadmap. “ The future of wires ”. For the device roadmap, the authors believe it would be interesting to update current roadmap with emerging devices such as FinFET-based gate transistors or emerging materials for the wire, which would impact overall speed.