This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS–I: REGULAR PAPERS 1

40-nm CMOS Wideband High-IF Receiver Using

a Modified Charge-Sharing Bandpass

Filter to Boost Q-Factor

Filipe Dias Baumgratz , Student Member, IEEE, Sandro Binsfeld Ferreira, Member, IEEE,

Michiel S. J. Steyaert, Fellow, IEEE, Sergio Bampi, Senior Member, IEEE,

and Filip Tavernier, Member, IEEE

Abstract—A 40-nm CMOS wideband high-IF receiver is

presented in this paper. The low-noise transconductance ampli-

fier (LNTA) uses dual noise cancellation in order to improve its

noise figure. The LNTA has also a folded-cascode structure to

increase its output impedance and prepare for a current-mode

passive mixer. This structure is merged into the output stage of

the LNTA, so there is no need for extra transistors. Additionally,

a modified charge-sharing bandpass filter with cross-connected

transconductors to boost Q-factor is proposed and discussed. The

highest voltage gain achieved by the receiver (RX) is 30 dB. The

RX noise figure is 3.3 dB at the maximum gain, while the IIP3

is −2.5 dBm at 1 GHz. The area of the receiver is very competitive

for the wide band considered, merely 0.137 mm

2

.TheRXand

clock generation circuitry drain 25 mA from a 0.9-V supply.

Index Terms—Receiver, wideband, high-IF, super-heterodyne,

low noise transconductance amplifier, LNTA, switched-capacitor

filter, bandpass filter, current mixer, positive feedback, Q-factor,

image attenuation.

I. INTRODUCTION

N

EW wireless applications such as software defined

radios or cognitive radios are demanding multi-band

and multi-standard operation, increasing the requirements for

flexibility and integrability in the radios [1]. Typical solutions

adopt either zero intermediate frequency (IF) or low-IF in the

receiver (RX) architectures since they offer less or no concerns

about image rejection. In such architectures, the channel

selection is easily performed on-chip by a low-pass filter (LPF)

after the mixer [2] which also adjusts the channel bandwidth.

Despite these interesting characteristics, the zero-IF and

low-IF topologies are constrained by 1/ f noise, second-order

Manuscript received August 4, 2017; revised November 8, 2017 and

December 19, 2017; accepted January 8, 2018. This work was supported

in part by the Brazilian National Council for Scientific and Technological

Development (CNPq), in part by CAPES, and in part by FAPERGS. This

paper was recommended by Associate Editor M. Onabajo. (Corresponding

author: Filipe Dias Baumgratz.)

F. D. Baumgratz is with PGMicro, Federal University of Rio Grande do

Sul, Porto Alegre 90040-060, Brazil, and also with KU Leuven, 3000 Leuven,

Belgium (e-mail: fdbaumgratz@inf.ufrgs.br).

S. B. Ferreira is with Unisinos University, 93020-190 S˜ao Leopoldo, Brazil.

M. S. J. Steyaert and F. Tavernier are with KU Leuven, 3000 Leuven,

Belgium.

S. Bampi is with PGMicro, Informatics Institute, Federal University of Rio

Grande do Sul, Porto Alegre 90040-060, Brazil.

Color versions of one or more of the figures in this paper are available

online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2018.2792909

nonlinearity, and DC-offset. To achieve high-performance,

the receivers overcome these constraints by extensively using

calibration [3]–[5].

Super-heterodyne RX architectures are not affected by these

common issues due to their high IF [6]–[8]. Nevertheless, they

traditionally require external filters for image rejection and

channel selection. Thus, they have drawn less interest for many

years.

The N-path filter proposed in [6] is an evolution of the origi-

nal concept [9], [10], and it solves the super-heterodyne exter-

nal filter problem by implementing a bandpass filter (BPF)

using a passive switched-capacitor (SC) topology. The low-Q

filter is translated to the radio frequency (RF) input by

the mixer, solving the requirement for large external filters.

Following the introduction of this new approach, other passive

SC BPFs have been reported [11]–[16]. Those BPFs use only

switches and capacitors and are consequently more friendly

to process scaling due to the reduction of the switches ON

resistance. In fact, their performance should improve in smaller

CMOS nodes, and the scalability can be increased by using

MOS capacitors.

Switched-capacitors BPFs allow for the design of fully

integrated receivers with a high-IF [6], [13]–[17], avoiding the

shortcomings presented previously. Like the super-heterodyne

architecture, the high-IF works with IFs of tens or even

hundreds of megahertz. The image and blockers are filtered

along the receiver chain by BPFs in the RF-domain, as shown

in [6], and in the IF-domain, as shown in [6] and [13]–[16].

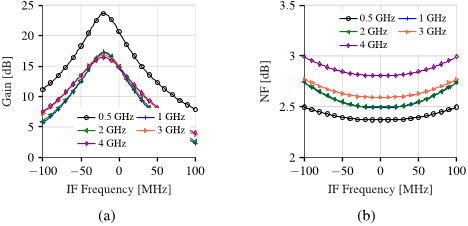

This paper presents a wideband high-IF receiver designed

in TSMC 40 nm CMOS, using SC BPFs to attenuate the

image and out-of-band interferers. The RX operates from

0.5 GHz to 4 GHz and two main architecture innova-

tions are introduced here. First, the low noise transconduc-

tance amplifier (LNTA) implements a clever utilization of a

folded-cascode structure, which not only increases the output

impedance of the LNTA but also reduces the number of

transistors. Second, a SC BPF, in which the Q-factor is boosted

by cross-connected transconductors at the input, is presented

and discussed. Moreover, since the mixer performs a single-

to-differential conversion, the LNTA input is single-ended and

there is no need for a chunky transformer at the input. This

results in a receiver showing high performance in a very wide

band, low power consumption, and small area.

1549-8328 © 2018 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See http://www.ieee.org/publications_standards/publications/rights/index.html for more information.

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

2 IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS–I: REGULAR PAPERS

Fig. 1. The proposed receiver chain chain with the clock generator modules.

This paper is organized as follows. Section II discusses the

receiver architecture. The circuits that compose the receiver

are presented in sections III - VI. Section VII shows the

measurement results. Finally, section VIII summarizes the

main achievements of this paper.

II. H

IGH-IF RECEIVER ARCHITECTURE

The receiver chain using a high-IF (HIF) architecture with

quadrature down-conversion is presented in Fig. 1. This topol-

ogy has been selected due to its low-noise and high-linearity.

Despite the passive blocks such as the mixer and the BPFs,

the noise remains low thanks to the high performance LNTA.

Moreover, the first BPF shapes the input impedance of the

mixer and attenuates the interferers.

As the first block in the receiver chain, the LNTA has the

primary task of mitigating the noise contribution from the

whole receiver chain. In addition, since the following block is a

current mode mixer, the LNTA must work as a transconductor,

having a large output impedance which maximizes the AC

current delivered to the mixer [18]. The LNTA has also

an additional linearity burden; since the following mixers

and filters are passive, i.e. highly linear but gain-less and

noisy, the LNTA must have a higher gain, which reduces its

linearity. In this design the supply voltage is limited to 0.9 V,

which limits the LNTA linearity even further. Consequently,

the LNTA becomes the linearity bottleneck of the receiver.

In [6] the LNTA is a self-biased inverter-based transconduc-

tor. Also, a large on-chip transformer to convert the input from

single-ended to differential has been used, which gives an extra

10 dB of voltage gain. Recently published LNTAs [14], [17]

use noise canceling techniques to improve noise figure. In [17]

a two-stage LNTA is presented; the first stage is a high linear

low noise amplifier since it works with a supply voltage higher

than the nominal (2 V), and the second stage does the voltage

to current conversion. In [14] the LNTA has only one stage

which reduces the power consumption, but requires a cascode

at the output to create a high output impedance which limits

the LNTA linearity due to the 0.9 V supply voltage. Both

circuits create the input match using a common-gate transistor

with their sources biased with external inductors. Our proposed

circuit uses a fully integrated single-ended LNTA, without

the need for external inductors or a chunky transformer.

The choice for a single-ended topology is further discussed

in section III.

One of the most interesting features of the passive mixer

is its transparency [19]. Combining the mixer with a BPF,

the impedance seen at the input of the mixer is shaped by

the BPF transfer function (TF). Therefore, interferers that

eventually arrive at the input have lower gain than the main

signal, increasing the linearity of the LNTA and, consequently,

of the receiver. Moreover, the passive mixer creates an anti-

aliasing filter when working as a sampler [18] and it performs

the single-ended to differential conversion easily, without

requiring additional circuitry.

The SC filters operate in the discrete-time (DT) domain.

Their advantages over the continuous-time (CT) filters were

extensively discussed in [6] and [13]. Overall, DT filters, such

as the N-path filters [6], [11], [20] and the charge-sharing (CS)

filters [13]–[16], are passive filters based on SC, being more

linear and less power hungry than CT filters. Although the

N-path filter has a higher Q-factor than the CS filter, its

transfer function has several replicas, while the CS filter

transfer function has only one peak between − f

s

/2and f

s

/2.

These replicas can reduce the blocker rejection or fold blockers

on top of the main signal. Hence, CS filters were chosen

for this design. Since the CS BPF has a low Q-factor [13],

the receiver needs two filter stages to attenuate the image

and the out-of-band interferers. The first filter is a first order

BPF which operates at the same sampling frequency ( f

s

)as

the mixer to properly cancel the aliasing. The second BPF,

on the other hand, does not need to use the same f

s

as the

mixer since the aliasing requirement was already met. Thus,

the clock of the second BPF is reduced, which then decimates

the input signal. In addition, the Q-factor of this BPF is

enhanced by increasing the order of the filter and by a circuit

improvement introduced in our proposed filter, as explained

ahead in section V-B.

The GM-cells shown in Fig. 1 are an intermediate stage

between the first and second filtering stages. These transcon-

ductors are needed to drive the passive second filtering stage

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

BAUMGRATZ et al.: 40-nm CMOS WIDEBAND HIGH-IF RX USING A MODIFIED CHARGE-SHARING BPF 3

Fig. 2. The proposed LNTA topology.

like the LNTA drives the passive mixer. Being the fourth

block in the chain, the GM-cells main restriction is linearity.

As depicted in the block diagram of Fig. 1, the receiver clock-

ing requires two non-overlapping clocks, two 25% duty-cycle

clocks and one 12.5% duty-cycle clock, with two different

circuits to generate them. Finally, the output buffers are simple

source-followers that isolate the circuit and provide a 50

output match to the measurement equipment.

III. LNTA

The output impedance is one of the most important non-

idealities of transconductors since it limits the AC current

delivered to the load and the effective V-to-I conversion (GM).

Therefore, the output impedance (Z

LNTA,out

)oftheLNTA

(Fig. 2) has to be higher than the input impedance of the

passive mixer (Z

MX,in

). The higher Z

LNTA,out

/Z

MX,in

ratio,

the better GM implementation.

The LNTA has two cascodes and one folded-cascode which

ensure a high output impedance. The cascodes also improve

the load isolation, so the input match and noise canceling

are immune to any load variation. The use of long channel

transistors for M2 and M3 would also increase the output

impedance without the need for cascodes, but it would harm

the input match at frequencies higher than 1 GHz since C

gs

increases proportionally to the gate length.

The folded-cascode that is created by connecting M6 to the

source of M5 is the best solution for the connection between

M6 and the output. Although M6 can be directly connected

to the output, it would reduce the output impedance.

The 50 input match is provided by M1. Since its

transconductance (g

m1

) is boosted by the local feedback

through M2, the LNTA input impedance is Z

LNTA,in

≈

1

/g

m1

(g

m2

/g

m4

+1),whereg

m2

and g

m4

are the transconductances

of M2 and M4, respectively. However, since the intrinsic gain

(g

m

/g

ds

) for a minimum length transistor in this technology is

about 5 V/V, g

ds1

cannot be neglected, and C

gs2,3

are also not

negligible at high frequencies. The input impedance including

those effects is given by

Z

LNTA,in

=

1

g

m1

(g

m2

/g

m4

+ 1)

1 + g

ds1

R

D1

+

g

ds1

1 + g

ds1

R

D1

+ s

C

gs2

+ C

gs3

,

(1)

Thus, Z

LNTA,in

is designed to be higher than 50 to

compensate for the parasitic impedances that appear in parallel

with Z

LNTA,in

and reduce its value.

The noise canceling technique cancels only the noise of the

transistor responsible for the input matching [21]–[23], which

is M1 in this design. Hence, the noise generated by the auxil-

iary amplifier, which is initially M2 in this design, remains a

full contributor to the overall noise figure, and it needs to be

reduced by traditional means, like increasing the g

m

.

In order to further reduce noise figure, the noise of M2 is

fed back to the input and amplified through a second auxiliary

amplifier. Thus, the noise of M2 is partially canceled as

explained further. The local feedback is created by connecting

the drain of M2 to the gate of M1 [24], [25], which also

boosts the g

m

of M1. The second auxiliary amplifier is

created by using current-reuse [26], which saves power. Hence,

M3 is added to the circuit. As a result, this LNTA topology

completely cancels the noise of M1 and partially cancels the

noise of M2, which are the major noise sources of the circuit.

After the noise cancellation, M3 and R

D1

are the dominant

noise sources of the LNTA. The noise contribution of M6 is

reduced by the gain g

m1

R

D1

and can thus be neglected.

The contribution of M1 and M2 to the noise factor are

represented as follows:

F

M1

≈ γ g

m1

R

S

g

m2

+ g

m3

− g

m6

G

m1

R

D1

g

m2

+ g

m3

+ g

m6

G

m1

R

D1

2

, (2)

and

F

M2

≈ γ g

m2

R

S

⎡

⎢

⎢

⎣

g

m1

1 + G

m1

+ G

m1

R

D1

g

m6

−

g

m3

g

m4

g

m2

+ g

m3

+ g

m6

G

m1

R

D1

⎤

⎥

⎥

⎦

2

.

(3)

G

m1

is g

m1

(g

m2

/g

m4

+ 1), γ is the noise coefficient, and R

s

is the signal source resistance, which is intended to be equal

to Z

LNTA,in

.

It can be deduced from (2) that the noise contribution

of M1 is zero if g

m2

+ g

m3

= g

m6

G

m1

R

D1

and from (3)

that the noise contribution of M2 is zero if 1 + G

m1

+

G

m1

R

D1

g

m6

=

g

m3

g

m4

. However, these conditions cannot be

achieved simultaneously. The best choice, therefore, is to fully

cancel the noise of M1 since it is the primary noise source and

only cancel the noise of M2 partially.

The proposed single-ended topology has two advantages

over its differential counterpart: a lower power consumption

and a larger GM while keeping the noise canceling con-

dition. The single-ended topology needs R

D1

andM6to

invert the polarity of both signal and noise. This additional

stage increases the degree of freedom of the design since

it decouples the values of g

m2

, g

m3

,andG

m1

.Inthe

differential version of this LNTA, the noise cancellation

condition would be g

m2

+ g

m3

= G

m1

since neither

M6 nor R

D1

are present. Hence, the values for g

m2

and g

m3

would be limited by G

m1

. The single-ended version, on the

other hand, does not have this limitation. Not being lim-

ited by G

m1

, g

m2

and g

m3

can be set to much higher

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

4 IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS–I: REGULAR PAPERS

TABLE I

LNTA S

IZING PARAMETERS

values which further reduce their noise and increase the

transconductance.

In the single-ended topology of this LNTA, the main prob-

lem is the linearity since both M6 and the cascode transistors

(M4 and M5) impose limits. The former increases the signal

distortion because M1 and R

D1

have already amplified the

signal. The latter reduces the linearity due to the four stacked

transistors within a supply voltage of 0.9 V. Furthermore,

the small V

DS

across those stacked transistors increases the

value of their distortion terms. In particular, the distortion of

M4 and M5 cannot be neglected [27].

Therefore, the gain of M6 is kept below one to minimize

distortion. The g

m

/I

D

of M1 and M2 have been selected in

such a way that their third-order distortion terms cancel each

other. The former is biased in strong inversion, and the latter in

moderate inversion [28]. Additionally, M4 and M5 are biased

like in [27] to achieve an optimal trade off between linearity

and noise.

The DC voltage at the output node is kept constant by the

DC-control block. In spite of any variation on the V

DS

of the

cascode, the DC output voltage remains constant at VDD/2,

which maintains these transistors in the selected operation

point.

Table I summarizes the sizing of the transistors, and Fig. 3

shows post-layout simulation results. The LNTA was simu-

lated using a 50 load that corresponds to the minimum

input impedance of the mixer. The simulated NF is below

2.3 dB within the entire band, and it has a minimum value

of 1.8 dB. The gain varies from 17 to 13.5 dB at 0.2 and

4 GHz respectively. Also, the input reflection coefficient (S11)

remains below −10 dB over the entire considered RF band.

Moreover, the LNTA has shown a small variation in corners

as presented in Fig. 3. The worst case NF remains below

3 dB at 125

◦

C which is the worst case corner for noise.

Meanwhile, the voltage gain drops only 2 dB in the SS corner.

Due to parasitic capacitances, the output impedance of the

LNTA reduces at higher frequencies. Consequently, the ratio

Z

LNTA,out

/Z

MX,in

is reduced, which hampers the driving of

the mixer, and compromises the overall RX gain.

IV. F

IRST FILTERING STAGE

The combination of a passive mixer and a charge-

sharing (CS) SC filter is beneficial since the mixer, if properly

designed, cancels the aliasing created by the SC architecture.

However, the aliasing cancellation happens only if the peaks

from the BPF filter are aligned with the nulls from the mixer;

thus their f

s

have to be equal or f

BPF

s

=

f

MX

s

2n

for n ∈ N

∗

,

i.e. using clock decimation for the BPF. The decimation is

avoided here since it would increase the noise figure due to

noise folding. As a result, the first BPF works at a high f

s

,

the same as the mixer, narrowing down the topology of choice

Fig. 3. LNTA simulation results for temperature corners 27

◦

, 125

◦

,and−40

◦

and process corners typical-typical (TT), fast-fast (FF), fast-slow (FS),

slow-fast (SF), and slow-slow (SS).

Fig. 4. Transfer Function of the mixer and BPF when f

s

= 4GHz.

to the 1st order BPF with 4 phases (BPF 4/4) [13], which

works well at high frequencies. Since the mixer has to match

the number of phases of the BPF, this design uses a 4-phase

passive mixer. Also, the 25 %-duty-cycle non-overlapping

clock drives the mixer, preventing I-Q crosstalk [18]. In addi-

tion, the mixer sampling frequency is four times the

LO frequency.

A. Mixer

The anti-aliasing filter is created only if the mixer, which

is presented in Fig 6, works as a sampler when its transfer

function is a sinc function [18],

H( f ) =

sin(π fT

s

)

π fT

s

, (4)

where T

s

is the sampling period and f the frequency in Hz.

Fig. 4 shows the TF of the anti-aliasing filter (dotted black

line). When combined with the BPF TF, the only remaining

peak is at the central frequency of the BPF while all the DT

replicas are attenuated.

A consequence of the mixer transparency is the

up-conversion of the baseband impedance, in this case an IF

impedance. Thus, its input impedance is a function not only

of the resistance of the switches, but also of the IF impedance,

which is a BPF filter in this design. According to [19],

the input impedance of a passive mixer is also affected by

the harmonics of the clock driving the switches. A resistor in

parallel with the IF impedance adds this effect to the electrical

model as can be seen in Fig. 5a. Moreover, the resistance

of only one switch has to be taken into consideration since

the switches are not closed at the same time due to the non-

overlapping clocks.

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination.

BAUMGRATZ et al.: 40-nm CMOS WIDEBAND HIGH-IF RX USING A MODIFIED CHARGE-SHARING BPF 5

Fig. 5. (a) The passive mixer electrical model [19]. (b) The variation of the

input impedance of the mixer with the LO frequency and (c) the value of C

R

programmed for each case. The comparison of the calculated and simulated

input impedance of the mixer at (d) 500 MHz and (e) 1 GHz.

Fig. 5a shows the electrical model proposed in [19], where

R

sw

is the resistance of the switches, R

sh

models the effect of

the clock harmonics on the input impedance, Z

IF

represents

the IF impedance, i.e. the BPF 4/4 input impedance, and ζ

is the impedance up-conversion constant. Hence, the input

impedance of the passive mixer is [19]

Z

MX,in

= R

sw

+ R

sh

||ζ Z

IF

, (5)

where ζ ≈ 0.203 and R

sh

≈ 4.3(R

LNTA,out

+ R

sw

) [19];

R

LNTA,out

is the real part of the output impedance of

the LNTA. Eq. (5) shows that Z

IF

and R

sh

have a considerable

effect on the input impedance of the mixer. Based on (5),

the input impedance of the mixer can be predicted as shown

in Fig. 5b. Since the input impedance of the BPF 4/4 decreases

with the LO frequency increase, the input impedance of the

mixer also drops, thereby reducing the overall gain. The

gain drop can be compensated by changing the value of the

capacitor C

R

(Fig. 5c) which controls the input impedance of

the BPF 4/4 and enable a flat gain response. The values pre-

dicted with (5) are reasonably accurate as observed in Fig. 5d

and Fig. 5e.

The mixer and BPF 4/4 will properly work as long as

Z

LNTA,out

Z

MX,in

, so that the Z

MX,in

is dominant.

As discussed in [18], the gain and the null depth of the

mixer are reduced if the previous condition is not fulfilled.

Henceforth, the aliasing cancellation, which is generated by

these nulls, will be limited.

There are two main reasons to reduce as much as pos-

sible Z

MX,in

: it increases the bandwidth of the LNTA, and

Z

MX,in

has to accommodate for any reduction on Z

LNTA,out

Fig. 6. Schematic of the passive mixer and the BPF 4/4.

that happens at high frequencies due to parasitic capacitances.

Otherwise, the mixer and the BPF 4/4 will not work properly at

these frequencies. Nevertheless, Z

MX,in

ends up being limited

by the CMOS technology since it is directly dependent on the

resistance of the mixer and BPF 4/4 switches.

The noise factor of the mixer and the BPF 4/4 can also be

calculated from the model in Fig. 5a and is given by

F

MX&BPF

= 1 +

v

2

n,sw

v

2

n,R

LNT A,out

+

v

2

n,sh

v

2

n,R

LNT A,out

R

LNTA,out

+ R

sw

R

sh

2

+

v

2

n,IF

v

2

n,R

LNT A,out

R

LNTA,out

+ R

sw

ζ Z

IF

2

(6)

where

v

2

n,sw

is the noise voltage of the mixer switches, v

2

n,sh

is the noise voltage of R

sh

,andv

2

n,IF

is the up-converted

noise from the IF stage, i.e. ζ

v

2

n,BPF4/4

. Eq. (6) shows

the BPF 4/4 as the main contributor to this noise factor.

Since increasing ζ Z

IF

affects the input impedance of the

mixer, the noise factor can only be effectively reduced by

reducing

v

2

n,IF

. In [19] the analysis has been done considering

the interface with a 50 antenna, which is not the case in

this design. Thus the model has to be adjusted to the LNTA

interface. For simplicity, hereafter, only the real part of the

output impedance of the LNTA will be considered.

B. First-Order Bandpass Filter

The main advantage of the BPF 4/4 is its high-frequency

operation; and, its main disadvantage is the low Q-factor

(ideally 0.5). The low Q-factor of the BPF 4/4 limits linearity

improvement on the LNTA. Fig. 6 shows the BPF 4/4, where

C

H

is the history capacitor, that stores the charge until

sampling and C

R

is the rotating capacitor, that shares the

charges with other branches.

The complex Z-domain transfer function of the

BPF 4/4 is [13]

H

4/4

(z) =

V

out

q

in

=

k

(1 − αz

−1

) − j (1 − α)z

−1

, (7)