Did you find this useful? Give us your feedback

18 citations

...3) Fixed-Point Performance: To improve performance in the signal-to-quantization-noise ratio (SQNR) with finite word length, we employed a block floating point (BFP) scheme [30], [28], [48] by representing a block of data values using the formula , in which M is the mantissa of the individual data value and E is a global exponent term for all data values....

[...]

...Moreover, rather than using a global operation scheme based on overall performance optimization [30]–[34], it is more helpful to minimize the power consumption (i....

[...]

...Based on the evaluation results presented in [30], [48], and [50], we determined that in fixed-point performance for OCT or OFDM FFTs, the proposed FFT structure lends directional support for SQNR for both FD-OCT and OFDM applications....

[...]

...For example, an eight-path radix-8 kernel may employ seven complex multipliers as shown in [27], [30], [31]....

[...]

...To enable a balanced comparison of hardware performance, we employed two parameters based on [22], [28], [30] and [51] in terms of “normalized N-point FFTs per energy” (N is the FFT length specified in our design) as shown in (14) and “normalized T....

[...]

16 citations

...Furthermore, the ping-pong cache memory architecture is proposed to further reduce memory accesses more efficiently [8]....

[...]

...For these reasons, several dynamic data scaling approaches have been proposed to preserve effective data word-length and avoiding data overflow [3], [8]....

[...]

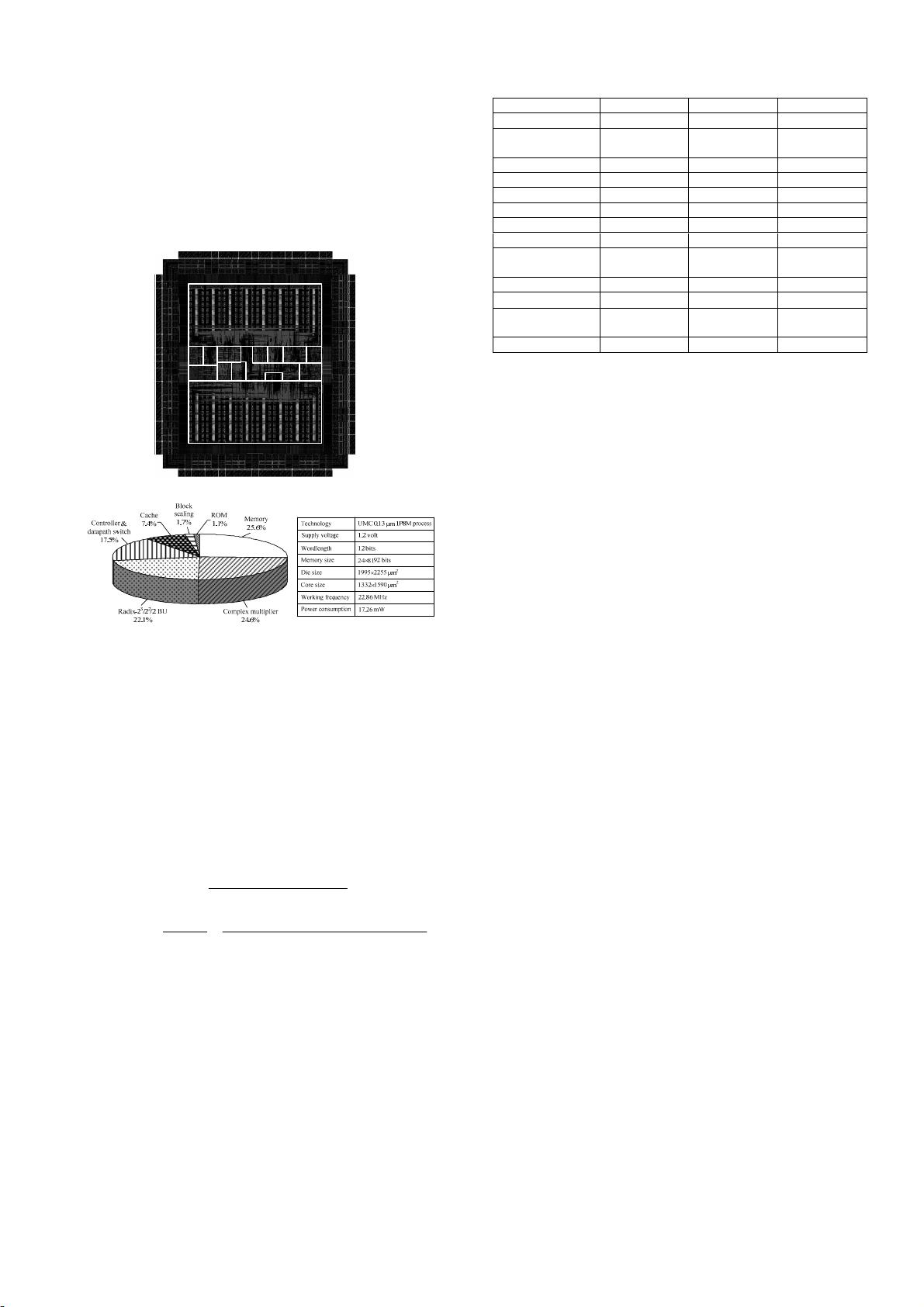

...Proposed Chen [8] Zhong [10] Technology 0....

[...]

...7 [8], respectively to be our baseline of performance comparison....

[...]

11 citations

...The performance indices for chip area and power consumption are defined as follows [1][3]:...

[...]

10 citations

10 citations

322 citations

...Thus we employ radix-23 and radix-22 [4] to replace radix-8 and radix-4, respectively....

[...]

...To reduce the number of complex multiplications, radix-8 algorithm is chosen to carry out the DFT [4]....

[...]

...Here we take the longest 2048-point DFT in the design as an example....

[...]

...reduce the number of complex multiplications, radix-8 algorithm is chosen to carry out the DFT [4]....

[...]

...Similarly, 128/256/ 512/1024-point DFT can also be decomposed to preceding 0-7803-9735-5/06/$20.00 ©2006 IEEE 203 radix-8 stages and a final radix-8/4/2 stage depending on the DFT size....

[...]

319 citations

...Thus by taking the guard interval of WiMAX systems into account, the proposed FFT/IFFT processor does not need to operate in a multiple sampling frequency as the previous cached-memory FFT designs do [2], [3]....

[...]

...However, the increase in wordlength [2] or idle cycles [3] still causes wastes in power consumption and hardware cost....

[...]

...Besides, to compare the FFT processor chips fabricated with different technologies, we adopt the normalized area and FFTs per energy [2] as our performance indices shown in eqs....

[...]

...Cached-memory FFT [2], [3] is proposed for low power consumption by reducing the memory accesses....

[...]

...There have been many researches on low-power FFT designs by employing the cached-memory architecture to reduce the memory accesses [2], [3]....

[...]

165 citations

...Besides, since FFT and IFFT have the same operations except for complexconjugated twiddle factors, we implement IFFT by simply taking conjugates ofFFT input/output [6] as shown in Fig....

[...]

128 citations

...For memory-based FFT processors supporting consecutive I/0, multiple main memories are needed as computation and I/0 buffers [7]....

[...]

...To reduce the total memory size, the continuous flow (CF) memory architecture is proposed [7] where only two N-word memories are required for N-point FFT....

[...]

111 citations

...Thus by taking the guard interval of WiMAX systems into account, the proposed FFT/IFFT processor does not need to operate in a multiple sampling frequency as the previous cached-memory FFT designs do [2], [3]....

[...]

...However, the increase in wordlength [2] or idle cycles [3] still causes wastes in power consumption and hardware cost....

[...]

...dynamck sloaing-FTprocessorP[3] is proposced bayempoyinguc mutiporleepnngts for icracighe-sz blocks....

[...]

...Cached-memory FFT [2], [3] is proposed for low power consumption by reducing the memory accesses....

[...]

...There have been many researches on low-power FFT designs by employing the cached-memory architecture to reduce the memory accesses [2], [3]....

[...]