Did you find this useful? Give us your feedback

7 citations

...[8] Y. Chen, Y.W. Lin and C.Y. Lee (2006), “A block scaling FFT/IFFT processor for WiMAX applications,” in Proc....

[...]

...The proposed technique is preferable for MIMO-OFDM baseband processor such as WiMAX [8] or LTE applications....

[...]

...[4] M. S. Patil, T. D. Chhatbar, and A. D. Darji, (2010), “An area efficient and low power implementation of 2048 point FFT/IFFT processor for mobile WiMAX,” in Proc....

[...]

...OFDM has been used in wide range of applications from wired communication modems, such as Digital subscriber line (xDSL) to wireless communication modems such as WiMAX, 3GPP, Long term evolution (LTE) to process baseband data....

[...]

...However, this results in more complex hardware as well as more cost, thus a bit-parallel complex constant multiplier [8] is used to reduce the cost and hardware complexity....

[...]

5 citations

4 citations

...Hence this can be called as Radix-2 algorithm [1]....

[...]

3 citations

2 citations

...[9] employs a smart structure for ROM-size reduction to produce twiddle factors as well as to compact the chip area....

[...]

...Dual-memory architecture has separate memory for butterfly inputs and butterfly outputs as opposed to one shared memory [9]....

[...]

322 citations

...Thus we employ radix-23 and radix-22 [4] to replace radix-8 and radix-4, respectively....

[...]

...To reduce the number of complex multiplications, radix-8 algorithm is chosen to carry out the DFT [4]....

[...]

...Here we take the longest 2048-point DFT in the design as an example....

[...]

...reduce the number of complex multiplications, radix-8 algorithm is chosen to carry out the DFT [4]....

[...]

...Similarly, 128/256/ 512/1024-point DFT can also be decomposed to preceding 0-7803-9735-5/06/$20.00 ©2006 IEEE 203 radix-8 stages and a final radix-8/4/2 stage depending on the DFT size....

[...]

319 citations

...Thus by taking the guard interval of WiMAX systems into account, the proposed FFT/IFFT processor does not need to operate in a multiple sampling frequency as the previous cached-memory FFT designs do [2], [3]....

[...]

...However, the increase in wordlength [2] or idle cycles [3] still causes wastes in power consumption and hardware cost....

[...]

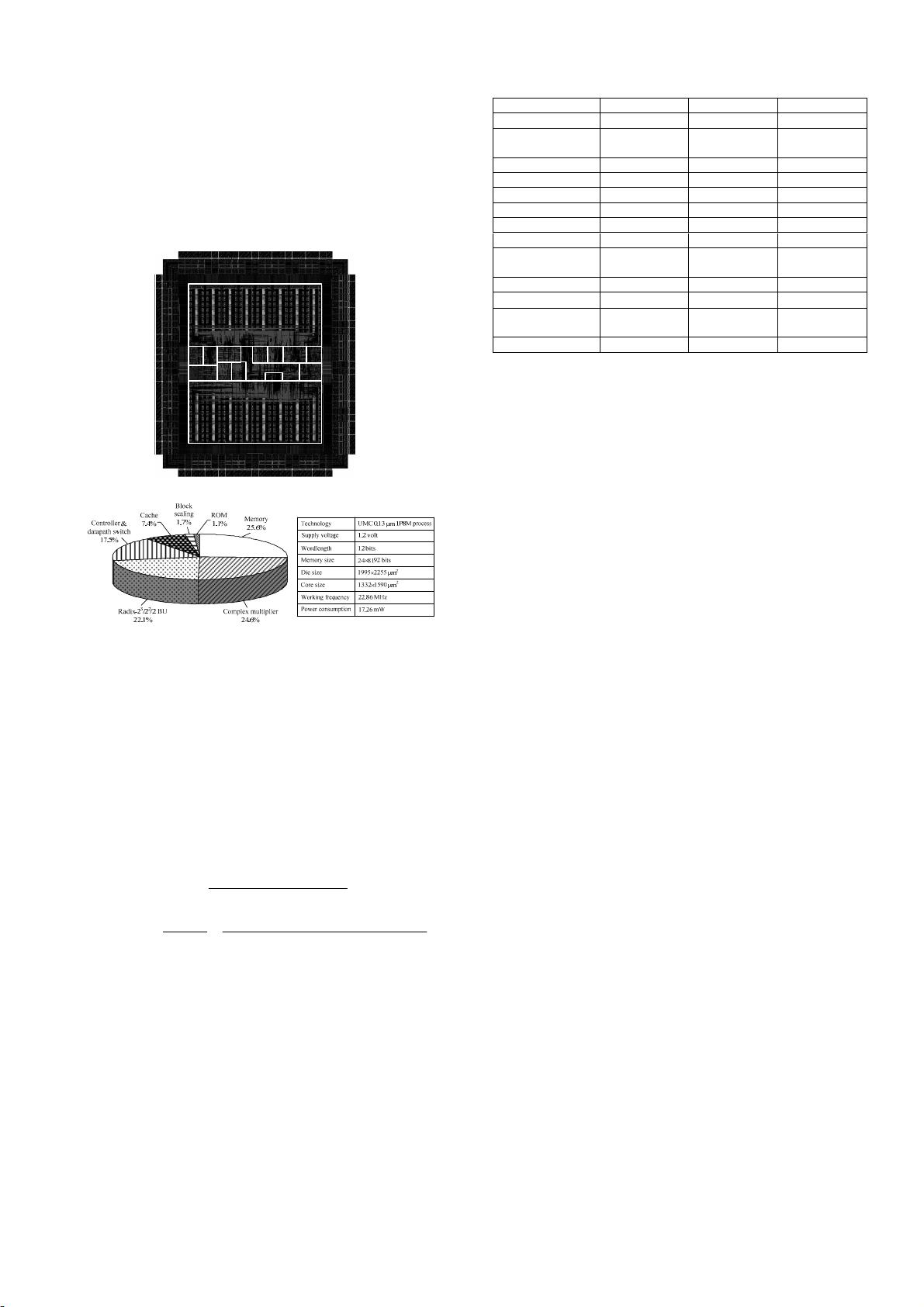

...Besides, to compare the FFT processor chips fabricated with different technologies, we adopt the normalized area and FFTs per energy [2] as our performance indices shown in eqs....

[...]

...Cached-memory FFT [2], [3] is proposed for low power consumption by reducing the memory accesses....

[...]

...There have been many researches on low-power FFT designs by employing the cached-memory architecture to reduce the memory accesses [2], [3]....

[...]

165 citations

...Besides, since FFT and IFFT have the same operations except for complexconjugated twiddle factors, we implement IFFT by simply taking conjugates ofFFT input/output [6] as shown in Fig....

[...]

128 citations

...For memory-based FFT processors supporting consecutive I/0, multiple main memories are needed as computation and I/0 buffers [7]....

[...]

...To reduce the total memory size, the continuous flow (CF) memory architecture is proposed [7] where only two N-word memories are required for N-point FFT....

[...]

111 citations

...Thus by taking the guard interval of WiMAX systems into account, the proposed FFT/IFFT processor does not need to operate in a multiple sampling frequency as the previous cached-memory FFT designs do [2], [3]....

[...]

...However, the increase in wordlength [2] or idle cycles [3] still causes wastes in power consumption and hardware cost....

[...]

...dynamck sloaing-FTprocessorP[3] is proposced bayempoyinguc mutiporleepnngts for icracighe-sz blocks....

[...]

...Cached-memory FFT [2], [3] is proposed for low power consumption by reducing the memory accesses....

[...]

...There have been many researches on low-power FFT designs by employing the cached-memory architecture to reduce the memory accesses [2], [3]....

[...]