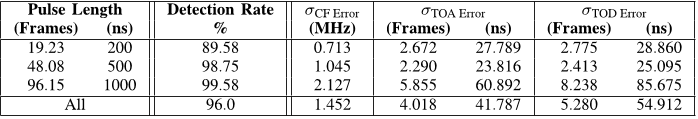

1

A Compressed Sensing Parameter Extraction

Platform for Radar Pulse Signal Acquisition

Juhwan Yoo, Christopher Turnes, Eric Nakamura, Chi Le, Stephen Becker, Emilio Sovero, Michael Wakin,

Michael Grant, Justin Romberg, Azita Emami-Neyestanak, and Emmanuel Cand

`

es

Abstract—In this paper we present a complete (hard-

ware/software) sub-Nyquist rate (×13) wideband signal acqui-

sition chain capable of acquiring radar pulse parameters in an

instantaneous bandwidth spanning 100 MHz–2.5 GHz with the

equivalent of 8 ENOB digitizing performance. The approach

is based on the alternative sensing-paradigm of Compressed-

Sensing (CS). The hardware platform features a fully-integrated

CS receiver architecture named the random-modulation pre-

integrator (RMPI) fabricated in Northrop Grumman’s 450 nm

InP HBT bipolar technology. The software back-end consists

of a novel CS parameter recovery algorithm which extracts

information about the signal without performing full time-

domain signal reconstruction. This approach significantly re-

duces the computational overhead involved in retrieving desired

information which demonstrates an avenue toward employing

CS techniques in power-constrained real-time applications. The

developed techniques are validated on CS samples physically

measured by the fabricated RMPI and measurement results are

presented. The parameter estimation algorithms are described

in detail and a complete description of the physical hardware

is given.

Index Terms—Compressed sensing, Indium-Phosphide, Pa-

rameter Estimation, Random-Modulation Pre-Integration

I. INTRODUCTION

A principal goal in the design of modern electronic systems

is to acquire large amounts of information quickly and with

little expenditure of resources. In the wireless technology

sector, the goal of maximizing information throughput is

illustrated by the strong interest in RF sensing and spectral

applications that require instantaneous bandwidths of many

GHz. Such systems have applications ranging from scientific

instrumentation to electronic intelligence. Although some

J. Yoo and A. Emami-Neyestanak are with the Department of Electrical

Engineering at the California Institute of Technology, Pasadena, CA, e-mail:

juhwan@caltech.edu

C. Turnes and J. Romberg are with the School of Electrical and

Computer Engineering at the Georgia Institute of Technology, Atlanta, GA,

e-mail: cturnes@gatech.edu

M. Wakin is with the Department of Electrical Engineering and

Computer Science, Colorado School of Mines, Golden, CO

S. Becker and M. Grant are with the Department of Applied and Com-

putational Mathematics at the California Institute of Technology, Pasadena,

CA; S. Becker is also with the Laboratoire Jacques-Louis Lions at Paris 6

University, Paris, France

C. Le, E. Nakamura, and E. Sovero are with the Northrop Grum-

man Corporation, Redondo Beach, CA, e-mail:eric.nakamura@ngc.com;

Emilio Sovero is now at Waveconnex Inc., Westlake Village, CA, e-mail:

emilio.sovero@waveconnex.com

E. Cand

`

es is with the Departments of Mathematics and Statistics at

Stanford University, Stanford, CA

solutions already exist, their large size, weight, and power

consumption make more efficient solutions desirable.

At present, realizing high bandwidth systems poses two

primary challenges. The first challenge comes from the

amount of power required to operate back-end ADCs at the

necessary digitization rate. This issue is so significant that

the remaining elements of the signal chain (RF front-end,

DSP core, etc.) are often chosen based upon an ADC that is

selected to be compatible with the available power budget [1].

The second challenge comes from need to store, compress,

and post-process the large volumes of data produced by such

systems. For example, a system that acquires samples at a

rate of 1 Gsps with 10 bits of resolution will fill 1 Gb of

memory in less than 1 s. In light of the ever growing demand

to capture higher bandwidths, it would seem that a solution

at the fundamental system level is needed to address these

challenges.

Some promise for addressing these challenges comes from

the theory of compressed sensing (CS) [2]–[6]. CS has

recently emerged as an alternative paradigm to the Shannon-

Nyquist sampling theorem, which at present is used implicitly

in the design of virtually all signal acquisition systems. In

short, the CS theory states that signals with high overall

bandwidth but comparatively low information level can be

acquired very efficiently using randomized measurement pro-

tocols. The requisite sampling rate is merely proportional to

the information level, and thus CS provides a framework for

sub-Nyquist rate signal acquisition. As we discuss further in

Sec. II, aliasing is avoided because of the random nature of

the measurement protocol.

The emergence of the CS theory is inspiring a fundamen-

tal re-conception of many physical signal acquisition and

processing platforms. The beginning of this renaissance has

already seen the re-design of cameras [7], medical imaging

devices [8], and RF transceivers [9]–[11]. However, the bene-

fits of CS are not without their costs. In particular, the task of

reconstructing Nyquist-rate samples from CS measurements

requires solving an inverse problem that cannot be addressed

with simple linear methods. Rather, a variety of nonlinear

algorithms have been proposed (see, e.g., [12]–[14]). While

the speed of these methods continues to improve, their

computational cost can still be appreciably greater than many

conventional algorithms for directly processing Nyquist-rate

samples. This matter of computation, if not addressed, poten-

tially limits the wide-spread application of CS architectures

“The views expressed are those of the author and do not reflect the official policy or position of the Department of Defense or the U.S. Government.”

This is in accordance with DoDI 5230.29, January 8, 2009.

Distribution Statement “A” (Approved for Public Release, Distribution Unlimited) [DISTAR case #18841]

in power constrained real-time applications.

In this paper we address these issues by presenting a

complete, novel signal acquisition platform (both hardware

and software) that is capable—in certain applications—of

estimating the desired signal parameters directly from CS

measurements [15]. In the spirit of compressive signal pro-

cessing [16], our approach takes the principal motivation of

CS one step further and aims to eliminate the overhead of first

reconstructing the Nyquist-rate signal samples before apply-

ing conventional DSP techniques for parameter extraction.

On the hardware side, we present a fully integrated

wideband CS receiver called the random-modulation pre-

integrator (RMPI) [9,10,12,17]. We fabricate this device with

Northrop Grumman’s 450 nm InP HBT bipolar process. On

the software side, we focus on signal environments consisting

of radar pulses and present a novel algorithm for extracting

radar pulse parameters—carrier frequency (CF), phase θ

0

,

amplitude A

0

, time-of-arrival (TOA), and time-of-departure

(TOD)—directly from CS measurements. (The exact signal

model is described in Sec. IV.)

Our complete system is capable of recovering radar

pulse parameters within an effective instantaneous bandwidth

(EIBW) spanning 100 MHz—2.5 GHz with a digitizing per-

formance of 8 ENOB. We validate the system by feeding the

fabricated RMPI with radar pulses and using the physically

digitized CS measurements to recover the parameters of

interest.

An outline of this paper is as follows: Sec. II provides

a brief background on CS and a description of the high-

level operation of the RMPI, Sec. III provides a complete

description of the hardware platform used to encode the CS

samples, Sec. IV provides details of the parameter estimation

algorithms, and Sec. V presents measurement results.

II. THE RMPI

A. Compressed Sensing

CS at its heart relies on two concepts: sparsity and

incoherence [5]. Sparsity captures the idea that many high-

dimensional signals can be represented using a relatively

small set of coefficients when expressed in a properly chosen

basis. Incoherence captures the idea of dissimilarity between

any two representations; two bases are said to be incoherent if

any signal having a sparse expansion in one of them must be

dense in the other. An example of an incoherent pair comes

from the classical time-frequency duality. A sparse signal

time—e.g., a Dirac-delta function—has a dense spectrum.

Similarly, a single tone is sparse in the Fourier domain but

dense in time.

The key observation underlying CS is that when a signal

is sparse in some basis, it can be acquired by taking a

small number of measurements that are incoherent with

its sparse basis [18]. Often this incoherence is achieved

RevisedHardwareDescription

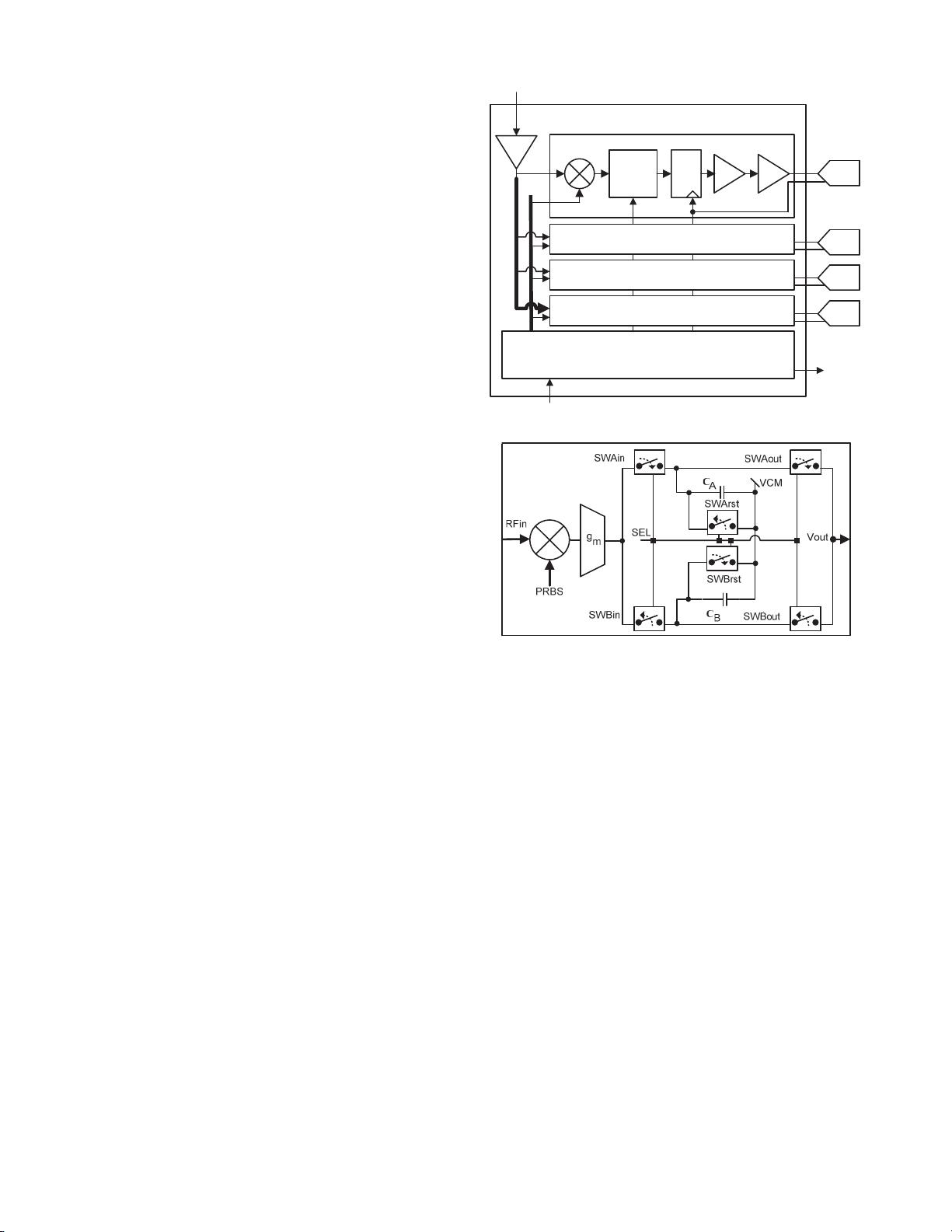

A. ArchitectureandOperation

The RMPI presented in this work was realized with the proprietary Northrop Grumman (NG) 450nm InP HBT bipolar process [25].

The process features a 4-layer metal stack with an fT and fmax > 300GHz. Fig. 1a shows the block diagram of the IC containing the

input buffer driving the common node of the four RD channels, and the timing generator. The timing generator is responsible for

generating the pseudo-random bit sequences (PRBS) and clocking waveforms to coordinate the track-and-hold and integration

operations. All analog and digital signal paths are implemented differentially to improve common-mode noise rejection and increase

linearity of the system. The analog path up to the integrator was designed for a 2.5 GHz bandwidth. After the integrator the signal

bandwidth is reduced and the circuits are design to meet settling requirements. A 5 GHz master clock reference (CLKin) is used to

clock the PRBS generators and sets the 2.5 GHz unambiguous RF bandwidth. The track-and-holds (T/H) operate at 1/52 the master

clock frequency or roughly 96 MHz and a switch capacitor integrator is used so that one capacitor can be reset while the second is

integrating the mixer output. Finally, an output buffer is designed to the drive the ADC with the correct swing and common-mode

voltage. The chip was designed for a full-scale input amplitude of 0.5V p-p differential and 1V p-p differential at the output.

(a) SystemBlockDiagram

(b) RDChannelBlockDiagram

Fig. 1: (a) Simplified block diagram of 4-channel RMPI. The analog-signal path of each RD channel is identical; however the

timing signals they receive in operation are different. (b) Functional diagram of the mixer and integrator circuit.

InP RMPI 4 Channel Sampler

CLKin

PRBS1-4

CLK1-4SEL1-4

SYNC

T/H

RD 4

RD 3

RD 2

RD 1

Ibuf

SW Cap

Integrator

Sel

COTS

ADC

COTS

ADC

COTS

ADC

COTS

ADC

Obuf

RFin

Gain

PN/Timing Generator

(a) System Block Diagram

RevisedHardwareDescription

A. ArchitectureandOperation

The RMPI presented in this work was realized with the proprietary Northrop Grumman (NG) 450nm InP HBT bipolar process [25].

The process features a 4-layer metal stack with an fT and fmax > 300GHz. Fig. 1a shows the block diagram of the IC containing the

input buffer driving the common node of the four RD channels, and the timing generator. The timing generator is responsible for

generating the pseudo-random bit sequences (PRBS) and clocking waveforms to coordinate the track-and-hold and integration

operations. All analog and digital signal paths are implemented differentially to improve common-mode noise rejection and increase

linearity of the system. The analog path up to the integrator was designed for a 2.5 GHz bandwidth. After the integrator the signal

bandwidth is reduced and the circuits are design to meet settling requirements. A 5 GHz master clock reference (CLKin) is used to

clock the PRBS generators and sets the 2.5 GHz unambiguous RF bandwidth. The track-and-holds (T/H) operate at 1/52 the master

clock frequency or roughly 96 MHz and a switch capacitor integrator is used so that one capacitor can be reset while the second is

integrating the mixer output. Finally, an output buffer is designed to the drive the ADC with the correct swing and common-mode

voltage. The chip was designed for a full-scale input amplitude of 0.5V p-p differential and 1V p-p differential at the output.

(a) SystemBlockDiagram

(b) RDChannelBlockDiagram

Fig. 1: (a) Simplified block diagram of 4-channel RMPI. The analog-signal path of each RD channel is identical; however the

timing signals they receive in operation are different. (b) Functional diagram of the mixer and integrator circuit.

InP RMPI 4 Channel Sampler

CLKin

PRBS1-4

CLK1-4SEL1-4

SYNC

T/H

RD 4

RD 3

RD 2

RD 1

Ibuf

SW Cap

Integrator

Sel

COTS

ADC

COTS

ADC

COTS

ADC

COTS

ADC

Obuf

RFin

Gain

PN/Timing Generator

(b) RD Channel Block Diagram

Fig. 1: (a) Simplified block diagram of 4-channel RMPI. The analog-signal

path of each RD channel is identical, however the timing signals they receive

in operation are different. (b) Functional diagram of the mixer and integrator

circuits.

by incorporating randomness into the measurement process.

There are many possibilities for implementing incoherent

random measurements; a convenient and admissible choice

for hardware implementation is to correlate the input signal

(in our case, a time-windowed version of the input signal)

with a pseudo-random binary sequence (PRBS) [4]. We

refer the reader to [5] and references therein for additional

information about the mathematical theory of CS.

B. A Brief History and Description of the RMPI

Almost simultaneously with the introduction of CS [2],

a number of CS-based signal-acquisition architectures were

proposed. Some of the more well-known proposals include:

the Random Demodulator (RD) [17,19,20], the Random-

Modulation Pre-Integrator (RMPI) [9,10,21], the Non-

Uniform Sampler (NUS) [4,22], Random Convolution [23],

the Modulated Wideband Converter (MWC) [24], and many

others [25]—for a comprehensive overview see [12]. The

basic function that all of these systems implement is to cor-

2

Distribution Statement “A” (Approved for Public Release, Distribution Unlimited) [DISTAR case #18841]

relate of the input signal x(t) with an incoherent, randomly

generated set of “basis” elements over a fixed time window.

The RMPI is one of the most direct physical implemen-

tations of the CS concept; it is composed of a parallel set

of RDs driven by a common input. (See Fig. 1a, which is

described more fully in Sec. III.) Each RD is driven by

a distinct PRBS p(t); it uses this PRBS to modulate the

incoming signal x(t), integrates the result over a time interval

of length T

int

, and then digitizes the output at a rate f

ADC

=

1/T

int

f

nyq

. In our RMPI, T

int

= 52 · T

nyq

with f

nyq

=

1/T

nyq

= 5 GHz. Thus f

ADC

= 1/(52 · T

nyq

) = 96.154 MHz;

the aggregate back-end sampling rate f

s

= 384.616 Msps,

which corresponds to undersampling the Nyquist rate by a

factor of 13. Aliasing is avoided in this measurement scheme

because (i) the modulation with the PRBS will spread the

spectrum of any tone (including high-frequency ones) across

the entire band so that one can effectively subsample, and

(ii) the input signal is again assumed to obey some model

(aside from merely being bandlimited).

Letting x denote a time-windowed vector of Nyquist-rate

samples of the input signal x(t), we can implicitly model

the RMPI measurement process as multiplication of x by a

matrix Φ having 13× fewer rows than columns. Each row of

this matrix corresponds to a portion of the PRBS sequence

used in a specific integration window from a specific channel.

As an example, if we consider a sample vector x of length

N = 1040, the matrix Φ will be block-diagonal, with each

block having 4 rows (representing the parallel operation of

the 4 channels) and T

int

/T

Nyq

= 52 columns (representing

an integration window of 52 Nyquist bins). The rows of

each block contain ±1 entries, and the overall matrix will

be composed of NT

Nyq

/T

int

= 20 blocks (one for each

integration window). Denoting the vector of measurements as

y, the RMPI mode of acquisition can be modeled as y = Φx

where Φ ∈ R

80×1040

.

We point out that high-fidelity recovery/extraction of in-

formation from CS measurements requires precise knowledge

of the system transfer function Φ. Thus, practical deviations

from the block-diagonal ±1 model described above must be

taken into account. For the measurements presented in this

paper, we construct a model of our system’s Φ matrix by

feeding in sinusoidal tones and using the output measure-

ments to characterize the system’s impulse response.

III. HARDWARE IMPLEMENTATION DESCRIPTION

A. Architecture and Operation

The RMPI presented in this work was realized with the

proprietary Northrop Grumman (NG) 450 nm InP HBT

bipolar process [26]. The process features a 4-layer metal

stack with an f

T

and f

max

> 300 GHz. Fig. 1a shows the

block diagram of the IC containing the input buffer driving

the common node of the four RD channels and the timing

generator. The timing generator is responsible for generating

the pseudo-random bit sequences (PRBS) and the clocking

waveforms to coordinate the track-and-hold (T/H) and inte-

gration operations. All analog and digital signal paths are

implemented differentially to improve common-mode noise

rejection and increase linearity of the system. The analog path

up to the integrator was designed for a 2.5 GHz bandwidth.

The ensuing integration reduces the bandwidth containing

significant energy content. The circuits following the inte-

grator are designed to meet the settling requirements of the

reduced bandwidth. A 5 GHz master clock reference (CLKin)

is used to toggle the PRBS generators and is chosen to be

the Nyquist-rate of the input bandwidth [12,17]. The T/H

operate at 1/52 the master clock frequency (= 96.154 MHz).

A switched-capacitor interleaving integrator [27] is used so

that one capacitor can be reset while the second integrates the

mixer output. Finally, an output buffer is designed to drive the

ADC with the correct swing and common-mode voltage. The

chip was designed for a full-scale input amplitude of 0.5 V

pp

differential and 1 V

pp

differential output. In operation, the

RMPI circuit takes the analog input signal, buffers it, and

distributes the buffered signal to each of the 4 channels. In

each channel, the signal is multiplied by one of 4 orthogonal

PRBS—each of which is a 3276 bit long Gold code [28]. The

resulting product is integrated by one of two sets of inter-

leaved capacitors for exactly one frame (52 CLKin cycles).

At the end of the integration period the signal is sampled and

then held for 26 CLKin cycles to allow the external ADC

to digitize the signal for post-processing. Immediately after

the signal is sampled, the capacitor begins discharging and

the second capacitor begins integrating the next frame (see

Fig. 1b). The interleaved integration capacitors are used to

avoid missing frames due to the reset operation. Additionally,

the sampling instants for each channel are staggered to create

more diversity in the windowed integrations obtained.

B. Analog Signal Path

The input buffer is a differential pair with emitter degen-

eration and 50 Ω termination at each single-ended input. It

has a gain of 3 dB, a 2.5 GHz bandwidth, 70 dB SFDR,

and a full-scale differential input amplitude of 0.5 V

pp

. The

random modulation is performed by a standard differential

Gilbert mixer with the PRBS generator driving the top pair

and the analog input driving the bottom differential pair.

Emitter degeneration is used on the bottom differential pair

to improve linearity. To reduce noise, the mixer was designed

to have about 20 dB gain to offset the attenuation from

the integrator. The output of the mixer is integrated using

interleaved switched capacitors as shown in Fig. 1b and Fig. 2

and has a 12.5 MHz pole frequency. Input and output select

switches are closed to route the mixer output current to the

integration capacitor as well as to read out the capacitors

with the T/H circuit. When the reset switch is on, the

integration capacitor voltage is reset to zero. At the end of

each integration cycle (one frame = 10.4 ns), the output of

3

Distribution Statement “A” (Approved for Public Release, Distribution Unlimited) [DISTAR case #18841]

the integrator is sampled by the T/H and held for 5.2 ns. This

ensures that the external ADC has enough time to digitize

the held voltage.

The T/H was implemented using the switched emitter

follower topology with gain ≈ 1. To minimize the hold-

mode feed-through, small feed-forward capacitors were in-

serted [29]. The switched emitter follower was chosen in

favor over the more conventional diode bridge switch for

its smaller footprint and comparatively low parasitic capaci-

tance. The amplifier after the T/H has a gain of 2. In addition

to emitter degeneration, diode connected transistors are used

in the output load to cancel the input differential pair V

be

modulation and improve linearity. The output driver was

designed to be DC-coupled to the external ADC and have

70 dB SFDR and a 1 V

pp

swing. In order to save power,

200 Ω on-chip termination resistors were used on each side

to exploit the relatively long settling time.

In operation, the RMPI circuit takes the analog input signal, buffers it, and distributes the buffered signal to each of the 4 channels. In

each channel, the signal is multiplied by one of 4 orthogonal PRBS–each of which is a 3276 bit long Gold code. The resulting product

is integrated by one of two sets of interleaved capacitors for exactly one frame (52 CLKin cycles). At the end of the integration period

the signal is sampled and then held for 26 CLKin cycles to allow the external ADC to digitize the signal for post-processing.

Immediately after the signal is sampled, the capacitor begins discharging and the second capacitor begins integrating the next frame

(see Fig. 1b.) The interleaved integration capacitors are used to avoid missing frames due to the reset operation. Additionally, the

sampling instants for each channel are staggered to create more diversity in the windowed integrations obtained.

B. AnalogSignalPath

The input buffer is a differential pair with emitter degeneration and 50 ohms termination at each single ended input. It has a gain of

3dB, a 2.5GHz bandwidth, 70dB SFDR and can handle a 0.5V p-p differential input. The random modulation is performed by a

standard Gilbert mixer with the PRBS on the top pair and the analog input on the bottom differential pair. Emitter degeneration is

used on the bottom differential pair to improve linearity. To reduce noise, the mixer was designed to have about 20dB gain to offset

the attenuation from the integrator. The output of the mixer is integrated using interleaved switched capacitors as shown in Fig. 1b

and Fig.2 and has a 12.5 MHz pole frequency. Input and output select switches are closed to route the mixer current to the integration

capacitor and to connect it to the track-and-hold circuit. When the reset switch is on, the integration capacitor voltage is reset to zero.

At the end of each integration cycle (one frame or 10.4 ns), the output of the integrator is sampled by the T/H and held at for 5.2 ns.

This ensures that the external ADC has enough time to acquire the data accurately.

The T/H was implemented using the switched emitter follower topology with a gain of approximately 1. To minimize the hold-mode

feed-through, small feed-forward capacitors were inserted [26]. The switch emitter follower was chosen in favor over the more

conventional diode bridge switch for its smaller footprint and comparatively low parasitic capacitance. The amplifier after the T/H

has a gain of 2. In addition to emitter degeneration, diode connected transistors are used in the output load to cancel the input

differential pair Vbe modulation and improve the linearity. The output driver was designed to be DC-coupled to the external ADC

and have 70dB SFDR and a 1V-p-p swing. 200 Ohm on-chip terminations for each side was used to save power by taking advantage

of the relatively long settling time.

Fig. 2: Simplified schematic of the interleaved switch capacitor integrator. The diodes act as switches to configure capacitors for

integration or reset it based on the level of the control signal (SEL). When SEL is high, integrator A is resetting and integrator B is

integrating. When SEL+ is low, integrator B is resetting and integrator A is integrating.

C. PRBSandTimingGenerator

A master clock is applied to CLKin, from which all required timing signals are generated. The input clock buffer was biased with a

relatively high power to reduce jitter and it has 4 separate output emitter followers to limit cross-talk. Each emitter follower provides

a low jitter signal to re-clock the PRBS input before it is mixed with the RF input in each channel.

The PRBS signals are generated with two 6-bit PRBS shift-registers. One PRBS generator (PN6A in Fig. 3) is programmed to cycle

every 52 CLKin cycles while the second (PN6B) is allowed to cycle through all 63 states. The 2 PRBS generator outputs are

combined to generate 4 orthogonal 3276 bit long Gold code sequences. PN6A is also used to generate the T/H clocks (divide by 52)

and select signal (divide by 104) for the switched capacitor integrator. Both PN generators also output a sync pulse used to

synchronize the system. The output pulse from PN6B is re-clocked with the pulse form PN6A to produce a sync pulse that is 52

CLKin cycles long once every 3276 cycles. The synchronization pulse is essential to provide precise knowledge of the chipping

sequence used in each integration window which is necessary for signal-recovery and parameter estimation.

CLKin and the RF input are located on opposite sides of the chip to minimize coupling. Special attention was paid to the routing of

the PRBS, T/H clocks, and select signals to minimize clock/data coupling among the four channels. A simplified block diagram of the

PRBS/timing generator is shown in Fig.3. The timing generator block was designed to operate upto 5GHz and it consumes roughly

2.8W.

DArst+

DArst-

DAin+

DAin-

DAout+

DAout-

DBrst+

DBrst-

DBout+

DBout-

DBin+

DBin-

VCM

Fig. 2: Simplified schematic of interleaved switched capacitor integrator.

The diodes act as switches to configure capacitors for integration or reset it

based on the level of the control signal (SEL). When SEL is high, integrator

A is resetting and integrator B is integrating. When SEL+ is low, integrator

B is resetting and integrator A is integrating.

C. PRBS & Timing Generator

A master clock is applied to CLKin, from which all

required timing signals are generated. The input clock buffer

was biased with a relatively high power to reduce jitter. In

addition, it has 4 separate output emitter followers to mitigate

the deleterious effects of cross-talk on the clock jitter. Each

emitter follower provides a low jitter signal to re-clock the

PRBS input before it is mixed with the RF input in each

channel.

The PRBS signals are generated with two 6 bit PRBS gen-

erating linear-feedback shift-registers (LFSR(s)) [30]. One

PRBS generator (PN6A in Fig. 3) is programmed to cycle

every 52 CLKin cycles while the second (PN6B in Fig. 3)

is allowed to cycle through all 63 states. The 2 PRBS

generator outputs are combined to generate 4 orthogonal

52 × 63 = 3276 bit long Gold code sequences. PN6A is

also used to generate the T/H clocks (divide by 52) and

select signal (divide by 104) for the switched capacitor

integrator. Both PN generators also output a sync pulse used

to synchronize the system. The output pulse from PN6B is

re-clocked with the pulse from PN6A to produce a sync

pulse that is 52 CLKin cycles long once every 3276 cycles.

The synchronization pulse is essential to provide precise

knowledge of the chipping sequence used in each integration

window. This relative alignment information is crucial for

signal-recovery and parameter estimation.

CLKin and the RF input are located on opposite sides of

the chip to minimize coupling. Special attention was paid

to the routing of the PRBS, T/H clocks, and select signals

to minimize clock/data coupling among the four channels.

A simplified block diagram of the PRBS/timing generator is

shown in Fig. 3. The timing generator block was designed to

operate at speeds in excess of 5 GHz and consumes 2.8 W

when operated at the designed rate.

Fig. 3: Simplified block diagram of PRBS/timing generator. Shown are (4) quadrature clocks for the T/H and (4) select signals for

the interleaved capacitors.

D. PerformanceAnalysis

The only change is instead of Fig. 6 for the die photo, it’s Fig. 4

Added References

[26] P. Vorenkamp and J. Verdaasdonk, “Fully Bipolar, 120-Msample/s 10-b Track-and-Hold Circuit,” IEE Journal of Solid-State

Circuits, Vol. 27, No. 7, July 1992.

Fig. 3: Simplified block diagram of PRBS/timing generator. Shown are (4)

quadrature clocks for the S/H and (4) control signals for the interleaved

capacitors. Combinational logic is used to prevent the illegal start up

condition of the PN generators and to generate divide by 52 and divide

by 104 used as control signals in the S/H and in the interleaved integrators

respectively.

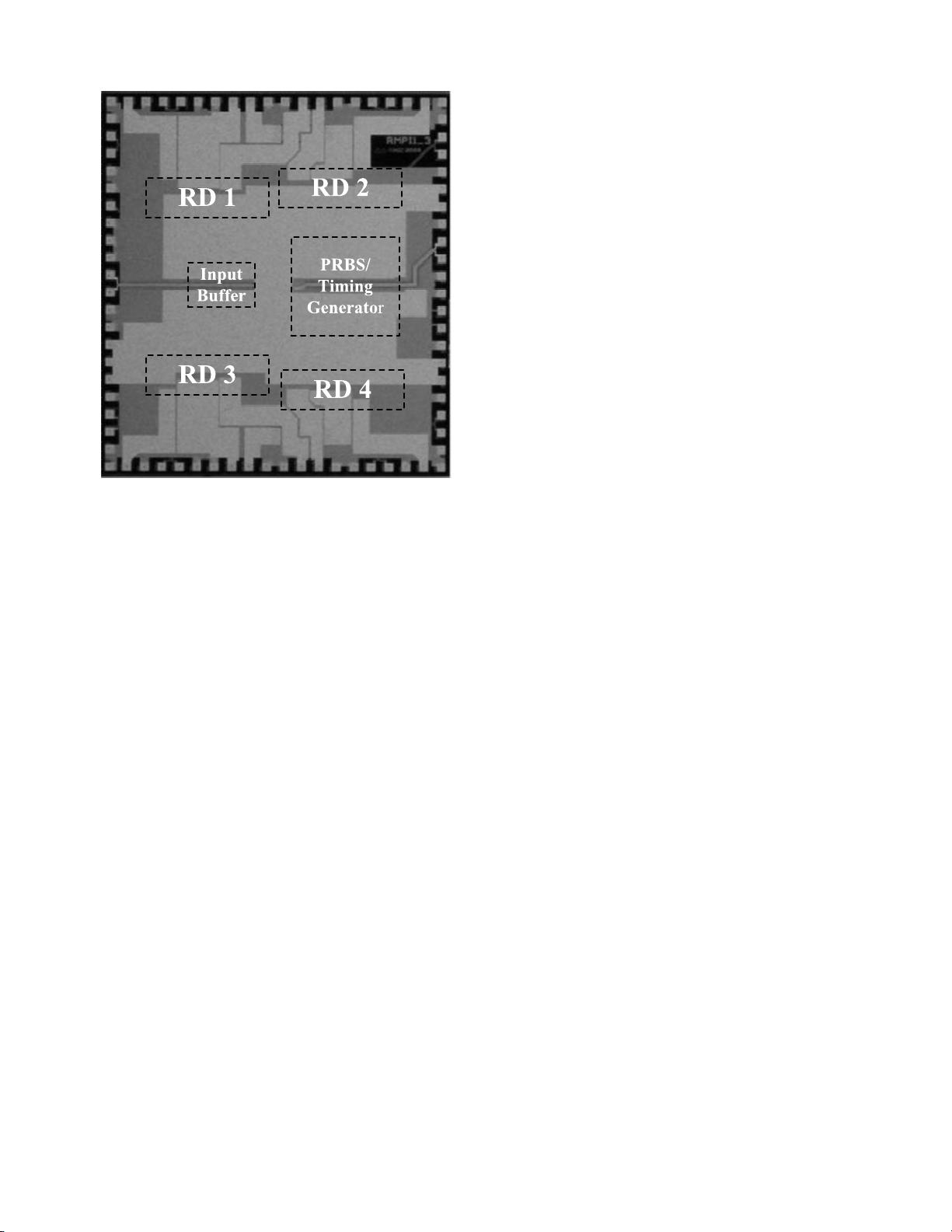

D. Performance Analysis

Simulation validation was done by performing transient-

based two-tone inter-modulation distortion simulations in the

Cadence design environment. Noise simulations were per-

formed using the periodic steady-state (PSS) mode of spectre.

The RMPI sampling system, including the off-chip ADCs

consumed 6.1 W of power. We point out that this system

was designed as a proof-of-concept and was not optimized

for power. Thus, caution should be used when comparing

the CS system in this work to conventional counterparts.

For example, the use of an InP process in this work leads

to power penalties compared to the CMOS RMPI (which

consumes ≈ 0.5 W) reported in [9,10], which is also similarly

unoptimized, due to the availability of static logic. A die

photo of the fabricated chip is shown in Fig. 4.

4

Distribution Statement “A” (Approved for Public Release, Distribution Unlimited) [DISTAR case #18841]

.

Fig. 4: RMPI IC die photo. Die size is 4.0 mm ×4.4 mm.

IV. PULSE-DESCRIPTOR WORD (PDW) EXTRACTION

Having described the acquisition system, we now present

algorithms for detecting radar pulses and estimating their pa-

rameters, referred to as pulse-descriptor words (PDW), from

randomly modulated pre-integrated (RMPI) samples. The

detection process is based on familiar principles employed

by detectors that operate on Nyquist samples. Our algorithms

use a combination of template matching, energy thresholding,

and consistency estimation to determine the presence of

pulses. By using all three of these methods, we gain robust

detection at the cost of a number of tunable parameters that

must be set to appropriate levels depending on the application

and sensing equipment. The general procedure consists of

three steps: first, we estimate the carrier frequency and energy

of a potential pulse segment at various time shifts; second,

based on consistency in frequency estimates and large enough

pulse energies, we apply criteria to determine if a pulse is

present; finally, for detected pulses we use our parameter

estimation methods to refine our carrier frequency, amplitude,

phase, time-of-arrival, and time-of-departure estimates.

The remainder of the section elaborates on the procedure

and is arranged as follows. First, we describe our methods

of parametric estimation, focusing in particular on carrier

frequency estimation. After describing how we can reliably

estimate the carrier frequency of a signal from compressive

measurements, we then explain how we use such estima-

tions to form a detection algorithm that jointly uses energy

detection and consistency of our frequency measurements.

We then describe how we perform parametric estimation on

compressive samples while simultaneously removing a band

in which a known interfering signal is present. Finally, we

combine the detection algorithm we have formulated with

the cancellation technique to present an algorithm capable of

detecting multiple overlapping pulses.

A. General Parametric Estimation

Our general parameter estimation problem can be stated

as follows. We consider signals x

0

(t) drawn from one of a

collection of (low-dimensional) subspaces {S

α

} indexed by

a parameter set α = (α

1

, α

2

, . . . , α

K

). Given the measure-

ments y = Φ[x

0

]+noise, we search for the set of parameters

corresponding to the subspace which contains a signal which

comes closest to explaining the measurements y. We solve

ˆα = arg min

α

min

x∈S

α

ky − Φ[x]k

2

2

. (IV.1)

The inner optimization finds the signal in S

α

that is most

consistent with the measurements for a fixed α; the outer

optimization compares these best fits for different α.

The inner optimization program, which is the classical

“closest point in a subspace” problem, has a well-known

closed form solution as it is easily formulated as a least-

squares problem.

Let u

α,1

(t), u

α,2

(t), . . . , u

α,d

(t) be a basis for the space

S

α

, meaning that

x

0

(t) ∈ S

α

⇒ x

0

(t) = a

1

u

α,1

(t) + a

2

u

α,2

(t) + · · · + a

p

u

α,d

(t),

for some unique a

1

, a

2

, . . . , a

d

∈ R. If we define V

α

to be the

M ×d matrix containing the inner products between each pair

of RMPI test functions φ

m

(t) and basis functions u

α,i

(t),

V

α

=

hφ

1

, u

α,1

i hφ

1

, u

α,2

i · · · hφ

1

, u

α,d

i

hφ

2

, u

α,1

i hφ

2

, u

α,2

i · · · hφ

2

, u

α,d

i

.

.

.

.

.

. · · ·

.

.

.

hφ

M

, u

α,1

i hφ

1

, u

α,2

i · · · hφ

M

, u

α,d

i

(IV.2)

then we can re-write (IV.1) as

ˆα = arg min

α

ky − V

α

(V

T

α

V

α

)

−1

V

T

α

yk

2

2

= arg min

α

k(I − P

α

)yk

2

2

, (IV.3)

where P

α

= V

α

(V

T

α

V

α

)

−1

V

T

α

is the orthogonal projector

onto the column space of V

α

. It is worth mentioning that

when the measurement noise consists of independent and

identically distributed Gaussian random variables, the result

ˆα in (IV.3) is the maximum likelihood estimate (MLE). When

the noise is correlated, we may instead pose the optimization

in terms of a weighted least squares problem.

In Sec. IV-B and Sec. IV-C below, we will discuss the

particular cases of frequency estimation for an unknown tone,

and time-of-arrival estimation for a square pulse modulated

to a known frequency. In both of these cases, we are trying

to estimate one parameter and the underlying subspaces S

α

have dimension d = 2. Moreover, the functional k(I−P

α

)yk

2

2

5

Distribution Statement “A” (Approved for Public Release, Distribution Unlimited) [DISTAR case #18841]