Did you find this useful? Give us your feedback

![Fig. 4. Feedforward-compensated opamp in [5].](/figures/fig-4-feedforward-compensated-opamp-in-5-20vn9jhu.png)

1 citations

...8 and compared to the performances of recently published CMOS filters [106, 116, 118, 119]....

[...]

...This Work [106] [118] [116] [119] [112] [120] [109] TCAS’14 TCASI’11 E-Lett....

[...]

1 citations

...In [13] and [14], amplifiers with new frequency compensation schemes have been proposed to achieve higher GBW with lower power consumptions....

[...]

1 citations

...The research[3] indicates that Feedforward-compensated amplifier has less power dissipation than Miller-compensated op-amps for the same design targets....

[...]

1 citations

4,826 citations

135 citations

...The FOM of the filters in [2] and [11] are lower, but these filters have a much broader transition band....

[...]

128 citations

...The FOM of the filters in [2] and [11] are lower, but these filters have a much broader transition band....

[...]

127 citations

...11 [wireless local-area network (WLAN)] has twice the signal bandwidth in the “n” mode as in the “a, b, and g” modes [4]....

[...]

126 citations

The replica integrator is initially reset, and an internally generated reference voltage Vref (approximately 400 mV) is applied to it for a period of 100 ns.

With nominal resistor and capacitor values, the replica integrator’s time constant 1/ω0 is 100 ns when the digital bits are set to midcode.

Because multiple inputs are summed, the loop gain tends to be lower, and the distortion tends to be higher than in an amplifier with a single input.

By determining the transfer function of the filter path and the buffer pathfor both positive and negative settings of the buffer gain, the external feedthrough can be cancelled, and the transfer function of the filter can be accurately measured [9].

A 5-bit control word b〈4 : 0〉 switches the resistors and the capacitors and varies the RC product from 55% to 175% of the midcode value to compensate for process variations.

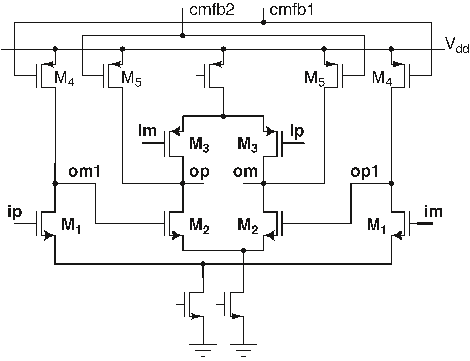

5. Separate common-mode feedback circuit (CMFB) stages are used to drive current sources M4 and M5 and to stabilize the common-mode output of each stage.

Its transconductance, which depends on Rgm and the transconductance of Ma, is adjusted to be equal to a3/R in the nominal process corner.

Power-efficient feedforward-compensated opamps in the integrators and feedforward current injection in the summing amplifier enable filters with an inherently high IIP3.

After five cycles of successive approximation, the bits converge to a value that sets the time constant of the replica integrator to 100 ns.

In the small number of characterized samples, the 3-dB bandwidth after automatic tuning is 16.3–16.6 MHz in the high-bandwidth mode and 7.5–8.4

In their implementation [see Fig. 7(c)], only a3x3/R, which is the largest component of the output current, is injected to the output using a transconductor.

Doubling the feedback capacitor array, as shown in Fig. 1(b), halves the bandwidth to 8.5 MHz while maintaining the same passbandnoise spectral density as required in WLAN receivers.