Abstract— Multilevel converters have become very

attractive for high voltage-level power conversion in

renewable power generation applications. The converter

topology is an important issue in the studies of multilevel

converter. Many multilevel topologies have been developed,

but few of them are qualified with capacitor voltage

self-balancing capability. This paper proposes a novel

diode-clamped modular multilevel converter (DCMMC)

with simplified capacitor voltage balancing control. In this

topology, low power rating diodes are used to clamp the

capacitor voltages of the converter. Only the top

sub-module in each arm of the converter requires capacitor

voltage control. Consequently, very few voltage sensors are

needed for voltage control and the control computation

burden is reduced greatly when the quantity of the

sub-modules is high. A simple voltage balancing control

method with carrier phase-shifted (CPS) modulation

strategy is developed for this topology. Experiments based

on a laboratory prototype were carried out and the results

validated the capacitor balancing performance of the

proposed topology.

Index Terms— Multilevel converters, diode-clamped modular

multilevel converter, capacitor voltage balancing.

I. INTRODUCTION

IGH voltage-level power conversion and transmission

have become very popular for wind power and

photovoltaic power generation, since the power scale of a wind

farm or a photovoltaic power station is becoming larger and

larger, even over hundreds of MWs. And high-voltage AC/DC

or DC/AC converters are the basic elements in such

applications. With low total harmonic distortion (THD) and

low voltage stress on power switches the multilevel converter is

a good choice for these applications.

Since 1980, multilevel converters have been developed

extensively [1]-[6]. The most famous multilevel converter

topologies are the neutral-point clamped (NPC), the

flying-capacitor (FC) and the cascaded multilevel converters. It

is easy to achieve a three- or five-level converter using the NPC

or FC topology. However, numerous clamping diodes and

capacitors are required when the voltage levels are high.

Furthermore, the capacitor voltage balancing control is difficult

and complicated [7]-[10].

With superior modularity and the least component

requirement among various multilevel topologies, the cascaded

H-bridge (CHB) multilevel converter seems to be the most

Manuscript received ******, ******This work is supported by ******.

suitable for medium-voltage active power conversion [11]-[16].

The voltage of the cells is maintained by isolated dc voltage

source, which can be supplied by wind turbine generator,

photovoltaic-cell, or windings of a multiwinding transformer,

etc. However, the requirement of isolated dc voltage supplies

and energy storage systems is the shortcoming in some

applications. When the CHB converter is applied in reactive

power conversion, e.g., STATCOM [17]-[20], the floating

capacitor voltage balancing control becomes the most

challenging issue.

Over the last decade the modular multilevel converter

(MMC) topology as another kind of cascaded topology has

gained growing attentions and found itself very attractive for

medium/high-voltage applications [21]-[24]. Its modularity and

scalability enable it to meet any voltage level requirement

[25]-[27]. However, like the CHB topology, the capacitor

voltage imbalance distributed in sub-modules (SMs) still

remains. Many researchers concentrate on developing control

and modulation strategies to solve the problem [27]-[39]. The

most widely accepted voltage balancing strategy is based on a

sorting method [27]. Li proposed an improved modulation

method to balance the capacitor voltages [28]. The control

systems rely on voltage sensors installed in all the SMs. In

addition, extra switching actions [29] [30] or high execution

frequency of voltage sorting algorithms [31] [32] are usually

involved, and the situation will deteriorate when the number of

SMs is high [33].

In 2001, Peng proposed a generalized multilevel converter

[38], which can balance each capacitor voltage automatically

without any additional circuits when applied in active or

reactive power conversion. From this generalized multilevel

converter topology, several other multilevel topologies can be

derived including the diode-clamped, capacitor-clamped,

cascaded H-bridge, Marx and modular multilevel topologies

[39]. However, the quantity of components in the general

multilevel converter is too high, which limits its applications in

high voltage-level conversion. The Marx multilevel converter

was proposed by Rodriguez and Leeb in [40], which can also

realize voltage self-balancing at the price of extra active power

switches compared with the MMC.

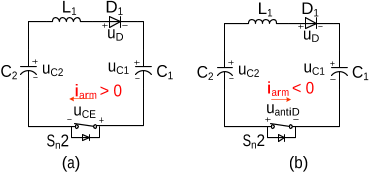

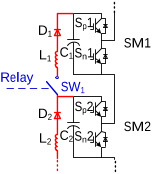

Based on the Marx and modular multilevel converters, this

paper proposes a new type of multilevel topology in order to

achieve a simplified capacitor voltage balancing method with

modularity and good harmonic performance. In this topology, a

low current rating diode and an inductor are used to replace the

balancing switch installed in each cell of the Marx multilevel

topology. We refer this new topology as the diode-clamped

MMC (DCM2C). In this topology the number of voltage