Did you find this useful? Give us your feedback

![Fig. 20. Extracted average FA (with standard deviation indicated) versus Ad. The surface adhesion energy per unit dimple area (Γ/Ad) is extracted from the surface force [11]. Each data point is obtained from measurements for more than ten relays with different L values.](/figures/fig-20-extracted-average-fa-with-standard-deviation-289j3tya.png)

![Fig. 21. Simulated energy-performance comparison for a 30-stage fan-out-4 inverter chain versus a relay chain (average transition probability=0.01, r=1, and total fixed capacitance Cfix,tot) [9]. Cfix,tot = 120 fF corresponds to an average fixed capacitance per relay CL of 0.5 fF. The MOSFET parameters are taken from the ITRS, for the 65-nm LSTP technology node. The inverter chain is optimized by gate sizing and supply and threshold voltage adjustment [23]– [28]. The relay parameters are summarized in Table III. The minimum energy (indicated as stars in the figure) is set by the surface adhesion energy Γ. Notice that, due to low gate capacitance, relay performance is more sensitive to fixed capacitance than MOSFET performance [9].](/figures/fig-21-simulated-energy-performance-comparison-for-a-30-bz12rg3b.png)

147 citations

63 citations

57 citations

...66g [6], which sets the optimum g for a given gd ....

[...]

...This energy is derived in [6] as follows:...

[...]

...Using optimized pass-gate circuit architectures, however, can mitigate the high Us for a scaled nanorelay [5], [6]....

[...]

...The relay minimizes Us when operated in its pull-in mode [6]; VPI can be estimated as follows:...

[...]

...Researchers have successfully fabricated operational electrostatic relays at the microscale [2]–[4], as well as relaybased circuits [5], [6]....

[...]

46 citations

46 citations

3,839 citations

3,008 citations

1,722 citations

1,215 citations

M. A. Horowitz, E. Alon, D. Patil, S. Naffziger, R. Kumar, and K. Bernstein, “ Scaling, power, and the future of CMOS, ” in IEDM Tech. In 1992, she joined the Xerox Palo Alto Research Center, Palo Alto, CA, as a Member of the research staff, where she worked on the research and development of polycrystalline-silicon thin-film transistor technologies for high-performance flat-panel displays.

Much like transistor scaling, relay miniaturization leads to dramatic improvements in density (for lower cost perfunction), switching delay (for higher performance), and energy efficiency.

For a given contact dimple gap thickness, the optimal dimple-gap thickness to actuation-gap thickness ratio is roughly 0.7, meaning that pull-in operation is preferred for energy-efficient relay design.

Using ANSYS, γf and γt are found to be 3.66 and14T relays have been demonstrated using conventional surface micromachining processes [10].

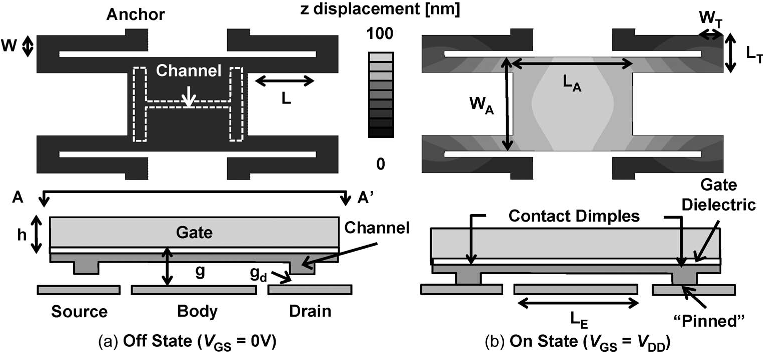

The gate electrode is supported by four suspended beams (with an effective spring constant keff ) anchored to the substrate at four corners.

In fact, the International Technology Roadmap for Semiconductors (ITRS) [40] predicts that the gate capacitance will only decrease by ∼2.5× as the transistor physical gate length is scaled from 38 to 7.4 nm.

This means that relay designs with lower beam stiffness, smaller contact dimple gap thickness, and therefore lower actuation area and supply voltage are feasible if a smaller contact dimple area is utilized.

the quality factor of nanometer-scale logic relays will be dominated by surface-related energy-loss mechanisms, due to their relatively large surface-to-volume ratio.

due to increasing variability, the minimum device width has been scaling relatively slowly and leading to minimal reduction in CMOS.

(28)Assuming ideal MOSFET scaling and constant operating temperature, Vddopt,MOS remains relatively constant, and hence, the minimum energy of CMOS scales linearly by the factor S. Based on Fig. 21, the physical gate length would need to be scaled down by approximately 20 times (i.e., to below 5 nm) to match the minimum energy potentially achievable with relays.

As derived in [6] and [32], the optimum supply voltage is proportional to the thermal voltageVddopt,MOS ∝ n × kBT/q (27)where n ≈ 1.2 is the subthreshold factor [6], [32].

From (23), for a low-Q relay with κ ≈ −0.34 and Vnorm ≈ 1.17−1.29, the optimal Cnorm ranges from 0.74 to 0.13; for a high-Q relay with κ ≈ −0.4 and Vnorm ≈ 1.17−1.29, the optimal Cnorm ranges from 0.97 to 0.27.7

FA can be extracted from the measurementsof Vpi and Vrl for devices of various beam lengths, according to the following equation [derived from (1)]:V 2rl = 27 4 gd g( 1 − gdg)2 V 2pi −2(g − gd)2 εoA FA. (3)FA is extracted to be 0.45 μN on average for TiO2-coated tungsten electrodes with a contact dimple area (Ad) of 2 × 10 μm2, as shown in Fig.

Vrl =√ 2(keffgd − FA)(g − gd)2εoA (1)where keff is the effective spring constant of the movable structure and A is the actuation area (≈ LA × WA, ignoring release etch holes).

As discussed in [39], due to this effect, the optimal supplyvoltage of a 32-bit adder increases from ∼0.25 to ∼0.33 V from the 65- to 32-nm technology nodes.

As will be derived in the following section, the energy efficiency of a relay is optimized by operating it in pull-in mode, i.e., designing it such that gd > g/3.

In contrast, for scaled logic relays with actuation gaps approaching 10 nm, i.e., less than the mean free path of an air molecule, squeeze-film damping will be negligible.

The voltage applied between the movable gate electrode and the fixed body electrode determines whether current can flow between the source and drain electrodes.