All figures (15)

Figure 9. Video processing architecture template.

Figure 8. Radio processing architecture template.

Figure 11. Complex QRD architectures.

Table 1. Useful language features for effective C/C++based design and synthesis.

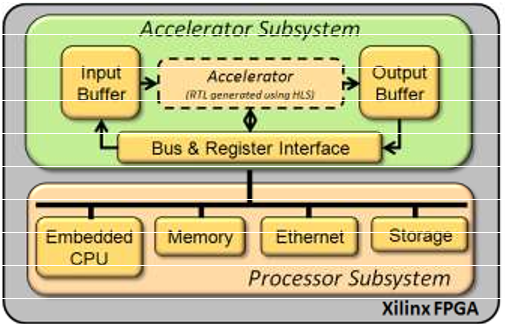

Figure 7. Block diagram showing an algorithmic block integrated with a processor and I/O.

Table 5. 8x8 RVD-QRD implementation results.

Figure 4. An example of memory partitioning and scheduling for throughput optimization.

Figure 5. HLS simulation and verification framework.

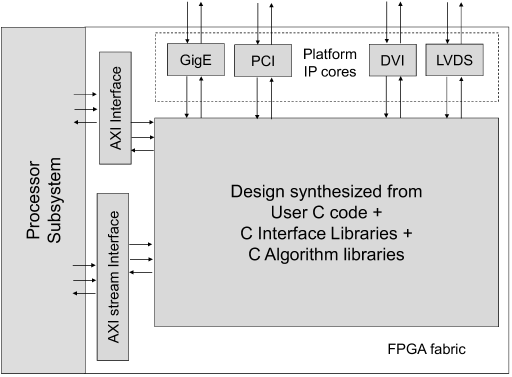

Figure 6. Automatic RTL test bench generation and connection in AutoPilot.

Figure 10. Architecture of the sphere decoder application. ![Table 3. Quality of results for DQPSK receiver workload: 18.75 MSamples/second input data at 75MHz clock speed. (Table reproduced from [101])](/figures/table-3-quality-of-results-for-dqpsk-receiver-workload-18-75-3kjt0f4e.png)

Table 3. Quality of results for DQPSK receiver workload: 18.75 MSamples/second input data at 75MHz clock speed. (Table reproduced from [101]) ![Table 2. Quality of results for BDTI optical flow workflow operating point 2: maximum throughput, 1280x720 progressive scan. (Table reproduced from [101])](/figures/table-2-quality-of-results-for-bdti-optical-flow-workflow-junqf16w.png)

Table 2. Quality of results for BDTI optical flow workflow operating point 2: maximum throughput, 1280x720 progressive scan. (Table reproduced from [101])

Figure 3. The Xilinx DSP48E block.

Figure 2. The structure of a scheduler using both hard constraints and soft constraints.

Figure 1. AutoESL and Xilinx C-to-FPGA design flow.