Did you find this useful? Give us your feedback

![Fig. 12. Equivalent thermal resistance diagram for a DPAK package mounted on a PCB. The thermal resistance of the thin solder between the package and the PCB is small and therefore is neglected [45].](/figures/fig-12-equivalent-thermal-resistance-diagram-for-a-dpak-7mddnsl0.png)

![TABLE I THERMAL CONDUCTIVITIES OF MATERIALS AT 25 OC [33]-[36]](/figures/table-i-thermal-conductivities-of-materials-at-25-oc-33-36-19kwd05l.png)

![Fig. 25. Comparison of the junction and top-case temperatures between measurements and calculations when (a) 0.5-W and (b) 1-W power losses are generated inside the diode. (c) Comparison of the board-ambient thermal resistances obtained from the measurements, the existing model [14], [31] and the proposed model.](/figures/fig-25-comparison-of-the-junction-and-top-case-temperatures-2hzing92.png)

![Fig. 16. (a) DPAK package structure; (b) Simplified package outline dimensions of diode VS-6EWL06FN-M3 [49].](/figures/fig-16-a-dpak-package-structure-b-simplified-package-outline-qofixaa8.png)

29 citations

14 citations

12 citations

...The copper layers serve as a heat spreader for better heat transfer [23] and they are also used in effective magnetic field cancellation routing to reduce the parasitics of the converter....

[...]

12 citations

9 citations

951 citations

...32 is a constant for horizontal plates [38]....

[...]

...59 is a constant for vertical plates [38]....

[...]

...The natural convection heat transfer coefficient for laminar flow of air at atmospheric pressure, hconv, and the radiation heat transfer coefficient hradi are [38] ⎧ ⎪⎪⎪⎨ ⎪⎪⎪⎩ hconv = λ[(Tx − Ta)/Lc] hradi = εσ[(Tx + 273) 2 + (Ta + 273) (2)] ×[(Tx + 273) + (Ta + 273)]...

[...]

...5 m [38], which is almost always the case in electronic systems....

[...]

...Then, we can obtain the convective heat transfer coefficients of the two top surfaces [38], i....

[...]

769 citations

..., GaN transistors) is continuingly shrinking in order to achieve higher power densities, lower parasitic inductances, and lower power losses [1]–[3]....

[...]

689 citations

...In addition, suitable heat dissipation measures should be considered as early as in the design and development phase, because subsequent modifications are generally more costly and involve increased engineering effort [9], [10]....

[...]

531 citations

251 citations

...However, thermal management has been identified as the main barrier for further power density increase [4]....

[...]

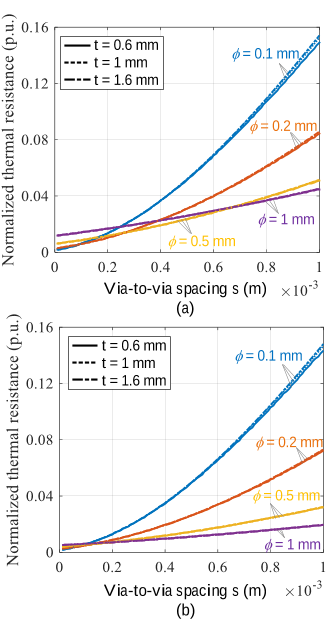

3. As can be seen, the parameters NCu, tCu and t, have a negligible impact on the normalized thermal resistance, implying that the copper and FR4 layers have a much higher thermal resistance compared to the vias.

Since there is a uniform heat source on the inner via array, and a powerful heatsink beneath the PCB, the radialdirection heat transfer of the inner-zone via array is not pronounced compared with the vertical direction.

4. When the vias are not filled, the optimal via diameter is about 0.25 mm; if = 0.8 mm is chosen, then there will be a 44% increase in the thermal resistance.

it is observed from (8) that both the radial and vertical outer-zone thermal resistances are functions of j, implying the two types of thermal resistances vary with respect to the outer via layer number.

Due to the phenomena of radial heat conduction and vertical heat convection in the PCB thermal system shown in Fig. 9(a), it is much easier to analyze the thermal resistance in the cylindrical coordinates.

When the steady state of the thermal system is reached, the temperature does notchange with time , and thus, (14) can be simplified as22d 1 d 0 dd T T P r r kr (15)The PCB is cooled by means of natural convection andradiation.

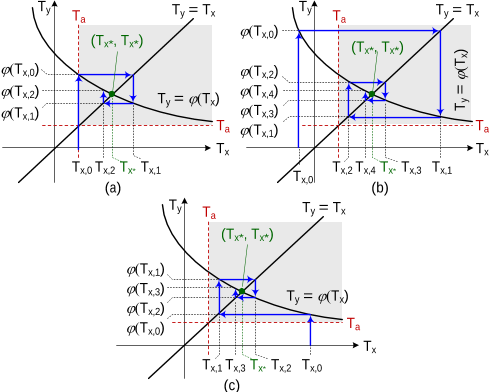

A fixed-point iteration based algorithm taking into account all the five thermal resistances shown in Fig. 12 is developed to design the copper pad size, as shown in Fig. 14.

When the vias are filled up with high-thermal-conductivity solder, then the via array with = 0.8 mm has the minimum thermal resistance.

a simplification method consisting of various steps of network transformations is proposed to derive the equivalent thermal resistance of Fig. 5(c), as illustrated in Fig.

With the same area for the via array, the thermal resistanceof Pattern II is about √3/2 = 86.6% of that in Pattern I. From (6), the authors can also obtain the optimal via diameter for both patterns, which can achieve the minimum thermal resistance, i.e.,2 ( 2 )( ) , Patterns The author& II2 ( ) PTH PTH

The existing analytical thermal resistance model for PCB pads overestimates the junction temperatures ofSMDs, whereas the proposed model enables a more accurate junction temperature prediction.

Compared to the reference design provided in [15], the thermal resistance can be reduced up to 62%, i.e., from 2.63 K/W (seeFig. 18(a)) based on [15] to 0.98 K/W with the proposed optimal design trajectory (Pattern II, = 0.8 mm, solder filling, see Fig. 18(b)).