# 2.4GHz Highly-Selective IoT Receiver Front-End with Power Optimized LNTA, Frequency Divider and Baseband Analog FIR Filter

Bart J. Thijssen, *Student Member, IEEE*, Eric A. M. Klumperink, *Fellow, IEEE*, Philip Quinlan, *Member, IEEE*, and Bram Nauta, *Fellow, IEEE*

Abstract—High selectivity becomes increasingly important with an increasing number of devices that compete in the congested 2.4GHz ISM-band. In addition, low power consumption is very important for IoT receivers. We propose a 2.4GHz zero-IF receiver front-end architecture that reduces power consumption by  $2 \times$  compared to state-of-the-art and improves selectivity by >20dB without compromising on other receiver metrics. To achieve this the entire receive chain is optimized. The LNTA is optimized to combine low noise with low power consumption. Stateof-the-art sub-30nm CMOS processes have almost equal strength complementary FETs, which result in altered design trade-offs. A Windmill 25%-duty cycle frequency divider architecture is proposed that uses only a single NOR-gate buffer per phase to minimize power consumption and phase noise. The proposed divider requires half the power consumption and has 2dB or more reduced phase noise when benchmarked against state-of-the-art designs. An analog FIR filter is implemented to provide very high receiver selectivity with ultra low power consumption. The receiver front-end is fabricated in a 22nm FDSOI technology and has an active area of 0.5mm<sup>2</sup>. It consumes 370µW from a 700mV supply voltage. This low power consumption is combined with 5.5dB noise figure. The receiver front-end has -7.5dBm IIP3 and 1-dB gain compression for a -22dBm blocker; both at maximum gain of 61dB. From three channels offset onward the adjacent channel rejection is >63dB for BLE, BT5.0 and IEEE802.15.4.

*Index Terms*—Low power, Internet-of-Things, receiver, analog FIR filter, frequency divider, LNTA, high selectivity.

#### I. INTRODUCTION

OW POWER receivers with very high selectivity are a prerequisite for the next generation Internet-of-Things (IoT) applications. It is expected that the number of wire-less devices will increase rapidly. Battery life-time becomes increasingly important because the burden of charging or changing batteries directly increases with the number of devices. An increasing number of devices compete in the already crowded low-GHz spectrum, thereby increasing the receiver's interference rejection requirements; especially, in the popular 2.4GHz ISM-band.

Reduced power consumption and improved selectivity should be achieved without compromising on noise figure

P. Quinlan is with Integrated Networking Products, Analog Devices, Cork, T12 X36X Ireland.

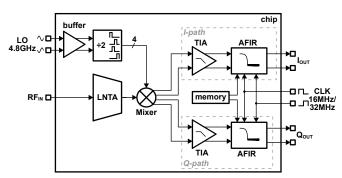

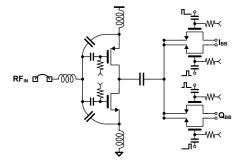

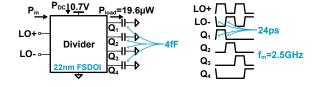

Fig. 1. Proposed receiver front-end architecture.

(NF). A good NF for state-of-the-art IoT receivers is 5-6dB [1-6]. In IoT receivers all blocks tend to contribute to the total power consumption [1-10]. Therefore, a fully optimized (system) design is required to obtain minimal power consumption.

This paper is an extension on [11], where we proposed an IoT receiver front-end that combines reduced power consumption with improved selectivity and without compromising on NF or linearity. Power optimization is applied across the entire receive chain: the low-noise transconductance amplifier (LNTA), frequency divider with mixer and baseband filter. The baseband filter is implemented as analog finite impulse response (FIR) filter to improve selectivity without increasing the power consumption. The receiver front-end is designed for Bluetooth Low-Energy (BLE), BT5.0 and IEEE802.15.4 and contains on-chip impedance matching. In this paper, we provide an extensive analysis of the optimizations in the LNTA, frequency divider and baseband filtering architectures. Furthermore, the measurement results are extended, including additional linearity measurements and discussion on the obtained performance.

The structure of the paper is as follows. First, the receiver front-end overview is provided in Section II. Followed by a detailed description of the optimizations in the LNTA (Section III) and frequency divider (Section IV), including a comparison to other divider approaches. The baseband filter architecture, including an analog FIR filter is described in Section V. Section VI discusses the measurement results and the conclusions are provided in Section VII.

#### **II. CIRCUIT IMPLEMENTATION**

Fig. 1 shows the proposed receiver front-end with zero-IF architecture [11]. A single-ended RF input is converted to current by an LNTA. This current is passed through a

B. J. Thijssen is with imec the Netherlands, 5656 AE Eindhoven, The Netherlands. (e-mail: bart.thijssen@imec.nl). He was formerly with the Integrated Circuit Design Group, MESA+ Institute, University of Twente.

E. A. M. Klumperink, and B. Nauta are with the Integrated Circuit Design Group, MESA+ Institute, University of Twente, 7500 AE Enschede, The Netherlands.

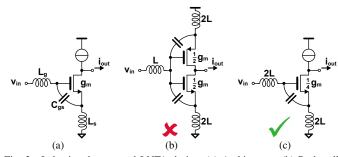

Fig. 2. Inductive degenerated LNTA design. (a) Architecture. (b) Push-pull implementation. (c) 2L implementation.

four-phase passive mixer to create differential I/Q baseband signals. The current is converted to voltage and low-pass filtered by a transimpedance amplifier (TIA). The channel selection is performed by an analog FIR (AFIR) filter, clocked at 16MHz and 32MHz for a 1Mbps and 2Mbps data-rate, respectively. The four-phase clock signals are provided by the divide-by-two frequency divider. For this prototype, the 16MHz/32MHz and 4.8GHz local oscillator (LO) clocks are provided externally, but multiphase clock generation and clock distribution is on-chip.

#### **III. LOW-NOISE TRANSCONDUCTANCE AMPLIFIER**

An inductive degenerated LNTA combines a low NF with low power consumption [12]. However, for very low power consumption the design trade-offs change. In the 2.4GHz IoT receiver application targeted in this work, our design goal is minimum power consumption at a reasonable NF.

## A. Ideal Inductors

Fig. 2a shows the inductive degenerated topology. The input impedance is

$$Z_{in} = j\omega(L_s + L_g) + \frac{1}{j\omega C_{gs}} + \frac{g_m}{C_{gs}}L_s$$

(1)

where  $g_m$  is the transistor's transconductance. Matching is accomplished at the resonance frequency

$$w_c^2 = \frac{1}{(L_s + L_g)C_{gs}}$$

(2)

for which  $Im(Z_{in}) = 0$  and

$$Z_{in} = \frac{g_m}{C_{gs}} L_s = Z_0 = 50\Omega \tag{3}$$

where  $Z_0$  is the source (antenna) impedance, here  $50\Omega$ . The noise performance of the LNTA can be described by its noise factor: the signal-to-noise ratio (SNR) degradation from input to output. Including only the thermal noise of the transistor transconductance, the noise factor is [12, 13]

$$F = 1 + \gamma Z_0 \frac{\omega_c^2 C_{gs}^2}{g_m} \tag{4}$$

where  $\gamma$  is the transistor's noise excess factor. The noise factor can be rewritten using (2) and the matching condition (3) as

$$F = 1 + \gamma \frac{1}{1 + \alpha} \tag{5}$$

with  $L_g = \alpha L_s$ . The corresponding required transconductance is

$$g_m = \frac{1}{F-1} \cdot \frac{\gamma Z_0}{w_c^2 L_{tot}^2} \tag{6}$$

where  $L_{tot} = L_s + L_g$ . (5) provides a possibly somewhat non-intuitive result: F is independent on  $g_m$ . It is solely determined by the inductor ratio  $\alpha$  for a given  $\gamma$ , assuming impedance matching and ideal inductors. According to (6), the minimal  $g_m$  is obtained for a maximum F and maximum  $L_{tot}$ . The maximum allowed F is often specified. The maximum inductor value is generally constrained by its self-resonance frequency or chip area requirements. In IoT applications, it is not desirable to have a very high inductor ratio  $\alpha$  — often applied in ultra-low NF-designs to obtain minimal NF but high  $L_{tot}$  should be pursued to minimize  $g_m$  and hence lower power consumption. The  $L_g$  and  $L_s$  values are in the same order of magnitude, given the maximum inductor value constraint.

Fig. 2 shows a thought experiment regarding the LNTA design; assuming  $\alpha = 1$  provides a sufficiently low NF and for simplicity the current source is ideal. Starting from  $L_g = L_s = L$  one could propose a push-pull design (Fig. 2b), since it provides double the  $g_m$  for the same bias current [14]. At first sight, this seems favorable only half the bias current is required. However, two 2*L*-sized inductors are required to provide an effective  $L_s = L$ . When a maximum inductance value of 2*L* is available, the circuit of Fig. 2c can also be implemented. This configuration requires only  $\frac{1}{4}g_m$  — in other words, half the bias current of the push-pull architecture — because  $g_m \propto 1/L_{tot}^2$ . It also requires a smaller area than Fig. 2b. This is a non-intuitive result and would mean that the push-pull architectures of [11, 14–16] are unfavorable.

## B. Including $Q_L$

Detailed analysis shows that the circuits in Fig. 2 are oversimplified. Integrated inductors are far from ideal and have a typical quality factor  $Q_L$  of 10 in the GHz frequency range. Including the limited  $Q_L$ , the noise factor becomes

$$F = 1 + \frac{r_g}{Z_0} + \frac{r_s}{Z_0} + \gamma \frac{1}{1+\alpha} \left(\frac{Z_0 + r_g + r_s}{Z_0}\right)^2$$

(7)

where  $r_g$  and  $r_s$  are the resistance of  $L_g$  and  $L_s$ , respectively. Not only the two resistive noise terms are added, but also the  $i_{out}/v_{in}$  and  $i_{out}/i_{n,g_m}$  transfers change and thereby the  $\gamma$  term, which was neglected in [12]. The  $\gamma$  term increases for higher  $r_g$  and  $r_s$  (lower  $Q_L$ ). The  $Q_L$  limitation affects the circuit matching only little, but it has a significant effect on the noise factor and thus the required  $g_m$ . Using (7), the required  $g_m$  is

$$g_m = \frac{1}{F - \left(1 + \frac{\omega_c L_{tot}}{Q_L Z_0}\right)} \cdot \frac{\gamma Z_0}{\omega_c^2 L_{tot}^2} \left(1 + \frac{\omega_c L_{tot}}{Q_L Z_0}\right)^2 \quad (8)$$

which simplifies to (6) for no inductor losses  $(Q_L \to \infty)$ .

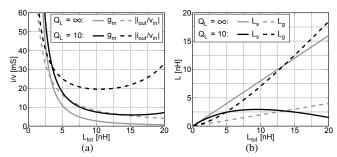

Fig. 3 shows the required  $g_m$  and inductances for  $Q_L = \infty$ and  $Q_L = 10$  as function of  $L_{tot}$ , assuming a desired noise factor of 1.8 and  $\gamma \approx 1$ . The required  $g_m$  is higher for

Fig. 3. LNTA parameters of Fig. 2a for different  $Q_L$  with F = 1.8. (a) Required transconductance and transconductance gain. (b) Inductance.

$Q_L = 10$  as expected. Some interesting observations can be made: For  $L_{tot} \ge 10$ nH, the required  $g_m$  is roughly constant; higher inductance hardly reduces the required  $g_m$ . Even when neglecting that high valued on-chip inductors typically have lower  $Q_L$ . The result is that chip area can be saved. Furthermore, the required  $L_s$  does not increase above 2.9nH (Fig. 3b).  $g_m$  is no longer proportional to  $1/L_s^2$ . The push-pull configuration is favorable when the maximum attainable inductor value is  $\ge 2L_s$  (here  $\ge 5.8$ nH).

Fig. 3a also shows the LNTA transconductance "gain"  $|i_{out}/v_{in}|$ . A higher  $|i_{out}/v_{in}|$  will result in smaller noise contribution of subsequent stages. At minimum  $g_m$ ,  $|i_{out}/v_{in}|$  is also at its minimum. However, it cannot be changed much by changing  $L_{tot}$ . By decreasing  $L_{tot}$ ,  $|i_{out}/v_{in}|$  increases, but the required  $g_m$  increases more rapidly and thus the LNTA current consumption; when taking into account that  $|i_{out}/v_{in}|$  is squared regarding the noise contribution for subsequent stages.  $|i_{out}/v_{in}|$  increases slightly for high inductor values, but the  $Q_L$  and self resonance frequency will decrease significantly for very large inductors (L > 8nH).

The above analysis provides insight in the design complexity of the inductive degenerated LNTA. It concludes that  $L_g$  and  $L_s$  should be in the same order of magnitude and a push-pull architecture can become favorable when including  $Q_L = 10$  in the analysis. The LNTA transconductance gain cannot be increased much to reduce the noise contribution of subsequent stages, because this would result in a large increase in power consumption or impractically large inductors.

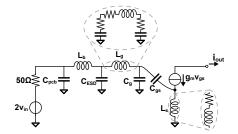

## C. Brute-Force Search Model

Including the limited  $Q_L$  is insufficient to fully optimize the LNTA design. This requires the more complex circuit of Fig. 4 to model the LNTA's small-signal behavior. Parasitic capacitors are included:  $C_{pcb}$  the PCB parasitic,  $C_{ESD}$  the ESD diodes' capacitance including pad parasitics, and  $C_g$  the parasitic to ground at the gate.  $L_b$  is the bondwire inductance, which has an estimated Q-factor of 35.  $L_s$  is modeled with  $Q_L = 10$ .  $L_g$  is not connected to ground and requires the more extensive II-model. The  $L_g$  II-models are derived from the S-parameters at 2.44GHz, which is sufficient to optimize for our target application. A design space for  $L_s$ ,  $C_{gs}$ ,  $g_m$  is estimated from the results of the simplified analysis. About 20 different  $L_g$  designs were characterized using Momentum simulations. All resistors and the  $g_m$  have an associated noise source.

Fig. 4. Small-signal model for brute-force optimization of the LNTA.

Fig. 5. Proposed LNTA including mixer.

Based on this design space, brute-force search is applied to find the minimal required  $g_m$  for the NF and  $S_{11} < 15$ dB in the 2.4GHz ISM-band requirements — optimizing the design. A push-pull architecture is selected, because the required  $L_s$ is sufficiently low at 3.6nH.  $L_g$  is 4.3nH, the inductors are approximately equal as expected to minimize  $g_m$ .

In addition to minimum  $g_m$  for a given NF, the linearity requirement has to be satisfied. The main non-linearity sources are the transistor transconductance and output impedance. The output impedance non-linearity contribution depends on mixer/TIA design. Typically, the TIA input impedance is limiting in-band while out-of-band (OOB) the mixer switch onresistance. The transconductance non-linearity can be changed by the biasing conditions. A larger overdrive voltage improves the linearity at the cost of transconductance efficiency  $g_m/I_{DC}$ and hence power consumption. An alternative measure would be to increase  $L_s$  (the transconductance feedback), but the desired  $L_s$  is already high.

#### D. LNTA and Mixer Topology

Fig. 5 shows the proposed LNTA including the passive mixer switches. In this design, both FETs are nominally biased at roughly half supply to allow for maximum voltage swing and to minimize large signal clipping given the supply headroom. The OOB input-referred third-order-intercept point (IIP3) is slightly limited by drain voltage swing induced non-linearity in the LNTA due to the large mixer switch resistance values, which have been optimized to save power. The OOB IIP3 could be improved by 4dB, according to simulation, by reducing the mixer switch resistance. The simulated output impedance magnitude of the LNTA is  $3.3k\Omega$ . The linearity is state-of-the-art for a BLE receiver (IIP3>–10dBm) combined with a low mixer load to the frequency divider. Constant  $g_m$ -biasing is employed to maintain the LNTA NF, matching and IIP3 specifications across PVT variations.

Fig. 6. Power consumption of multiple buffers driving a capacitive load.

#### **IV. FREQUENCY DIVIDER**

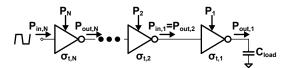

A significant part of the power consumption is consumed by the frequency divider and mixer clock buffers in an IoT receiver, e.g. one third in [5]. The proposed receiver front-end employs 25% duty-cycle clocks to downconvert the singleended LNTA output RF current to differential I/Q baseband currents. In this section, a minimum logic gate design strategy to minimize power consumption is explained, followed by a novel "Windmill" frequency divider architecture to achieve very low power consumption [11]. Finally, the Windmill divider performance is evaluated by a comparison to multiple prior art designs.

## A. Minimum Logic Gate Design Strategy

Fig. 6 shows a chain of multiple (inverter) buffers;  $P_n$  is the power provided by the supply and  $P_{in,n} = P_{out,n+1}$  is the power required to drive stage n. The fundamental required power to drive the (mixer) load is

$$P_{load} = f_m C_{load} V_{DD}^2 = P_{out,1} \tag{9}$$

where  $f_m$  is the mixer clock frequency and  $V_{DD}$  the supply voltage. All other power is "lost" — in the output parasitics of the buffer, as crowbar current or in driving the buffer. Therefore, the power dissipation of a single buffer stage is

$$P_{diss,n} = P_n - P_{out,n} + P_{in,n} \tag{10}$$

and the total dissipated power of an N stage buffer is

$$P_{diss} = \sum_{n=1}^{N} P_n - P_{out,1} + P_{in,N} = \sum_{n=1}^{N} P_{diss,n}$$

(11)

The total random time deviation  $\sigma_t$ , either by phase noise and/or mismatch, is the sum of the variances

$$\sigma_t^2 = \sum_{n=1}^N \sigma_{t,n}^2 \tag{12}$$

assuming that the individual random timing deviations are uncorrelated. Eqs. (11) and (12) show that minimum  $P_{diss}$ and  $\sigma_t^2$  is obtained when the most efficient buffers — in terms of minimum  $P_{diss}$  and  $\sigma_t^2$  — are used with a minimal number of stages. Therefore, a minimum number of efficient gates e.g. CMOS logic gates — is a strong starting point to optimize the frequency divider.

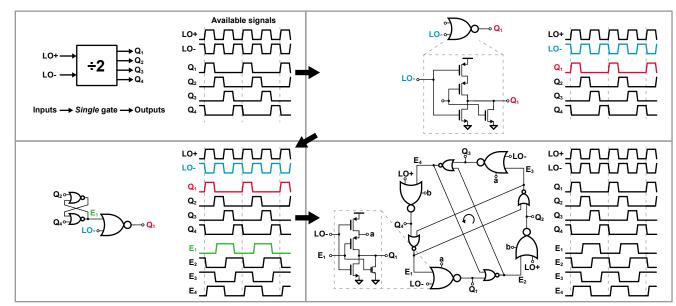

#### B. Windmill Frequency Divider

Fig. 7 illustrates the design procedure of the 25% dutycycle frequency divider starting from the minimum — single — gate design strategy. Typically, differential 50% duty-cycle LO signals are available at  $2f_m$  or  $4f_m$  to generate the mixer clocks [5–9, 17, 18]. At minimum one selective gate is required to create the 25% duty-cycle mixer phases. Here, we start with  $2f_m$  clocks. This results in less power consumption in the buffers that create the square wave LO from the sinusoidal voltage-controlled oscillator (VCO) signals.

The available signals of the design are the input signals LO+ and LO-, 50% duty-cycle at  $2f_m$ , and the output signals  $Q_x$  (x = 1..4), 25% duty-cycle at  $f_m$ , as shown in Fig. 7 (top left). The second illustration shows the single gate implementation using a NOR-gate. A NOR-gate is chosen, because it provides selectivity on high pulses as required. NOR-gates are a very efficient in modern CMOS technologies where NFETs and PFETs are approximately equal strength. LO- is inverted through the NOR-gate to create  $Q_1$ . Every other LO- low should be passed to  $Q_1$  which requires a memory element to count the LO- lows. The memory element is implemented as shown in Fig. 7 (bottom left) by a NOR SR-latch. Signals  $Q_2$  and  $Q_4$  create an enable signal  $E_1$ , which is low for every other LO- low. This structure is repeated in the last illustration for every output, to create the "Windmill" divider — indicating the rotating nature of the gate enable signals  $E_x$  and outputs  $Q_x$ . The latches toggle the LO-, LO+ to  $Q_1/Q_3$ ,  $Q_2/Q_4$ , respectively.

Only the large transistors in the large NOR gates contribute to the output edges and have to be scaled to the drive mixer load. All other transistors can be minimal size as long as the divider meets the speed requirement. Furthermore, only those large transistors contribute to the phase noise and mismatch. In this way, very low power consumption is achieved while also realizing good phase noise and mismatch as only a single gate propagation delay contributes to timing uncertainty. The top PFET of the opposite large NOR gates is shared, via nodes aand b, to reduce the uncorrelated phase noise contributions that degrade the receiver's NF [19, 20]. In addition, since the PFET is shared, a single PFET is used to create two rising edges; reducing the power consumption of the preceding buffers. The phase relation of the outputs is independent on the start-up condition as verified by the I/Q mismatch simulations.

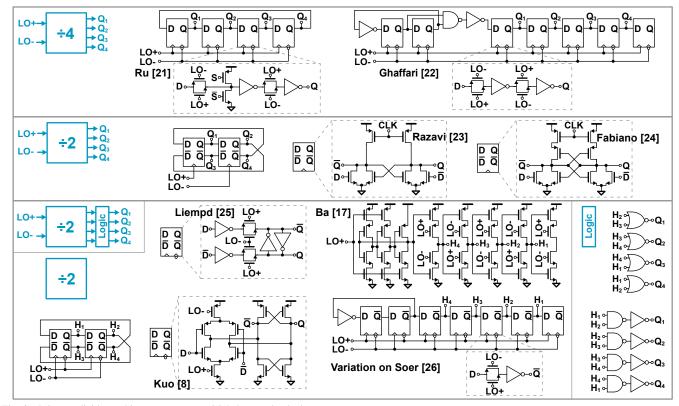

#### C. Divider Comparison

In this section, we provide a comparison between published divider architectures that create 25% duty-cycle clock signals. Three approaches can be distinguished as illustrated in Fig. 8:

- Direct divide-by-4; divide a differential LO at  $4f_m$  by four to create 25% duty-cycle clock signals; [21, 22].

- Direct divide-by-2; divide a differential LO at  $2f_m$  by two to create 25% duty-cycle clock signals; the Windmill divider (Fig. 7) and [23, 24].

- Divide-by-2 with logic; divide a differential LO at 2fm by two to create 50% duty-cycle clock signals at fm and use subsequent logic to create 25% duty-cycle outputs; [8, 17, 25] and a variation on [26] without the extra intermediate inverters to reduce its power consumption.

The dividers, all designed in 22nm FDSOI, are compared by simulation with the assumptions as summarized in Fig. 9.  $C_{load}$  is 4fF for each  $Q_x$ -output — equal to the mixer switch that is optimized by using  $3\times$  the minimal finger gate pitch to reduce its parasitic capacitance and contact resistance by

Fig. 7. Step-by-step design of the 25% duty-cycle "Windmill" frequency divider.

Fig. 8. Prior art divider architectures to create 25% duty-cycle clocks.

Fig. 9. Assumptions (highlighted) for simulation based 25% duty-cycle divider comparison. The LO signals are shown for the divide-by-2 case.

increasing the number of source and drain contacts. The output frequency is 2.5GHz, which means an input frequency of

10GHz and 5GHz for the divide-by-4 and divide-by-2 cases, respectively. The required power to drive the mixer load is 19.6µW for a 700mV supply. The *LO* rise-  $(5\% \rightarrow 95\%)$  and fall-times  $(95\% \rightarrow 5\%)$  are 24ps. The transistors are sized such that the outputs  $Q_x$  have equal rise- and fall-times as the inputs:  $24\pm0.3$ ps. All designs are optimized in terms of scaling, e.g. in [22] the first divider is minimal size as these transistors do not contribute to the phase noise or mismatch. The dividers of [17, 22, 26] contain a dummy device to avoid I/Q-offsets.

The schematic simulation results are summarized in Table I,

|                                           | Windmill | Ru [21] | Ghaffari [22] | Razavi [23] | Fabiano [24] | Kuc    | o [8]  | Liempd [25] | Ba [17] | Soer [26]<br>inspired |

|-------------------------------------------|----------|---------|---------------|-------------|--------------|--------|--------|-------------|---------|-----------------------|

| Division factor                           | 2        | 4       | 4             | 2           | 2            | 2      |        | 2           | 2       | 2                     |

| 50% $ ightarrow$ 25% duty-cycle           | -        | -       | -             | -           | -            | AND    | NOR    | AND         | AND     | AND                   |

| P <sub>DC</sub> [µW]                      | 36.1     | 41.7    | 53.1          | 187.0       | 57.4         | 62.9   | 63.9   | 59.7        | 59.7    | 57.9                  |

| P <sub>diss</sub> [µW]                    | 27.3     | 47.1    | 70.0          | 172.5       | 51.1         | 53.5   | 54.5   | 48.7        | 57.1    | 49.2                  |

| Phase Noise, white [dBc]<br>(@100MHz)     | -159.0   | -157.0  | -157.0        | -155.3      | -154.5       | -154.9 | -156.7 | -155.4      | -154.6  | -154.9                |

| Phase Noise, 1/f region [dBc]<br>(@10kHz) | -135.0   | -132.8  | -132.9        | -132.5      | -134.5       | -130.4 | -132.2 | -130.9      | -130.0  | -129.9                |

| σ <sub>ιQ</sub> [%]                       | 0.60     | 0.82    | 0.84          | 0.71        | 0.55         | 1.0    | 0.75   | 1.0         | 1.1     | 1.1                   |

TABLE I

Simulated Performance Comparison of 25% Duty-Cycle Clock Dividers in 22nm FDSOI

The assumptions for this comparison are shown in Fig. 9.

where the best performance per specification is highlighted by bold text. The dividers are compared on power dissipation  $(P_{diss})$  as defined in (10), phase noise in the white and 1/f regions and I/Q-mismatch ( $\sigma_{IQ}$ ). I/Q mismatch is of little concern in the proposed zero-IF architecture, but is included for a complete comparison of the dividers. The divider DC power consumption ( $P_{DC}$ ) is also included for completeness.

The power dissipation of the Windmill divider is 42% reduced or more compared to the other architectures. The Windmill divider has the lowest phase noise by 2dB or more in the white noise region. The 1/f-noise is less dominant, because the noise corner is at a low offset frequency of about 2MHz. Only [24] has a slightly better I/Q-mismatch than the Windmill divider at a significantly higher power dissipation. For [8], the two different logic architectures are compared. The NOR-based design has lower phase noise and I/Q-mismatch at a similar power dissipation. The NOR-gate benefits from the equal NFET-PFET strength in modern CMOS processes

Some remarks: [21] requires start-up circuitry, controlled by S and  $\overline{S}$ , which can introduce possible start-up issues. [23, 24] have clock overlap, because the rising edge of  $Q_{x+1}$  triggers the falling edge of  $Q_x$ . [17] has an additional static 1.2% I/Q-offset, because the rising edge of  $H_4$  is relatively slow. During  $H_4$ 's rising edge, the input of the tri-state inverter is not at ground, because of charge injection of the previous stage while the input node is floating. Furthermore, [17] has a significantly asymmetric load to the driver of the divider.

All in all, the Windmill divider consumes almost half the power and has 2dB less phase noise. The Windmill divider is the only design with only a single gate involved in creating both rising and falling output edges and has outstanding performance. Moreover, it does not have any of the (potential) issues mentioned above. These results are not IoT application specific — all designs can be scaled for more drive power or to reduce phase noise and/or I/Q-mismatch.

#### V. BASEBAND ANALOG FIR FILTER

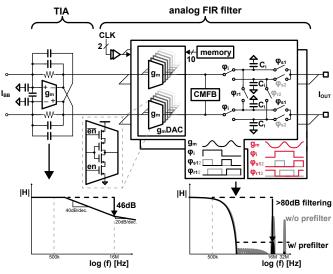

High selectivity is achieved by the baseband analog FIR filter as shown in Fig. 10. It contains two time-interleaved paths to double the sample-rate for the same filter bandwidth [27, 28]. The transconductor is implemented as a 10bit pseudo-differential transconductance DAC ( $g_m DAC$ ). A detailed explanation of the analog FIR filtering operation is described

Fig. 10. Baseband filter consisting of TIA and analog FIR filter.

in [27, 28]. Low power consumption is obtained by push-pull transconductors, 5bit thermometer coding of the  $g_mDAC$  and a low update rate of the  $g_mDAC$ . The push-pull transconductors have low input referred noise for a given supply current. 5bit thermometer coding of the  $g_mDAC$  reduces the number of transitions in the  $g_mDAC$ , because the filter code turns fully on/off only once per integration cycle, much slower than the  $g_mDAC$  update frequency. Furthermore, the partially thermometer coding of the  $g_mDAC$  reduces the effect of transconductor mismatch on the filter stopband — in this design limited to -60dB [28].

The  $g_m$ DAC update-rate is 16MHz instead of 64MHz [27, 28] to further reduce the power consumption [11]. This comes at the cost of a closer filter alias and proportionally reduced attenuation of the filter alias. The inherent sinc windowed integration provides now only 34dB of attenuation of this alias. The TIA is employed to provide a prefilter that mitigates the remaining alias. The TIA provides  $2^{nd}$ -order filtering by feedforward capacitors for about one decade [29]. In this way, 46dB of filtering is achieved at the alias frequency. Resulting in 80dB of total attenuation of the analog FIR alias. The exact cut-off frequency of the TIA is relatively relaxed, because it only has to provide prefiltering of the alias. Furthermore, the filtering characteristic is determined by the  $g_m$ DAC-code

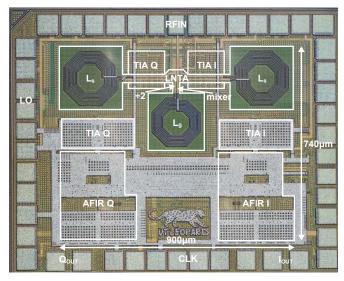

Fig. 11. Die micrograph indicating the major blocks.

and clock signals — making the baseband filtering PVT insensitive [28]. Back-biasing is employed to compensate for the differential DC-offset in the TIAs. In this way, the DC-offset can be compensated without a significant increase in power consumption or noise — in contrast to current injection. The differential DC-offset of the  $g_m$ DACs is very small, well below 1mV referred at the output.

#### VI. EXPERIMENTAL RESULTS

The receiver front-end was designed and fabricated in a 22nm FDSOI process and wire-bonded in a  $40 \times 40$  pin QFN package. The die has an active area of 0.5mm<sup>2</sup> and the supply voltage is 700mV. Fig. 11 shows the die micrograph.

The measurement setup is published in [11]. The package is placed in a zero insertion force (ZIF) socket (Ironwood SG-MLF). Impedance matching is realized on chip — no external matching components are used. The capacitor output voltage is measured using an active probe (Teledyne LeCroy AP033) and the charge sharing loss is de-embedded as in [28]. The measurements are performed in BLE (1Mbps) mode unless stated otherwise.

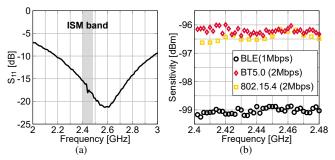

#### A. Matching and Sensitivity

The measured  $S_{11}$  is shown in Fig. 12a. Good matching  $(S_{11} < -10 \text{dB})$  is achieved between 2.2 and 2.9GHz. The receiver's  $S_{11}$  is below -15 dB in the ISM-band which is used in the targeted applications.

The measured noise figure is 5.5dB. The measured sensitivity for <0.1% bit-error-rate (BER) is shown in Fig. 12b for each channel. The transmitted signal is a PRBS-9 sequence. The received signal is demodulated using Matlab CPM demodulator (BLE, BT5.0) and MSK demodulator (802.15.4). For BLE, the Matlab CPM demodulator requires roughly 8dB SNR to achieve 0.1% BER, which is about 2dB less than a coherent receiver with threshold detection. The sensitivity is flat across the measured band. The 802.15.4 standard is characterized at 2Mbps HS-OQPSK raw data rate without despreading as in [3, 4].

Fig. 12. Measured receiver front-end performance. (a) S<sub>11</sub>. (b) Sensitivity.

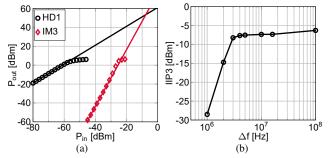

Fig. 13. Measured linearity. (a) In-band gain and out-of-band IM3 (for  $\Delta f = 4.01$ MHz and  $2\Delta f = 7.98$ MHz input tones). (b) IIP3 versus frequency offset.

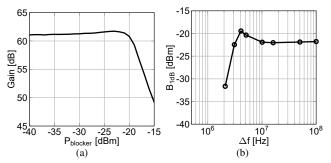

Fig. 14. Measured receiver front-end performance in presence of a blocker. (a) Gain for a blocker at 4.1MHz offset. (b)  $B_{1dB}$  versus frequency offset.

#### B. Linearity

The large signal in-band linearity is characterized by the compression point. The in-band gain is shown in Fig. 13a. The maximum gain is 61dB, roughly 30dB in both the frontend up to the TIA and analog FIR filter. The output-referred 1dB compression point ( $OP_{1dB}$ ) is 5.0dBm, corresponding to a  $1.1V_{pp}$  differential output voltage.

The small-signal nonlinearity is characterized by the thirdorder modulation (IM3) product as shown in Fig. 13. The IIP3 is -7.5dBm for a 4.01MHz offset at maximum gain of 61dB. The IIP3 is approximately flat from a 3MHz offset frequency. Simulation shows that this is limited by the LNTA.

Fig. 14 shows the measured blocker 1-dB compression point (B<sub>1dB</sub>), the blocker input power for which the in-band gain is 1dB compressed. The B<sub>1dB</sub> is approximately -22dBm for a frequency offset  $\geq$ 3MHz.

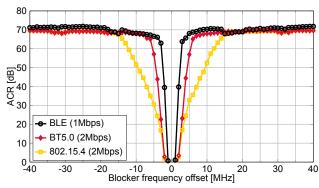

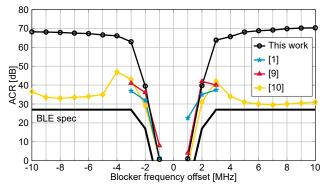

# C. Adjacent Channel Rejection

The receiver's performance in presence of a blocker is characterized by the adjacent channel rejection (ACR). The ACR

Fig. 15. Measured adjacent channel rejection for different standards.

is measured with the desired signal strength at sensitivity+3dB and a blocker signal, modulated using the same standard with PRBS-15 sequence, at various offset frequencies. The wanted signal and blocker are generated with an R&S SMW200A and R&S SMBV100A, respectively. Fig. 15 shows the measured ACR.

The ACR is  $\geq 63$ dB for BLE (1Mbps) at a frequency offset  $\geq 3$ MHz. BT5.0 with double the data-rate has double the filter bandwidth. This shows in the ACR as  $\geq 65$ dB ACR at  $\geq 6$ MHz; double the frequency offset of BLE. The 802.15.4 ACR is  $\geq 67$ dB for frequency offsets of  $\geq 15$ MHz. 802.15.4 does not use Gaussian filtering of the transmitted signals and has therefore more transmitted spectral leakage in neighboring channels, which limits the maximal achievable ACR as confirmed here by the measurements. The filter alias at 16MHz/32MHz for 1Mbps/2Mbps is just visible by a small perturbation in the ACR rejection profile — indicating that the prefilter operates as desired.

In the following, we provide a short discussion regarding the ACR. From Fig. 15, we conclude that the ACR for BLE is limited to about 70dB. Various sources can constrain the ACR performance:

- Limited blocker attenuation; the (small-signal) filtering.

- Reciprocal mixing; because of LO phase noise.

- Blocker gain compression; related to B<sub>1dB</sub>.

The demodulation algorithm requires an SNR as derived from

$$SNR_{min} \approx 174 + Sensitiviy - NF - 10 \log(BW)$$

$\approx 10 dB$  (13)

where NF is measured noise figure and BW the bandwidth. Therefore, 70dB of ACR requires about 80dB of attenuation to still demodulate the wanted signal. The phase noise of the mixer clock will result in an in-band reciprocal mixing product. The receiver's blocker noise figure (BNF) can be estimated as [30]

$$BNF \approx -174 + P_b + \mathcal{L}(\Delta f) \tag{14}$$

where  $P_b$  is the blocker input power, which is

$$P_b = \text{Sensitivity} + 3 + \text{ACR} \tag{15}$$

at a given ACR level. From Eqs. (13) to (15) the maximum allowed phase noise to achieve 70dB ACR is derived as

$$\mathcal{L}_{\max}(\Delta f) \approx -\text{SNR}_{\min} - 10\log(\text{BW}) - \text{ACR}$$

$$\approx -140 \text{dBc/Hz}$$

(16)

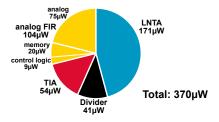

Fig. 16. Power consumption breakdown.

neglecting the circuit induced noise, i.e. BNF = NF + 3dB, as in [30]. The minimal required  $B_{1dB}$  for 70dB ACR is

$$B_{1dB,min} \approx Sensitivity + 3 + ACR$$

$\approx -26 dBm$  (17)

From a frequency offset of 5MHz onward, the BLE ACR is roughly constant at 70dB. Although, the analog FIR filter has constant rejection, the prefilter has more attenuation for larger frequency offsets. Hence, the ACR is not limited by the filter attenuation in this region. The simulated phase noise of the Windmill divider is -153.6dBc/Hz at 1MHz offset, which means that also the phase noise is not limiting. The ACR is most likely limited by blocker gain compression of -22dBm, which is somewhat more severe for a modulated blocker. This also explains that the 2Mbps ACR is slightly worse, because these standards have 3dB higher sensitivity and thus less "headroom" towards blocker gain compression.

At 2MHz offset, the ACR is 39dB — requiring a  $B_{1dB}$  of approximately -57dBm, which is much less than the measured -31dBm. The required filtering is roughly 49dB. The expected attenuation at 2MHz is about 70dB (10dB TIA + 60dB analog FIR [27, 28]). However, the blocker is modulated with 1Mbps covering a bandwidth of 1MHz, so that the filter attenuation from 1.5 to 2.5MHz offset is relevant. The worst case attenuation at 1.5MHz is only 46dB (6dB TIA + 40dB analog FIR [27, 28]), because of the steep FIR filter profile. At 3MHz offset the expected filtering is 76dB (16dB TIA + 60dB analog FIR [27, 28]). Therefore, the measured ACR of 39dB/63dB for 2MHz/3MHz offset can be explained by taking into account the blocker bandwidth. Consequently, the filter profile limits the ACR performance below approximately 5MHz offset when also taking into account the divider phase noise above.

The receivers frequency response was not measured here, as it is constrained by compression above 5MHz. Instead we report ACR performance, because this is what ultimately matters. The analog FIR filter response can be found in [28].

## D. Power Consumption

The total power consumption is  $370\mu$ W as shown in Fig. 16. The frequency divider power consumption is only  $41\mu$ W, excluding the preceding buffer.

## E. Comparison

The ACR in BLE-mode is compared to state-of-the-art IoT receivers in Fig. 17. The proposed receiver front-end has >20dB improved ACR for frequency offsets >2MHz. The

|                                                           | This Work            |                      |                       | [9]<br>ISSCC'20        |                        | [18]<br>ISSCC'20   | [10]<br>TMTT'19    | [1]<br>ISSCC'18    | [2]<br>ISSCC'18    |                      | [3] <sup>h</sup><br>ISSCC'15 |                       | [7]<br>ISSCC'13  | [5]<br>CICC'17     |

|-----------------------------------------------------------|----------------------|----------------------|-----------------------|------------------------|------------------------|--------------------|--------------------|--------------------|--------------------|----------------------|------------------------------|-----------------------|------------------|--------------------|

| Standard                                                  | BLE                  | BT5.0                | 802.15.4 <sup>d</sup> | BLE                    | BT5.0                  | BLE                | BLE                | BLE                | BLE                | BT5.0                | BLE                          | 802.15.4 <sup>d</sup> | BLE              | BLE                |

| Data rate [Mbps]                                          | 1                    | 2                    | 2                     | 1                      | 2                      | 1                  | 1                  | 1                  | 1                  | 2                    | 1                            | 2                     | 1                | 1                  |

| On-chip Matching                                          | Yes                  |                      |                       | Yes                    |                        | Yes                | No                 | Yes                | Yes                |                      | No                           |                       | Yes              | Yes                |

| P <sub>DC</sub> [mW]                                      | 0.37                 | 0.40                 | 0.40                  | 0.89e                  | -                      | 5.3 <sup>g</sup>   | 1.44°              | 1.2ª               | 1.1º               | -                    | 1.95°                        | -                     | 1.7              | 0.7°               |

| NF [dB]                                                   | 5.5                  |                      |                       | -                      |                        | -                  | 7.2                | 6                  | 5.9                |                      | 6.1                          |                       | 8.5              | 5.2                |

| Sensitivity [dBm]                                         | -99 <sup>b</sup>     | -96 <sup>b</sup>     | -96.5 <sup>b</sup>    | -96.4                  | -93.5                  | -94                | -92                | -94                | -95                | -92                  | -94                          | -91                   | -                | -95.8              |

| ACR 2 <sup>nd</sup> /3 <sup>rd</sup> channel <sup>a</sup> | 39/63 <sup>b,c</sup> | 44/65 <sup>b,c</sup> | 52/67 <sup>b,c</sup>  | 36.1/41.0 <sup>f</sup> | 36.3/45.0 <sup>f</sup> | 40/42 <sup>f</sup> | 29/42 <sup>f</sup> | 31/36 <sup>f</sup> | 18/30 <sup>f</sup> | 18/29.5 <sup>f</sup> | 25/35 <sup>f</sup>           | 24/35 <sup>f</sup>    | -                | -                  |

| IIP3 [dBm]                                                | -7.5                 |                      |                       | -13.1                  |                        | -                  | -17                | -                  | -                  |                      | -                            |                       | -6               | -19.7 <sup>i</sup> |

| B <sub>1dB</sub> [dBm]                                    | -22                  |                      |                       | -                      |                        | -                  | -                  | -                  | -                  |                      | -                            |                       | -                | -                  |

| Gain [dB]                                                 | 61                   | 57                   | 57                    | 43.1                   |                        | -                  | 42                 | 68                 | -                  |                      | -                            |                       | 57               | 47-72              |

| Supply Voltage [V]                                        | 0.7                  |                      | 0.5                   |                        | 0.8                    | 1.2                | 1                  | 0.8                |                    | 1                    |                              | 0.6&1.2               | 1                |                    |

| Active Area [mm <sup>2</sup> ]                            | 0.5                  |                      | 1.9 <sup>g</sup>      |                        | 0.89 <sup>g</sup>      | 0.7                | 1.64 <sup>g</sup>  | 0.8 <sup>g</sup>   |                    | 1.3 <sup>g</sup>     |                              | 0.22                  | 0.7 <sup>g</sup> |                    |

| Technology                                                | 22nm<br>FDSOI        |                      | 22nm<br>FDSOI         |                        | 40nm<br>CMOS           | 130nm<br>CMOS      | 65nm<br>CMOS       | 40nm<br>CMOS       |                    | 40nm<br>CMOS         |                              | 65nm<br>CMOS          | 40nm<br>CMOS     |                    |

TABLE II

Receiver Performance Summary and Comparison

<sup>a</sup>Channel spacing: BLE 1MHz; BT5.0 2MHz; 802.15.4 5MHz. <sup>b</sup>Demodulated using Matlab CPM demodulator (BLE, BT5.0) and MSK demodulator (802.15.4), both using a Viterbi algorithm with traceback depth of 16. <sup>a</sup>Measured with wanted signal at sensitivity +3dB. <sup>a</sup>Verified with 2Mbps raw data rate HS-OQPSK without de-spreading as in [3,4]. <sup>a</sup>Power consumption is estimated from power breakdown, e.g. w/o VCO/PLL. <sup>a</sup>Measured with wanted signal at -67dBm. <sup>a</sup>Includes more than RX path. <sup>b</sup>Some specifications of this work are found in [4]. <sup>i</sup>At minimal gain of 47dB.

Fig. 17. Comparison of the measured ACR for BLE (1Mbps).

prior art is measured with the wanted signal at -67dBm, which is similar to placing a 29dB attenuator in front of the proposed receiver front-end. Alternatively, the feedback resistor can be reduced to avoid gain compression. The TIA feedback resistor is tunable in this design — allowing a 20dB gain reduction. Note that this is not an industrial product design, but rather an academic research paper that has a broader scope: software defined ultra-low-power radio frontends. Rather than choosing a standard specific sensitivity, we instead use a more general standard independent criterion: (actual NF based) sensitivity+3dB.

Table II summarizes the proposed receiver's performance and compares it to state-the-of-art 2.4GHz IoT receivers only comparing the front-end. The power consumption of the receive chain is reduced by  $2\times$  or more, while achieving similar noise figure. The ACR is improved by more than 20dB at the 3<sup>rd</sup> channel offset. The IIP3 linearity is similar or higher than the prior art.

#### F. Full Receiver Discussion

In this section, the proposed design's performance is placed in the perspective of a full receiver design — including phaselocked loop (PLL) and analog-to-digital converter (ADC).

In this design, all the channel filtering requirements are achieved by placing the high-order analog FIR filter after the TIA. This architecture choice significantly relaxes the dynamic range, sample rate and power consumption requirements of the ADC and down-stream digital signal processing functions, which only has to support demodulation and symbol detection.

In an application, the LO comes from an on-chip PLL with VCO and its phase noise could result in significant blocker induced noise which cannot be filtered — constraining the ACR. The phase noise of a state-of-the-art 0.5mW 5GHz VCO is -140dBc/Hz at 10MHz offset [31]. This corresponds to -140dBc/Hz at 5MHz offset when divided down to 2.5GHz using the frequency divider, which is sufficiently low for the achieved ACR.

It is useful to estimate the total power consumption of the entire receiver. A state-of-the art all-digital phase-locked loop (ADPLL) consumes  $673\mu$ W [32] and will consume roughly 910 $\mu$ W when implementing the low phase noise VCO design of [31] to obtain the ACR performance. The sampled output of the analog FIR filter, at 1Msample/s, can be used for ADC conversion. The ADC power consumption will be negligible if a successive-approximation register (SAR) ADC is used. E.g., the 1Msample/s 10bit SAR ADC in [33] consumes only 3.2 $\mu$ W, more than sufficient for demodulation. Hence, the total power consumption excluding demodulation is estimated as 0.91+0.37=1.3mW.

# VII. CONCLUSIONS

A 2.4GHz IoT receiver front-end is proposed and characterized for BLE, BT5.0 and IEEE802.15.4. The entire receive Several techniques are proposed that achieve a  $370\mu$ W power consumption — almost  $2\times$  lower than the state-ofthe-art — in combination with a competitive 5.5dB NF. The LNTA has a push-pull inductive degenerated common-source architecture and is optimized using brute-force search on a simplified, though accurate, model. A single gate Windmill frequency divider has almost half the power dissipation concurrent with a phase noise improvement of 2dB or more compared to prior art. An analog FIR filter is implemented with prefilter. Its 10bit transconductor DAC contains push-pull transconductors, 5bit thermometer coding and a low (16MHz for BLE) FIR-coefficient update-rate to optimize its power consumption while also achieving very sharp transition band. The receiver has  $\geq$ 63dB ACR at  $\geq$ 3 channels offset improving the state-of-the-art by  $\geq$ 20dB.

The proposed architecture and implementation techniques result in very low power consumption combined with outstanding selectivity, which makes the receiver front-end design ready for future IoT standards.

#### **ACKNOWLEDGMENTS**

We would like to thank G. Wienk for CAD assistance, H. de Vries and A. Rop for measurement support, and our other colleagues from the ICD-group for fruitful discussions. We thank Y. Sudarsanam and B. Uppiliappan from Analog Devices Boston for the memory and decoder design. We thank GlobalFoundries for silicon donation.

#### REFERENCES

- [1] H. Liu, Z. Sun, D. Tang, H. Huang, T. Kaneko, W. Deng, R. Wu, K. Okada, and A. Matsuzawa, "An ADPLL-Centric Bluetooth Low-Energy Transceiver with 2.3mW Interference-Tolerant Hybrid-Loop Receiver and 2.9mW Single-Point Polar Transmitter in 65nm CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, 2018, pp. 444–445.

- [2] M. Ding, X. Wang, P. Zhang, Y. He, S. Traferro, K. Shibata, M. Song, H. Korpela, K. Ueda, Y.-H. Liu, C. Bachmann, and K. Philips, "A 0.8V 0.8mm<sup>2</sup> Bluetooth 5/BLE Digital-Intensive Transceiver with a 2.3mW Phase-Tracking RX Utilizing a Hybrid Loop Filter for Interference Resilience in 40nm CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, vol. 61, Feb. 2018, pp. 446–448.

- [3] Y.-H. Liu, C. Bachmann, X. Wang, Y. Zhang, A. Ba, B. Busze, M. Ding, P. Harpe, G.-J. van Schaik, G. Selimis, H. Giesen, J. Gloudemans, A. Sbai, L. Huang, H. Kato, G. Dolmans, K. Philips, and H. de Groot, "A 3.7mW-RX 4.4mW-TX Fully Integrated Bluetooth Low-Energy/IEEE802.15.4/Proprietary SoC with an ADPLL-Based Fast Frequency Offset Compensation in 40nm CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, Feb. 2015, pp. 236–237.

- [4] Y.-H. Liu, V. K. Purushothaman, C. Lu, J. Dijkhuis, R. B. Staszewski, C. Bachmann, and K. Philips, "A 770pJ/b 0.85V 0.3mm<sup>2</sup> DCO-Based Phase-Tracking RX Featuring Direct Demodulation and Data-Aided Carrier Tracking for IoT Applications," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, vol. 60, pp. 408–409, 2017.

- [5] A. H. M. Shirazi, H. M. Lavasani, M. Sharifzadeh, Y. Rajavi, S. Mirabbasi, and M. Taghivand, "A 980µW 5.2dB-NF Current-Reused Direct-Conversion Bluetooth-Low-Energy Receiver in 40nm CMOS," in *IEEE Cust. Integr. Circuits Conf.*, Apr. 2017.

- [6] Y.-H. Liu, X. Huang, M. Vidojkovic, A. Ba, P. Harpe, G. Dolmans, and H. de Groot, "A 1.9nJ/b 2.4GHz Multistandard (Bluetooth Low Energy/Zigbee/IEEE802.15.6) Transceiver for Personal/Body-Area Networks," in *EEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, Feb. 2013, pp. 446–447.

- [7] Z. Lin, P. I. Mak, and R. P. Martins, "A 1.7mW 0.22mm<sup>2</sup> 2.4GHz ZigBee RX Exploiting a Current-Reuse Blixer + Hybrid Filter Topology in 65nm CMOS," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, pp. 448–449, 2013.

- [8] F.-W. Kuo, S. Binsfeld Ferreira, H.-N. R. Chen, L.-C. Cho, C.-P. Jou, F.-L. Hsueh, I. Madadi, M. Tohidian, M. Shahmohammadi, M. Babaie, and R. B. Staszewski, "A Bluetooth Low-Energy Transceiver With 3.7-mW All-Digital Transmitter, 2.75-mW High-IF Discrete-Time Receiver, and TX/RX Switchable On-Chip Matching Network," *IEEE J. Solid-State Circuits*, vol. 52, no. 4, pp. 1144–1162, Apr. 2017.

- [9] M. Tamura, H. Takano, S. Shinke, H. Fujita, H. Nakahara, N. Suzuki, Y. Nakada, Y. Shinohe, S. Etou, T. Fujiwara, and Y. Katayama, "A 0.5V BLE Transceiver with a 1.9mW RX Achieving -96.4dBm Sensitivity and 4.1dB Adjacent Channel Rejection at 1MHz Offset in 22nm FDSOI," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, vol. 63, Feb. 2020, pp. 468–469.

- [10] M. Silva-Pereira, J. T. de Sousa, J. Costa Freire, and J. Caldinhas Vaz, "A 1.7-mW -92-dBm Sensitivity Low-IF Receiver in 0.13-μm CMOS for Bluetooth LE Applications," *IEEE Trans. Microw. Theory Tech.*, vol. 67, no. 1, pp. 332–346, Jan. 2019.

- [11] B. J. Thijssen, E. A. M. Klumperink, P. Quinlan, and B. Nauta, "A 370μW 5.5dB-NF BLE/BT5.0/IEEE 802.15.4-Compliant Receiver with >63dB Adjacent Channel Rejection at >2 Channels Offset in 22nm FDSOI," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, Feb. 2020, pp. 467–468.

- [12] D. Shaeffer and T. Lee, "A 1.5-V, 1.5-GHz CMOS Low Noise Amplifier," *IEEE J. Solid-State Circuits*, vol. 32, no. 5, pp. 745–759, May 1997.

- [13] B. Razavi, RF Microelectronics, 2nd ed. Pearson ductation, 2013.

- [14] F. Gatta, E. Sacchi, F. Svelto, P. Vilmercati, and R. Castello, "A 2-dB Noise Figure 900-MHz Differential CMOS LNA," *IEEE J. Solid-State Circuits*, vol. 36, no. 10, pp. 1444–1452, 2001.

- [15] Z. Jiang, D. A. Johns, and A. Liscidini, "A Low-Power sub-GHz RF Receiver Front-End with Enhanced Blocker Tolerance," in *IEEE Cust. Integr. Circuits Conf.*, Apr. 2018, pp. 1–4.

- [16] K. Xu, J. Yin, P.-I. Mak, R. B. Staszewski, and R. P. Martins, "A Single-Pin Antenna Interface RF Front End Using a Single-MOS DCO-PA and a Push-Pull LNA," *IEEE J. Solid-State Circuits*, vol. 55, no. 8, pp. 2055– 2068, 2020.

- [17] A. Ba, K. Salimi, P. Mateman, P. Boer, J. van den Heuvel, J. Gloudemans, J. Dijkhuis, M. Ding, Y.-h. Liu, C. Bachmann, G. Dolmans, and K. Philips, "A 4mW-RX 7mW-TX IEEE 802.11ah Fully-Integrated RF Transceiver," in *IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2017, pp. 232–235.

- [18] E. Bechthum, J. Dijkhuis, M. Ding, Y. He, J. V. D. Heuvel, P. Mateman, G.-j. V. Schaik, K. Shibata, M. Song, E. Tiurin, S. Traferro, Y.-H. Liu, and C. Bachmann, "A Low-Power BLE Transceiver with Support for Phase-Based Ranging, Featuring 5μs PLL Locking Time and 5.3ms Ranging Time, Enabled by Staircase-Chirp PLL with Stick-Lock Channel-Switching," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, pp. 470–471, 2020.

- [19] D. Murphy, A. Hafez, A. Mirzaei, M. Mikhemar, H. Darabi, M. C. F. Chang, and A. Abidi, "A Blocker-Tolerant Wideband Noise-Cancelling Receiver with a 2dB Noise Figure," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, vol. 55, pp. 74–75, 2012.

- [20] D. Murphy, H. Darabi, A. Abidi, A. A. Hafez, A. Mirzaei, M. Mikhemar, and M.-C. F. Chang, "A Blocker-Tolerant, Noise-Cancelling Receiver Suitable for Wideband Wireless Applications," *IEEE J. Solid-State Circuits*, vol. 47, no. 12, pp. 2943–2963, Dec. 2012.

- [21] Z. Ru, N. Moseley, E. A. Klumperink, and B. Nauta, "Digitally Enhanced Software-Defined Radio Receiver Robust to Out-of-Band Interference," *IEEE J. Solid-State Circuits*, vol. 44, no. 12, pp. 3359– 3375, Dec. 2009.

- [22] A. Ghaffari, E. A. M. Klumperink, M. C. M. Soer, and B. Nauta, "Tunable High-Q N-Path Band-Pass Filters: Modeling and Verification," *IEEE J. Solid-State Circuits*, vol. 46, no. 5, pp. 998–1010, May 2011.

- [23] B. Razavi, K. F. Lee, and R. H. Yan, "Design of High-Speed, Low-Power Frequency Dividers and Phase-Locked Loops in Deep Submicron CMOS," *IEEE J. Solid-State Circuits*, vol. 30, no. 2, pp. 101–109, 1995.

- [24] I. Fabiano, M. Sosio, A. Liscidini, and R. Castello, "SAW-Less Analog Front-End Receivers for TDD and FDD," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3067–3079, Dec. 2013.

- [25] B. van Liempd, J. Borremans, E. Martens, S. Cha, H. Suys, B. Verbruggen, and J. Craninckx, "A 0.9 V 0.46 GHz Harmonic Recombination SDR Receiver in 28 nm CMOS With HR3/HR5 and IIP2 Calibration," *IEEE J. Solid-State Circuits*, vol. 49, no. 8, pp. 1815–1826, Aug. 2014.

- [26] M. C. M. Soer, E. A. M. Klumperink, D.-J. van den Broek, B. Nauta, and F. E. van Vliet, "Beamformer With Constant-Gm Vector Modulators and Its Spatial Intermodulation Distortion," *IEEE J. Solid-State Circuits*, vol. 52, no. 3, pp. 735–746, Mar. 2017.

- [27] B. J. Thijssen, E. A. M. Klumperink, P. Quinlan, and B. Nauta, "A 0.063.4-MHz 92-μW Analog FIR Channel Selection Filter With Very Sharp Transition Band for IoT Receivers," *IEEE Solid-State Circuits Lett.*, vol. 2, no. 9, pp. 171–174, 2019.

- [28] —, "Low-Power Highly-Selective Channel Filtering Using a Transconductor-Capacitor Analog FIR," *IEEE J. Solid-State Circuits*, vol. 55, no. 7, pp. 1785–1795, 2020.

- [29] Y. C. Lien, E. A. Klumperink, B. Tenbroek, J. Strange, and B. Nauta, "Enhanced-Selectivity High-Linearity Low-Noise Mixer-First Receiver with Complex Pole Pair Due to Capacitive Positive Feedback," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1348–1360, 2018.

- [30] H. Wu, M. Mikhemar, D. Murphy, H. Darabi, and M.-C. F. Chang, "A Blocker-Tolerant Inductor-Less Wideband Receiver With Phase and Thermal Noise Cancellation," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 2948–2964, Dec. 2015.

- [31] D. Murphy and H. Darabi, "A Complementary VCO for IoE that Achieves a 195dBc/Hz FOM and Flicker Noise Corner of 200kHz," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, vol. 59, Jan. 2016, pp. 44–45.

- [32] Y. He, Y.-H. Liu, T. Kuramochi, J. van den Heuvel, B. Busze, N. Markulic, C. Bachmann, and K. Philips, "A 673µW 1.8-to-2.5GHz Dividerless Fractional-N Digital PLL with an Inherent Frequency-Capture Capability and a Phase-Dithering Spur Mitigation for IoT Applications," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, Feb. 2017, pp. 420–421.

- [33] H. S. Bindra, A.-J. Annema, S. M. Louwsma, E. J. M. van Tuijl, and B. Nauta, "An energy reduced sampling technique applied to a 10b 1MS/s SAR ADC," in *IEEE Eur. Solid State Circuits Conf.*, Sep. 2017, pp. 235–238.

Eric A.M. Klumperink (M'98-SM'06) was born on April 4th, 1960, in Lichtenvoorde, The Netherlands. He received the B.Sc. degree from HTS, Enschede (1982), worked in industry on digital hardware and software, and then joined the University of Twente, Enschede, in 1984, shifting focus to analog CMOS circuit research. This resulted in several publications and his Ph.D. thesis "Transconductance Based CMOS Circuits: Circuit Generation, Classification and Analysis" (1997).

In 1998, Eric started as Assistant Professor at the IC-Design Laboratory in Twente and shifted research focus to RF CMOS circuits (e.g. sabbatical at the Ruhr Universitaet in Bochum, Germany). Since 2006, he is an Associate Professor, teaching Analog & RF IC Electronics and guiding PhD and MSc projects related to RF CMOS circuit design with focus on Software Defined Radio, Cognitive Radio and Beamforming. He served as an Associate Editor for the IEEE TCAS-II (2006-2007), IEEE TCAS-I (2008-2009) and the IEEE JSSC (2010-2014), as IEEE SSC Distinguished Lecturer (2014/2015), and as member of the technical program committees of ISSCC (2011-2016) and the IEEE RFIC Symposium (2011-..). He holds several patents, authored and co-authored 175+ internationally refereed journal and conference papers, and was recognized as 20+ ISSCC paper contributor over 1954-2013. He is a co-recipient of the ISSCC 2002 and the ISSCC 2009 "Van Vessem Outstanding Paper Award".

**Bart J. Thijssen** (S'16) was born in Ede, The Netherlands, in 1992. He obtained the B.Sc. degree (*cum laude*) in advanced technology and M.Sc. degree (*cum laude*) in electrical engineering from the University of Twente, Enschede, The Netherlands, in 2014 and 2016, respectively.

From 2016 to 2020, he worked as a Ph.D. Candidate with the ICD-Group at the University of Twente, investigating ultra-low power receivers. In 2020, he joined imec the Netherlands starting as Researcher, where he is developing ultra low power

transceivers for IoT. His current research interests include digitally inspired analog filters, low power and high-end radios, and radar systems. He has authored 5 technical journal and conference papers and holds 1 granted patent. Bart Thijssen is recipient of the "Analog Devices Outstanding Student Designer Award".

**Philip Quinlan** obtained a B.Eng. in Electronic Engineering and an M.Eng. in Computer Science from the University of Limerick in 1983 and 1994 respectively. From 1983-1998 he worked in Analog Devices, Limerick, Ireland on the design of mixed-signal CMOS products for Hard Disk-Drive (HDD) Servo and Read Channels. In 1998 he joined ST Microelectronics, Longmont, Colorado, USA where he worked on the development of PRML Read-Channel technology.

In 2001, he joined Analog Devices, Cork, Ireland, where he led a design team on the development of a family of highperformance, low-power Transceiver products. Since 2015 he has been a Technology Director at Analog Devices, working on the development of advanced ultra-low-power Radio Technologies. His interests include the design of low-power analog CMOS circuits and signal-processing techniques employed in Wireless Digital Communication Channels. He has authored or co-authored 15 technical journal and conference papers and holds 16 granted US patents.

**Bram Nauta** (S'89-M'91-SM'03-F'08) was born in 1964 in Hengelo, The Netherlands. In 1987 he received the M.Sc degree (*cum laude*) in electrical engineering from the University of Twente, Enschede, The Netherlands. In 1991 he received the Ph.D. degree from the same university on the subject of analog CMOS filters for very high frequencies. In 1991 he joined the Mixed-Signal Circuits and Systems Department of Philips Research, Eindhoven the Netherlands. In 1998 he returned to the University of Twente, where he is currently a distinguished

professor, heading the IC Design group. Since 2016 he also serves as chair of the EE department at this university. His current research interest is highspeed analog CMOS circuits, software defined radio, cognitive radio and beamforming.

He served as the Editor-in-Chief (2007-2010) of the IEEE Journal of Solid-State Circuits (JSSC), and was the 2013 program chair of the International Solid State Circuits Conference (ISSCC). He served as the President of the IEEE Solid-State Circuits Society (2018-2019 term).

Also, he served as Associate Editor of IEEE Transactions on Circuits and Systems II (1997-1999), and of JSSC (2001-2006). He was in the Technical Program Committee of the Symposium on VLSI circuits (2009-2013) and is in the steering committee and programme committee of the European Solid State Circuit Conference (ESSCIRC). He served as distinguished lecturer of the IEEE, is co-recipient of the ISSCC 2002 and 2009 "Van Vessem Outstanding Paper Award" and in 2014 he received the "Simon Stevin Meester" award ( $500.000 \in$ ), the largest Dutch national prize for achievements in technical sciences. He is fellow of the IEEE and member of the Royal Netherlands Academy of Arts and Sciences (KNAW).