Received 4 March 2019; revised 9 April 2019; accepted 23 April 2019. Date of publication 1 May 2019; date of current version 17 May 2019. The review of this paper was arranged by Editor M. Liu.

Digital Object Identifier 10.1109/JEDS.2019.2913426

# 2-Bit/Cell Operation of Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> Based FeFET Memory Devices for NAND Applications

# BINJIAN ZENG<sup>®</sup>, MIN LIAO<sup>®</sup>, QIANGXIANG PENG<sup>®</sup>, WENWU XIAO<sup>®</sup>, JIAJIA LIAO<sup>®</sup>, SHUAIZHI ZHENG<sup>®</sup>, AND YICHUN ZHOU

Key Laboratory of Low Dimensional Materials and Application Technology of Ministry of Education, School of Materials Science and Engineering, Xiangtan University, Xiangtan 411105, China

CORRESPONDING AUTHORS: M. LIAO AND Y. C. ZHOU (e-mail: mliao@xtu.edu.cn; zhouyc@xtu.edu.cn)

This work was supported in part by the National Natural Science Foundation of China under Grant 51702273 and Grant 61504115, in part by the "Huxiang Young Talents Plan" Project of Hunan Province under Grant 2018RS3087, and in part by the Science and Technology Innovation Project of Hunan Province under Grant 2017XK2048.

**ABSTRACT** The multilevel memory performances of ferroelectric field effect transistor (FeFET) with  $Hf_{0.5}Zr_{0.5}O_2$  (HZO) ferroelectric thin film are investigated. First, similar retention characteristics are observed for intermediate and saturated polarization states of HZO ferroelectric thin film, which enables memories for multi-bit data storage. And then, 2-bit/cell operation of HZO-based FeFET is demonstrated utilizing two NAND architecture compatible write schemes of varying program pulse amplitude and width. Low cycle-to-cycle variability, long retention to extrapolation of 10 years at 85°C, and endurance of 500 cycles are achieved for the both schemes. Moreover, the mechanism for multilevel memory operations of the FeFET is illustrated based on the polarization switching dynamics of HZO ferroelectric thin film.

**INDEX TERMS** FeFET memory,  $Hf_{0.5}Zr_{0.5}O_2$ , 2-bit/cell, write schemes, retention, endurance.

### I. INTRODUCTION

Hafnium oxide (HfO<sub>2</sub>) based ferroelectric field effect transistor (FeFET) memory is a promising contender among the emerging non-volatile memories for mass storage applications, with the sign of excellent process compatibility, low power, fast speed and Flash-like structure [1]-[3]. Fascinatingly, it could make use of existing NAND Flash manufacturing environments, such as memory array and integration technologies. Moreover, it was demonstrated that HfO<sub>2</sub> based 3D-FeFET memory could address most issues of 3D NAND Flash for aggressively scaling and allow for a longer scaling path, thereby becoming remarkably attractive for mass storage applications [4]. On the other hand, multilevel memory cell technology is an effective way for low cost, high density memory applications, which has been intensively developed along with the evolution of NAND Flash integration technologies [5]. Thus, it is imperative to explore the multilevel memory performances of HfO2 based FeFET memory devices for NAND applications.

Recently, the multilevel behaviors in the  $HfO_2$  based FeFETs have been reported by some researchers, and they

were harnessed to mimic brain synapses for neuromorphic applications [6]–[10]. For example, a 32-state (5-bit)  $Hf_{0.5}Zr_{0.5}O_2$  (HZO) based FeFET synapse with symmetric potentiation and depression characteristics was demonstrated based on the voltage-controlled partial polarization switching dynamics [9]. Moreover, it has been revealed that the multilevel capability of the  $HfO_2$  based FeFET devices is driven by the gradual polarization switching behaviors of  $HfO_2$  based ferroelectric thin film. However, the critical memory characteristics (i.e., write variability, endurance and retention) of the multilevel  $HfO_2$  based FeFETs were seldom investigated. Especially, the systematical studies on the stability of the subloop operations (i.e., intermediate polarization states) for the FeFETs are required.

Among the  $HfO_2$  based ferroelectric thin films, HZO is widely used for device applications [1], [2], [7]–[13], which can be realized more easily in mass production due to homogenously and reproducibly doping [14]. In this work, memory characteristics of the 2-bit/cell (the common multilevel memory cell) HZO based FeFET memory are systematically investigated utilizing two NAND architecture compatible write schemes.

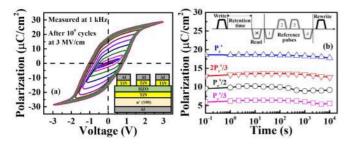

**FIGURE 1.** (a) *P-V* hysteresis loops for MFM capacitors. (b) Retention properties of various polarization states of MFM capacitors including saturated polarization ( $P_r^s$ ) and intermediate polarization states ( $P_r^s/3$ ,  $P_r^s/2$ ,  $2P_r^s/3$ ).

### **II. EXPERIMENTS**

Metal-ferroelectric-metal (MFM) capacitors were prepared by deposition of a Al/TiN/HZO/TiN film stack on  $n^+$ -Si(100) substrates. A 10-nm-thick HZO layer was formed by alternately depositing HfO<sub>2</sub> and ZrO<sub>2</sub> layer through ALD process. For crystallization, annealing was performed at 600°C for 30 sec in N<sub>2</sub> following the formation of TiN top electrodes. The n-channel FeFETs with an Al/TiN/HZO/SiO<sub>2</sub>/Si gate stack were fabricated using a gate last process. Following the formation of source (S)/drain (D), a 3-nm-thick SiO<sub>2</sub> buffer layer was grown on the chemically cleaned active area by dry oxidation. Afterward, the TiN/HZO film stack was deposited and annealed utilizing the same process for MFM capacitors. Finally, after opening contact holes at S/D region, the contact was formed by Al metal deposition, patterning, and annealing at 400°C.

#### **III. RESULTS AND DISCUSSION**

Polarization hysteresis (P-V) loops of an MFM capacitor are shown in Fig. 1(a), where the inset is a schematic of the MFM. Initially, the wake-up process was carried out by cycling the MFM capacitor with alternating switching pulses at  $\pm 3$  MV/cm (10 kHz) for  $1 \times 10^5$  cycles. After wake-up cycling, a characteristic transformation from a linear-loop behavior to sub-loop behaviors and a well saturated ferroelectric hysteresis is observed when increasing the applied voltage from 0.2 to 3 V, which indicates the coexistence of multi domains and the possibility of multilevel polarization applications [7]. The remanent polarization  $(P_r)$  at saturated state  $(P_r^s)$  is 18.6  $\mu$ C/cm<sup>2</sup> and coercive electric field  $(E_c)$ is 0.95 MV/cm. Moreover, the retention properties are characterized. The inset of Fig. 1(b) shows the pulse sequence for retention measurement, where the write pulse is used to establish a defined polarization state and the five pulses ( $\times$ , 1, 2, 3, and 4) are used to read the absolute value of the polarization after a certain retention time [15]. As shown in Fig. 1(b), the four polarization states  $(P_r^s, 2P_r^s/3, P_r^s/2)$ and  $P_r^{s/3}$  are very stable, with 4.3%, 2.3%, 4.2% and 6.6% polarization loss after 10<sup>4</sup> s for  $P_r^s$ ,  $2P_r^s/3$ ,  $P_r^s/2$  and  $P_r^s/3$ , respectively. The remarkable stability of these intermediate polarization states is similar to that of P(VDF-TrFE) and PZT based MFM capacitors [16], which might originate from the

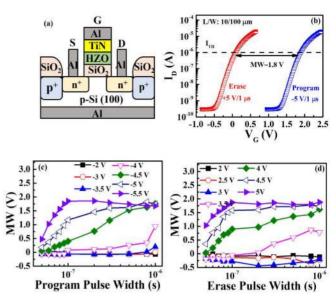

**FIGURE 2.** (a) Schematic of the fabricated FeFET. (b)  $I_D - V_G$  characteristics of a FeFET after an erase pulse (+5 V/1  $\mu$ s) and a program pulse (-5 V/1  $\mu$ s). (c) and (d) are the *MW* of the studied FeFET as a function of program and erase pulse width for varying pulse amplitudes, respectively.

coexistence of effectively independent domains, with different polarizations due to different values of the coercive field. Thus, the stable retention properties of intermediate and saturated polarization states in the HZO thin film demonstrate its ability for multi-bit data storage.

Fig. 2(a) shows a schematic of the fabricated HZO based FeFETs, which has a gate length (L) and width (W) of 10 µm and 100 µm, respectively. Fig. 2(b) shows the transfer characteristics ( $I_D - V_G$  curves) responding to a 1-µs -/+5-V program (Prg)/erase (Ers) pulse of a fabricated FeFET. Clearly, the shift of  $I_D - V_G$  curves opposite to the polarity of the applied pulses is induced, indicating that the hysteresis is originated from polarization switching of HZO ferroelectric thin film. The hysteresis width of the FeFET known as memory window (MW) is defined as the difference of threshold voltage  $(V_{TH})$  values between programed and erased states, where the  $V_{TH}$  can be determined as a gate voltage corresponding to a specified value of drain current  $(I_{TH})$  at  $10^{-7}$  A·W/L [17]. The large MW  $\sim 1.8$  V of the studied FeFET might be the largest one among the reported HfO2 based FeFETs [6]-[9], [18]-[20], which would be more practical to achieve more distinctly separate states compared with the previously announced results [6]-[9]. Moreover, detailed program/erase characteristics of the FeFET are elucidated for pulses with varying pulse width (50 ns-1 µs) and amplitude (2-5.5 V), shown in Figs. 2(c) and (d). Prior to each write pulse (Prg or Ers), the FeFET cell is set into an erased or programmed state by applying an initialization pulse of  $+5 \text{ V/1} \mu \text{s}$  or -5 V/1  $\mu$ s, respectively. One can see that no polarization reversal ( $MW \sim 0$ ) is detected up to 1 µs in the voltage range between -3 V and +3 V. When the absolute value of the

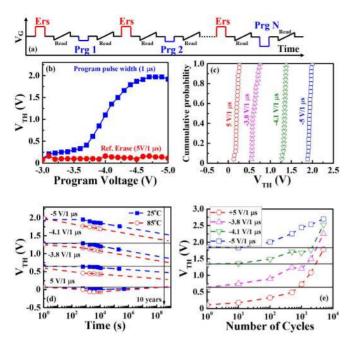

**FIGURE 3.** (a)  $V_G$  waveform scheme for varying program voltage. (b)  $V_{TH}$  as a function of program voltage referring to erase operations. (c) Distribution of  $V_{TH}$  levels for repeated write operations. (d) Retention properties of the four  $V_{TH}$  states. (e) Endurance properties of the four  $V_{TH}$  states cycled at  $\pm 5$  V/1  $\mu$ s.

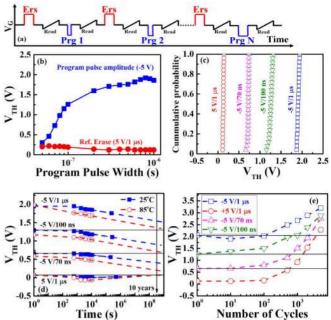

**FIGURE 4.** (a)  $V_G$  waveform scheme for varying program pulse width. (b)  $V_{TH}$  as a function of program pulse width referring to erase operations. (c) Distribution of  $V_{TH}$  levels for repeated write operations. (d) Retention properties of the four  $V_{TH}$  states. (e) Endurance properties of the four  $V_{TH}$  states cycled at ±5 V/1  $\mu$ s.

applied voltage is larger than 3 V, varying Prg/Ers pulse amplitude or width results in various *MW* values, which highly agrees with the general trend of polarization switching in ferroelectrics [21]. This behavior holds for multilevel operation of the FeFET device.

In NAND Flash applications, the conventional and incremental step pulse program (ISPP) schemes are based on varying program pulse width and amplitude, respectively [5]. Thus, the multi-bit memory operations of the studied FeFET are investigated with the two write schemes. First, the ISPP waveforms of  $V_G$  shown in Fig. 3(a) is adopted with increasing program pulse amplitude of 0.1 V/step. Fig. 3(b) shows gradual switching events as a function of program pulse amplitude. Four separate  $V_{TH}$  states are set by applying  $V_G$  pulses with -3.8 V/1  $\mu$ s, -4.1 V/1  $\mu$ s, -5 V/1  $\mu$ s, and +5 V/1  $\mu$ s, respectively. Fig. 3(c) shows the cumulative distributions of the corresponding four  $V_{TH}$  states by repeating write procedures for 25 times for each considered state, indicating a very low cycle-to-cycle variability. The solid and open symbols in Fig. 3(d) show that there is no significant degradation for the four  $V_{TH}$  states during retention measurements both at 25°C and 85°C. According to the read margins indicated by the black solid lines and symbol-dash lines, the states can be distinguished up to extrapolation of 10 years at both temperatures. Moreover, the remain read margins for 2-bit/cell operation of the studied FeFET are comparable to those for 1-bit/cell operation of the previously reported HZO based FeFET [18], which are contributed by the large MW and stable intermediate polarizations. In addition, Fig. 3(e) shows the evolution of the four  $V_{TH}$  states over cycling. The MW between Prg  $(-5 \text{ V/1} \mu \text{s})$  and Ers  $(+5 \text{ V/1} \mu \text{s})$  degrades after 5000 alternating Prg  $(-5 \text{ V/1 } \mu \text{s})$  and Ers  $(+5 \text{ V/1 } \mu \text{s})$  cycles, which is mainly caused by oxide charge trapping and interface trap generation [22]–[24]. The four  $V_{TH}$  states remain separated up to 5000 cycles and can be sensed after 500 cycles according to the read margins. The strategies of reducing the interfacial field stress and heating techniques for damage recovery can be utilized to improve the endurance limitations [25], [26]. On the other hand, the 2-bit/cell operation is demonstrated by varying program pulse width, which is schematically shown in Fig. 4(a). As shown in Fig. 4(b), consecutive  $V_{TH}$  values are obtained by increasing program pulse width from 50 ns to 1  $\mu$ s at -5 V. Similar to ISPP scheme, low cycle-to-cycle variability, long retention to extrapolation of 10 years at 85°C, and endurance of 500 cycles of four separate  $V_{TH}$  states realized by +5 V/1  $\mu$ s, -5 V/70 ns, -5 V/100 ns and -5 V/1  $\mu$ s can be seen in Figs. 4(c), (d), and (e), respectively.

Note that the polarization reversal of HZO ferroelectric thin film and other  $HfO_2$  based ferroelectric thin films follows the nucleation limited switching (NLS) model [27]–[29]. Primarily, the polarization reversal was considered as an ensemble of elementary regions that switch independently with a distribution of switching times. This distribution of switching times was attributed to variations in local electric fields when a uniform external field is applied,

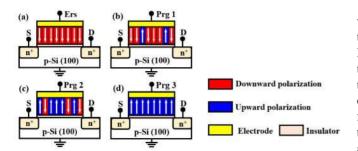

**FIGURE 5.** (a)-(d) are schematics for four  $V_{TH}$  states of FeFET with saturated downward polarization (Ers), intermediate polarizations including a few (Prg 1) and more (Prg 2) upward domains among downward domains, and saturated upward polarization (Prg 3), respectively.

due to impurities or crystal defects. Generally, the characteristic switching time  $\tau$  (i.e., the unique waiting time for domain nucleation of elementary regions) is expressed as [27]

$$\tau(E_a, E) = \tau_{\infty} exp\left\{ \left(\frac{E_a}{E}\right)^a \right\}$$

(1)

where  $E_a$  is the activation field,  $\tau_{\infty}$  is the time constant obtained for an infinite applied field, and a is an empirical parameter ( $\geq$  1). The value of local electrical field E can be obtained by  $E = \eta E_{ext}$ , here  $E_{ext}$  is the applied external field and  $\eta$  is a random variable with probability density function (PDF)  $f(\eta)$ . Accordingly, the mechanism of write operation corresponding to 2-bit/cell in FeFET memory could be schematically depicted as Fig. 5, where the domains only with upward or downward polarization are considered. At the beginning, all the domains are assumed to be downward as shown in Fig. 5 (a), because the positive  $V_G$  pulse  $(+5 \text{ V/1 } \mu \text{s})$  is high enough. As for ISPP scheme, when the amplitude of negative  $V_G$  pulse increases from -3 V to -5 V, the relative value of local electrical field E increases, and the characteristic switching time  $\tau$  decreases based on Eq. (1). Since the downward domains exceeding the local characteristic switching time in the HZO film will switch to upward, the proportion of upward domains increases with increasing the pulse amplitude. Besides, for the scheme of varying the  $V_G$  pulse width, the characteristic switching time  $\tau$  follows the probability density function f( $\eta$ ) due to the constant  $E_{ext}$ . The proportion of downward domains induced to reversal also will increase with increasing the pulse width from 50 ns to 1 µs. The behavior for a few downward domains reversal realized by the two schemes  $(-3.8 \text{ V/1} \mu\text{s},$ -5 V/70 ns) is schematically shown in Fig. 5 (b), and that for more downward domains reversal induced by the two schemes (-4.1 V/1  $\mu$ s, -5 V/100 ns) is shown in Fig. 5 (c). Fig. 5 (d) represents the completely reversal of domains from downward to upward realized by the relatively high negative  $V_G$  pulse amplitude or width (-5 V/1  $\mu$ s). In a word, various ratios of upward and downward domain achieved by varying pulse amplitude or width produce different net values of polarization or  $E_c$  responsible for  $V_{TH}$ ,

which favors multilevel operation of the FeFET. Moreover, the coexistence of effectively independent domains in the HZO film contributes to the stability of the multi-states in the HZO based FeFET device [16], [30]. On the basis of the above-mentioned mechanism, the uniform coexistence of multi domains in the gate region ( $W \times L$ ) is necessary for multilevel memory applications. Because of the spatial distribution of dielectric and ferroelectric grains as well as the grain size distribution, the variability from cell to cell would be prohibitive for the reliable operation when scaling the gate dimension of FeFET. To implement highly scaled multilevel FeFET memory device, in addition to the film engineering [30], nonplanar configurations might be the candidates due to the large effective W, such as FinFET devices [10] or 3-D memory array architectures [31].

## **IV. CONCLUSION**

The 2-bit/cell operation in HZO based FeFET memory device for NAND architecture applications was demonstrated. Our results show that the stable retention of intermediate polarization states in the HZO ferroelectric thin film enables its memories for multi-bit data storage. Moreover, 2-bit/cell operation of HZO-based FeFET with low cycle-to-cycle variability, long retention to extrapolation of 10 years at 85°C, and endurance of 500 cycles were achieved utilizing two NAND architecture compatible write schemes. The operation principle of 2-bit/cell HZO based FeFET is based on the polarization reversal of HZO ferroelectric thin film following nucleation limited switching model. But further studies are required for practical engineering applications, such as enlarging the memory window, controlling device-to-device variability, improving the endurance, etc.

#### REFERENCES

- C.-H. Cheng and A. Chin, "Low-leakage-current DRAM-like memory using a one-transistor ferroelectric MOSFET with a Hf-based gate dielectric," *IEEE Electron Device Lett.*, vol. 35, no. 1, pp. 138–140, Jan. 2014.

- [2] Y.-C. Chiu *et al.*, "Low power 1T DRAM/NVM versatile memory featuring steep sub-60-mV/decade operation, fast 20-ns speed, and robust 85°C-extrapolated 10<sup>16</sup> endurance," in *Proc. Symp. VLSI Tech.*, Kyoto, Japan, Jun. 2015, pp. T184–T185.

- [3] International Roadmap for Devices and Systems (IRDS) 2017 Edition. [Online]. Available: https://irds.ieee.org/

- [4] J. Van Houdt, "3D memories and ferroelectrics," in Proc. IEEE Int. Memory Workshop, Monterey, CA, USA, May 2017, pp. 1–3.

- [5] S. Aritome, NAND Flash Memory Technologies. New York, NY, USA: Wiley, 2015, pp. 93–97.

- [6] H. Mulaosmanovic *et al.*, "Novel ferroelectric FET based synapse for neuromorphic systems," in *Proc. Symp. VLSI (VLSIT)*, Kyoto, Japan, Jun. 2017, pp. T176–T177.

- [7] S. Oh *et al.*, "HfZrO<sub>x</sub>-based ferroelectric synapse device with 32 levels of conductance states for neuromorphic applications," *IEEE Electron Device Lett.*, vol. 38, no. 6, pp. 732–735, Jun. 2017.

- [8] M. Jerry *et al.*, "Ferroelectric FET analog synapse for acceleration of deep neural network training," in *IEDM Tech. Dig.*, Dec. 2017, pp. 6.2.1–6.2.4.

- [9] M. Jerry et al., "A ferroelectric field effect transistor based synaptic weight cell," J. Phys. D Appl. Phys., vol. 51, no. 43, pp. 434001-1–434001-7, Aug. 2018.

- [10] M. Seo *et al.*, "First demonstration of a logic-process compatible junctionless ferroelectric FinFET synapse for neuromorphic applications," *IEEE Electron Device Lett.*, vol. 39, no. 9, pp. 1445–1448, Sep. 2018.

- [11] J. Li *et al.*, "Negative capacitance Ge PFETs for performance improvement: Impact of thickness of HfZrO<sub>x</sub>," *IEEE Trans. Electron Devices*, vol. 65, no. 3, pp. 1217–1222, Mar. 2018.

- [12] J. R. Zhou et al., "Ferroelectric negative capacitance GeSn PFETs with sub-20 mV/decade subthreshold swing," *IEEE Electron Device Lett.*, vol. 38, no. 8, pp. 1157–1160, Aug. 2017.

- [13] J. R. Zhou *et al.*, "Ferroelectric HfZrO<sub>x</sub> Ge and GeSn PMOSFETs with sub-60 mV/decade subthreshold swing, negligible hysteresis, and improved I<sub>DS</sub>," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2016, pp. 310–313.

- [14] S. J. Kim *et al.*, "Ferroelectric Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> thin films: A review of recent advances," *JOM*, vol. 71, no. 1, pp. 246–255, Sep. 2019.

- [15] Manual for TF Analyzer 2000E With FE-Module. [Online]. Available: http://www.eng.auburn.edu/files/acad\_depts/matl/lab-manuels/ 153%20-%20Testing%20and%20Characterization%20Lab/manuals/ thin-film-analyzer-manual.pdf

- [16] D. Zhao *et al.*, "Retention of intermediate polarization states in ferroelectric materials enabling memories for multi-bit data storage," *Appl. Phys. Lett.*, vol. 108, no. 23, pp. 232907-1–232907-5, Jun. 2016.

- [17] A. Ortiz-Conde *et al.*, "A review of recent MOSFET threshold voltage extraction methods," *Microelectron. Rel.*, vol. 42, no. 4–5, pp. 583–596, Apr./May 2002.

- [18] K. Ni *et al.*, "Critical role of interlayer in Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> ferroelectric FET nonvolatile memory performance," *IEEE Trans. Electron Devices*, vol. 65, no. 6, pp. 2461–2469, Jun. 2018.

- [19] E. Yurchuk *et al.*, "Impact of scaling on the performance of HfO<sub>2</sub>based ferroelectric field effect transistors," *IEEE Trans. Electron Devices*, vol. 16, no. 11, pp. 3699–3706, Nov. 2014.

- [20] T. Ali et al., "Silicon doped hafnium oxide (HSO) and hafnium zirconium oxide (HZO) based FeFET: A material relation to device physics," *Appl. Phys. Lett.*, vol. 112, no. 22, pp. 222903-1–222903-5, Jun. 2018.

- [21] J. Müller et al., "Nanosecond polarization switching and long retention in a novel MFIS-FET based on ferroelectric HfO<sub>2</sub>," *IEEE Electron Device Lett.*, vol. 33, no. 29, pp. 185–187, Feb. 2012.

- [22] E. Yurchuk *et al.*, "Origin of the endurance degradation in the novel HfO<sub>2</sub>-based 1T ferroelectric non-volatile memories," in *Proc. IEEE IRPS*, Waikoloa, HI, USA, Jun. 2014, pp. 2E.5.1–2E.5.5.

- [23] N. Gong and T.-P. Ma, "A study of endurance issues in HfO<sub>2</sub>based ferroelectric field effect transistors: Charge trapping and trap generation," *IEEE Electron Device Lett.*, vol. 39, no. 1, pp. 15–18, Jan. 2018.

- [24] B. J. Zeng *et al.*, "Compatibility of HfN metal gate electrodes with Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> ferroelectric thin films for ferroelectric field-effect transistors," *IEEE Electron Device Lett.*, vol. 39, no. 10, pp. 1508–1511, Oct. 2018.

- [25] J. Muller et al., "High endurance strategies for hafnium oxide based ferroelectric field effect transistor," in Proc. 16th Non Volatile Memory Technol. Symp. (NVMTS), Pittsburgh, PA, USA, Oct. 2016, pp. 1–7.

- [26] H. Mulaosmanovic *et al.*, "Recovery of cycling endurance failure in ferroelectric FETs by self-heating," *IEEE Electron Device Lett.*, vol. 40, no. 2, pp. 216–219, Feb. 2019.

- [27] C. Alessandri et al., "Switching dynamics of ferroelectric Zr-doped HfO<sub>2</sub>," *IEEE Electron Device Lett.*, vol. 39, no. 11, pp. 1780–1783, Nov. 2018.

- [28] H. Mulaosmanovic *et al.*, "Switching kinetics in nanoscale hafnium oxide based ferroelectric field-effect transistors," ACS Appl. Mater. Interfaces, vol. 9, no.4, pp. 3792–3798, Jan. 2017.

- [29] N. Gong *et al.*, "Nucleation limited switching (NLS) model for HfO<sub>2</sub>based metal-ferroelectric-metal (MFM) capacitors: Switching kinetics and retention characteristics," *Appl. Phys. Lett.*, vol. 112, no. 26, pp. 262903-1–262903-5, Jun. 2018.

- [30] H. Mulaosmanovic *et al.*, "Evidence of single domain switching in hafnium oxide based FeFETs: Enabler for multi-level FeFET memory cells," in *IEDM Tech. Dig.*, Washington, DC, USA, Dec. 2015, pp. 26.8.1–26.8.3.

- [31] K. Florent *et al.*, "Vertical ferroelectric HfO<sub>2</sub> FET based on 3-D NAND architecture: Towards dense low-power memory," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2018, pp. 2.5.1–2.5.4.

**BINJIAN ZENG** received the B.S. degree in material forming and control engineering from the Changsha University of Science and Technology, Hunan, China, in 2013. He is currently pursuing the Ph.D. degree in materials science and engineering with Xiangtan University, mainly researching on the HfO<sub>2</sub>-based ferroelectric thin films and memory devices.

**MIN LIAO** received the B.S. degree in microelectronics and the M.E. degree in microelectronics and solid state electronics from Xiangtan University, China, in 2006 and 2009, respectively, and the Ph.D. degree in electronics and applied physics from the Interdisciplinary Graduate School of Science and Engineering, Tokyo Institute of Technology, Japan, in 2012, where he was a Post-Doctoral Researcher and an Assistant Professor from 2012 to 2016. He joined Xiangtan University, China, in 2016, where he is currently

a Professor with the School of Materials Science and Engineering. His research interests are in the areas of device physics and process technologies of ferroelectric thin films and their related devices.

**QIANGXIANG PENG** received the Ph.D. degree in microelectronics and solid-state electronics from the University of Electronics Science and Technology of China in 2014, where he researched on the pyroelectric material preparation and uncooled infrared detectors. In 2015, he joined Xiangtan University and has been researching on the ferroelectric materials and its integrated devices and processes. From 2016 to 2017, he was a Visiting Fellow with the Tokyo Institute of Technology, where he engaged in the fabrication and E-DAM encourses

of ferroelectric material and FeRAM processes.

**WENWU XIAO** received the B.Eng. degree from the Changsha University of Science and Technology, China. He is currently pursuing the Ph.D. degree with the School of Materials Science and Engineering, Xiangtan University, China. His research interests is in the area of hafnium oxidebased materials and devices.

**JIAJIA LIAO** received the B.S. degree from the School of Materials Science and Engineering, Xiangtan University, China, in 2015, where she is currently pursuing the M.D.-Ph.D. degree, mainly researching on the ferroelectric thin films and related memory devices.

**SHUAIZHI ZHENG** received the B.S. degree in chemistry and the M.S. degree in inorganic chemistry from Beijing Normal University, China, in 2005 and 2008, respectively, and the academic degree of Doctor of Natural Sciences from the Institute of Inorganic Chemistry I, Faculty of Natural Sciences, Ulm University, Germany, in 2014. She was a visiting student with Hokkaido University, Japan, in 2014. She joined Xiangtan University, China, in 2017, where she is currently a Lecturer with the School of Materials Science

and Engineering. Her research interests are in the areas of ferroelectric thin films and their related devices.

**YICHUN ZHOU** received the Ph.D. degree in basic mechanics from the Chinese Academy of Science, Beijing, China, in 1994. From 1999 to 2001, he was a Visiting Professor with Tohoku University, Sendai, Japan. He is currently a Professor with the School of Materials Science and Engineering, Xiangtan University, Xiangtan, China. His research interests include the growth of thin films, the switching properties of ferroelectric thin film, and the ferroelectric memory devices.