www.afm-journal.de

# ADVANCED FUNCTIONAL MATERIALS

### 3D Free-Form Patterning of Silicon by Ion Implantation, Silicon Deposition, and Selective Silicon Etching

Andreas C. Fischer, Lyubov M. Belova, Yuri G. M. Rikers, B. Gunnar Malm, Henry H. Radamson, Mohammadreza Kolahdouz, Kristinn B. Gylfason, Göran Stemme, and Frank Niklaus\*

A method for additive layer-by-layer fabrication of arbitrarily shaped 3D silicon micro- and nanostructures is reported. The fabrication is based on alternating steps of chemical vapor deposition of silicon and local implantation of gallium ions by focused ion beam (FIB) writing. In a final step, the defined 3D structures are formed by etching the silicon in potassium hydroxide (KOH), in which the local ion implantation provides the etching selectivity. The method is demonstrated by fabricating 3D structures made of two and three silicon layers, including suspended beams that are 40 nm thick, 500 nm wide, and 4  $\mu$ m long, and patterned lines that are 33 nm wide.

### 1. Introduction

Silicon (Si) is one of the most attractive materials for many micro- and nanoscale devices, due to its excellent mechanical, optical, and electrical properties.<sup>[1]</sup> Conventional Si machining techniques, including lithography and deep Si etching, allow cost-efficient implementation of simple suspended three dimensional (3D) Si structures. However, more complex 3D Si structures can only be implemented by using complicated fabrication schemes involving a multitude of different processes. Additive layer-by-layer manufacturing techniques for polymer and metal 3D structures are well established. In these techniques, the arbitrarily shaped 3D structures are formed by stacking patterned material layers on top of each other.<sup>[2–10]</sup> A

A. C. Fischer, Dr. K. B. Gylfason, Prof. G. Stemme, Prof. F. Niklaus KTH Royal Institute of Technology Microsystem Technology Laboratory 10044 Stockholm, Sweden E-mail: frank.niklaus@ee.kth.se Prof. L. M. Belova KTH Royal Institute of Technology Engineering Materials Physics Laboratory 10044 Stockholm, Sweden Dr. Y. G. M. Rikers **FEI Electron Optics** Achtseweg Noord 5, 5600 KA Eindhoven, The Netherlands Prof. B. G. Malm, Prof. H. H. Radamson, Dr. M. Kolahdouz KTH Royal Institute of Technology Integrated Devices and Circuits 16440 Kista, Sweden

comparable process that allows additive layer-by-layer fabrication of 3D Si structures could provide a wealth of opportunities for new types of nanophotonics, nano-electromechanical systems (NEMS) and micro-electromechanical systems (MEMS).

Existing additive layer-by-layer manufacturing techniques include stereolithography,<sup>[2,3]</sup> solid ground curing,<sup>[2]</sup> selective laser sintering,<sup>[2,7]</sup> 3D inkjet printing,<sup>[2]</sup> fused deposition modeling,<sup>[2,8–18]</sup> and laminated object modeling.<sup>[2,19,20]</sup> In stereolithography, solid ground curing, and

direct laser writing, 3D polymer structures are fabricated by locally exposing a photosensitive polymer with light, which allows subsequent selective dissolution of the polymer.<sup>[2-6]</sup> In 3D inkjet printing, and in some fused deposition modeling techniques, 3D structures are formed by printing functional inks, often in combination with supporting sacrificial inks that are subsequently selectively dissolved.<sup>[2,8]</sup> Typical materials used in these techniques include polymers, waxes, and inks filled with e.g. metal, carbon, or ceramics. Laser-beam,<sup>[11-13]</sup> focused ion-beam (FIB),<sup>[14–16]</sup> electron-beam,<sup>[14]</sup> and proton-beam<sup>[17,18]</sup> assisted deposition are other fused deposition modeling techniques for additive fabrication of 3D structures. Laser-assisted deposition has been demonstrated for the fabrication of 3D Si structures with dimensions in the range of tens of µm.<sup>[12,13]</sup> Focused ion-beam, electron-beam, and proton-beam assisted deposition methods can achieve structural dimensions of the order of a few tens of nm, but the fabrication of suspended Si structures has not been shown with these techniques. Layer-bylayer fabrication of 3D polycrystalline Si structures with dimensions below 1 µm has been demonstrated using conventional semiconductor manufacturing processes.<sup>[19,21]</sup> The applied processes are combinations of poly-crystalline Si deposition, SiO<sub>2</sub> deposition, photolithography, reactive ion etching, chemicalmechanical polishing (CMP), and selective etching of the sacrificial layer. These approaches require a large number of different process and photolithography steps that cannot be easily automated. Transfer printing of pre-patterned Si membranes (laminated object modeling) has been used to fabricate 3D Si structures with dimensions in the micrometer-range.<sup>[20,22]</sup> It is however difficult to efficiently automate these processes, and to achieve sub-micrometer alignment accuracies during lamination of the pre-patterned membranes.

4004

DOI: 10.1002/adfm.201200845

www.MaterialsViews.com

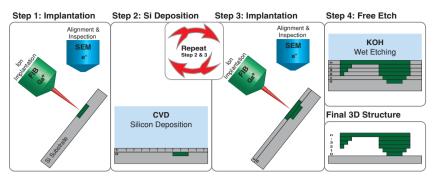

**Figure 1.** A schematic of the additive layer-by-layer fabrication process: Step 1: Local implantation of Ga<sup>+</sup> ions into a Si substrate surface using FIB writing. Step 2: CVD of a thin Si layer. Step 3: Local implantation of Ga<sup>+</sup> ions in the deposited Si layer using FIB writing. Steps 2 and 3 are repeated until the 3D structure is defined in the Si layers by the locally implanted Ga<sup>+</sup> ions. Step 4: Selective etching of the Si that contains no implanted Ga ions in KOH, to obtain the final 3D Si structure.

Here, we report a straightforward method for additive layerby-layer fabrication of arbitrarily shaped 3D Si micro- and nanostructures. The method is schematically illustrated in Figure 1, and consists of a cyclic process of defining a pattern with implanted gallium ions (Ga<sup>+</sup>) in a Si laver using FIB writing (Figure 1, Steps 1 and 3), followed by chemical vapor deposition of a 40-70 nm thick Si layer (Figure 1, Step 2). By repeating Steps 2 and 3, 3D structures are defined within the deposited Si layers. The local implantation of Ga<sup>+</sup> ions into Si results in an etch selectivity for potassium hydroxide (KOH) wet etching,<sup>[23-28]</sup> tetramethylammonium hydroxide (TMAH) wet etching,<sup>[29]</sup> and cryogenic reactive ion etching.<sup>[30-32]</sup> Etch selectivities of >1000 in KOH<sup>[28]</sup> and >2000 in TMAH<sup>[29]</sup> have been demonstrated. Thus, the defined 3D Si structures can be formed by selective freeetching, using one of these etches as a final patterning step (Figure 1, Step 4). In this work, free-etching in KOH was used. We demonstrate the feasibility of our method by fabricating 2- and 3-layer 3D structures, including suspended Si beams that are 40 nm thick, 500 nm wide, and up to 4 µm long. To

the best of our knowledge, this is the first demonstration of patterning 3D Si structures by additive layer-by-layer fabrication using a cyclic process combining chemical vapor deposition (CVD) of Si layers and local ion implantation by FIB writing with a final etch to form 3D Si structures. The process combines two mature and established fabrication methods: CVD, providing high-quality thin Si layers, and FIB implantation of Ga<sup>+</sup> ions in Si, capable of forming patterns with lateral dimensions of below 20 nm and typical implantation depths of 30-50 nm.<sup>[26]</sup> An important feature of the proposed additive layer-by-layer fabrication process is that it may be possible to implement Si CVD and FIB writing as switched processes in a single automated tool. Such a tool could enable "printing" of 3D Si microand nanostructures directly from 3D CAD models, without requiring a fully equipped

semiconductor clean-room. To increase throughput, highly parallel FIB writing with multi-ion-beam arrays may even be viable.<sup>[33]</sup>

UNCTIONAL

www.afm-iournal.de

### 2. Results and Discussion

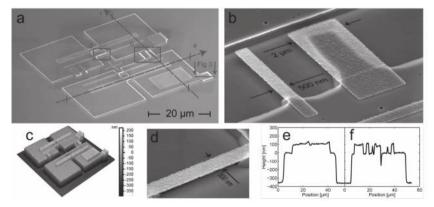

To demonstrate the method, both 2- and 3-layer 3D Si structures were fabricated. The 2-layer structures, shown in the scanning electron microscope (SEM) image in **Figure 2**a, have been fabricated by two Ga<sup>+</sup> ion implantation steps (10 pC/ $\mu$ m<sup>2</sup> dose) and one Si deposition step. The structures consist of four raised Si platforms, with cantilevers extending out from the platforms and doubly clamped Si beams that connect the platforms. In the experiments, the platforms

were defined in a (100) Si substrate (p-type, 0.005–0.020  $\Omega$ -cm) by Ga<sup>+</sup> ion implantation (Figure 1, Step 1). Thereafter, a layer of Si was grown on the wafer at a temperature of 635 °C (Figure 1, Step 2). Next, the beams were defined in the deposited Si layer by a second Ga<sup>+</sup> ion implantation (Figure 1, Step 3), followed by a 30 s rapid thermal anneal at 650 °C in an argon atmosphere. Finally, the non-implanted Si was selectively etched in a 30% solution of KOH for 8 min at 36 °C (Figure 1, Step 4). The resulting suspended beams have a width of 500 nm, a thickness of 40 nm, and a length of up to 4 µm. Indicated in Figure 2a are the enlarged areas shown in Figure 2b,d, the line height profiles of Figure 2e,f, and the cross section of Figure 3. Figure 2b is an enlarged view of two cantilever beams. The narrower beam is 500 nm wide, and the wider one 2 µm wide. The KOH has freed the narrow beam, while the wide beam is still supported. Given the high selectivity of the KOH etch (>1000), the wide beam could be freed by extending the etch time. The beams show no signs of stress, and are flat after the free-etch. Figure 2c shows the height profile of the complete structure, as measured by white light interferometry. Figure 2d is an

**Figure 2.** a) An SEM image of the fabricated 2-layer structures. Indicated in the image are the enlarged areas shown in (b,d), the line height profiles of (e,f), and the cross section used in Figure 3. b) An enlarged view of two cantilever beams. It is visible that the narrow beam is freeetched while the wide beam is still supported. c) The height profile of the complete structure, as measured with white light interferometry. d) An enlarged view of a doubly clamped beam. e) Height profile along a doubly clamped beam. f) Height profile along a cantilever beam.

##

\_Materials

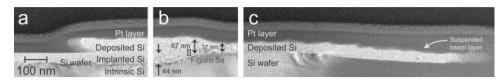

Figure 3. TEM cross sections at: a) the edge of the deposited and implanted beam layer; b) the edge of platform implantation. Indicated are the layer thicknesses and the area enlarged in Figure 5a; and c) the suspended deposited and implanted beam layer.

enlarged view of one of the free-etched doubly clamped beams of 500 nm width. The top surface of the patterned Si structures was profiled using atomic force microscopy (AFM). The root mean square (RMS) roughness of the measured  $3 \times 3 \ \mu m^2$  areas was 5.1 nm, which is sufficiently flat for many MEMS, NEMS, and optical applications.

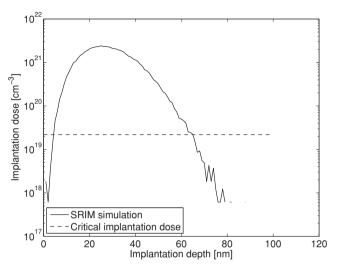

Figure 3 shows a transmission electron microscope (TEM) image of the laver stack along the cross-section indicated in Figure 2a. The three Si layers visible in Figure 3a are, from bottom to top, the intrinsic Si of the substrate, the implanted platform layer, and the grown and implanted beam layer. The platinum (Pt) protective layer was deposited locally via a combination of electron beam and ion beam induced deposition, during the TEM lamella preparation. By comparing, in Figure 3a, the surface level of the implanted platform region on the left to the level of the original wafer surface protected under the deposited layer on the right, we find that no more than a few nm of implanted silicon is removed during the KOH etch. Considering that 350 nm of non-implanted silicon is removed in the same etch step, we observe an etch selectivity in our process of at least the order of 100 between implanted and non-implanted regions. A slight under-etch of the deposited Si layer is visible, most likely due to incomplete penetration of the Ga+ ions through the layer. Figure 3b shows the cross-section at the edge of the platform implantation into the substrate. The thickness of the implanted layer in the platform area is 44 nm. The thickness of the layer deposited over the implanted platform region is 67 nm, and the thickness of the free-etched suspended layer deposited over the non-implanted region is 37 nm. The thickness of the free-etched suspended layer agrees reasonably well with the predictions of the TRIM simulation code.<sup>[34]</sup> A simulated 30 keV Ga<sup>+</sup> ion implantation into Si yields a mean implantation depth of 28 nm, and one standard deviation of ion distribution of 10 nm. For an implanted Ga<sup>+</sup> ion area dose of 10 pC/ $\mu$ m<sup>2</sup> (6 × 10<sup>15</sup> cm<sup>-2</sup>), the thickness of the layer receiving a volume dose above the critical value for achieving an etch selectivity in KOH  $(2.2 \times 10^{19} \text{ cm}^{-3})^{[27]}$  is 60 nm. Figure 4 shows the simulated implantation profile. The reason for the thinner than expected observed layer could be that diffusion of Ga<sup>+</sup> ions during annealing tends to dilute the ion concentration below the critical level in the interface facing non-implanted Si. The difference in thickness of the Si layer grown on implanted and non-implanted Si is the result of a difference in Si growth mechanism on the two regions. This effect is known from so called differential epitaxy, where the growth rates over different types of exposed surfaces vary significantly under identical conditions (gas flow, partial pressure, temperature), i.e., faster growth might occur on implanted regions as compared to non-implanted regions, where the surface is perfectly

**Figure 4.** The volume dose profile of a 30 keV Ga<sup>+</sup> ion implantation into Si at an area dose of 10 pC/µm<sup>2</sup> (6 × 10<sup>15</sup> cm<sup>-2</sup>), calculated with the TRIM simulation code.<sup>[34]</sup> The mean implantation depth is 28 nm, the standard deviation of ion distribution is 10 nm, and the dose is above the critical value for etch selectivity in KOH, which is  $2.2 \times 10^{19}$  cm<sup>-3</sup>, in a 60 nm thick layer.

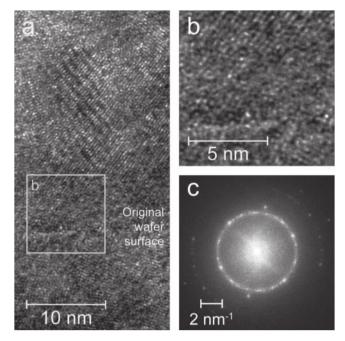

crystalline.<sup>[35,36]</sup> The gray rectangle in Figure 3b indicates the area enlarged in **Figure 5a**. Figure 3c shows the suspended beam layer embedded in the platinum cover layer. Figure 5a shows a high-resolution TEM image of the area indicated in Figure 3b, i.e., around the original wafer surface (shown in more detail in Figure 5b). Lattice fringes are clearly visible, indicating that both the implanted layer of the wafer and the deposited layer are polycrystalline with grains smaller than 10 nm. This is confirmed by the fast Fourier transform (FFT) analysis shown in Figure 5c. Amorphization of Si is a known result of FIB Ga<sup>+</sup> ion implantation,<sup>[37]</sup> and the subsequent annealing steps have caused re-crystallization of the amorphized Si to a polycrystal-line state.

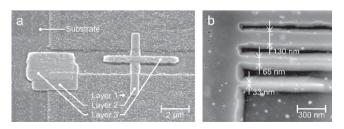

To demonstrate the feasibility of our fabrication method for multilayer 3D structures with more than one deposited Si layer, 3-layer structures have been fabricated. The 3-layer structures shown in **Figure 6**a were fabricated by three implantation steps and two Si deposition steps. The base substrate was a (100) Si substrate (p-type, 14–22  $\Omega$  cm) and the first layer was patterned in the Si substrate. Thereafter, two Si deposition steps with subsequent FIB implantation steps were performed. The same process sequence and parameters as for the 2-layer structures were used for the 3-layer structures, including wafer cleaning, rapid thermal anneals, FIB implantations, Si layer depositions,

www.MaterialsViews.com

**Figure 5.** a) A TEM image of the cross section of the layer stack at the edge of the platform implantation. b) An enlarged view of the interface between the original wafer surface and the deposited and implanted layer. c) FFT analysis of (a).

and the final KOH etch. The structures demonstrate all the different overlaps possible with three layers. To investigate the limits of the smallest feature size that can be implemented, resolution test structures with narrow line patterns were written in a deposited layer using the same procedure. Figure 6b shows the narrowest patterned Si lines that were resolved, which are as narrow as 33 nm. The sloped sidewalls that can be seen beneath the lines are indicative of preferential etching in different lattice directions, which is characteristic of KOH etching. The results from the resolution test structures clearly demonstrate the potential of this method for fabricating 3D Si devices with dimensions on the nm-scale.

### 3. Conclusions

A simple additive layer-by-layer method for the fabrication of arbitrarily shaped 3D Si micro- and nanostructures is reported.

Figure 6. a) An SEM image of 3-layer structures. b) An SEM image of lines of widths as small as 33 nm, patterned in a deposited layer.

The feasibility of the method is demonstrated by fabricating suspended Si beams with sub-micrometer dimensions, and patterned lines with dimensions on the nanometer scale, in 2and 3-layer processes. It may be possible to implement Si CVD and FIB writing as switched processes in a single automated tool, which could enable "printing" of 3D Si micro- and nanostructures directly from 3D CAD models. Thus, the proposed technology could change and greatly simplify the fabrication of many MEMS, NEMS and Si photonic devices, without requiring a fully equipped semiconductor cleanroom. This layer-by-layer fabrication method is in principle also viable for the implementation of 3D structures in semiconductors other than Si.

### 4. Experimental Section

In the FIB implantation, an area dose of 10 pC/ $\mu$ m<sup>2</sup> (6 × 10<sup>15</sup> cm<sup>-2</sup>) of Ga<sup>+</sup> ions was used, at an acceleration voltage of 30 kV, utilizing a Nova 600 NanoLab from FEI (the Netherlands). Before each Si laver deposition, the (100) silicon wafers were cleaned by the following steps: 10 s dip in 5% hydrofluoric acid (HF), 5 min wash in deionized (DI) water, 5 min etch in hot H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> 3:1, 5 min DI wash, 10 s dip in 5% HF, and 5 min DI wash. The Si layers were grown from a disilane  $(Si_2H_6)$  precursor, at a pressure of 2600 Pa and a temperature of 635 °C. using an Epsilon 2000 single wafer epitaxy tool from ASM International N.V. (the Netherlands). During the wafer loading procedure, the wafers were exposed to temperature steps of 850 °C for 13 s, followed by 725 °C for 120 s. After the final implantation, the wafers were treated with a rapid thermal anneal in an argon atmosphere at 650 °C for 30 s. The structures were formed by a final etch in KOH. First, a 3 s dip in 5% HF was done to remove the native silicon oxide and then the wafers were etched in 30% KOH at 36 °C for 4 to 8 min, depending on the targeted under-etch. Finally, the wafers were washed in DI water for 3 min and dried with N<sub>2</sub>. The AFM measurements were made with an MFP-3D from Asylum Research (USA), and TEM images with a Tecnai G2 F20XT from FEI (the Netherlands).

### Acknowledgements

This work was funded by the European Research Council (ERC) under grant agreement No.277879 M&M's.

Received: March 26, 2012 Published online: June 8, 2012

- [1] K. E. Petersen, Proc. IEEE 1982, 70, 420.

- [2] B. Wendel, D. Rietzel, F. Kühnlein, R. Feulner, G. Hülder, E. Schmachtenberg, *Macromol. Mater. Eng.* 2008, 293, 799.

- [3] J. Stampfl, S. Baudis, C. Heller, R. Liska, A. Neumeister, R. Kling, A. Ostendorf, M. Spitzbart, J. Micromech. Microeng. 2008, 18, 125014.

- [4] G. von Freymann, A. Ledermann, M. Thiel, I. Staude, S. Essig, K. Busch, M. Wegener, Adv. Funct. Mater. 2010, 20, 1038.

- [5] M. Deubel, G. von Freymann, M. Wegener, S. Pereira, K. Busch, C. M. Soukoulis, *Nat. Mater.* 2004, 3, 444.

- [6] K. Busch, G. von Freymann, S. Linden, S. F. Mingaleev, L. Tkeshelashvili, M. Wegener, *Phys. Rep.* 2007, 444, 101.

- [7] J. P. Kruth, X. Wang, T. Laoui, L. Froyen, Assem. Autom. 2003, 23, 357.

- [8] J. A. Lewis, Adv. Funct. Mater. 2006, 16, 2193.

- [9] D. B. Chrisey, Science 2000, 289, 879.

- [10] G. M. Gratson, M. Xu, J. A. Lewis, Nature 2004, 428, 386.

#### www.afm-journal.de

FUNCTIONAL

www.MaterialsViews.com

- [11] S. Johansson, J. Å. Schweitz, H. Westberg, M. Boman, J. Appl. Phys. 1992, 72, 5956.

- [12] H. Westberg, M. Boman, S. Johansson, J. Å. Schweitz, J. Appl. Phys. 1993, 73, 7864.

- [13] P. B. Kargl, N. Arnold, D. Bäuerle, Appl. Surf. Sci. 1997, 108, 257.

- [14] I. Utke, P. Hoffmann, J. Melngailis, J. Vac. Sci. Technol. B 2008, 26, 1197.

- [15] A. A. Tseng, Small 2005, 1, 924.

- [16] S. Reyntjens, R. Puers, J. MIcromech. Microeng. 2001, 11, 287.

- [17] H. J. Whitlow, M. Ling Ng, V. Auzelyte, I. Maximov, L. Montelius, J. A. van Kan, A. A. Bettiol, F. Watt, *Nanotechnology* **2004**, *15*, 223.

- [18] E. J. Teo, M. B. H. Breese, E. P. Tavernier, A. A.Bettiol, F. Watt, M. H. Liu, D. J. Blackwood, *Appl. Phys. Lett.* **2004**, *84*, 3202.

- [19] G. Subramania, Q. Li, Y.-J. Lee, J. J. Figiel, G. T. Wang, A. J. Fischer, *Nano Lett.* 2011, 11, 4591.

- [20] S. Kima, J. Wu, A. Carlson, S. H. Jin, A. Kovalsky, P. Glass, Z. Liu, N. Ahmed, S. L. Elgan, W. Chen, P. M. Ferreira, M. Sitti, Y. Huang, J. A. Rogers, *Proc. Natl. Acad. Sci. USA* **2010**, *107*, 17095.

- [21] S. Y. Lin, J. G. Fleming, D. L. Hetherington, B. K. Smith, R. Biswas, K. M. Ho, M. M. Sigalas, W. Zubrzycki, S. R. Kurtz, J. Bur, *Nature* 1998, 394, 251.

- [22] A. Carlson, H.-J. Kim-Lee, J. Wu, P. Elvikis, H. Cheng, A. Kovalsky, S. Elgan, Q. Yu, P. M. Ferreira, Y. Huang, K. T. Turner, J. A. Rogers, *Appl. Phys. Lett.* **2011**, *98*, 264104.

- [23] B. Schmidt, L. Bischoff, J. Teichert, Sens. Actuators A 1997, 61, 369.

- [24] J. Brugger, G. Beljakovic, M. Despont, N. F. de Rooij, P. Vettiger, *Microelectron. Eng.* 1997, 35, 401.

- [25] N. Kawasegi, N. Morita, S. Yamada, N. Takano, T. Oyama, K. Ashida, J. Taniguchi, I. Miyamoto, *JSME Int. J. Series C* 2006, 49, 583.

- [26] R. Böttger, L. Bischoff, B. Schmidt, M. Krause, J. Micromech. Microeng. 2011, 21, 095025.

- [27] L. Bischoff, B. Schmidt, H. Lange, D. Donzev, Nucl. Instrum. Meth. Phys. Res. Sect. B 2009, 267, 1372.

- [28] I. L. Berry, A. L. Caviglia, J. Vac. Sci. Technol. B 1983, 1, 1059.

- [29] P. Sievilä, N. Chekurov, I. Tittonen, Nanotechnology 2010, 21, 145301.

- [30] H. X. Qian, W. Zhou, J. Miao, L. E. N. Lim, X. R. Zeng, J. Micromech. Microeng. 2008, 18, 035003.

- [31] N. Chekurov, K. Grigoras, A. Peltonen, S. Franssila, I. Tittonen, Nanotechnology 2009, 20, 065307.

- [32] N. Chekurov, K. Grigoras, L. Sainiemi, A. Peltonen, I. Tittonen, S. Franssila, J. Micromech. Microeng. 2010, 20, 085009.

- [33] E. Platzgummer, S. Cernusca, C. Klein, J. Klikovits, S. Kvasnica, H. Loeschner, Proc. SPIE 2010, 7823, 782308.

- [34] J. F. Ziegler, J. P. Biersack, M. D. Ziegler, SRIM The Stopping and Range of Ions in Matter. Lulu Press Co., Morrisville, NC 2008.

- [35] J. Pejnefors, S.-L. Zhang, H. H. Radamson, J. V. Grahn, M. Ostling, J. Appl. Phys. 2000, 88, 1655.

- [36] P. Ashburn, Materi. Sci. Semicond. Process. 2001, 4, 521.

- [37] M. Rommel, G. Spoldi, V. Yanev, S. Beuer, B. Amon, J. Jambreck, S. Petersen, A. J. Bauer, L. Frey, J. Vac. Sci. Technol. B 2010, 28, 595.