# Postprint

This is the accepted version of a paper published in *IEEE Electron Device Letters*. This paper has been peer-reviewed but does not include the final publisher proof-corrections or journal pagination.

Citation for the original published paper (version of record):

Elahipanah, H., Salemi, A., Zetterling, C-M., Östling, M. (2015) 5.8-kV Implantation-Free 4H-SiC BJT With Multiple-Shallow-Trench Junction Termination Extension.

*IEEE Electron Device Letters*, 36(2): 168-170 http://dx.doi.org/10.1109/LED.2014.2386317

Access to the published version may require subscription.

N.B. When citing this work, cite the original published paper.

Permanent link to this version:

http://urn.kb.se/resolve?urn=urn:nbn:se:kth:diva-163477

# 5.8-kV Implantation-Free 4H-SiC BJT with Multiple-Shallow-Trench Junction Termination Extension

Hossein Elahipanah, *Member, IEEE*, Arash Salemi, *Student Member, IEEE*, Carl-Mikael Zetterling, *Senior Member, IEEE*, and Mikael Östling, *Fellow, IEEE*

Abstract—Implantation-free 4H-SiC BJTs with multiple-shallow-trench junction termination extension (ST-JTE) have been fabricated. The maximum current gain of 40 at a current density of 370 A/cm² is obtained for the device with active area of 0.065 mm². A maximum open-base breakdown voltage (BV) of 5.85 kV is measured, which is 93% of the theoretical breakdown voltage. A specific on-resistance ( $R_{ON}$ ) of 28 m $\Omega$ .cm² was obtained.

Index Terms—4H-SiC, multiple-shallow-trench JTE, implantation-free, high-voltage BJT.

#### I. Introduction

SILICON carbide bipolar junction transistors (BJTs) in the 3–7-kV range with low on-resistance (R<sub>ON</sub>) are very attractive devices for industrial applications due to their low loss and fast switching speed. Besides, gaining lower on-resistance results in lower loss which is as important as improving the breakdown voltage to its theoretical value. Several termination techniques have been developed and optimized to approach the ideal breakdown voltage and improve the termination efficiency [1-12]. Among them, implantation-free devices with low R<sub>ON</sub> have the advantage of preventing life-time-killing defects and current degradation caused by ion implantation [10]. These devices are based on etched junction termination extensions (JTEs) in which the remaining dose of the JTEs is controlled by the etching depth. Table I summarized the recent results reported for SiC BJTs.

In this letter, an implantation-free 4H-SiC BJT with multiple-shallow-trench JTE (ST-JTE) termination is demonstrated. The effect of material and etching uncertainties is investigated by numerical simulation and compared with experimental data. The fabricated ST- JTE device has three advantages. First, it is completely free of ion implantation and the following high temperature activation annealing to avoid any further defects caused by it. Second, compared with multi-implanted or graded-etched JTEs, the trench structures are

Manuscript received October 29, 2014; revised November 19 and December 04, 2014; This work was supported by the Swedish Foundation for Strategic Research.

The authors are with the School of Information and Communication Technology, KTH Royal Institute of Technology, Kista SE-164 40, Sweden (e-mail: hosseine@kth.se).

TABLE I. PERFORMANCE COMPARISON BETWEEN THE ST-JTE AND RECENT SIC POWER BITS

| Ref. / Size*  | BV<br>(kV) | $R_{ON}$ $(m\Omega.cm^2)$ | Gain | Termination<br>Efficiency (%) |

|---------------|------------|---------------------------|------|-------------------------------|

| [3] / S       | 3.2        | 28                        | 28   | 40                            |

| [4] / S       | 6          | 28                        | 3    |                               |

| [5] / S       | 23.5       | 321                       | 63   | 78                            |

| [6] / S       | 9.2        | 49                        | 7    |                               |

| [7] / L       | 1.8        | 4.4                       | 40   |                               |

| [8] / L       | 2.3        | 4.5                       | 35   | 85                            |

| [9] / L       | 1.8        | 2.8                       | 117  | -                             |

| [10] / S      | 2.8        | 4                         | 55   | 75                            |

| [10] / L      |            | 6.8                       | 52   |                               |

| [11]/L        | 10.5       | 110                       | 75   | 91                            |

| [12] / L      | 2.7        | 4                         | 132  | > 90                          |

| This work / S | 5.85       | 28                        | 40   | 93                            |

\* "S" FOR SMALL-AREA ( $< 0.5 \text{ MM}^2$ ) LOW-CURRENT (I < 1 A) AND "L" FOR LARGE-AREA ( $> 2.5 \text{ MM}^2$ ) HIGH-CURRENT (I > 5 A) BJTs.

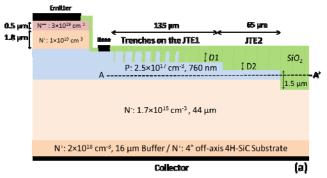

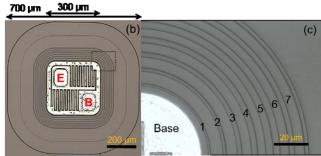

Fig. 1. (a) Schematic cross-sectional view of the 4H-SiC with trenched JTE (ST-JTE), (b) optical microscopic image of the ST-JTE BJT with seven trenches, and (c) magnified optical microscopic image of the trench structures. The trenches are formed on the first JTE with the depth of 300 nm.

simultaneously formed by the first JTE with no extra mask, which makes it a simpler and cheaper structure to fabricate; meanwhile prevents any further misalignment issue. Third, the maximum BV of 5.85 kV is obtained which is 93% of the theoretical value [13]. Higher termination efficiency is yet achievable by increasing the number of trenches and squeezing the trenches which requires lithography with higher resolution.

#### II. DEVICE STRUCTURE AND FABRICATION

The cross-sectional schematic view of the ST-JTE is shown in Fig. 1(a). The total area of the device is  $0.49~\text{mm}^2$ . The width of the emitter and base fingers are  $10~\text{and}~4~\mu\text{m}$ , respectively (see Fig. 1(b)). Trench structures gradually decreasing in dimensions have been formed on the first JTE (see Fig. 1(c)). Depending on the design, the depth of the trenches can be controlled by the etching of the other layers with no additional mask. Considering the lithography limit to  $1~\mu\text{m}$ , the number, width, and spacing of the trenches are also optimized to reach the optimized electric field spreading. The optimized result is obtained for the ST-JTE with seven trenches as deep as 300 nm; whereas the spacing gradually increases from  $1~\mu\text{m}$  to  $7~\mu\text{m}$  and the width is gradually decreasing from  $9~\mu\text{m}$  to  $3~\mu\text{m}$ .

A 100-mm 4H-SiC n<sup>+</sup>-substrate with five different epilayers on top is used (see Fig. 1(a)). A 2.5-µm layer of SiO<sub>2</sub> is deposited and patterned as the hard mask. Then, inductively coupled plasma (ICP) deep etching is used to form the emitter and mesa. Afterward, reactive ion etching (RIE) is used to accurately form the JTEs with the depth of  $D_1 = 300$  nm and  $D_2 = 160$  nm, respectively. Trench structures are simultaneously formed by the etching step of the first JTE with the same depth. As a result, the etching uniformity of ±5% is achieved, which significantly improved the yield of the wafer. Also, extra etchings are performed to investigate the dose dependency of the breakdown voltage. Subsequently, sacrificial oxidation was done in O<sub>2</sub> for 1 h. After removal of the thermally grown oxide, 50 nm SiO<sub>2</sub> was deposited by PECVD and annealed at 1100 °C in N<sub>2</sub>O environment for 3 h as the passivation layer. A Ni layer with a thickness of 140nm was deposited and patterned on the emitter and back-side collector. Contacts were annealed in Ar at 950 °C for 1 min. A 110-nm Ni/Ti/Al metal stack with the thickness 0.1/0.15/0.85 was deposited and patterned on the base layer and annealed in N<sub>2</sub> at 815 °C for 2 min to form the p-contacts [14]. To improve the current spreading through the contacts, 500 nm of Al was deposited and formed on the n- and p-contacts. Using TLM structures, a contact resistivity of  $1.4 \times 10^{-5}$   $\Omega.\text{cm}^2$  and  $1.5 \times 10^{-4} \,\Omega.\text{cm}^2$  are measured for the emitter and base contact, respectively. Subsequently, a thick oxide was deposited as the insulator layer and the contact windows were opened. Finally, 2.5-µm Al was sputtered and patterned to form the emitter and base electrodes.

### III. RESULTS AND DISCUSSION

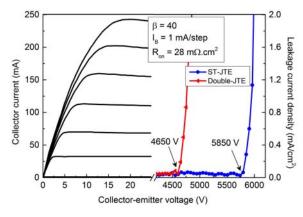

The  $I_C$ – $V_C$  characteristic of the ST-JTE device in forward and blocking mode is shown in Fig. 2. A maximum current gain of 40 at  $I_C$  = 0.24 A ( $J_C$  = 370 A/cm<sup>2</sup>) and  $V_{CE}$  = 4.3 V at

$I_C = 0.1$  A are achieved. The current flow in the thick collector layer is analyzed by 2-D simulation and the estimated equivalent active area of the device is  $0.065 \text{ mm}^2$ . Therefore, the specific on-resistance of  $R_{\rm ON} = 28 \text{ m}\Omega.\text{cm}^2$  was calculated considering the current spreading effect. It should be noted that the on-resistance of the device is expected to be higher when scaled up to large-area since the small-area BJT benefits from significant current spreading in the collector layer. The forward voltage drop at  $J_C = 100 \text{ A/cm}^2$  is 2.6 V. The maximum open-base breakdown voltage of 5850 V and 4650 V are measured for the ST-JTE and double-JTE, respectively. These correspond to 93% and 75% of the theoretical value, respectively, which prove the efficiency of the ST-JTE structure. Therefore, less termination area is required for the ST-JTE device leading to reduction of total device cost.

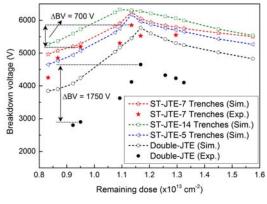

The remaining dose of the dopants in the JTEs is controlled by the etching process. Fig. 3 illustrates the BV versus the player dose for ST-JTE compare with conventional double-JTE. It is apparent that the ST-JTE BJTs have much less sensitivity to the etching variation. Also, simulation results show that higher number of trenches results in wider stable dose range which will result in higher yield of the wafer. The maximum breakdown voltage variation (ΔBV) of 700 V and 1700 V is measured for the ST-JTE and conventional double-JTE

Fig. 2. *I-V* forward characteristics of the ST-JTE device and comparison of the breakdown voltages of the ST-JTE and conventional double-JTE device.

Fig. 3. Experimental and simulated breakdown voltages of the ST-JTE and double-JTE devices as a function of the remaining dose of

the JTE1. The dose range for the ST-JTE structures are much wider than that of the double-JTE.

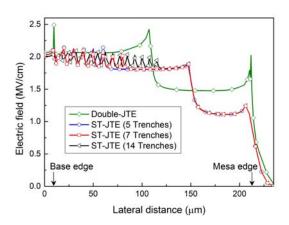

Fig. 4. Simulated electric field distribution along the device at the cutline of AA' for the applied reverse voltage of 6 kV.

20% variation in the remaining dose of the p-layer, respectively. Among the 26 measured ST-JTE devices, 80% blocks more than 4.5 kV and the yield of high blocking ST-JTE BJTs (> 5 kV) is about 55%.

The influence of charges at the oxide/SiC interface on the breakdown voltage of SiC devices has been reported [15]. The amount of charges in a certain area varies by forming the trenches. Therefore, taking the presence of these charges into account, the optimum effective dose of 1.15×10<sup>13</sup> cm<sup>-3</sup> is found for the first JTE by simulation. Fig. 4 compares the simulated electric field for the ST-JTEs with different number of trenches with conventional double-JTE structure at their optimum dose for the applied reverse voltage of 6 kV. It is apparent that the electric field is shared by the multiple trenches leading to alleviated peaks in the electric field. Therefore, these trenches prevent the field crowding and shield the high field at the JTE and mesa corners. Thus the electric field in the ST-JTE is more uniform which results in higher efficiency of the termination technique. Also, it is apparent that higher number of trenches with smaller widths results in better electric field distribution. Considering the lithography limit to 1 µm, the optimized result is obtained for the ST-JTE with seven trenches. The smallest dimension required for realizing the ST-JTE with 14 trenches is 0.5 µm compare with 1 µm for the device with seven trenches. One can expect that a finer photolithography improves the termination efficiency and sensitivity to the etching and doping variation (remaining dose) of the p-layer. However, it is recommended not to design too narrow trenches with dense

The performance of the ST-JTE BJT compared with that of the best reported BJTs are summarized in Table I. The maximum open-base BV of 5850 V and  $R_{ON}$  of 28  $m\Omega.cm^2$  are obtained, respectively, which is very close to the 4H-SiC unipolar limit. The termination efficiency of the ST-JTE device is among the highest values reported to date.

## IV. CONCLUSION

An implantation-free 4H-SiC BJT with multiple-shallow-

trench JTE structure (ST-JTE) is presented. A specific onresistance ( $R_{ON}$ ) of 28 m $\Omega$ .cm<sup>2</sup> is obtained for the device with active area of 0.065 mm<sup>2</sup>. A maximum open-base breakdown voltage (BV) of 5.85 kV is measured which corresponds to 93% of the ideal value. No extra mask is required to form these trenches which result in a simpler process without any further misalignment issue.

#### REFERENCES

- [1] M. Östling, "Silicon carbide based power devices," in *IEDM*, San Francisco, CA, 2010, pp. 13.3.1–13.3.4.

- [2] A. Agarwal, M. Das, B. Hull, S. Krishnaswami, J. Palmour, J. Richmonds, S. H. Ryu, and J. Zhang, "Progress in silicon carbide power devices," in *Proc. 64th Device Res. Conf.*, Jun. 2006, pp. 155–158.

- [3] C.-F. Huang and J. R. Cooper Jr, "4H-SiC npn bipolar junction transistors with BV<sub>CEO</sub> > 3,200 V," in *Proc. 14th ISPSD*, Jun. 2002, pp. 57–60

- [4] S. Balachandran, C. Li, P. A. Losee, I. B. Bhat, and T. P. Chow, "6 kV 4H-SiC BJTs with specific on-resistance below the unipolar limit using selectively grown base contact process," in *Proc. 19th ISPSD*, Jun. 2007, pp. 293–296.

- [5] H. Miyake, T. Okuda, H. Niwa, T. Kimoto, and J. Suda, "21-kV SiC BJTs with space-modulated junction termination extension," *IEEE Electron Device Lett.*, vol. 33, no. 11, pp. 1598–1600, Nov. 2012.

- [6] J. Zhang, H. Zhao, P. Alexandrov, and T. Burke, "Demonstration of first 9.2 kV 4H-SiC bipolar junction transistor," *Electron. Lett.*, vol. 40, no. 21, pp. 1381–1382, Oct. 2004.

- [7] Q. Zhang, A. Burk, F. Husna, R. Callanan, A. Agarwal, J. Palmour, R. Stahlbush, and C. Scozzie, "4H-SiC bipolar junction transistors: From research to development A case study: 1200 V, 20 A, stable SiC BJTs with high blocking yield," in *Proc. 21st ISPSD*, Jun. 2009, pp. 339–342.

- [8] M. Domeij, C. Zaring, A. O. Konstantinov, M. Nawaz, J.-O. Svedberg, K. Gumaelius, I. Keri, A. Lindgren, B. Hammarlund, M. Östling, M. Reimark, "2.2 kV SiC BJTs with low V<sub>CESAT</sub> fast switching and short-circuit capability," *Mater. Sci. Forum*, vol. 645–648, pp. 1033–1036, Apr. 2010.

- [9] M. Domeij, A. Konstantinov, A. Lindgren, C. Zaring, K. Gumaelius, M. Reimark, "Large area 1200 V SiC BJTs with β>100 and ρON<3 mΩcm²," *Mater. Sci. Forum*, vol. 717–720, pp. 1123–1126, May 2012.

- [10] R. Ghandi, B. Buono, M. Domeij, C.-M. Zetterling, and M. Östling, "High-voltage (2.8 kV) implantation-free 4H-SiC BJTs with long-term stability of the current gain," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2665–2669, Aug. 2011.

- [11] S. Sundaresan, S. Jeliazkov, B. Grummel, and R. Singh, "10 kV SiC BJTs—Static, switching and reliability characteristics," in *Proc. 25th ISPSD*, Jun. 2013, pp. 303–306.

- [12] S. G. Sundaresan, S. Jeliazkov, B. Grummel, R. Singh, "Rapidly maturing SiC junction transistors featuring current gain (β) > 130, blocking voltages up to 2700 V and stable long-term operation," *Mater. Sci. Forum*, vol. 778–780, pp. 1001–1004, Feb. 2014.

- [13] A. Konstantinov, Q. Wahab, N. Nordell, and U. Lindefelt, "Ionization rates and critical fields in 4H silicon carbide," *Appl. Phys. Lett.*, vol. 71, no. 1, pp. 90–92, Jul. 1997.

- [14] C.-M. Zetterling, *Process Technology for Silicon Carbide Devices*, London, U.K.: IET, Mar 2002.

- [15] R. Ghandi, B. Buono, M. Domeij, R. Esteve, A. Schöner, J. Han, S. Dimitrijev, S. A. Reshanov, C.-M. Zetterling, and M. Östling, "Surface passivation effects on the performance of 4H-SiC BJTs," *IEEE Trans. Electron Devices*, vol. 58, no. 1, pp. 259–265, Jan. 2011.