Open access • Journal Article • DOI:10.1002/SDTP.13394

# 8.4: Invited Paper: Oxide devices for displays and low power electronics — Source link 🖸

Jiawei Zhang, Wensi Cai, Joshua Wilson, Xiaochen Ma ...+8 more authors Institutions: University of Manchester, Shandong University Published on: 04 Oct 2019 Topics: Schottky diode, Low-power electronics, Oxide and Adder

# Related papers:

- Implementation of a 900 V Switching Circuit for High Breakdown Voltage beta-Ga2O3 Schottky Diodes

- · Silicon carbide Schottky diodes and MOSFETs: Solutions to performance problems

- A Comparison of Silicon and Silicon Carbide MOSFET Switching Characteristics

- A vertical SiC JFET with a monolithically integrated JBS diode

- A qualitative study of the dc performance of SIPMOS transistors

The University of Manchester Research

# Oxide devices for displays and low power electronics

DOI: 10.1002/sdtp.13394

# **Document Version**

Accepted author manuscript

# Link to publication record in Manchester Research Explorer

# Citation for published version (APA):

Zhang, J., Cai, W., Wilson, J., Ma, X., Brownless, J., Li, Y., Yang, J., Yuan, Y., Ma, P., Xin, Q., & Song, A. (2019). Oxide devices for displays and low power electronics. In *SID Symposium Digest of Technical Papers* https://doi.org/10.1002/sdtp.13394

Published in:

SID Symposium Digest of Technical Papers

# Citing this paper

Please note that where the full-text provided on Manchester Research Explorer is the Author Accepted Manuscript or Proof version this may differ from the final Published version. If citing, it is advised that you check and use the publisher's definitive version.

# General rights

Copyright and moral rights for the publications made accessible in the Research Explorer are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

# **Takedown policy**

If you believe that this document breaches copyright please refer to the University of Manchester's Takedown Procedures [http://man.ac.uk/04Y6Bo] or contact uml.scholarlycommunications@manchester.ac.uk providing relevant details, so we can investigate your claim.

# Oxide devices for displays and low power electronics

Jiawei Zhang\*, Wensi Cai\*, Joshua Wilson\*, Xiaochen Ma\*, Joseph Brownless\*, Yunpeng

Li\*\*, Jin Yang\*\*, Yuzhuo Yuan\*\*, Pengfei Ma\*\*, Qian Xin\*\*, and Aimin Song\*,\*\*

\* School of Electrical and Electronic Engineering, The University of Manchester, Manchester, U.K.

\*\* Center of Nanoelectronics and School of Microelectronics, Shandong University, Jinan, China

# Abstract

Oxide semiconductors have been envisaged to find applications in flexible electronics in daily life such as wearable electronic gadgets to offer novel user experiences. However, there are still several bottlenecks to overcome in order to realise this goal, especially the lack of oxide-semiconductor components fast enough for wireless communications, low power oxide transistors, and high-performance p-type oxide semiconductors for complementary circuits. Here we review our recent work to address these problems, including gigahertz operating IGZO Schottky diodes and TFTs, 1 V operating TFTs, complementary circuits using IGZO and SnO TFTs, and a novel TFT structure with unique performance.

# **Author Keywords**

Oxide semiconductors; complementary circuit; full adder; Schottky diode; source-gated transistor; low voltage electronics.

### 1. Introduction

Since the first demonstration of flexible amorphous IGZO thin-film transistors (TFT) in 2004<sup>[1]</sup>, amorphous oxide semiconductors have received much attention due to their superior electrical characteristics. These materials compliment traditional semiconductors not only in basic applications but also in emerging areas such as flexible electronics, "smart" paper, and wearable technologies. The major advantages of metal oxide semiconductors include their low fabrication temperature, variable deposition methods, highly uniform surface and flexibility. Though IGZO technology is nearly mature, its major application

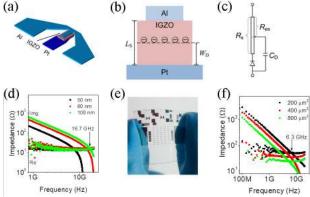

**Figure 1.** (a) Schematic diagram of the IGZO Schottky diode with coplanar waveguide structure. (b) Crosssectional diagram of the Pt-IGZO Schottky diode. (c) Equivalent circuit of the thin-film Schottky diode. (d) Real and imaginary impedance of the diode on a glass substrate at high frequencies obtained from S-parameters. (e) Image of the flexible IGZO Schottky diode. (h) Real and imaginary impedance of the flexible diode at high frequencies obtained from S-parameters. Adapted with permission from [3]. Copyright © 2015, Springer Nature.

to date is still use as the driving units in display pixels. This is due to the lack of several important capabilities: high-frequency electronic devices for RF and microwave transmitters, low power consumption devices for wearable electronics, and high performance p-type oxide semiconductors for large-scale complementary circuits.

Here, we review our recent work on a) high-performance oxidebased Schottky diodes with an ideality factor of 1.09, ultra-low noise, and operating speed >20 GHz on glass<sup>[2]</sup> and 2.45 GHz on flexible substrate<sup>[3]</sup>; b) IGZO TFTs capable of reaching a benchmark speed of 1 GHz<sup>[4]</sup>, which are, to the best of our knowledge, the fastest oxide-based diodes and transistors to date; c) a few different methods to achieve IGZO TFTs capable of onevolt operations<sup>[5-9]</sup>; d) CMOS-like oxide logic gates and functional circuits including inverters with a gain up to 150<sup>[10, 11]</sup>, NAND gate<sup>[12]</sup>, D-latch<sup>[13]</sup>, 51 stage ring oscillator<sup>[13]</sup>, complementary static random access memories<sup>[14]</sup>, and a one-bit full adder<sup>[13]</sup>, etc, by integrating SnO-based p-type TFTs with IGZO-based n-type TFTs; and finally e) novel oxide TFTs with a Schottky source contact that show no short channel effect, almost total immunity to negative bias illumination stress, and have a gain over two orders of magnitude higher than that of a typical silicon transistor<sup>[15]</sup>.

# 2. Oxide-semiconductor based electronic devices

**High frequency Schottky diodes:** High-frequency rectifiers are the essential element in the transmitters which are used for wireless communications. The key frequencies include 2.4 GHz for typical Wi-Fi channels and Bluetooth, 3.8 GHz for the 4G long-term evolution band and 6 GHz for parts of 5G communication. In order to reach these frequencies, we optimized the Pt/IGZO Schottky interface and investigated the relationship between the series resistance and depletion capacitance of the IGZO Schottky diodes<sup>[3]</sup>. Figure 1(a) shows the design of the diode and Figure 1(b) shows the cross-section schematic. The Schottky junction is formed between the Pt and IGZO interface and Al is used to form the ohmic contact. By introducing oxygen during the deposition of IGZO, the effects of Fermi level pinning are reduced due to the passivation of the dangling bonds at the IGZO surface.

The cut-off frequency of a Schottky diode can be calculated by using  $f_T = 1/(2\pi R_s C_D)$ , where R<sub>s</sub> is the series resistance and C<sub>D</sub> is the capacitance of the depletion layer. For conventional bulk materials, the series resistance remains almost the same

during operation. However, for thin-film Schottky diodes, the semiconductor layer may be fully depleted at low forward biases. Here we proposed a new parameter, effective series resistance,  $R_{es}$ , to describe the effective resistance that determines the cut-off frequency, as shown in Figure 1(c). The S-parameter at high frequencies indicates that  $R_{es}$  is around 1000 times smaller than  $R_{s}$ . By further optimizing the IGZO thickness, the highest

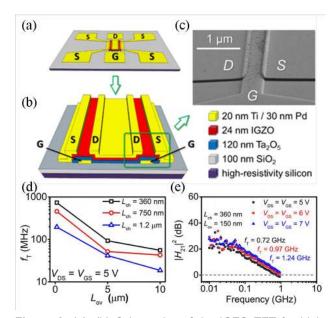

**Figure 2.** (a), (b) Schematics of the IGZO TFT for high-frequency measurement. (c) SEM image of the channel. (d) Cut-off frequencies of the IGZO TFTs with different channel lengths and overlapping lengths. (e) Cut-off frequencies of the IGZO TFT under different biases. Adapted with permission from [4]. Copyright © 2018, IEEE.

intrinsic cut-off frequency obtained from S-parameters is 16.7 GHz on glass substrates, as shown in Figure 1(d), and 6.3 GHz on flexible substrates, as shown in Figures 1(e) and 1(f). By optimizing the active area of the diode, the cut-off frequency is further improved beyond 20 GHz<sup>[2]</sup>. By integrating the GHz operating IGZO Schottky diodes with TFTs, a range of wireless devices using oxide semiconductors can be constructed.

High frequency IGZO TFTs: For integrated circuits, the speed of TFTs limits the computation capacity. Thus it is necessary to improve the operation frequency of oxide-semiconductor TFTs in order to commercialize IGZO for applications in the 'internet of things' (IoT). The current-gain cut-off frequency can be described by  $f_T = \frac{g_m}{2\pi c_G} \approx \frac{\mu_{eff}(v_{eT} - v_{TH})}{2\pi L_{eff}(L_{eH} + L_{op})}$ , where  $g_m$  is the transconductance,  $V_G$  is the gate voltage,  $V_{TH}$  is the threshold voltage,  $\mu_{eff}$  is the effective field-effect mobility, C<sub>G</sub> is the total gate capacitance,  $L_{CH}$  is the channel length and  $L_{OV}$  is the overlap length between the source/drain contact and the gate electrode<sup>[4]</sup>. It is plausible that the cut-off frequency can be improved by reducing the channel length and the overlap length. However, in practice,  $\mu_{eff}$ decreases when reducing  $L_{\mbox{\scriptsize CH}}$  as the contact resistance becomes more dominant to the total resistance between source and drain. Increasing L<sub>OV</sub> is able to reduce the contact resistance but also contributes to a higher parasitic overlap capacitance. Besides, reducing L<sub>CH</sub> may introduce the short-channel effect which makes the device difficult to pinch off. Thus optimising the channel length and overlap length is critical to realizing a high operating frequency<sup>[4]</sup>.

The structure and an SEM image of the IGZO TFT are shown in Figures 2(a) to 2(c). All the patterns are defined by using electronbeam lithography. Devices with different  $L_{CH}$  and  $L_{OV}$  are fabricated and characterized using a vector network analyzer. The IGZO TFT with the shortest  $L_{CH}$  of 360 nm and  $L_{OV}$  of 150 nm showed the highest cut-off frequency (shown in Figure 2(d)) and reached 1.24 GHz at  $V_G = V_D = 7 V$  (shown in Figure 2(e)). This implies that the operational frequency may be further improved by reducing the  $L_{OV}$  and  $L_{CH}$ . This work demonstrates that it is possible to realize oxide-based integrated circuits operating at gigahertz frequencies.

**Low power electronics:** Low operating voltages have been long desired for TFTs as the operating voltage directly determines the power consumption. According to the operation mechanism of TFTs, the operating voltage can be reduced by increasing the capacitance per unit area of the gate dielectric. We have proposed two methods to improve the capacitance. One is to reduce the thickness of the dielectric layer and the other is to use electrolytes instead of dielectrics.

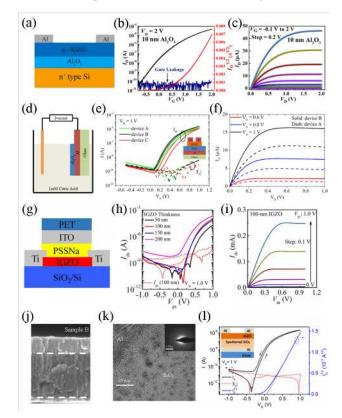

One challenge of reducing the dielectric thickness is that it is difficult to deposit conformal and pin-hole free films with thicknesses of a few nanometers. Atomic-layer deposition (ALD) is a widely used method. By using ALD, a 10 nm thick  $Al_2O_3$  layer is deposited as the dielectric layer, as shown in Figure  $3(a)^{[9]}$ . The capacitance is found to be 720 nF/cm<sup>2</sup>, which makes the IGZO TFT operate within 1 V as shown in Figures 3(b) and

**Figure 3.** (a) Cross-sectional schematic, (b) transfer curve, and (c) output curves of IGZO TFT with 10 nm thick ALD Al<sub>2</sub>O<sub>3</sub> dielectric layer. (d) Schematic of the anodization process. (e) Trasnfer curvesm, and (f) output curves of the IGZO TFT with 3 nm thick anodized AlO<sub>x</sub> layer. (g) Cross-sectional schematic, (h) transfer curve, and (i) output curves of IGZO TFT with PSSNa electrolyte. (j) SEM and (k) TEM images of the SiO<sub>2</sub> electrolyte. (l) Output curves of the IGZO TFT with SiO<sub>2</sub> electrolyte. Adapted with permission from [6-9]. Copyright © AIP Publishing; 2018, IEEE; 2017, Springer Nature.

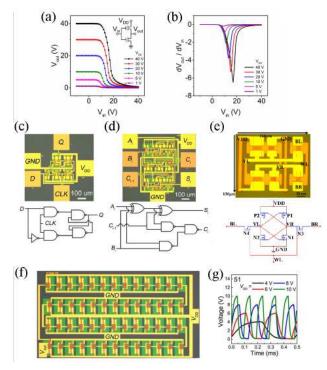

**Figure 4.** (a) Output voltages and (b) gain of the IGZO/SnO inverter. (c), (d), (e) Images and electrical schemetics of the IGZO/SnO based D-Latch, 1 bit full adder, and randomly accessible memory.(f) Image and (g) output votages of a 51-satge ring oscillator based on IGZO and SnO TFTs. Adapted with permission from [13], [14], and [16]. Copyright © 2018,2019, IEEE.

3(c). By replacing the Al<sub>2</sub>O<sub>3</sub> with 5 nm thick HfO<sub>2</sub>, the operating voltage further reduces to 0.5 V with a gate capacitance of 1,300 nF/cm<sup>2[5]</sup>. However, one drawback of ALD is that it normally requires high vacuum and a relatively high deposition temperature. An alternative method to form ultra-thin oxides is anodization<sup>[6]</sup>. Figure 3(d) shows the schematic diagram of the anodization process for an AlO<sub>x</sub> layer. The deposition thickness is controlled by the applied voltage. By using an anodization voltage of 2.3 V, a 3 nm thick AlO<sub>x</sub> layer is obtained. The capacitance reaches 1,000 nF/cm<sup>2</sup> and the IGZO TFT also realized a 1 V operation, as shown in Figures 3(e) and 3(f). Compared with ALD, anodization has several advantages including room temperature processing, no need of vacuum, low cost, and being suitable for large-area production. Such a technique provides an alternative solution for the future large-area flexible and low power electronics.

The other method to improve the capacitance is to use electrolyte instead of conventional dialectics. The high capacitance of electrolyte is attributed to the mobile ions forming an electric double layer at the interface. The most commonly used electrolytes in TFTs are solution processed ionic liquids or ionic gels. Figure 3(g) shows the cross-sectional schematic of an IGZO TFT with PSSNa ionic gel<sup>[7]</sup>. It adopts a "carving, cutting, and flip-chip bonding" technique during the fabrication. The capacitance reaches a maximum of 4.5  $\mu$ F/cm<sup>2</sup>. The transfer and output curves of the PSSNa gated IGZO TFT are shown in Figures 3(h) and 3(i). However, it is still challenging to use ionic liquid or ionic gel in industrial applications as it is difficult to maintain the electrolyte shape and control the thickness during the

fabrication process. Thus, a new type of electrolyte is proposed, namely a solid-state electrolyte. Such a material can be deposited using industrial compatible techniques including sputtering and plasma-enhanced chemical-vapor deposition. Here a 200 nm thick SiO<sub>x</sub> electrolyte is RF sputtered with a loose structure, by tuning the deposition power and pressure<sup>[8]</sup>. SEM and TEM images of the sputtered  $SiO_x$  electrolyte are shown in Figures 3(i) and 3(k). The maximum capacitance is found to be over 300 nF/cm<sup>2</sup>. In Figure 3(1), the SiO<sub>x</sub> electrolyte gated IGZO TFT also demonstrate 1 V operation. It is noted that the capacitance of the electrolyte drops with frequency due to the slow mobile ions. As the capacitance of the  $SiO_x$  electrolyte does not fully depend on the thickness, compared with the ultra-thin dielectrics, the SiO<sub>x</sub> electrolyte can be made thicker, giving a higher level of uniformity and a lower leakage current. These make the electrolyte gated TFTs suitable to be used in applications operating at low frequencies.

CMOS electronics: In contast to the rapid development in ntype oxide semiconductors. SnO has been regarded as the most promising p-type oxide semiconductor due to its high stability in air and comparable field-effect mobility to IGZO. It is highly desired to complement SnO with IGZO to form complementary integrated circuits as they both can be deposited using RF sputtering, which is currently used widely in the display industry. The first IGZO/SnO complementary inverter was demonstrated in 2017 with a gain of around  $25^{[16]}$ , as shown in Figures 4(a) and 4(b). Then some improved IGZO/SnO inverters<sup>[10, 11]</sup>, NAND<sup>[12]</sup>, NOR<sup>[13]</sup>, and XOR<sup>[13]</sup> gates were demonstrated in the following years. By cascading these basic logic gates, we have also realized a D-latch (Figure 4(c))<sup>[13]</sup>, a 1-bit full-adder (Figure 4(d))<sup>[13]</sup>, and RAM (Figure 4(e))<sup>[14]</sup> based on IGZO and SnO TFTs. These are the essential components for the central processing unit. A 51stage ring oscillator composed of 104 IGZO and SnO TFTs is shown in Figure 4(f)<sup>[13]</sup>. The oscillation frequency reaches 10 kHz at a supplied voltage of 10 V, as shown in Figure 4(g). It is the first medium-scale complementary circuit fully based on oxide semiconductors. The successful demonstration of such complicated circuits indicates it is highly possible to build lowpower, large-scale oxide semiconductor based complementary circuits for applications such as flexible mobile phones and transparent computers.

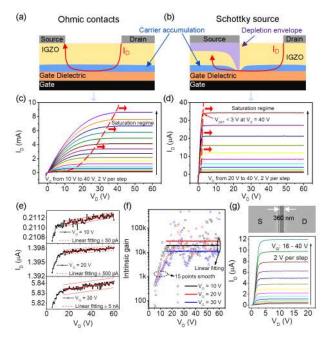

**Novel oxide TFTs:** Transistors are the cornerstone of the modern technologies. In order to realize further advancement, it is necessary to design new transistors with improved performance. Here we present a novel transistor, called the source-gated transistor, by combining the Schottky source with the  $TFT^{[15]}$ . The cross-sectional schematics and the output curves of the conventional TFT and the SGT are shown in Figures 5(a) to 5(d). One significant difference is that the saturation voltages of the SGT in the output curves are much lower than those in the conventional TFTs. This is because the saturation of SGT is due to the channel becoming depleted by the Schottky source under reverse bias. The source/drain current is limited by the reverse current of the Schottky contact. The detailed theory and equations can be found in Ref. 15.

As the saturation is caused by the depletion at the source contact, the channel length modulation, which determines the output resistance of conventional TFTs, has little effect on the output currents of SGTs. Thus such device has the potential to realize a higher intrinsic voltage gain,  $A_V$ , as it equals  $\frac{dI_D}{dV_d} \int \frac{dI_D}{dV_D}$ . For an IGZO SGT with an IGZO thickness of 20 nm, the average

**Figure 5.** (a), (b) Cross-sectional schematics and (c), (d) output curves of a IGZO TFT and SGT. (e) Zoomed output curves and (f) calculated intrinsic voltage gain of the IGZO SGT. (g) SEM image and output curves of the IGZO SGT with a channel length of 360 nm. Adapted with permission from [15]. Copyright © 2019, National Academy of Sciences.

intrinsic voltage gain reached 29,000, as shown in Figures 5(e) and 5(f), which is almost 100 times higher than the value obtained by the conventional Si MOSFET. Besides this, the short channel effect is no longer a critical issue when scaling down the device as the current is limited by the resistance at the source contact instead of by the channel resistance. In Figure 5(g), it is shown that the device still operates properly when decreasing the channel length down to 360 nm. The IGZO SGT also exhibited almost total immunity to negative bias illumination thermal stress, solving another long lasting problem to use oxide semiconductors in display industries. These advantages along with the analytical theory may make SGT another fundamental component in thin-film electronics.

### 3. Conclusion

In summary, our preliminary work on oxide semiconductor based electronics, including gigahertz operating Schottky diodes/TFTs, 1 V operating TFTs, complementary integrated circuits, and novel SGTs, may pave the path towards the realization of daily used flexible and/or transparent electronics.

# 4. Acknowledgements

This work was supported by the North-West Nanoscience Doctoral Training Center, EPSRC Grants EP/N021258/1, EP/G03737X/1, and EP/L01548X/1, National Key Research and Development Program of China Grants 2016YFA0301200 and 2016YFA0201800, and National Natural Science Foundation of China Grants 11374185 and 11304180.

#### 5. References

[1] K. Nomura, H. Ohta, A. Takagi, *et al.*, "Room-temperature fabrication of transparent flexible thin-film transistors using

amorphous oxide semiconductors," Nature, **432**, 488-492 (2004).

- [2] J. Zhang, H. Wang, J. Wilson, *et al.*, "Room Temperature Processed Ultrahigh-Frequency Indium-Gallium–Zinc-Oxide Schottky Diode," IEEE Electron Device Lett., **37**, 389-392 (2016).

- [3] J. Zhang, Y. Li, B. Zhang, *et al.*, "Flexible indium-galliumzinc-oxide Schottky diode operating beyond 2.45 GHz," Nat Commun, 6, 7561 (2015).

- [4] Y. Wang, J. Yang, H. Wang, *et al.*, "Amorphous-InGaZnO Thin-Film Transistors Operating Beyond 1 GHz Achieved by Optimizing the Channel and Gate Dimensions," IEEE Trans. Electron Devices, **65**, 1377-1382 (2018).

- [5] P. Ma, J. Sun, G. Liang, *et al.*, "Half-volt operation of IGZO thin-film transistors enabled by ultrathin HfO2 gate dielectric," Appl. Phys. Lett., **113**, 063501 (2018).

- [6] W. Cai, S. Park, J. Zhang, *et al.*, "One-Volt IGZO Thin-Film Transistors With Ultra-Thin, Solution-Processed Al<sub>x</sub>O<sub>y</sub> Gate Dielectric," IEEE Electron Device Lett., **39**, 375-378 (2018).

- [7] L. Du, D. He, Y. Liu, *et al.*, "Low-Voltage, Flexible IGZO Transistors Gated by PSSNa Electrolyte," IEEE Electron Device Lett., **39**, 1334-1337 (2018).

- [8] X. Ma, J. Zhang, W. Cai, et al., "A Sputtered Silicon Oxide Electrolyte for High-Performance Thin-Film Transistors," Scientific Reports, 7, 809 (2017).

- [9] P. Ma, L. Du, Y. Wang, et al., "Low voltage operation of IGZO thin film transistors enabled by ultrathin Al2O3 gate dielectric," Appl. Phys. Lett., 112, 023501 (2018).

- [10] J. Yang, Y. Wang, Y. Li, *et al.*, "Highly Optimized Complementary Inverters Based on p-SnO and n-InGaZnO With High Uniformity," IEEE Electron Device Lett., **39**, 516-519 (2018).

- [11] Y. Yuan, J. Yang, Z. Hu, et al., "Oxide-Based Complementary Inverters With High Gain and Nanowatt Power Consumption," IEEE Electron Device Lett., 39, 1676-1679 (2018).

- [12] Y. Li, J. Yang, Y. Wang, et al., "Complementary Integrated Circuits Based on p-Type SnO and n-Type IGZO Thin-Film Transistors," IEEE Electron Device Lett., 39, 208-211 (2018).

- [13] Y. Li, J. Zhang, J. Yang, *et al.*, "Complementary Integrated Circuits Based on n-Type and p-Type Oxide Semiconductors for Applications Beyond Flat-Panel Displays," IEEE Trans. Electron Devices, **66**, 950-956 (2019).

- [14] J. Yang, Y. Yuan, Y. Li, et al., "All-Oxide-Semiconductor-Based Thin-Film Complementary Static Random Access Memory," IEEE Electron Device Lett., 39, 1876-1879 (2018).

- [15] J. Zhang, J. Wilson, G. Auton, *et al.*, "Extremely high-gain source-gated transistors," Proceedings of the National Academy of Sciences, 201820756 (2019).

- [16] J. Zhang, J. Yang, Y. Li, *et al.*, "High Performance Complementary Circuits Based on p-SnO and n-IGZO Thin-Film Transistors," Materials, **10**, 2017).