# 820 V GaN-on-Si Quasi-Vertical P-i-N Diodes with BFOM of 2.0 GW/cm<sup>2</sup>

Riyaz Abdul Khadar, Chao Liu, Liyang Zhang, Peng Xiang, Kai Cheng and Elison Matioli, *Member*, *IEEE*

Abstract— In this work we demonstrate GaN-on-Si p-i-n diodes with high breakdown voltage (BV) and state-of-the-art Baliga's Figure of Merit (BFOM) among GaN-on-Si vertical devices. The growth and doping of the GaN drift layer were optimized, leading to a remarkable electron mobility of 720 cm²/Vs for a Si doping level of  $2\times10^{16}$  cm⁻³. With a 4 µm-thick drift layer, we achieved an excellent breakdown voltage of 820 V and ultra low specific on resistance ( $R_{\rm on,sp}$ ) of 0.33 m $\Omega$ cm². This results in a BFOM of 2.0 GW/cm², the highest value reported for GaN-on-Si vertical diodes. These results reveal the excellent prospect of GaN-on-Si for cost-effective vertical power devices.

Index Terms - GaN vertical power devices, GaN-on-Si, high breakdown, quasi-vertical, p-i-n diodes.

### I. INTRODUCTION

aN-based devices have the capability to work at higher voltages, temperatures and switching frequencies with higher efficiencies as compared to existing Si devices [1]. This emanates from the superior properties of GaN such as higher bandgap, saturation velocity, electron mobility and critical electric field as compared to Si [2]. Lateral GaN electronic devices such as HEMTs [3]–[7] have been extensively researched upon and are already commercially available for the 200-600 V power applications. However, these devices suffer from poor scalability, limited breakdown voltage compared to the GaN capability, and reliability issues [8], [9].

A vertical structure is more suitable for high power applications as it offers better scalability, higher current density, larger breakdown voltages, and lower sensitivity to traps and surface states [10]. Recently reported vertical devices on low defect density epitaxial layers grown on high-quality bulk GaN substrates have reached nearly ideal performance, thus reaffirming the choice of GaN vertical devices for future power applications [11]–[17]. However, these substrates are available only in small diameters and are prohibitively expensive. Hence, for the future adoption and commercialization of GaN vertical power devices, it would be desirable to develop such devices in low-cost substrates, such as Silicon. Recent demonstrations of GaN-on-Si p-i-n diodes [18]–[23], as well as vertical GaN-on-Si power MOSFETs, reaching a BV of 645 V [24],

This work was supported the European Research Council (ERC) under the ERC Grant Agreement 679425. R. A. Khadar, C. Liu, and E. Matioli are with the Power and Wide-band-gap Electronics Research Laboratory, École Polytechnique Fédérale de Lausanne, CH-1015 Lausanne, Switzerland. L. Zhang, P. Xiang, and K. Cheng are with Enkris Semiconductor, Inc.

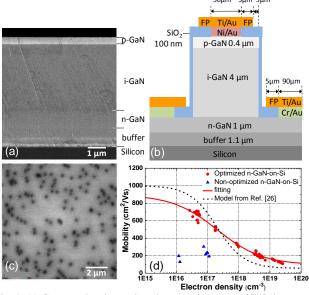

Fig. 1. (a) Cross sectional scanning electron microscope (SEM) image of the GaN-on-Si wafer revealing clearly the different layers. (b) Simplified schematic of the fabricated p-i-n diode on GaN-on-Si. (c) Cathodoluminescence (CL) image of the as-grown GaN layer on Si. (d) Electron mobility versus electron density of the optimized and non-optimized n-GaN layers compared against the model from Ref. [26].

reveal the great promise of such substrates. Fully vertical p-i-n diodes have also been demonstrated by substrate removal reaching a BV up to 500 V [19]. However, these values are much below the performances demonstrated in bulk GaN and for their use in practical applications, both the BV and the  $R_{\rm on,sp}$  need to be significantly improved.

In this letter, we report quasi-vertical GaN-on-Si p-i-n diodes with BV of 820 V, achieved using a 4  $\mu$ m-thick GaN drift layer while earlier reports on p-i-n diodes fabricated on GaN-on-Si used drift layer thicknesses of about 2-2.7  $\mu$ m [18]–[22]. The doping of the GaN drift layer was optimized, leading to a remarkable electron mobility of 720 cm²/Vs with a Si doping level of  $2\times10^{16}$  cm<sup>-3</sup>. In the forward conduction, these diodes demonstrated a very low  $R_{\rm on,sp}$  of 0.33 m $\Omega$ cm² at 6.4 V and current density over 10 kA/cm² at 10 V with excellent stability at higher temperatures. In reverse bias, the devices presented low leakage current of  $4\times10^{-2}$  A/cm² at -500 V. These results yield a BFOM of 2.0 GW/cm² which is more than 6x-larger than the best value reported to date in GaN-on-Si p-i-n diodes [19].

© 2018 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

### II. DEVICE STRUCTURE AND FABRICATION

The p-i-n epitaxial structure consisted of 0.4  $\mu$ m-thick p-GaN ( $N_A \sim 3 \times 10^{17}$  cm<sup>-3</sup>), 4  $\mu$ m-thick GaN drift layer ( $N_D \sim 2 \times 10^{16}$  cm<sup>-3</sup>), 1  $\mu$ m-thick n-GaN ( $N_D \sim 10^{19}$  cm<sup>-3</sup>) and 1.1  $\mu$ m-thick buffer layer grown on p-type Si, as shown in Fig. 1(a) and (b). All the GaN layers were grown by metal-organic chemical vapor deposition (MOCVD) on 6-inch Si (111) substrates.

High quality buffer layers with low defect densities are important to grow thick GaN-on-Si with low threading dislocation densities, especially the AlN nucleation layer. AlN on Si with high crystalline quality with (002) X-ray rocking curve (XRC) of less than 1000 arc sec and smooth surface was obtained by optimizing the AlN growth. With high-quality buffer layer, thick GaN on Si was grown without relaxation of the compressive stress during growth. High-resolution x-ray diffraction (HRXRD) was used to characterize the crystalline quality of the as-grown p-i-n structure on Si. The full width at half maximum (FWHM) of the X-ray omega rocking curves for (002) and (102) orientations were 235 arcsec and 307 arcsec, respectively. From the FWHM values we estimated a threading dislocation density (TDD) of 2.95×108 cm<sup>-2</sup> through empirical equations from Refs. [25]. A similar TDD of about 2.0×108 cm<sup>-2</sup> was obtained from cathodoluminescence (CL) microscopy of the GaN grown on Si as shown in Fig. 1(c). In addition to TDD, impurity control such as carbon, silicon and oxygen is also critical. To achieve high breakdown voltage and low leakage current in GaN diodes, the background impurities, including both Si and O, have to be controlled to less than 1×10<sup>16</sup> cm<sup>-3</sup>. Large O or Si background concentrations, for example, in the range of  $1 \times 10^{17}$  cm<sup>-3</sup>, require intentional carbon doping to compensate the shallow donors of Si or O in order to achieve high breakdown voltage. However, the presence of C may significantly degrade the electron mobility of Si-doped n-GaN. As it is shown in Fig.1(d), the non-optimized n-type GaN sample, which has a relatively high C concentration of ~  $8\times10^{16}$  cm<sup>-3</sup>, presented an electron mobility of ~ 200 cm<sup>2</sup>/Vs at a doping level of  $1\times10^{17}$  cm<sup>-3</sup>. By tuning the growth parameters, the C concentration was reduced to less than  $1 \times 10^{16}$  cm<sup>-3</sup>, leading to a much larger mobility of 720 cm<sup>2</sup>/Vs at a Si doping level of 2×10<sup>16</sup> cm<sup>-3</sup>. Furthermore, from SIMS measurements of our un-intentionally doped GaN samples, the Si or O background level was below 1×10<sup>16</sup> cm<sup>-3</sup>, and thus not requiring extra C doping. Fig. 1(d) shows the mobility of n-GaN/i-GaN/buffer/Si samples as a function of electron density obtained using an Accent HL5500 Hall system [26].

The fabrication process of the quasi-vertical diodes (Fig. 1(b)) started with the activation of p-GaN by thermal annealing in  $N_2$  ambient at 750 °C for 15 min. The p-electrode layer was formed by Ni (20 nm)/Au (50 nm) subsequently annealed at 480 °C in  $N_2/O_2$  ambient for 10 min for ohmic contact formation. This was followed by mesa isolation through a deep etching of GaN using inductively coupled plasma-reactive ion etching (ICP-RIE) to access the bottom n-GaN layer. The sample was then treated with 25% Tetra Methyl Ammonium Hydroxide (TMAH) at 85 °C for 1 hour to smoothen the sidewalls and heal the damages occurred during the deep-etching step. Cr (50 nm)/Au (250 nm) bi-layer was deposited for ohmic contact to n-GaN. The etched sidewalls

were passivated with 100nm-thick SiO<sub>2</sub>, deposited by atomic layer deposition (ALD), and the field plates (FP) were formed with Ti (50 nm)/Au (300 nm) bi-layer (Fig. 1(b)).

### III. RESULTS AND DISCUSSION

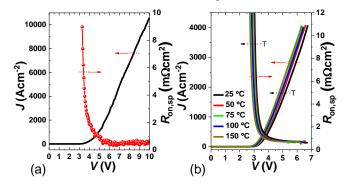

Fig. 2(a) shows the forward current density versus voltage (J-V) characteristics and the specific on-resistance  $(R_{\text{on,sp}})$  of p-i-n diodes with passivation and FP. We observed no difference in the forward characteristics between the passivated and the un-passivated devices. The diode anode diameter was 56  $\mu$ m. The turn-on voltage  $(V_{\text{on}})$ , extracted at a current density of 20 A/cm² was 3.3 V which is close to the bandgap of GaN. The  $R_{\text{on,sp}}$  extracted from the forward J-V plot at 6.4 V was 0.33 m $\Omega$ cm², while the equivalent on-resistance calculated by voltage over current at 6.4 V was 1.56 m $\Omega$ cm². For quasi-vertical diodes, the on-resistance is mainly determined by the current crowding in the n-GaN layer towards the n-GaN contact [27], which was significantly alleviated in these devices due to the highly doped 1  $\mu$ m-thick n-GaN layer presenting a low sheet resistance of 26  $\Omega$ cm. For larger anode contacts, we

Fig. 2. (a) Forward J-V and specific on-resistance measurement. (b) Forward J-V and specific on-resistance measurement at various temperatures.

observed an increase in  $R_{\rm on,sp}$  since the higher current leads to a much more severe current crowding at the n-GaN layer. Current crowding can be further reduced by modifying the device structure from a quasi- to a fully-vertical structure, by substrate removal for instance [20]. Another main contribution to the  $R_{\rm on,sp}$  comes from the thick drift layer, which was minimized in our devices by optimizing the electron mobility and doping of the GaN drift layer. This resulted in a much smaller  $R_{\rm on,sp}$  than in previous reports of GaN-on-Si p-i-n diodes, even compared to fully vertical structures [18] and to devices with larger doping in n-GaN layers [19].

Our diodes presented a very high current density (normalized by the anode surface), larger than 10 kA/cm² at 10 V, which to our knowledge is the highest value reported for GaN diodes grown on foreign substrates [18]–[23], [28]–[30]. Despite the thick GaN layers grown on Si, a small ideality factor of 2.56 was extracted at a forward voltage of 2.4 V, reflecting the excellent quality of the epitaxial layers.

Fig. 2(b) shows the temperature dependence of the forward J-V characteristics. As expected, the turn-on voltage decreased at higher temperatures due to bandgap narrowing and thermally-enhanced carrier diffusion. We observed very little change in  $R_{\text{on,sp}}$  and drift in the current density with temperature, as opposed to degradation or inconsistencies observed in

previously reported papers [19], [20]. These excellent results are comparable to fully vertical diodes fabricated on GaN substrates [14], [36].

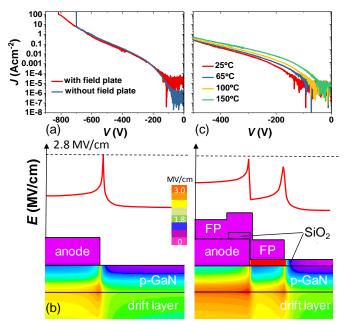

Fig. 3(a) shows the reverse current density versus voltage (J-V) curve of the diode in logarithmic scale, performed on an insulating chuck. The BV of the diode without FP was 700 V, which was significantly improved to 820 V by the 5  $\mu$ m-long FP (Fig. 1(b)), corresponding to an average electric field in the

Fig. 3. (a) Reverse *J-V* measurement (b) Simulated electric field in a non-terminated (at 690 V) and terminated diode (at 823 V). (c) Reverse *J-V* measurement at various temperatures.

drift layer of 2.1 MV/cm. To the best of our knowledge, this is the highest BV among all previously reported quasi/fully-vertical GaN-on-Si p-i-n diodes. This enhancement was confirmed by 2D-TCAD simulations as shown in Fig 3(b). For a non-terminated anode, the electric field at a reverse bias of 690 V peaks at the edge of the electrode at about 2.8 MV/cm. The field plate spreads the electric field in two peaks at the edge of the anode and of the FP, resulting in an electric field peak of  $\sim 2.7$  MV/cm at a much higher voltage of 823 V.

The measured leakage current density was ~ 5×10<sup>-3</sup> A/cm<sup>2</sup> and  $\sim 4 \times 10^{-2}$  A/cm<sup>2</sup> at -300 V and -500 V, respectively. Such low reverse leakage current can be attributed to the high crystalline quality of the GaN epi layers grown on Si substrate, since it is dominated by space charge limited current (SCLC), mainly due to traps in the thick epi-layers [21], [32]. According to the model from Ref. [32], the epitaxial GaN grown on Si contains both acceptor- as well as donor- type traps. At low reverse voltages, the acceptor traps start getting filled with electrons. As the reverse voltage increases, the Fermi level moves up towards the conduction band and the ionized donor traps start getting filled. At the point where all the trap states get filled, denoting the onset of the trap filled voltage, the current increases sharply as the Fermi level reaches the conduction band. The leakage current in log-scale, prior to the trap filled voltage, is proportional to  $V^n$ . A value of  $n \sim 6.39$  was obtained by fitting the Fig. 3(a), which is comparable to previous reports of p-i-n diodes on GaN-on-Si [20], [21]. We have not observed

a significant difference in leakage current with and without passivation, which we believe is due to the effective healing of the etching damages on the sidewalls by the TMAH treatment [33]. Fig. 3(c) shows the reverse *J-V* characteristics of the diodes at different temperatures, revealing a slight increase in leakage current with temperature due to thermal carrier generation.

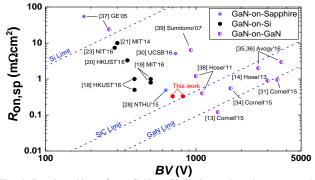

The performance of our diodes was benchmarked against other GaN vertical diodes reported in the literature in a  $R_{\rm on,sp}$  vs BV plot as shown in Fig. 4 [13,14,18-21,23,28,30,31,33-38] . The excellent BV of 700 V (without field plate) and 820 V of our diodes, with a small  $R_{\rm on,sp}$  of 0.33 m $\Omega$ cm<sup>2</sup>, leads to a BFOM value of 2.0 GW/cm<sup>2</sup>, which is more than 6x-larger than the best value reported for p-i-n diodes fabricated on GaN-on-Si [19].

Fig. 4. Benchmarking of our GaN-on-Si diodes against those reported in literature using  $R_{\text{on,sp}}$  and BV as parameters.

### IV. CONCLUSIONS

In this work we demonstrated a high performance quasi-vertical GaN-on-Si p-i-n diode with record performance, achieved with a drift layer with 4  $\mu$ m-thick drift layer. The growth and doping of the GaN drift layer were optimized, leading to a remarkable electron mobility of 720 cm²/Vs for a doping level of  $2\times10^{16}$  cm³. A low  $R_{\rm on,sp}$  of 0.33 m $\Omega$ cm², high forward current density of 10 kA/cm² at 10 V, and a record breakdown voltage of 820 V were achieved. As a result, our diodes presented a BFOM of 2.0 GW/cm², which is the best achieved on GaN-on–Si diodes. These results demonstrate the enormous potential of GaN-on-Si diodes for low-cost high-voltage power devices.

# V. ACKNOWLEDGEMENT

We would like to thank the staff at CMi and ICMP cleanrooms at EPFL for technical support and advice.

## VI. REFERENCES

- S. Chowdhury, "Vertical Gallium Nitride Technology," in *Power GaN Devices*, Springer, Cham, 2017, pp. 101–121.

- [2] S. Chowdhury, Z. Stum, Z. D. Li, K. Ueno, and T. P. Chow, "Comparison of 600V Si, SiC and GaN Power Devices," *Mater. Sci. Forum*, vol. 778–780, pp. 971–974, 2014, doi: 10.4028/www.scientific.net/MSF.778-780.971.

- [3] Y. Dora, A. Chakraborty, L. Mccarthy, S. Keller, S. P. Denbaars, and U. K. Mishra, "High Breakdown Voltage Achieved on AlGaN/GaN HEMTs With Integrated Slant Field Plates," *IEEE Electron Device Lett.*, vol. 27, no. 9, pp. 713–715, Sep. 2006, doi: 10.1109/LED.2006.881020.

- [4] S. Karmalkar and U. K. Mishra, "Enhancement of breakdown voltage in AlGaN/GaN high electron mobility transistors using a field plate,"

- *IEEE Trans. Electron Devices*, vol. 48, no. 8, pp. 1515–1521, Aug. 2001, doi: 10.1109/16.936500.

- [5] W. Saito, Y. Takada, M. Kuraguchi, K. Tsuda, I. Omura, T. Ogura, and H. Ohashi, "High breakdown voltage AlGaN-GaN power-HEMT design and high current density switching behavior," *IEEE Trans. Electron Devices*, vol. 50, no. 12, pp. 2528–2531, Dec. 2003, doi: 10.1109/TED.2003.819248.

- [6] J. Ma and E. Matioli, "Slanted Tri-gates for High-Voltage GaN Power Devices," *IEEE Electron Device Lett.*, vol. PP, no. 99, pp. 1–1, 2017, doi: 10.1109/LED.2017.2731799.

- [7] J. Ma and E. Matioli, "High Performance Tri-Gate GaN Power MOSHEMTs on Silicon Substrate," *IEEE Electron Device Lett.*, vol. 38, no. 3, pp. 367–370, Mar. 2017, doi: 10.1109/LED.2017.2661755.

- [8] W. Saito, "Reliability of GaN-HEMTs for high-voltage switching applications," in 2011 Int. Reliab. Phys. Symp., Apr. 2011, p. 4E.1.1-4E.1.5, doi: 10.1109/IRPS.2011.5784510.

- [9] J. Joh and J. A. del Alamo, "A Current-Transient Methodology for Trap Analysis for GaN High Electron Mobility Transistors," *IEEE Trans. Electron Devices*, vol. 58, no. 1, pp. 132–140, Jan. 2011, doi: 10.1109/TED.2010.2087339.

- [10] B. J. Baliga, "Trends in power semiconductor devices," *IEEE Trans. Electron Devices*, vol. 43, no. 10, pp. 1717–1731, Oct. 1996, doi: 10.1109/16.536818.

- [11] T. Kachi, "State-of-the-art GaN vertical power devices," in 2015 IEEE Int. Electron Devices Meet. IEDM, Dec. 2015, p. 16.1.1-16.1.4, doi: 10.1109/IEDM.2015.7409708.

- [12] T. T. Kao, J. Kim, Y. C. Lee, M. H. Ji, T. Detchprohm, R. D. Dupuis, and S. C. Shen, "Homojunction GaN pin Rectifiers with Ultra-low On-state Resistance," CS MANT ECH Tech Dig, p. 157, 2014.

- [13] Z. Hu, K. Nomoto, B. Song, M. Zhu, M. Qi, M. Pan, X. Gao, V. Protasenko, D. Jena, and H. G. Xing, "Near unity ideality factor and Shockley-Read-Hall lifetime in GaN-on-GaN p-n diodes with avalanche breakdown," *Appl. Phys. Lett.*, vol. 107, no. 24, p. 243501, Dec. 2015, doi: 10.1063/1.4937436.

- [14] Y. Hatakeyama, K. Nomoto, A. Terano, N. Kaneda, T. Tsuchiya, T. Mishima, and T. Nakamura, "High-Breakdown-Voltage and Low-Specific-on-Resistance GaN p-n Junction Diodes on Free-Standing GaN Substrates Fabricated Through Low-Damage Field-Plate Process," *Jpn. J. Appl. Phys.*, vol. 52, no. 2R, p. 028007, Feb. 2013, doi: 10.7567/JJAP.52.028007.

- [15] W. Li, K. Nomoto, M. Pilla, M. Pan, X. Gao, D. Jena, and H. G. Xing, "Design and Realization of GaN Trench Junction-Barrier-Schottky-Diodes," *IEEE Trans. Electron Devices*, vol. PP, no. 99, pp. 1–7, 2017, doi: 10.1109/TED.2017.2662702.

- [16] Y. Zhang, Z. Liu, M. J. Tadjer, M. Sun, D. Piedra, C. Hatem, T. J. Anderson, L. E. Luna, A. Nath, A. D. Koehler, H. Okumura, J. Hu, X. Zhang, X. Gao, B. N. Feigelson, K. D. Hobart, and T. Palacios, "Vertical GaN Junction Barrier Schottky Rectifiers by Selective Ion Implantation," *IEEE Electron Device Lett.*, vol. 38, no. 8, pp. 1097–1100, Aug. 2017, doi: 10.1109/LED.2017.2720689.

- [17] M. Sun, Y. Zhang, X. Gao, and T. Palacios, "High-Performance GaN Vertical Fin Power Transistors on Bulk GaN Substrates," *IEEE Electron Device Lett.*, vol. 38, no. 4, pp. 509–512, Apr. 2017, doi: 10.1109/LED.2017.2670925.

- [18] X. Zhang, X. Zou, X. Lu, C. W. Tang, and K. M. Lau, "Fully- and Quasi-Vertical GaN-on-Si p-i-n Diodes: High Performance and Comprehensive Comparison," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 809–815, Mar. 2017, doi: 10.1109/TED.2017.2647990.

- [19] Y. Zhang, D. Piedra, M. Sun, J. Hennig, A. Dadgar, L. Yu, and T. Palacios, "High-Performance 500 V Quasi- and Fully-Vertical GaN-on-Si pn Diodes," *IEEE Electron Device Lett.*, vol. 38, no. 2, pp. 248–251, Feb. 2017, doi: 10.1109/LED.2016.2646669.

- [20] X. Zou, X. Zhang, X. Lu, C. W. Tang, and K. M. Lau, "Fully Vertical GaN p-i-n Diodes Using GaN-on-Si Epilayers," *IEEE Electron Device* Lett., vol. 37, no. 5, pp. 636–639, May 2016, doi: 10.1109/LED.2016.2548488.

- [21] Y. Zhang, M. Sun, D. Piedra, M. Azize, X. Zhang, T. Fujishima, and T. Palacios, "GaN-on-Si Vertical Schottky and p-n Diodes," *IEEE Electron Device Lett.*, vol. 35, no. 6, pp. 618–620, Jun. 2014, doi: 10.1109/LED.2014.2314637.

- [22] X. Zou, X. Zhang, X. Lu, C. W. Tang, and K. M. Lau, "Breakdown Ruggedness of Quasi-Vertical GaN-Based p-i-n Diodes on Si Substrates," *IEEE Electron Device Lett.*, vol. 37, no. 9, pp. 1158–1161, Sep. 2016, doi: 10.1109/LED.2016.2594821.

- [23] S. Mase, Y. Urayama, T. Hamada, J. J. Freedsman, and T. Egawa "Novel fully vertical GaN p-n diode on Si substrate grown by metalorganic chemical vapor deposition," *Appl. Phys. Express*, vol. 9, no. 11, p. 111005, Oct. 2016, doi: 10.7567/APEX.9.111005.

- [24] C. Liu, R. A. Khadar, and E. Matioli, "GaN-on-Si Quasi-Vertical Power MOSFETs," *IEEE Electron Device Lett.*, vol. PP, no. 99, pp. 1–1, 2017, doi: 10.1109/LED.2017.2779445.

- [25] P. Gay, P. B. Hirsch, and A. Kelly, "The estimation of dislocation densities in metals from X-ray data," *Acta Metall.*, vol. 1, no. 3, pp. 315–319, May 1953, doi: 10.1016/0001-6160(53)90106-0.

- [26] T. T. Mnatsakanov, M. E. Levinshtein, L. I. Pomortseva, S. N. Yurkov, G. S. Simin, and M. Asif Khan, "Carrier mobility model for GaN," *Solid-State Electron.*, vol. 47, no. 1, pp. 111–115, Jan. 2003, doi: 10.1016/S0038-1101(02)00256-3.

- [27] Y. Zhang, M. Sun, D. Piedra, J. Hennig, A. Dadgar, and T. Palacios, "Reduction of on-resistance and current crowding in quasi-vertical GaN power diodes," *Appl. Phys. Lett.*, vol. 111, no. 16, p. 163506, Oct. 2017, doi: 10.1063/1.4989599.

- [28] B. S. Zheng, P. Y. Chen, C. J. Yu, Y. F. Chang, C. L. Ho, M. C. Wu, and K. C. Hsieh, "Suppression of Current Leakage Along Mesa Surfaces in GaN-Based p-i-n Diodes," *IEEE Electron Device Lett.*, vol. 36, no. 9, pp. 932–934, Sep. 2015, doi: 10.1109/LED.2015.2458899.

- [29] Y. F. Chang, C. L. Liao, B. S. Zheng, J. Z. Liu, C. L. Ho, K. C. Hsieh, and M. C. Wu, "Using Two-Step Mesa to Prevent the Effects of Sidewall Defects on the GaN p-i-n Diodes," *IEEE J. Quantum Electron.*, vol. 51, no. 10, pp. 1–6, Oct. 2015, doi: 10.1109/JQE.2015.2479465.

- [30] C. Gupta, Y. Enatsu, G. Gupta, S. Keller, and U. K. Mishra, "High breakdown voltage p-n diodes on GaN on sapphire by MOCVD," *Phys. Status Solidi A*, vol. 213, no. 4, pp. 878–882, Apr. 2016, doi: 10.1002/pssa.201532554.

- [31] K. Nomoto, Z. Hu, B. Song, M. Zhu, M. Qi, R. Yan, V. Protasenko, E. Imhoff, J. Kuo, N. Kaneda, T. Mishima, T. Nakamura, D. Jena, and H. G. Xing, "GaN-on-GaN p-n power diodes with 3.48 kV and 0.95 mΩ-cm²: A record high figure-of-merit of 12.8 GW/cm²," in 2015 IEEE Int. Electron Devices Meet. IEDM, Dec. 2015, p. 9.7.1-9.7.4, doi: 10.1109/IEDM.2015.7409665.

- [32] C. Zhou, Q. Jiang, S. Huang, and K. J. Chen, "Vertical Leakage/Breakdown Mechanisms in AlGaN/GaN-on-Si Devices," *IEEE Electron Device Lett.*, vol. 33, no. 8, pp. 1132–1134, Aug. 2012, doi: 10.1109/LED.2012.2200874.

- [33] Y. Zhang, M. Sun, H. Y. Wong, Y. Lin, P. Srivastava, C. Hatem, M. Azize, D. Piedra, L. Yu, T. Sumitomo, N. A. de Braga, R. V. Mickevicius, and T. Palacios, "Origin and Control of OFF-State Leakage Current in GaN-on-Si Vertical Diodes," *IEEE Trans. Electron Devices*, vol. 62, no. 7, pp. 2155–2161, Jul. 2015, doi: 10.1109/TED.2015.2426711.

- [34] K. Nomoto, B. Song, Z. Hu, M. Zhu, M. Qi, N. Kaneda, T. Mishima, T. Nakamura, D. Jena, and H. G. Xing, "1.7-kV and 0.55-mΩcm² GaN p-n Diodes on Bulk GaN Substrates With Avalanche Capability," *IEEE Electron Device Lett.*, vol. 37, no. 2, pp. 161–164, Feb. 2016, doi: 10.1109/LED.2015.2506638.

- [35] I. C. Kizilyalli, A. P. Edwards, O. Aktas, T. Prunty, and D. Bour, "Vertical Power p-n Diodes Based on Bulk GaN," *IEEE Trans. Electron Devices*, vol. 62, no. 2, pp. 414–422, Feb. 2015, doi: 10.1109/TED.2014.2360861.

- [36] I. C. Kizilyalli, A. P. Edwards, H. Nie, D. Disney, and D. Bour, "High Voltage Vertical GaN p-n Diodes With Avalanche Capability," *IEEE Trans. Electron Devices*, vol. 60, no. 10, pp. 3067–3070, Oct. 2013, doi: 10.1109/TED.2013.2266664.

- [37] X. A. Cao, H. Lu, S. F. LeBoeuf, C. Cowen, S. D. Arthur and W. Wang "Growth and characterization of GaN PiN rectifiers on free-standing GaN: Applied Physics Letters: Vol 87, No 5." [Online]. Available: http://aip.scitation.org/doi/full/10.1063/1.2001738. [Accessed: 10-Aug-2017].

- [38] Y. Hatakeyama, K. Nomoto, N. Kaneda, T. Kawano, T. Mishima, and T. Nakamura, "Over 3.0 Figure-of-Merit GaN p-n Junction Diodes on Free-Standing GaN Substrates," *IEEE Electron Device Lett.*, vol. 32, no. 12, pp. 1674–1676, Dec. 2011, doi: 10.1109/LED.2011.2167125.

- [39] Y. Yoshizumi, S. Hashimoto, T. Tanabe, and M. Kiyama, "High-breakdown-voltage pn-junction diodes on GaN substrates," *J. Cryst. Growth*, vol. 298, pp. 875–878, Jan. 2007, doi: 10.1016/j.jcrysgro.2006.10.246.