## This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# A 0.18-µm CMOS voltage-to-frequency converter with low circuit sensitivity

Koay, Kuan Chuang; Chan, Pak Kwong

2018

Koay, K. C., & Chan, P. K. (2018). A 0.18-µm CMOS voltage-to-frequency converter with low circuit sensitivity. IEEE Sensors Journal, 18(15), 6245-6253. doi:10.1109/JSEN.2018.2846635

https://hdl.handle.net/10356/105578

### https://doi.org/10.1109/JSEN.2018.2846635

© 2018 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. The published version is available at: https://doi.org/10.1109/JSEN.2018.2846635

Downloaded on 27 Aug 2022 15:12:13 SGT

## A 0.18 µm CMOS Voltage-to-Frequency Converter with Low Circuit Sensitivity

K.C. Koay, Student Member, IEEE, and P.K. Chan, Senior Member, IEEE

Abstract—A process, voltage and temperature insensitive resistor-to-frequency converter is proposed. This insensitivity is achieved by matching the current defining capacitor in a novel switched-capacitor (SC) voltage-to-current (V-I) converter with the integrating capacitor in a conventional relaxation oscillator. Implemented in 0.18  $\mu$ m CMOS technology, the SC V-I converter together with the relaxation oscillator and voltage regulator occupies 0.45mm<sup>2</sup>. The proposed work has shown a sensitivity of 199.9 Hz/( $\mu\Omega/\Omega$ ) which is based on a center frequency of 125kHz. Testing with a commercial sensor, the sensor interface has demonstrated a sensitivity of 1.269 kHz/psi. The sensor interface consumes only 112.5  $\mu$ W at 1.5V power supply. Therefore, it is suitable for Internet-of-Things applications.

*Index Terms*— Transconductor, switched-capacitor circuit, voltage-to-current converter, voltage-to-frequency converter, Internet-of-Things

#### I. INTRODUCTION

AS the Internet-of-Things becomes more popular, a robust and lowpower sensor network system is highly desirable. Resistive sensors are widely preferred due to its insensitive to electromagnetic interference, relatively higher immunity against environmental parasitic capacitances, low cost and ease of integration [1], [2]. They are typically used in physical force related to sensing parameters such as pressure, stress and strain. Any change in the physical force will be converted into change in resistance. To convert this variation of resistance into change in voltage, the resistive sensors are typically configured in a Wheatstone Bridge configuration.

The maximum change in resistance for the resistive sensors are typically 2% in terms of its bridge resistance. This corresponds to a change of 24mV for a full Wheatstone Bridge sensor with a supply voltage of 1.2V. Hence, this change of voltage will often be amplified and converted into digital code for transmission to permit ease of maintaining signal fidelity [3]–[7]. Another way of maintaining signal fidelity is to convert this voltage signal into frequency domain signal [8]–[13]. The key benefits of this conversion scheme are that the output signal is having higher noise immunity compared to voltage domain signal and it allows ease of interfacing with digital circuit on the basis of little or no synchronization [11], [14]. Conventional voltage-to-frequency (VF) converter often requires a resistor for current conversion and a capacitor to convert the current into frequency

domain signal through a relaxation oscillator. Due to the difference in device types used, the output frequency will vary widely across process and temperature variations. This in turn requires more elaborate calibration process, causing higher time to market and increase the production cost.

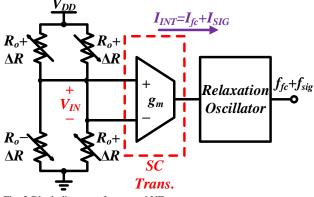

To minimize the process variation caused by the mismatch between device types, a clocked VF converter was proposed [15]. In this work, the switched-capacitor (SC) technique is utilized to translate voltage input into frequency output. This eliminates the need of resistor, thus providing better stability across process and temperature variations. However, when the output frequency is quantized, the quantization effect is worsened when the output frequency approaches the clock frequency. To eliminate this issue, a SC VF converter is proposed. This converter will convert the input voltage into a continuous-time current through a SC voltage-to-current converter with the embedded integrator. The smoothed signal current is then injected into an integrating capacitor and converted into a frequency domain signal. As a result, this eliminates the quantization issue in [15] while maintaining the output frequency stability across process variation and temperature variation. Fig. 2 shows the block diagram of the proposed VF converter.

In Section II, the respective building block will be described. The measurement results will be presented in Section III. In Section IV, the performance of SC VF converter will be compared with other state-of-the-art works. Finally, the concluding remark will be drawn in Section V.

#### II. PROPOSED SENSOR INTERFACE

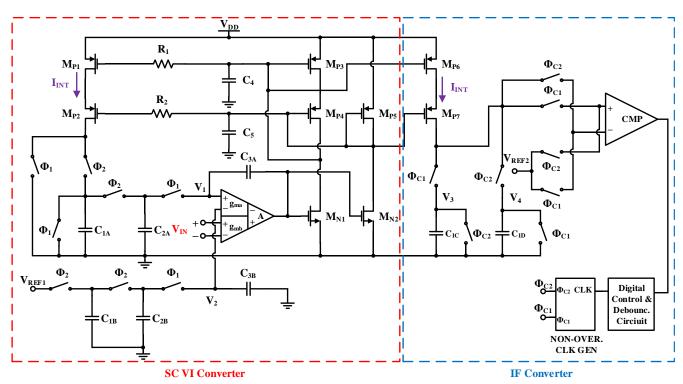

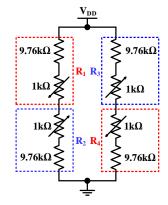

Fig. 1 shows the proposed sensor interface that converts a Wheatstone Bridge sensor output voltage into a frequency domain signal output. The proposed sensor interface consists of two main blocks, which are the VI converter and the current-to-frequency (IF) converter. Table I shows the capacitance of each capacitor used in the design. The Wheatstone Bridge sensor translates the change of physical parameter, such as pressure in this case, into the resistive change on each arm of the Bridge.

The differential output of a full Wheatstone bridge is given as

$$V_{IN} = \frac{\Delta R}{R} V_{DD} \tag{1}$$

where  $V_{IN}$  is the differential output voltage of sensor that will be processed by the proposed interface,  $\Delta R$  is the variation of resistance relative to the bridge resistance, R, and  $V_{DD}$  is the supply voltage of the Wheatstone Bridge. As shown by (1), the output voltage, which refers to the input voltage of the proposed sensor interface, is linearly proportional to the supply voltage. In order to maintain a stable supply, a low dropout (LDO) regulator with an output voltage of 1.2V is

The authors are with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798. (e-mail: koay0013@e.ntu.edu.sg; epkchan@ntu.edu.sg).

Fig. 1 Proposed SC VF converter.

adopted to power the Wheatstone Bridge sensor. In this design, the sensor system is targeted to achieve untrimmed accuracy of less than 1.5%, as the conventional pressure sensor will have a span variation of 5% full scale span variation. Since the error caused by the delay,  $\tau$ , is  $\tau \times f_{OUT}^2$ , in conjunction with the comparator delay in the range of 10ns

Fig. 2 Block diagram of proposed VF converter.

to 25ns, the maximum output frequency is chosen as 185kHz to limit the error to 0.5%. Therefore, the chosen sensitivity is based on the input range, the ratio of the input pairs' transconductance, the current mirror ratio and the capacitor ratio. To maintain good matching for the current mirror and capacitor, their ratio is fixed as 1/1. For the input pair, a gain of 2 is adopted in the design. With this design criteria, when the sensitivity is chosen as  $199.9\text{Hz/}(\mu\Omega/\Omega)$ , this gives a theoretical center frequency of 125kHz with an input range of  $\pm 0.02 \Omega/\Omega$ .

The design of VI converter will be discussed in subsection A whereas the IF converter will be discussed in subsection B. The chopping Differential Difference Amplifier (DDA) that is used in the VI converter will be discussed in the subsection C.

TABLE ISIZING OF CAPACITORS IN THE PROPOSED SC VI CONVERTERCap.Size (pF)Cap.Size (pF) $C_{1A}, C_{1B}, C_{1C}, C_{1D}$ 20 $C_{3A}, C_{3B}$ 11 $C_{2A}, C_{2B}$ 2 $C_4, C_5$ 1

2

#### A. VI Converter

To transform the sensor voltage into current, a SC VI converter which is based on [16], [17] coupled with a DDA [18], is used. In this work, the SC VI converter is modified to a quasi-differential structure so as to reduce the charge injection as well as clock feedthrough effect. The resistor-capacitor low-pass filters formed by resistors R<sub>1</sub>, C<sub>4</sub> and R<sub>2</sub>, C5 are used to filter the switching noise coupled from the drain of MP1 and  $M_{P2}$  to the gate of  $M_{P3}$  and  $M_{P4}$ . During  $\Phi_1$ ,  $C_{1A}$  is being discharged to ground while C2A is being forced to VREF1+2VIN because the DDA is designed to have a gain of 2. The detailed discussion on the design of DDA will be discussed in Section II-C. At this juncture, C<sub>2B</sub> is disconnected to C1B and connected to C3B. When the VI converter goes into  $\Phi_2$ , C<sub>1A</sub> together with C<sub>2A</sub> is connected to the drain terminal of MP2. It is being charged up by a constant current, IINT, while C1B and C<sub>2B</sub> are being charged up by V<sub>REF1</sub>. In next clock cycle, C<sub>2A</sub> will then be connected to V1. The excess positive charge of C3A will be injected into C<sub>2A</sub> if the voltage on C<sub>2A</sub> is lower than virtual ground, thus increasing the charging current I<sub>INT</sub>. On the contrary, if the voltage on  $C_{2A}$  is higher than virtual ground, the excess positive charge on  $C_{2A}$ will be injected into C<sub>3A</sub>, thus decreasing I<sub>INT</sub>.

From [17], the expression for the charging current  $I_{INT}$  under a clock with 50% duty cycle can be given as

$$I_{INT} = 2(V_{REF1} + 2V_{IN})C_{1A}f_{CLK} = I_{DC} + I_{SIG}$$

(2)

where  $V_{REF1}$  is the reference voltage employed to generate a dc reference current. This reference current will provide a center frequency for the VF converter. The voltage is chosen to be 150mV in this design.  $f_{CLK}$  is the clock frequency generated by off-chip crystal oscillator and chosen to be 500kHz. The I<sub>DC</sub> and I<sub>SIG</sub> are the DC current generated from voltage reference and the signal current resulted from the differential output voltage of the Wheatstone Bridge sensor, respectively. Referenced from (2), the targeted design values for I<sub>DC</sub> and I<sub>SIG</sub> are 3µA and ±0.96 µA, respectively in this design.

#### B. IF Converter

To convert IINT into a frequency domain signal, a relaxation oscillator is needed. This relaxation oscillator makes use of a self-chopped topology similar to [19]. The goal is to reduce the offset effect and lowfrequency noise introduced by the comparator. During  $\Phi_{C1}$ , the I<sub>INT</sub> is injected into C<sub>1C</sub> while C<sub>1D</sub> is being discharged to ground. C<sub>1C</sub> is also connected to the non-inverting input of comparator while V<sub>REF2</sub> is connected to the inverting input of comparator. At this juncture, the output of comparator is low. When the voltage V<sub>3</sub> is being charged up to pass VREF2+VOFFSET\_COMP, the output of comparator will be switched to high. The VOFFSET\_COMP is the offset voltage modelled as a DC voltage in series with the VREF2. Besides, a debouncing circuit is used to prevent the noise from causing unwanted switching activity by maintaining the comparator output for about 10ns after each switching activity. The debouncing circuit's output will then go through a nonoverlapping clock generator to set the SR latch output to high. The SR latch is used as the output signal for VF converter. This SR latch output will go through another non-overlapping clock generator to trigger  $\Phi_{C2}$ to high and  $\Phi_{C1}$  to low. In  $\Phi_{C2}$ ,  $C_{1D}$  will be charged up by I<sub>INT</sub> while C<sub>1C</sub> will be discharged to ground. In this phase, V<sub>4</sub> will be connected to the inverting input of the comparator while VREF2 will be connected to the non-inverting input of comparator. When V4 is charged up to the value of  $V_{REF2} - V_{OFFSET_COMP}$ , the output of comparator will switch to low, thus setting  $\Phi_{C1}$  to high and  $\Phi_{C2}$  to low. The output frequency can be obtained as follows:

$$f_{Q} = \frac{2(V_{REF1} + 2\Delta R / R)C_{1A}f_{CLK}}{C_{1C}(V_{REF2} + V_{OFF\_COMP}) + C_{1D}(V_{REF2} - V_{OFF\_COMP})}$$

(3)

$$f_{Q} = \frac{2(V_{REF1} + 2V_{IN})C_{1A}f_{CLK}}{C_{1C}(V_{REF2} + V_{OFF\_COMP}) + C_{1D}(V_{REF2} - V_{OFF\_COMP})}$$

$$\approx \frac{(V_{REF1} + 2V_{IN})f_{CLK}}{V_{REF2}} = f_{DC} + f_{SIG}$$

(4)

where  $f_{DC}$  is the output offset frequency and  $f_{SIG}$  is the output signaldependent frequency. From (3), one can deduce that the output frequency,  $f_Q$ , is independent of the comparator offset. Moreover, if the capacitors C<sub>1A</sub>, C<sub>1B</sub>, C<sub>1C</sub> and C<sub>1D</sub> are well matched, the output frequency will be independent of actual capacitor value and only dependent on the reference voltage, the reference frequency and the input voltage signal. It can be seen that  $f_{DC}$  can be made to be independent of process, voltage and temperature variations if the reference voltages are generated using a well-matched resistor ladder. With V<sub>REF1</sub>=150mV, V<sub>REF2</sub> = 600mV and a V<sub>IN</sub> of ±24mV, the  $f_{DC}$  and  $f_{SIG}$ 's range are theoretically calculate as 125kHz and ±40kHz, respectively.

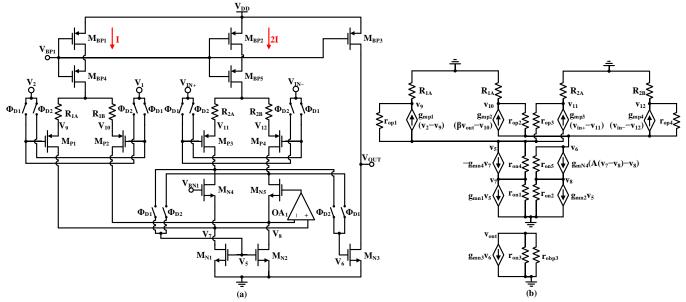

#### C. Chopping Differential Difference Amplifier

Fig. 3 shows the proposed chopping DDA. This DDA is a folded DDA for  $M_{P1}$  and  $M_{P2}$ , while a differential amplifier  $OA_1$  with cascode active load for  $M_{P3}$  and  $M_{P4}$ . This reduces the channel length modulation effect due to the large input common-mode difference between the two input ports. However, conventional biasing for the cascode devices  $M_{N4}$  and  $M_{N5}$ , where the gate of  $M_{N4}$  and  $M_{N5}$  are tied to the same biasing voltage, is not ideal for this architecture. This is due to the difference in current density for the cascode devices when the input voltage is varying. In other words, the  $V_{DS}$  values of  $M_{N4}$  and  $M_{N5}$  will vary with the input signal. To reduce the signal dependency, a low-power operational amplifier (op-amp) [20] is used to generate the biasing voltage for  $M_{N5}$  so that  $V_5$  and  $V_6$  are equalized. In this design, the DDA is designed to have a gain of 2 between two input ports,  $V_1-V_2$  and  $V_{IN+}-V_{IN-}$ . This gain aims to widen the signal frequency

Fig. 3 (a) Proposed DDA (b) Small-signal model of proposed DDA during  $\Phi_{D1}$ .

range without increasing the size of  $C_{1A}$  and  $C_{1B}$ . It can be derived through the small-signal model as shown in Fig. 3 (b). Several assumptions are made to simplify the derivation. They are given as follows:

- (i) The input pairs and the current mirror pairs have the same transconductance. They are  $g_{mp1} = g_{mp2}$ ,  $g_{mp3} = g_{mp4}$ ,  $g_{mn1} = g_{mn2}$  and  $g_{mn4} = g_{mn5}$ . Although the input pairs will exhibit difference in their transconductances at different input signals, the difference can be reduced through the source-degenerated resistors  $R_{1A}$ ,  $R_{1B}$ ,  $R_{2A}$  and  $R_{2B}$ .

- (ii) The input pairs and the current mirror pairs have the identical output impedance. They are  $r_{op1} = r_{op2}$ ,  $r_{op3} = r_{op4}$ ,  $r_{on1} = r_{on2}$ ,  $r_{on4} = r_{on5}$ .

- (iii) The resistance pairs are identical, with  $R_{2x} = R = 0.5R_{1X}$ .

- (iv) The gain factor  $g_{mx}r_{ox}$  for each transistor and the gain A for the op-amp is much larger than 1.

- (v) As  $V_2$  is close to  $V_{REF1}$ , its small-signal value is 0V.

Since V<sub>1</sub> contains the feedback signal, it is equal to  $\beta$ vout, where  $\beta$ =C<sub>3A</sub>/(C<sub>2A</sub>+C<sub>3A</sub>) during  $\Phi_1$  and  $\beta$ =C<sub>3A</sub>/(C<sub>P</sub>+C<sub>3A</sub>), with C<sub>P</sub> is the parasitic capacitance seen at V<sub>1</sub>. As the values of C<sub>P</sub> and C<sub>2A</sub> are much smaller than that of C<sub>3A</sub>,  $\beta$  is approximately equal to 1. The transfer function is obtained as follows:

$$\frac{v_1}{v_{in}} = \frac{\beta v_{out}}{v_{in}} = \frac{g_{mp3} \left(2g_{mp1}R + 1\right)}{g_{mp1} \left(g_{mp3}R + 1\right)}$$

(5)

From (5), to achieve a gain of 2,  $g_{mp3}$  needs to be two times of  $g_{mp1}$ . Thus, the current of  $M_{P3}$  and  $M_{P4}$  needs to be double of  $M_{P1}$  and  $M_{P2}$  because  $M_{P1}$ - $M_{P4}$  are biased in the subthreshold region.

To eliminate the offset of amplifier, the chopping technique is employed by chopping the input pairs  $M_{P1}$ - $M_{P2}$  and  $M_{P3}$ - $M_{P4}$ , together with the active loads  $M_{N1}$ - $M_{N2}$ . The offset for the transistors pair can be modeled as a voltage source at the gate of transistor. For simplicity,  $M_{P1}$ ,  $M_{P3}$  and  $M_{N2}$  are assumed to have the respective offset voltage of  $V_{off\_P1}$ ,  $V_{off\_P3}$  and  $V_{off\_N2}$ . The effect of the offset on  $V_1$  during  $\Phi_{D1}$  is then derived to give

$$V_{1} = \begin{cases} V_{REF1} + 2V_{IN} + V_{off\_DDA} & t \subseteq \Phi_{D1} \\ V_{REF1} + 2V_{IN} - V_{off\_DDA} & t \subseteq \Phi_{D2} \end{cases}$$

(6)

with  $V_{off_DDA} = V_{off_P1} + 2V_{off_P3} - V_{off_N2}g_{mn1}(2g_{mp1}R+1)/g_{mp1}$ . Substituting (5) into (6), we have

$$f_{Q} = \begin{cases} \frac{\left(V_{REF1} + 2V_{IN} + V_{off\_DDA}\right) f_{CLK}}{V_{REF2}} & t \subseteq \Phi_{D1} \\ \frac{\left(V_{REF1} + 2V_{IN} - V_{off\_DDA}\right) f_{CLK}}{V_{REF2}} & t \subseteq \Phi_{D2} \end{cases}$$

(7)

From (7), it can be observed that the average output frequency of two phases is independent of offset voltage of DDA.

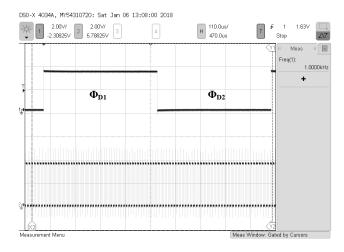

The measurement of the output frequency at each of the  $\Phi_{D1}$  and  $\Phi_{D2}$  chopping phase will begin after 100µs from the start of  $\Phi_{D1}$  and  $\Phi_{D2}$ , respectively. This is to cater for the settling time needed by the VI converter. The frequency of VF converter will then be calculated and the average frequency of  $\Phi_{D1}$  and  $\Phi_{D2}$  will be obtained.

#### III. EXPERIMENTAL RESULTS

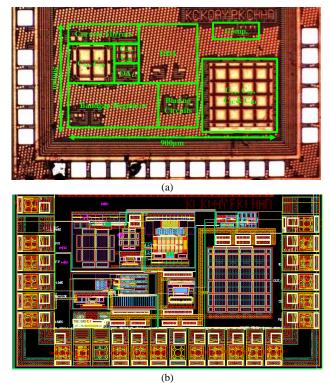

Implemented in AMS-0.18µm CMOS technology, the VF converter occupies an active area of 0.45 mm<sup>2</sup> as depicted in Fig. 4. The equipment employed for testing are Agilent DSO-X 4043A oscilloscope, Agilent 33600A function generator, Agilent 34461A multimeter, and Wiltech AS20W compressor and vacuum pump. The performance of the chips has been measured in three types of configuration. They are: (i) VF converter, (ii) full Wheatstone bridge configuration and (iii) pressure sensor configuration.

#### A. VF Converter

In this configuration, the supply current of VF converter is  $75\mu$ A at 1.5 V supply voltage. The measured transient waveforms are shown in Fig. 5, with the chopping clock displayed as the top trace and the VF

Fig. 4 (a) Chip micrograph and (b) layout of the VF converter.

Fig. 5 Transient waveform of the VF converter.

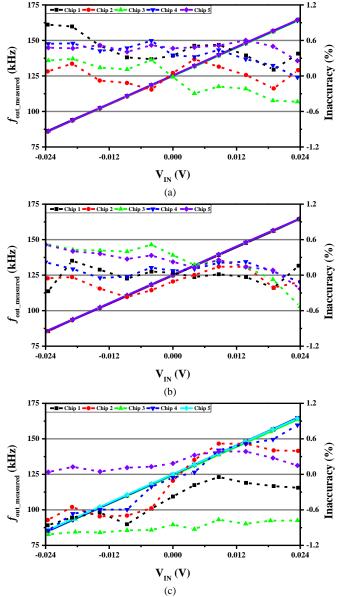

Fig. 6 Temperature variation of 5 chips at (a) 80 °C, (b) 25 °C and (c) -40 °C, with solid lines representing the transfer function of VF converters and dashed lines representing the accuracy of VF converters.

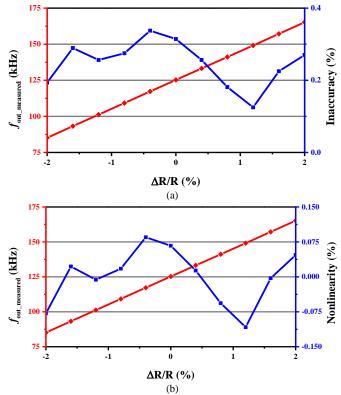

converter's output displayed as the bottom trace. Fig. 6 has shown the transfer function of VF converter which is characterized at temperature of 80 °C, 25 °C and -40 °C. It is noted that these measurements are conducted by injecting a DC input differential voltage with a value ranging from -24mV to 24mV. The inaccuracy is defined as follows:

Inaccuracy =

$$\frac{f_{out\_measured} - f_{out\_ideal}}{f_{ideal\_max} - f_{ideal\_min}} \times 100\%$$

(8)

where  $f_{out\_measured}$  is the measured output frequency,  $f_{out\_ideal}$  is the ideal output frequency,  $f_{ideal\_max}$  is the maximum output frequency at  $V_{in}$ =+24 mV, which is 165kHz.  $f_{ideal\_min}$  is the minimum output frequency at  $V_{in}$ =-24 mV, which is 85kHz. Along with the transfer function, the measured inaccuracies are illustrated in Fig. 6. At temperature of 80 °C, 25 °C and -40 °C, the average sensitivity of sensor is obtained as 1.6605 kHz/mV, 1.6609 kHz/mV and 1.6822 kHz/mV, respectively whereas the average offset frequency is

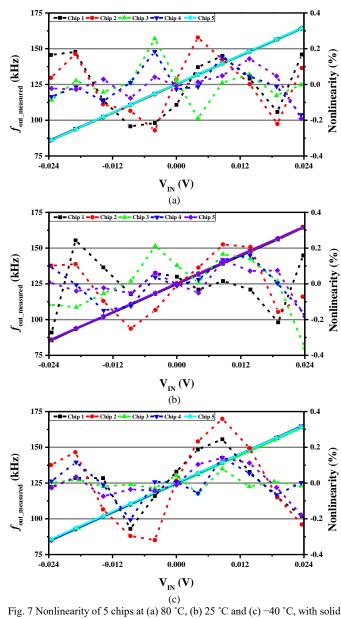

Fig. 7 Nonlinearity of 5 chips at (a) 80  $^{\circ}$ C, (b) 25  $^{\circ}$ C and (c) –40  $^{\circ}$ C, with solid lines representing the transfer function of VF converters and dashed lines representing the nonlinearity of VF converters.

obtained as 125.2 kHz, 125.02 kHz and 124.79 kHz. Over all temperatures, the five measured chips have shown worst inaccuracy of less than 1.1% at -40 °C. This is highly stable when compared to that of conventional counterparts which rely on the accuracy of a resistor and a capacitor. For CMOS process, a resistor will have a typical variation of  $\pm 15\%$  while a capacitor will have a variation of about  $\pm 10\%$  across process corners. This leads to a variation of  $\pm 56.8\%$  and -30.4% in the output frequency as encountered for conventional VF converters. The non-linearity of sensor interface is also measured and the results are depicted in Fig. 7. The nonlinearity is defined as follows:

Nonlinearity =

$$\frac{f_{out\_measured} - f_{out\_bfc}}{f_{out\_bfc\_max} - f_{out\_bfc\_min}} \times 100\%$$

(9)

where  $f_{out\_bfc}$  is the best-fit-curve output frequency at the given input voltage,  $f_{out\_bfc\_max}$  is the maximum best-fit-curve

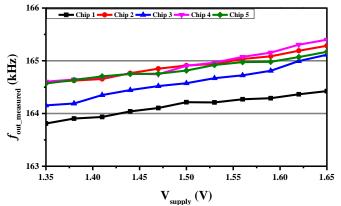

output frequency and *f*<sub>out\_bfc\_min</sub> is the minimum best-fit-curve output frequency. As revealed in Fig. 7, the worst nonlinearity is 0.36%. The frequency variation exhibited by the interface due to DC supply variation is also measured at an output frequency of 165kHz at 25 °C. The measurement results are shown in Fig. 8. The worst-case frequency variation is observed as 3.7 Hz/mV.

#### B. Full Wheatstone Bridge Configuration

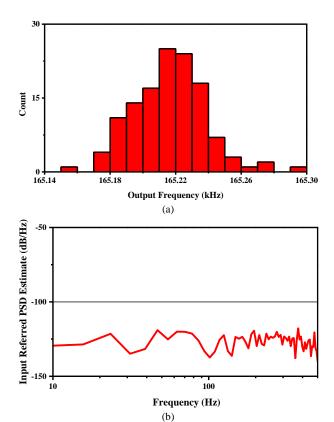

The proposed VF converter is tested with a full Wheatstone Bridge test setup. The test setup is shown in Fig. 9. Emulating a sensing bridge with a bridge resistance of 10 k $\Omega \pm 2\%$ , each R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub> and R<sub>4</sub> consists of a 25-turns potentiometer of 1 k $\Omega$  and a fixed resistor of 9.76 k $\Omega$ . The resistance variation of R<sub>1</sub> and R<sub>4</sub> are equal in magnitude but in opposite direction than that of R<sub>2</sub> and R<sub>3</sub>. The transfer function of the interface with respect to the bridge resistance change is shown in Fig. 10. The test subject is based on one of the 5 chips, which is chip 5 in this case. The measured nonlinearity is -0.11% and the worst-case inaccuracy is 0.34%. The measured sensitivity of sensor interface with the full Wheatstone bridge is 199.9 Hz/( $\mu\Omega/\Omega$ ). while the offset frequency is obtained as 125.2 kHz. To find the frequency uncertainty of sensor interface, 128 samples of the output frequency is taken with Altera DE0 [21] at the maximum bridge imbalance of +2%. Fig. 11(a) depicts the distribution of the output frequency. The standard deviation of the measured output frequency is 22.35 Hz. Fig. 11 (b) depicts the input referred power spectrum density of the proposed interface based on 128 points-FFT. The input referred noise is estimated as 13µVrms. This leads to a resolution of 10 bits.

Fig. 8 Frequency variation of the VF converter against voltage supply variation

Fig. 9 Full Wheatstone bridge sensing configuration.

#### C. Pressure Sensor Configuration

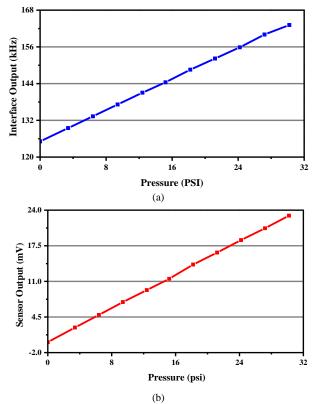

The sensor interface is then tested with a full Wheatstone bridge based Honeywell pressure sensor NSC-DANN030PGUNV [22] to measure the pressure in a tank. A pump AS20W is used to inject and drain the air from this pressure tank. Fig. 12 shows the output of commercial pressure sensor. It has shown that the commercial sensor displays a sensitivity of 0.765 mV/psi and an offset voltage of -0.032 mV. Turning to the sensor interface in conjunction with the sensor, it yields a sensitivity of 1.269 kHz/psi with an offset frequency of 125.2 kHz.

#### IV. PERFORMANCE COMPARISON

Table II shows the performance comparison of the proposed VF converter with other representative frequency converters. With a power consumption of 112.5  $\mu$ W and a measurement time of 1 ms, the proposed converter has demonstrated low energy-noise product while maintaining good accuracy across temperature variation and process variation. The proposed converter offers good linearity in comparison to other VF converters because the delay arising from the discharge of capacitor in the conventional IF conversion is eliminated. Three Figure-of-Merits, FOM<sub>1</sub> [23], FOM<sub>2</sub> and FOM<sub>3</sub>, are adopted to evaluate the efficiency of VF converters. They are defined as follows:

$$FOM_{1} = Power \times T_{measured} \times \frac{\sigma_{f}}{f_{max} - f_{min}}$$

(10)

$$FOM_2 = Power \times T_{measured} \times \left(\frac{\sigma_f}{f_{max} - f_{min}}\right)^2$$

(11)

$$FOM_{3} = \frac{Power \times T_{measured}}{ENOB}$$

(12)

Fig. 10 Measured output frequency: (a) inaccuracy and (b) nonlinearity of the sensor interface in full Wheatstone bridge configuration.

Fig. 11 (a)Output frequency distribution and (b) power spectral density of proposed sensor interface.

Fig. 12 Measured (a) output frequency of the sensor interface and (b) output voltage of the commercial pressure sensor.

| Table II Performance | comparison of the | proposed converter | with the reported works |

|----------------------|-------------------|--------------------|-------------------------|

|                      | comparison of the | proposed converter | with the reported works |

| Donomotor                                                                                                                   | [8]<br>TIM    | [10]<br>TIM       | [28]<br>TCAS II | [11]<br>Sens. Act., A       | [29]<br>ETRI               | [12]<br>TIM     | [13]<br>Sanaara I  | [23]<br>TIM   | [26]<br>JSSC          | [27]<br>ISSCC        | This work                              |

|-----------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|-----------------|-----------------------------|----------------------------|-----------------|--------------------|---------------|-----------------------|----------------------|----------------------------------------|

|                                                                                                                             | 1998          | 2000              | 2006            | 2007                        | 2007                       | 2011            | Sensors J.<br>2013 | 2015          | 2016                  | 2017                 | THIS WORK                              |

| Technology                                                                                                                  | Disc.         | Disc.             | 0.25 μm<br>CMOS | 0.7 μm<br>CMOS              | 0.35 μm<br>CMOS            | 0.18 μm<br>CMOS | 0.18 μm<br>CMOS    | 65 nm<br>CMOS | 0.18 μm<br>CMOS       | 0.18 μm<br>CMOS      | 0.18 μm<br>CMOS                        |

| Supply (V)                                                                                                                  | 3.3           | ±6.5              | 2.5             | 5                           | 1.5                        | 1.8             | 1.2                | 1.2           | 1.55                  | 1.8                  | 1.5                                    |

| Input Range                                                                                                                 | $\pm 15 mV^*$ | $5m\Omega/\Omega$ | 0.1-0.8V        | $\pm 0.025 \Omega / \Omega$ | $\pm 0.01 \Omega / \Omega$ | 0-1.2V          | 0-1.2V             | 30n-60µA      | ±10mV###              | ±10mV                | ±0.02 Ω/Ω                              |

| Power (mW)                                                                                                                  | NA            | 81.3**            | NA              | 67                          | 0.270                      | 0.375           | 0.080              | 0.168         | 2.42                  | 2.16                 | 0.1125                                 |

| Sensitivity                                                                                                                 | NA            | 0.5<br>Hz/(μΩ/Ω)  | 520<br>kHz/V    | 60.4<br>Hz/1000ppm          | 5<br>µV/V/mmHg             | 861<br>kHz/V    | 750<br>kHz/V       | 41.5<br>Hz/nA | NA                    | NA                   | 199.9<br>Hz/(μΩ/Ω)                     |

| Temp. Range (°C)                                                                                                            | 0 to 50       | NA                | NA              | NA                          | NA                         | -20 to 120      | -40 to 120         | -30 to 80     | NA                    | NA                   | -40 to 80                              |

| Nonlinearity (%)                                                                                                            | 0.186         | $\pm 0.2^{\#}$    | ±1#             | $\pm 0.4^{\#}$              | 0.23                       | 0.4             | 0.009##            | ±0.6# 11m##   | NA                    | NA                   | ±0.11 <sup>#</sup> 1.75m <sup>##</sup> |

| Timing Capacitor                                                                                                            | External      | External          | Integrated      | External                    | Integrated                 | Integrated      | Integrated         | Integrated    | NA                    | NA                   | Integrated                             |

| $\sigma_f$ (Hz)                                                                                                             | NA            | 0.2               | NA              | 0.3                         | NA                         | NA              | NA                 | 539           | NA                    | NA                   | 22.35                                  |

| Freq. Range, $\Delta f(Hz)$                                                                                                 | 15-368k       | 10k±2.5k          | 52-416k         | 6.4k±1.51k                  | NA                         | 0.1-1.1M        | 0.1M-1M            | 1.3k-2.489M   | NA                    | NA                   | 85k-165k                               |

| $\sigma_f / \Delta f (\mu \text{Hz/Hz}) \text{ or}$<br>(2 $\sqrt{2} \times \text{SNR}$ ) <sup>-1</sup> ( $\mu \text{V/V}$ ) | NA            | 40.0              | NA              | 99.3                        | NA                         | NA              | 1411 <sup>†</sup>  | 216           | 130                   | 16.5                 | 279.4                                  |

| Conversion time (ms)                                                                                                        | NA            | 10                | NA              | 20                          | 3.3                        | NA              | 32.8               | 16            | 50                    | 0.5                  | 1                                      |

| FOM <sub>1</sub> (nJ)                                                                                                       | NA            | 32.5**            | NA              | 133.2                       | NA                         | NA              | $3.7^{\dagger}$    | 0.71‡         | 1.57                  | 8.9×10 <sup>-3</sup> | 31.4×10 <sup>-3</sup>                  |

| FOM <sub>2</sub> (pJ)                                                                                                       | NA            | 0.325**           | NA              | 82.6                        | NA                         | NA              | 131 <sup>†</sup>   | 0.95‡         | 2.05×10 <sup>-2</sup> | 7.4×10 <sup>-5</sup> | 8.78×10 <sup>-3</sup>                  |

| FOM <sub>3</sub> (µJ/ENOB)                                                                                                  | NA            | 63                | NA              | 120                         | NA                         | 0.34            | 0.26               | NA            | 11                    | 0.07                 | 0.01                                   |

\*Differential input voltage.

\*\*Estimated.

\*Maximum nonlinearity in % full scale.

##1-R<sup>2</sup> nonlinearity.

where  $T_{measured}$  = gate time,  $f_{max}$  = maximum output frequency,  $f_{min}$  = minimum output frequency,  $\sigma_f$  = maximum standard deviation of output frequency and ENOB is the number of effective bit of the interface. The lower the three FOM values, the better are the performances. From (11), the  $\sigma_{f'}(f_{max}-f_{min})$  can be interpreted in an alternative representation as

###Calculated based on full scale range/max IA gain.

<sup>†</sup>Estimated based on +5%  $\Delta R/R$  in half bridge configuration.

$\ddagger$  Bias current of 30 $\mu$ A for center frequency included.

$$\frac{\sigma_f}{f_{\text{max}} - f_{\text{min}}} \equiv \frac{1}{2\sqrt{2}(SNR)} \tag{13}$$

, where SNR is the signal-to-noise ratio. This is because  $f_{max}$ - $f_{min}$  is equivalent to maximum output signal range and  $\sigma_f$  is equivalent to the rms output noise voltage. The FOM<sub>1</sub> is in similar form with Walden FOM [24] whereas FOM<sub>2</sub> is in similar form with thermal FOM [25].

FOM<sub>3</sub> is defined as the energy consumption per ENOB. It is mainly because IoT application deals with energy efficiency and hence FOM<sub>3</sub> is regarded as the critical evaluation parameter for performance comparison. From the comparison results, it can be seen that the proposed VF converter has achieved better FOM<sub>1</sub> and FOM<sub>2</sub> with respect to that of the reported works [10]–[13], [23], [26]. Besides, in comparison to the instrumentation amplifier with sigma-delta ADC sensor interface [27], despite the sensor interface displays relatively higher values in FOM<sub>1</sub> and FOM<sub>2</sub>, the proposed circuit shows 7 times lower in the energy consumption per ENOB as interpreted from FOM<sub>3</sub> whilst offering reasonable good signal-to-noise ratio. Therefore, it is suitable for IoT applications.

#### V. CONCLUSION

A low-energy low-noise VF converter with reduced circuit sensitivity has been proposed. Through the SC tracking design in the novel circuit architecture that involves SC VI and IF conversion techniques, good output frequency accuracy across process, voltage and temperature variations is obtained. In addition, by incorporating the chopper stabilization technique to reduce the offsets and low-frequency noise arising from both the amplifier and comparator, the circuit's performance in terms of precision, noise and output signal frequency jitter effect is greatly improved. As a result, the proposed circuit has achieved the compromising good results from the three FOMs with respect to the reported works whilst offering a simple architectural solution.

#### REFERENCES

- [1] D. M. Ştefănescu, *Handbook of force transducers*. Berlin, Heidelberg: Springer, 2011.

- [2] P. Ripka and A. Tipek, Eds., Modern sensors handbook. London, UK: ISTE, 2007.

- [3] Qiuting Huang and M. Oberle, "A 0.5-mW passive telemetry IC for biomedical applications," *IEEE J. Solid-State Circuits*, vol. 33, no. 7, pp. 937–946, Jul. 1998.

- [4] W. Claes, W. Sansen, and R. Puers, "A 40-μA/channel compensated 18-channel strain gauge measurement system for stress monitoring in dental implants," *IEEE J. Solid-State Circuits*, vol. 37, no. 3, pp. 293– 301, 2002.

- [5] B. Gosselin and M. Ghovanloo, "A high-performance analog frontend for an intraoral tongue-operated assistive technology," in *IEEE International Symposium of Circuits and Systems (ISCAS)*, 2011, pp. 2613–2616.

- [6] Z. Tan, S. H. Shalmany, G. C. M. Meijer, and M. a P. Pertijs, "An energy-efficient 15-bit capacitive-sensor interface based on period modulation," *IEEE J. Solid-State Circuits*, vol. 47, no. 7, pp. 1703– 1711, Jul. 2012.

- [7] J. Chen, Z. Zhu, S. Huang, and Y. Cheng, "All switched-capacitor realized piezoresistive pressure sensor interface chip for automotive TPMS," *IEICE Electron. Express*, vol. 10, no. 1, pp. 20120641– 20120641, 2013.

- [8] D. McDonagh and K. I. Arshak, "Stable differential voltage to frequency converter with low supply voltage and frequency offset control," *IEEE Trans. Instrum. Meas.*, vol. 47, no. 5, pp. 1355–1361, 1998.

- [9] V. Ferrari, C. Ghidini, D. Marioli, and a. Taroni, "Oscillator-based signal conditioning with improved linearity for resistive sensors," *IEEE Trans. Instrum. Meas.*, vol. 47, no. 1, pp. 293–298, 1998.

- [10] V. Ferrari, D. Marioli, and a. Taroni, "Oscillator-based interface for measurand-plus-temperature readout from resistive bridge sensors," *IEEE Trans. Instrum. Meas.*, vol. 49, no. 3, pp. 585–590, Jun. 2000.

- [11] V. Ferrari, A. Ghisla, Z. K. Vajna, D. Marioli, and A. Taroni, "ASIC front-end interface with frequency and duty cycle output for resistivebridge sensors," *Sensors Actuators A, Phys.*, vol. 138, no. 1, pp. 112– 119, Jul. 2007.

- [12] M. R. Valero, S. Celma, B. Calvo, and N. Medrano, "CMOS voltageto-frequency converter with temperature drift compensation," *IEEE Trans. Instrum. Meas.*, vol. 60, no. 9, pp. 3232–3234, 2011.

- [13] C. Azcona, B. Calvo, S. Celma, N. Medrano, and P. A. Martinez, "Ratiometric voltage-to-frequency converter for long-life autonomous portable equipment," *IEEE Sens. J.*, vol. 13, no. 6, pp. 2382–2390, 2013.

- [14] S. Middelhoek, P. J. French, J. H. Huijsing, and W. J. Lian, "Sensors with digital or frequency output," *Sensors and Actuators*, vol. 15, no. 2, pp. 119–133, Oct. 1988.

- [15] H. Matsumoto and K. Watanabe, "Switched-capacitor frequency-tovoltage and voltage-to-frequency converters based on chargebalancing principle," in *IEEE International Symposium on Circuits* and Systems, 1988, pp. 2221–2224.

- [16] M. Hufford, E. Naviasky, S. Williams, and M. Williams, "An improved wideband PLL with adaptive frequency response that tracks the reference," in *Proceedings of the IEEE Custom Integrated Circuits Conference*, 2005, pp. 544–547.

- [17] B. R. Gregoire and U.-K. Moon, "A sub 1-V constant Gm-C switched-capacitor current source," *IEEE Trans. Circuits Syst. II Express Briefs*, vol. 54, no. 3, pp. 222–226, Mar. 2007.

- [18] E. Sackinger and W. Guggenbuhl, "A versatile building block: the CMOS differential difference amplifier," *IEEE J. Solid-State Circuits*, vol. 22, no. 2, pp. 287–294, Apr. 1987.

- [19] A. Paidimarri, D. Griffith, A. Wang, A. P. Chandrakasan, and G. Burra, "A 120nW 18.5kHz RC oscillator with comparator offset cancellation for ±0.25% temperature stability," in *Proceeding of the IEEE International Solid-State Circuits Conference*, 2013, vol. 56, pp. 184–185.

- [20] Libin Yao, M. Steyaert, and W. Sansen, "Fast-settling CMOS twostage operational transconductance amplifiers and their systematic design," in *Proceedings of International Symposium on Circuits and Systems.*, 2002, p. II-839-II-842.

- [21] Terasic, "Altera DE0 Board." [Online]. Available: http://www.terasic.com.tw/cgi-

- bin/page/archive.pl?Language=English&No=364. [Accessed: 11-Jul-2017].

- [22] "TruStability® board mount pressure sensors," NJ,USA., 2014.

- [23] K. C. Koay and P. K. Chan, "A low-power resistance-to-frequency converter circuit with wide frequency range," *IEEE Trans. Instrum. Meas.*, vol. 64, no. 12, pp. 3173–3182, Dec. 2015.

- [24] R. H. Walden, "Analog-to-digital converter survey and analysis," *IEEE J. Sel. Areas Commun.*, vol. 17, no. 4, pp. 539–550, 1999.

- [25] A. M. a. Ali, C. Dillon, R. Sneed, A. S. Morgan, S. Bardsley, J. Kornblum, and L. Wu, "A 14-bit 125 MS/s IF/RF Sampling Pipelined ADC With 100 dB SFDR and 50 fs Jitter," *IEEE J. Solid-State Circuits*, vol. 41, no. 8, pp. 1846–1855, Aug. 2006.

- [26] M. Maruyama, S. Taguchi, M. Yamanoue, and K. Iizuka, "An Analog Front-End for a Multifunction Sensor Employing a Weak-Inversion Biasing Technique with 26 nVrms, 25 aCrms, and 19 fArms Input-Referred Noise," *IEEE J. Solid-State Circuits*, vol. 51, no. 10, pp. 2252–2261, 2016.

- [27] H. Jiang, K. A. A. Makinwa, and S. Nihtianov, "An energy-efficient 3.7nV/√Hz bridge-readout IC with a stable bridge offset compensation scheme," in 2017 IEEE International Solid-State Circuits Conference (ISSCC), 2017, pp. 172–173.

- [28] C. Wang, T. Lee, C. Li, and R. Hu, "An all-MOS high linearity voltage-to-frequency converter chip with 520 KHz/V sensitivity," *IEEE Trans. Circuits Syst. II Express Briefs*, vol. 53, no. 8, pp. 744– 747, Aug. 2006.

- [29] A. Thanachayanont and S. Sangtong, "Low-voltage current-sensing CMOS interface circuit for piezo-resistive pressure sensor," *ETRI J.*, vol. 29, no. 1, pp. 70–78, 2007.

9

Kuan Chuang Koay (S15) was born in Malaysia. He received his B. Eng (Hons) degree from Nanyang Technological University (NTU), Singapore, in 2012. He joined Qualcomm, Singapore as an analog integrated circuit designer in 2017. His research interests include frequency compensation techniques for low-dropout regulators, design of switching regulator and design of sensor interface IC.

**Pak Kwong Chan** (M'92–SM'10) was born in Hong Kong. He received the B.Sc. (Hons) degree from University of Essex, Colchester, U. K., in 1987, the M.Sc. degree from University of Manchester, Institute of Science and Technology, Manchester, U.K., in 1988, and the PhD degree from University of Plymouth, U.K. in 1992. From 1989 to 1992, he was a Research Assistant with University of Plymouth, working

in the area of MOS continuous-time filters. In 1993, he joined Institute of Microelectronics (IME), Singapore as a Member Technical Staff, where he designed high-performance analog/mixed-signal circuits for integrated systems and CMOS sensor interfaces for industrial applications. In 1996, He was a Staff Engineer with Motorola, Singapore where he developed the magnetic write channel for Motorola 1st generation hard-disk preamplifier. He joined Nanyang Technological University, Singapore in 1997, where he is an Associate Professor in the School of Electrical and Electronic Engineering. He served the Program Director (analog/mixed-signal IC and applications) for the Center for Integrated Circuits and Systems (CICS) from 2003 to 2010. He also conducted numerous IC design short courses to the industry and IC design centers. His current research interests include sensor circuits and systems, mixed-mode circuits and systems, PVT-insensitive circuits and systems, precision analog circuits, ultra-low-voltage low-power circuits as well as power management IC for integrated sensors, system-on-chip and internet-ofthings applications. Dr Chan has served as a Guest Editor for the Journal of Circuits, Systems and Computers and for the Sensors.