# A 0.19e- rms Read Noise 16.7Mpixel Stacked Quanta Image Sensor With 1.1µm-Pitch Backside Illuminated Pixels

Jiaju Ma<sup>®</sup>, *Member, IEEE*, Dexue Zhang<sup>®</sup>, Omar A. Elgendy<sup>®</sup>, *Member, IEEE*, and Saleh Masoodian<sup>®</sup>

Abstract—This letter reports a 16.7 Mpixel, 3D-stacked backside illuminated Quanta Image Sensor (QIS) with 1.1  $\mu$ m-pitch pixels which achieves 0.19 e- rms array read noise and 0.12 e- rms best single-pixel read noise under room temperature operation. The accurate photon-counting capability enables superior imaging performance under ultra-low-light conditions. The sensor supports programmable analog-to-digital convertor (ADC) resolution from 1-14 bits and video frame rates up to 40 fps with 4096 × 4096 resolution and 600 mW power consumption.

Index Terms— Photon-counting, low-light imaging, CMOS image sensor, quanta image sensor.

#### I. INTRODUCTION

THE read noise reduction in CMOS image sensors (CIS) is an active research and development topic in recent years because of its prominent impact in low-light imaging performance for professional and consumer applications. By reducing the noise to low enough levels for accurate counting of every photoelectron, the highest possible signal-to-noise ratio (SNR) under photon-limited imaging conditions can be realized. From previous studies [1]–[3], the input-referred read noise needs to be 0.45 e- rms or lower to enable some basic photoelectron counting capabilities and read noise of <0.15 e- rms is needed for accurate photoelectron counting with <0.1% bit error rate (BER).

Process and design improvements are being made to reduce the read noise by suppressing the temporal noise from in-pixel source followers (SF) [4]–[9] or increasing the conversion gain of the pixel output node [10]–[13]. As a result of these improvements, sub-electron read noise has been reported in multiple studies. This provides a foundation for the development of a CIS-based Quanta Image Sensor (CIS-QIS), a next-generation image sensor with photon-counting pixels that supports high-speed and low-power operation with high pixel resolution [14]. A 1Mpix QIS was reported in 2017 with

The authors are with Gigajot Technology, Inc., Pasadena, CA 91107 USA (e-mail: jiaju.ma@gigajot.tech).

Color versions of one or more figures in this letter are available at https://doi.org/10.1109/LED.2021.3072842.

Digital Object Identifier 10.1109/LED.2021.3072842

sub-0.3 e- rms input-referred read noise and accurate photoncounting capabilities [15]. Compared to other conventional high-sensitivity detectors such as single-photon avalanche diode (SPAD) [16]–[18], CIS-QIS eliminates the needs of electron multiplication and its associated negative effects, and usually provides higher pixel resolution with smaller pixel sizes, higher quantum efficiency, substantially higher fullwell capacity, and lower dark count rate with lower power consumption and better manufacturability.

#### II. SENSOR ARCHITECTURE

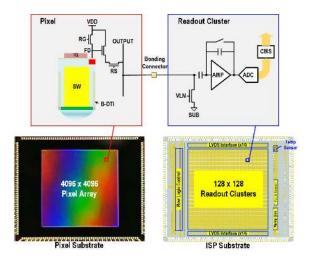

This letter reports a CIS-QIS designed and manufactured in a commercial 45 nm/ 65 nm stacked backside illuminated (BSI) CIS process. The sensor architecture is illustrated in Figure 2. It consists of 4096 × 4096 1.1  $\mu$ m-pitch pixels on the pixel substrate (top). The readout circuits are fabricated on the ISP substrate (bottom). The two wafers are bonded and connected through high-density wafer-wafer connectors. A cluster-parallel readout architecture is implemented on the bottom substrate to reduce the parasitic resistance and capacitance introduced by large pixel array and long pixel output columns [14], [15]. Improved readout speed and power efficiency are realized with this architecture.

On the top substrate, the active pixel array is sectioned into  $128 \times 128$  clusters (1024 pixels per cluster), and each cluster is connected to a corresponding readout cluster unit on the bottom substrate. On the bottom substrate, each readout cluster contains a programmable-gain amplifier (PGA) with 1x to 8x analog gain, a single-slope analog-to-digital converter (SSADC) with 1-14 bit programmable bit depth, and a correlated multiple sampling (CMS) signal processor with programmable number of CMS cycles [4], [6], [19], [20]. The  $128 \times 128$  clusters function in parallel and the output data is carried off-chip by 28 pairs of LVDS lanes with up to 1.2 Gbps/lane throughput rate. The bottom substrate also contains a temperature sensor, a phase-locked loop (PLL), a counter, and a ramp generator. The pixel structure is shown in Figure 2. The pixel structure contains a transfer gate (TG), a reset transistor, a source follower, and a row select (RS) transistor. The pump-gate architecture with a vertical storage well (SW) and a distal floating diffusion (FD) is implemented to improve the conversion gain and reduce the input-referred read noise [21]. A buried-channel SF [22]-[24] is used to

Manuscript received March 25, 2021; revised April 4, 2021; accepted April 9, 2021. Date of publication April 13, 2021; date of current version May 21, 2021. The review of this letter was arranged by Editor L. K. Nanver. (*Corresponding author: Jiaju Ma.*)

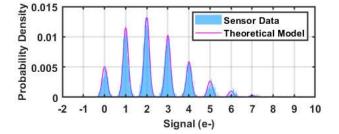

Fig. 1. A photon-counting histogram from a pixel with 0.12 e- rms read noise and 2.3 e-/pixel average signal level showing a distinctly discrete numbers of photoelectrons. The sensor data closely matches the theoretical Poisson-Gaussian model.

Fig. 2. Sensor architecture and block diagrams of a pixel and a readout cluster.

reduce the temporal noise associated with the Si-SiO<sub>2</sub> interface trapping events. The backside deep trench isolation (B-DTI) is implemented in the pixels to improve inter-pixel isolation.

## **III. CHARACTERIZATION RESULTS**

## A. Read Noise and Dark Performance

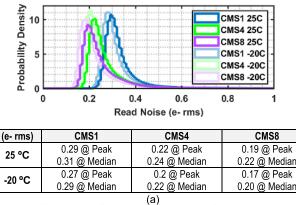

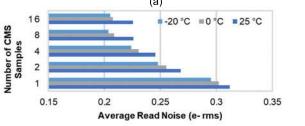

The total input-referred temporal noise (read noise) of the sensor was characterized with PGA 8x gain with different numbers of CMS cycles and 70  $\mu$ sec integration time under multiple temperatures. The conversion gain of the pixels at the output of the SF is 340  $\mu$ V/e measured by the photon transfer curve methodology [25]. Under room temperature (25 °C) with one CMS cycle, the measured read noise is 0.29 e- rms at the peak of the noise distribution and 0.31 e- rms at the median. With CMS 8, the read noise is further reduced to 0.19 e- rms at the peak and 0.22 e- rms at the median. The results of CMS 16 do not show significant reduction over CMS 8, which is likely due to increased low-frequency noise from the SFs and the accumulated FD dark current during the extended CMS sampling time. For similar reasons, the noise reduction ratio from the CMS operation is lower than the theoretical values given by  $\sigma/\sqrt{N}$ , where  $\sigma$  is the noise level with CMS 1 and N is the number of CMS cycles. At -20 °C, the read noise is further reduced to 0.17 e- rms at the peak and 0.20 e- rms at the median with CMS 8. This noise reduction is likely a result of reduced thermal noise from the SFs and less FD

Fig. 3. (a) Read noise distributions with PGA 8x gain and CMS 1, 4, 8 under 25 °C and -20 °C. (b) Average read noise with 1-16 CMS cycles under -20 °C, 0 °C, and 25 °C.

(b)

dark current accumulated during the CMS sampling time. A small number of pixels with excessively high noise are present, and the signal distributions of these high-noise pixels exhibit a trimodal signature that is often linked to random telegraph signal (RTS) caused by interface traps in the pixel SFs. The amount of these high-noise pixels (>10 e- rms) is found to be less than 1ppm with CMS1 and room temperature operation.

Besides the ultra-low total temporal noise, low dark signal non-uniformity (DSNU) (0.1 e- rms), excellent row temporal noise (0.02 e- rms) and column temporal noise (0.02 e- rms) are also demonstrated with the sensor under 25 °C and CMS 1 operation. The overall noise performance is significantly improved compared to [15] as results of an improved buriedchannel SF design and the addition of on-chip low-noise ADC and CMS circuitry.

The photon-counting capability of the sensor is demonstrated with the photon-counting histogram (PCH) methodology [26]. The PCH from one pixel with CMS 8 at room temperature is shown in Figure 1. This sensor signal distribution closely matches the Poisson-Gaussian distribution with 0.12 e- rms read noise and 2.3 e-/pixel/frame average signal. In this example, The ultra-low read noise results in fully separated peaks in the PCH. To our knowledge, this is the lowest read noise ever demonstrated with CMOS active pixels.

## B. Photon Response Performance

The light response of the sensor was characterized with the photon transfer curve. The 1.1  $\mu$ m pixels show a linear full well capacity (FWC) of 1500 e-, which is currently limited by the photodiode capacity and expected to be further improved

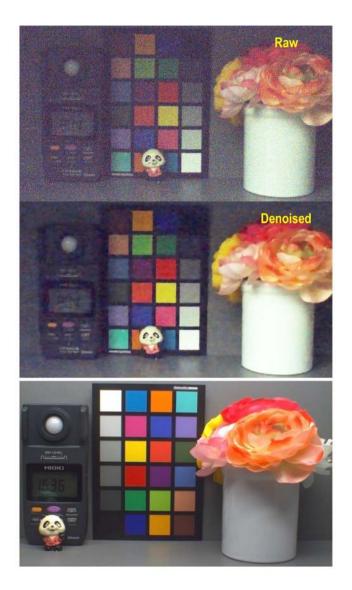

Fig. 4. Sample images under 0.01 lux and 1636 lux illumination levels.

in the future wafer splits with optimized photodiode implant conditions. The measured quantum efficiency (QE) of the sensor has peak values of 64%, 75%, and 64% for red, green, and blue respectively.

#### C. Imaging Demonstration

The sample images from both high-light (1636 lux) and lowlight (0.01 lux) conditions are shown in Figure 4. The 1636 lux image was captured with 1x PGA gain, CMS 1, f/5.6 lens and 30msec integration time. This image was processed with a standard color image processing pipeline with demosaicing, white balancing, and color correction. The 0.01 lux image was captured with 8x PGA gain, CMS 1, 600 msec integration and f/1.4 lens with an average signal level as low as 1.6 photoelectrons per pixel. The image on the top was processed with a standard image processing pipeline, while the image on the bottom was generated with a neural network-based color pipeline with joint demosaicing and denoising optimized for QIS in ultra-low light imaging [27].

TABLE I SENSOR PERFORMANCE SUMMARY

| Process Technology        |               | 45nm/65nm Stacked CIS BSI Process          |

|---------------------------|---------------|--------------------------------------------|

| Pixel Size                |               | 1.1 μm x 1.1 μm                            |

| Pixel Resolution          |               | 4096 x 4096                                |

| Chroma                    |               | RGB Bayer /Mono                            |

| Power Consumption         |               | 600 mW                                     |

| ADC Bit Depth             |               | 1-14 bit programmable                      |

| Max Frame Rate            |               | 40 fps @ 4096 x 4096                       |

|                           |               | 60 fps @ 3840 x 2160                       |

| Read Noise                | 25 °C, CMS 8  | 0.19 e- rms @ Peak<br>0.22 e- rms @ Median |

|                           | -20 °C, CMS 8 | 0.17 e- rms @ Peak<br>0.20 e- rms @ Median |

| RTS (>10e- rms)           |               | <1 ppm                                     |

| Linear Full-Well Capacity |               | 1500 e-                                    |

| Dynamic Range             |               | 77 dB                                      |

| Non-Linearity             |               | <0.5%                                      |

| PRNU                      |               | <1.5%                                      |

| Quantum Efficiency @ Peak |               | 76% @ 520nm                                |

| Dark Current              | 60C           | 4.5 e-/pix/sec                             |

|                           | 20C           | 0.086 e-/pix/sec                           |

| Lag                       |               | <0.1 e- (less than the measurable level)   |

## **IV. CONCLUSION**

This letter reports a 16.7 Mpixel QIS with 1.1  $\mu$ m-pitch pixels fabricated in a 45/65 nm stacked BSI CIS process. This sensor achieves 0.19 e- rms array read noise and 0.12 e- rms best single-pixel read noise under room temperature operation. The superior imaging performance under ultra-low-light conditions is demonstrated with accurate photon-counting capabilities. A summary of the sensor performance is shown in Table I. The excellent low-light performance makes the sensor ideal for a variety of imaging applications including scientific, security, defense, medical, consumer, and cellphone.

### ACKNOWLEDGMENT

The authors appreciate TSMC for manufacturing the sensor presented in this work, especially the teams led by F.S. Guo and Y. Yamashita. The authors are also thankful for the advice from E. Fossum, technical discussion with M. Guidash, proofreading from L. Anzagira, and technical support from other colleagues at Gigajot Technology.

#### REFERENCES

- E. R. Fossum, "Modeling the performance of single-bit and multi-bit quanta image sensors," *IEEE J. Electron Devices Soc.*, vol. 1, no. 9, pp. 166–174, Sep. 2013, doi: 10.1109/JEDS.2013.2284054.

- [2] E. R. Fossum, "Photon counting error rates in single-bit and multi-bit quanta image sensors," *IEEE J. Electron Devices Soc.*, vol. 4, no. 3, pp. 136–143, May 2016, doi: 10.1109/JEDS.2016.2536722.

- [3] N. Teranishi, "Required conditions for photon-counting image sensors," *IEEE Trans. Electron Devices*, vol. 59, no. 8, pp. 2199–2205, Aug. 2012.

- [4] S. Kawahito, S. Suh, T. Shirei, S. Itoh, and S. Aoyama, "Noise reduction effects of column-parallel correlated multiple sampling and sourcefollower driving current switching for CMOS image sensors," in *Proc. Int. Image Sensor Workshop*, 2009, pp. 320–323.

- [5] A. Boukhayma, A. Peizerat, and C. Enz. (2015). A 0.4 e-RMS Temporal Readout Noise 7.5 μm Pitch and a 66% Fill Factor Pixel for Low Light CMOS Image Sensors. Accessed: Jul. 21, 2017. [Online]. Available: http://www.imagesensors.org/PastWorkshops/2015Workshop/ 2015Papers/Sessions/Session\_12/12-03\_Boukhayama-peizerat.pdf

- [6] S.-F. Yeh, K.-Y. Chou, H.-Y. Tu, C. Y.-P. Chao, and F.-L. Hsueh, "A 0.66e<sub>rms</sub><sup>-</sup> temporal-readout-noise 3-D-stacked CMOS image sensor with conditional correlated multiple sampling technique," *IEEE J. Solid-State Circuits*, vol. 53, no. 2, pp. 527–537, Feb. 2018, doi: 10. 1109/JSSC.2017.2765927.

- [7] S. Ichino, T. Mawaki, S. Wakashima, A. Teramoto, R. Kuroda, P. Gaubert, T. Goto, T. Suwa, and S. Sugawa, "Statistical analysis of random telegraph noise in source follower transistors with various shapes," in *Proc. Int. Image Sensor Workshop*, 2017, pp. 39–42.

- [8] M. Guidash, J. Ma, T. Vogelsang, and J. Endsley, "Reduction of CMOS image sensor read noise to enable photon counting," *Sensors*, vol. 16, no. 4, p. 517, Apr. 2016, doi: 10.3390/s16040517.

- [9] Y. Chen, Y. Xu, Y. Chae, A. Mierop, X. Wang, and A. Theuwissen, "A 0.7 e<sup>-</sup><sub>rms</sub>-temporal-readout-noise CMOS image sensor for lowlight-level imaging," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2012, pp. 384–386.

- [10] M.-W. Seo, S. Kawahito, K. Kagawa, and K. Yasutomi, "A 0.27erms read noise 220-μV/e-conversion gain reset-gate-less CMOS image sensor with 0.11-μm CIS process," *IEEE Electron Device Lett.*, vol. 36, no. 12, pp. 1344–1347, Dec. 2015.

- [11] M. Sato, Y. Yorikado, Y. Matsumura, H. Naganuma, E. Kato, T. Toyofuku, A. Kato, and Y. Oike, "A 0.5 e-rms noise 1.45 μmpitch CMOS image sensor with reference shared in-pixel differential amplifier at 8.3 Mpixel 35 fps," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 108–110, doi: 10. 1109/ISSCC19947.2020.9063017.

- [12] S. Adachi, W. Lee, N. Akahane, H. Oshikubo, K. Mizobuchi, and S. Sugawa, "A 200-μV/e<sup>-</sup> CMOS image sensor with 100-ke<sup>-</sup> full well capacity," *IEEE J. Solid-State Circuits*, vol. 43, no. 4, pp. 823–829, Apr. 2008, doi: 10.1109/JSSC.2008.917549.

- [13] J. Ma and E. R. Fossum, "Quanta image sensor jot with sub 0.3e- r.m.s. Read noise and photon counting capability," *IEEE Electron Device Lett.*, vol. 36, no. 9, pp. 926–928, Sep. 2015, doi: 10. 1109/LED.2015.2456067.

- [14] E. Fossum, J. Ma, S. Masoodian, L. Anzagira, and R. Zizza, "The quanta image sensor: Every photon counts," *Sensors*, vol. 16, no. 8, p. 1260, Aug. 2016, doi: 10.3390/s16081260.

- [15] J. Ma, S. Masoodian, D. A. Starkey, and E. R. Fossum, "Photonnumber-resolving megapixel image sensor at room temperature without avalanche gain," *Optica*, vol. 4, no. 12, p. 1474, Dec. 2017, doi: 10. 1364/OPTICA.4.001474.

- [16] N. Dutton, I. Gyongy, L. Parmesan, and R. Henderson, "Single photon counting performance and noise analysis of CMOS SPAD-based image sensors," *Sensors*, vol. 16, no. 7, p. 1122, Jul. 2016.

- [17] T. Al Abbas, N. A. W. Dutton, O. Almer, S. Pellegrini, Y. Henrion, and R. K. Henderson, "Backside illuminated SPAD image sensor with 7.83 μm pitch in 3D-stacked CMOS technology," in *IEDM Tech. Dig.*, Dec. 2016, pp. 8.1.1–8.1.4, doi: 10.1109/IEDM.2016.7838372.

- [18] K. Morimoto, A. Ardelean, M.-L. Wu, A. C. Ulku, I. M. Antolovic, C. Bruschini, and E. Charbon, "Megapixel time-gated SPAD image sensor for 2D and 3D imaging applications," *Optica*, vol. 7, no. 4, p. 346, Apr. 2020, doi: 10.1364/optica.386574.

- [19] S. Kawahito and M.-W. Seo, "Noise reduction effect of multiplesampling-based signal-readout circuits for ultra-low noise CMOS image sensors," *Sensors*, vol. 16, no. 11, p. 1867, Nov. 2016, doi: 10. 3390/s16111867.

- [20] Y. Chen, Y. Xu, A. J. Mierop, and A. J. P. Theuwissen, "Columnparallel digital correlated multiple sampling for low-noise CMOS image sensors," *IEEE Sensors J.*, vol. 12, no. 4, pp. 793–799, Apr. 2012.

- [21] J. Ma and E. R. Fossum, "A pump-gate jot device with high conversion gain for a quanta image sensor," *IEEE J. Electron Devices Soc.*, vol. 3, no. 2, pp. 73–77, Mar. 2015, doi: 10.1109/JEDS.2015.2390491.

- [22] R. Kuroda, A. Yonezawa, A. Teramoto, T.-L. Li, Y. Tochigi, and S. Sugawa, "A statistical evaluation of random telegraph noise of in-pixel source follower equivalent surface and buried channel transistors," *IEEE Trans. Electron Devices*, vol. 60, no. 10, pp. 3555–3561, Oct. 2013, doi: 10.1109/TED.2013.2278980.

- [23] Y. Chen, X. Wang, A. J. Mierop, and A. J. P. Theuwissen, "A CMOS image sensor with in-pixel buried-channel source follower and optimized row selector," *IEEE Trans. Electron Devices*, vol. 56, no. 11, pp. 2390–2397, Nov. 2009, doi: 10.1109/TED.2009.2030600.

- [24] X. Wang, M. F. Snoeij, P. R. Rao, A. Mierop, and A. J. P. Theuwissen, "A CMOS image sensor with a buried-channel source follower," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, vol. 51, Feb. 2008, pp. 62–64, doi: 10.1109/ISSCC.2008.4523057.

- [25] J. R. Janesick, K. P. Klaasen, and T. Elliott, "Charge-coupleddevice charge-collection efficiency and the photon-transfer technique," *Opt. Eng.*, vol. 26, no. 10, Oct. 1987, Art. no. 261072, doi: 10. 1117/12.7974183.

- [26] D. A. Starkey and E. R. Fossum, "Determining conversion gain and read noise using a photon-counting histogram method for deep sub-electron read noise image sensors," *IEEE J. Electron Devices Soc.*, vol. 4, no. 3, pp. 129–135, May 2016.

- [27] O. A. Elgendy, A. Gnanasambandam, S. H. Chan, and J. Ma, "Low-light demosaicking and denoising for small pixels using learned frequency selection," *IEEE Trans. Comput. Imag.*, vol. 7, pp. 137–150, 2021, doi: 10.1109/TCI.2021.3052694.