# A 0.6 V, 4.32 mW, 68 GHz Low Phase-Noise VCO With Intrinsic-Tuned Technique in 0.13 $\mu$ m CMOS

Hsien-Ku Chen, Hsien-Jui Chen, Da-Chiang Chang, Ying-Zong Juang, and Shey-Shi Lu, Senior Member, IEEE

Abstract-An intrinsic-tuned, 68 GHz voltage controlled oscillator (VCO) without an extra on-chip accumulation-mode metal oxide semiconductor (MOS)-varactor is demonstrated in a standard, 0.13  $\mu$ m CMOS technology. This VCO exhibits phase noises of -98.4 dBc/Hz and -115.2 dBc/Hz at 1 and 10 MHz offset, respectively, along with a tuning range of 4.5% even under a small power consumption of 4.32 mW. Besides, the highest figure-of-merit (taking frequency tuning range into account) of -182 dBc/Hz under the 1 MHz offset condition is achieved among all previously reported >60 GHz CMOS-based VCOs, which is attributed to the proposed intrinsic tuning mechanism.

Index Terms—Accumulation-mode, back-gate, CMOS, intrinsic tuned, millimeter-wave (MMW), phase noise, quality factor, small chip size, varactor, voltage controlled oscillator (VCO).

# I. INTRODUCTION

**R** ECENTLY, on-chip, accumulation-mode metal oxide semiconductor (MOS) area of the semiconduc semiconductor (MOS)-varactors have been adopted in millimeter-wave (MMW) voltage controlled oscillators (VCOs) for frequency tuning [1]-[6]. Published MMW VCOs incorporating MOS-varactors [1]–[4] exhibit phase noises between -102.7 and -108 dBc/Hz at 10 MHz offset. This fact indicates that phase noise can be further improved by enhancing the low quality factor (Q) of the MMW varactor (Q ~12.5 at 24 GHz for  $C_{\rm max}/C_{\rm min}~$  =3.5 [2] and Q~ ~5 at 60 GHz for  $C_{\rm max}/C_{\rm min}$  =2 [7]), which is the main reason for the degradation of figure-of-merit (FOM) of the MMW VCOs. Although, a differential-tuned mechanism has been proposed for suppressing the external noise caused by the measurement [3], the issue about the low Q varactor still remains. Push-push topology is usually utilized for MMW VCO designs [5], [6], where the LC resonant tank is designed at half of the desired output frequency  $(f_0)$  to avoid the inherent low gain characteristic of the MOSFET at higher frequencies, so that the oscillation condition can still be easily sustained. Besides, better phase noise can also be achieved by push-push topology due to the high Q characteristic of on-chip accumulation-mode MOS-varactors at lower

Manuscript received February 2, 2008; revised February 12, 2008. This work was supported by the National Science Council and Ministry of Economic Affairs of Taiwan, R.O.C., under Grants NSC-96-2218E002-010 and 96-EC-17-A-05-S1-020.

H.-K. Chen and S.-S. Lu are with the Graduate Institute of Electronics Engineering, National Taiwan University, Taipei 10617, Taiwan, R.O.C. (e-mail: sslu@ntu.edu.tw).

H.-J. Chen is with the Faraday Technology Corporation, Hsinchu, Taiwan, R.O.C.

D.-C. Chang and Y.-Z. Juang are with the Chip Implementation Center, National Applied Research Laboratories, Hsinchu 300, Taiwan, R.O.C.

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LMWC.2008.925106

Intrinsic Tuning

Fig. 1. Schematic of low phase-noise intrinsic-tuned VCO.

frequencies. However, process variations will cause an imperfect differential output of the VCO, resulting in a weaker desired signal at  $f_0$  (< -20 dBm in [5], [6]). Therefore, it usually needs an additional amplifier to compensate for the mismatch loss, which consumes extra dc power. Others used a dielectric resonator for enhancing the Q of the LC resonant tank, and thus, a better phase noise was achieved [8]. Nevertheless a tuning range of only 0.2% was reported. In this letter, an alternate way for MMW VCO design is proposed, in which the low Q on-chip accumulation-mode MOS-varactor is replaced by an intrinsic PN junction capacitor for achieving a tunable low phase-noise MMW VCO. Although this method has been adopted in VCOs operated below 10 GHz [9], [10], this work demonstrates that it is especially advantageous in MMW VCOs.

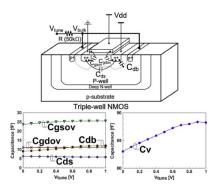

### II. INTRINSIC-TUNED VCO DESIGN

The cross-coupled transistors are utilized to provide the sufficient negative resistance for compensating the losses in the LCresonant tank. Note that parasitic capacitances on the order of several tens of pico-Farads are inevitably associated with these transistors. On the other hand, for a MMW design, the values of the inductance and capacitance of the resonant tank are also on the order of femto-Henry and several tens of pico-Farads, respectively. Therefore the parasitic capacitive effect due to the cross-coupled transistors will become dominant at the oscillation frequencies of MMW VCO. In this letter, we regard the parasitic capacitance as a varactor in cross-coupled transistors, which avoids the use of low-Q accumulation-mode MOS varactor, so that the parasitic capacitance effect is minimized in designing a 68 GHz VCO as shown in Fig. 1. The triple-well device with the intrinsic junction capacitances are also illustrated in Fig. 2.  $C_{\rm gsov}$  and  $C_{\rm gdov}$  are the overlap capacitances.  $C_{\rm ds}$  is the drain-source capacitance.  $C_{\rm db}$  is the p-n junction capacitance between drain and bulk of the NMOS (M1 or M2). In the normal operation of an NMOS, the depletion region between the drain and bulk is formed and the p-n junction is re-

467

Fig. 2. Triple-well device with the intrinsic junction capacitances.

verse-biased. Once the voltage is decreased at the n-type terminal or increased at the p-type terminal, the depletion region between the drain and bulk is reduced, resulting in a larger junction capacitance  $C_{db}$ . It can be seen in Fig. 2 that the junction capacitance  $C_{\rm db}$  increases from 8.9 to 12.1 fF when the voltage  $V_{\text{tune}}$  is increasing from 0 to 1 V. However, the drain to bulk voltage must be limited to be less than the turn-on voltage to prevent the p-n junction from entering into the forward-biased region. Besides, the capacitance  $C_{gsov}$  slightly increases with increasing  $V_{\text{tune}}$ . Contrarily, the capacitances  $C_{\text{gdov}}$  and  $C_{\rm ds}$  are insensitive to the voltage  $V_{\rm tune}$ . The effective capacitance  $C_v$  at the drain of M1 or M2 is approximately equal to  $4C_{\rm gdov} + C_{\rm gsov} + C_{\rm ds} + C_{\rm db}$ . The tuning range of  $C_{\rm max}/C_{\rm min} =$  $C_v(V_{\text{tune}} = 1 \text{ V})/C_v(V_{\text{tune}} = 0 \text{ V}) \sim 1.1$  in this proposed intrinsic-tuned technique is achieved. A center-tap inductor is utilized for providing the inductance in the LC resonant tank. The top two metals (Metal seven and eight) are stacked together, giving a total metal thickness of 4.8  $\mu$ m-thick for decreasing the conductor loss. Hence the inductor Q is further improved. Simulations show that an inductance L of 54 pH along with a Q of 20 is obtained at 69.8 GHz. The resonant tank Q of the MMW VCO does not degrade much by the use of the proposed intrinsic tuning topology. The resonant frequency of the proposed VCO can be predicted approximately to be  $\omega_0 = 1/\sqrt{L(C_v + C_{\text{buf}_{\text{in}}})}$  when the input capacitance  $C_{\text{buf}_{\text{in}}}$ of the output buffer amplifier is taken into account. The output buffer amplifier is designed to prevent the oscillation from frequency drift in future integration. The stack winding inductor is utilized as the choke for the buffer amplifier of the VCO due to its merit of small-size. In the conventional stack inductor design, the distance d between the coil and reference ground is nonzero (e.g., 15  $\mu$ m) to prevent the coupling caused from other coils or wirings for keeping the inductance stable. Nevertheless, it has been verified by simulation and measurement results that the closed ground (i.e.,  $d = 0 \ \mu m$ ) stack inductor contributes at least 75% area reduction factor compared to the condition of  $d = 15 \ \mu \text{m}$  under the similar inductance from dc to 67 GHz  $(L_{\text{buff}} \sim 0.21 \text{ nH})$ , which can greatly reduces the whole size of the VCO.

## **III. EXPERIMENTAL RESULTS**

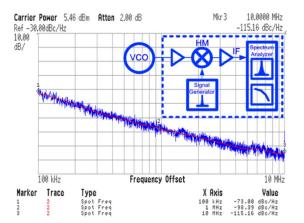

The overall measurement setup for the phase noise is shown in the inset of Fig. 3. The VCO is measured via on-wafer probing with an Agilent 11970 V harmonic mixer (HM) which

Fig. 3. Measurement setup and measured phase noise of the proposed VCO.

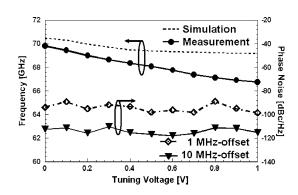

Fig. 4. Measured characteristics of oscillation frequency and phase noise versus tuning voltage.

down-converts the output of VCO to an IF of  $\sim$  365 MHz. And then the IF is further analyzed by the Agilent E4448A 50 GHz spectrum analyzer [2], [4]. Note that two off-chip amplifiers, one before and the other after HM, have been used to compensate for loss due to measurement setup. The circuit is measured with 7.2 mA bias current from a 0.6 V supply. This is the lowest supply voltage among all previously reported CMOS-based MMW VCOs [1]–[6], [8]. If  $V_{DD}$  is increased to 1.2 V, simulation results show that both the oscillation frequency and tuning range decrease while the power consumption increases. Note that under the condition of  $V_{\rm DD}=0.6~{

m V}$  and  $V_{

m tune}=$ 1 V, 10.73  $\mu$ A is going to the PN junction between the bulk and source of M1 (or M2). Since this current is much lower than that (3.6 mA) of drain to source  $(I_{ds})$  of M1, its impact is negligible. The discrepancy of  $V_{\text{tune}}$  and  $V_{\text{bulk}}$  is due to the use of large resistor R (50 k $\Omega$ ) between them. From simulations, it is found that the leakage current from bulk to source will become appreciable, i.e., reaching 1/100 of Ids, only when  $V_{\rm tune}$  is greater than 2.25 V. Fig. 4 shows characteristics of the phase noise and frequency tuning range (FTR) versus the tuning voltage varied from 0 to 1 V, respectively. The circuit operates with a FTR of 4.5% from the lowest frequency of 66.7 GHz to the highest frequency of 69.8 GHz. Note that while the simulated oscillation frequency is flattened near 1 V, which is consistent with the trend of junction capacitive Cv (see Fig. 2), the measured oscillation frequency does not show this trend. The discrepancy in the tendency between the measured and simulated oscillation frequencies may be attributed to the

| Ref.           | Technology<br>[µm] | Technique<br>Note     | f₀<br>[GHz] | FTR<br>[%] | PN [dBc/Hz] |         | Power      | FOM [dBc/Hz] |         | FOM <sub>t</sub> [dBc/Hz] |         |

|----------------|--------------------|-----------------------|-------------|------------|-------------|---------|------------|--------------|---------|---------------------------|---------|

|                |                    |                       |             |            | 1MHz        | 10MHz   | [mW]       | 1MHz         | 10MHz   | 1MHz                      | 10MHz   |

| [1] ISSCC 2001 | CMOS 0.25          | MOS-Var.              | 50          | 2          | -97         | 1       | 13 @1.3V   | -179.8       | 1       | -165.8                    | 1       |

| [2] JSSC 2006  | CMOS 0.13          | MOS-Var.              | 56.5        | 10.27      | -89         | -108    | 9.8 @1.5V  | -174.13      | -173.13 | -174.36                   | -173.36 |

|                |                    |                       | 98.5        | 2.54       | 1           | -102.7  | 7 @1.5V    | 1            | -174.12 | 1                         | -161.63 |

| [3] ISSCC 2005 | CMOS 0.12          | Differential MOS-Var. | 44          | 9.8        | -101        | 1       | 7.5 @1.5V  | -185         | 1       | -184.8                    | 1       |

| [4] ISSCC 2007 | CMOS 0.065         | MOS-Var.              | 70.2        | 9.55       | 1           | -106.14 | 5.4 @1.2V  | 1            | -175.76 | 1                         | -175.36 |

| [5] ISSCC 2005 | CMOS 0.13          | Push-Push<br>MOS-Var. | 114         | 2.11       | 1           | -107.6  | 8.4 @1.2V  | 1            | -179.5  | 1                         | -165.96 |

| [6] EL 2006    | CMOS 0.13          | Push-Push<br>MOS-Var. | 192.1       | 0.68       | 1           | -100    | 16.5 @1.5V | 1            | -173.49 | 1                         | -150    |

| [8] ISSCC 2006 | CMOS 0.09          | Resonator             | 60          | 0.2        | -100        | 1       | 1.9 @1.0V  | -193         | 1       | -158.8                    | 1       |

| This Work      | CMOS 0.13          | Intrinsic Cap.        | 69.8        | 4.5        | -98.4       | -115.2  | 4.32 @0.6V | -188.9       | -185.7  | -182                      | /-178.8 |

TABLE I

Performance Comparison of State-of-the-art Millimeter-Wave VCO

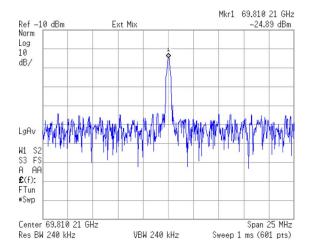

Fig. 5. Spectrum of the proposed VCO before calibrating the cable loss of 9.5 dB.

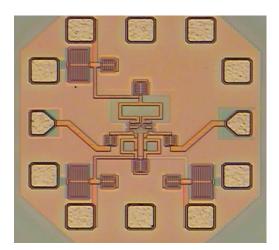

Fig. 6. Chip micrograph of proposed VCO.

inadequate modeling provided by the foundry, which is valid only up to 30 GHz. Measured phase noises of < -89 dBc/Hz and < -110 dBc/Hz at 1 and 10 MHz offset away from the carrier, respectively, are achieved over the whole tuning voltage. Output power of > -24.8 dBm without calibrating the cable loss of 9.5 dB is also obtained as shown in Fig. 5. The carrier power is much smaller than that in Fig. 3 because no amplifier/HM is used for this measurement. The die micrograph of the fabricated VCO including the buffer amplifier is shown in Fig. 6 with the core size of only  $120 \times 130 \ \mu m^2$ .

## IV. CONCLUSION

In this letter, the intrinsic-tuned 68 GHz VCO without an extra low-Q device is reported. This VCO achieves a phase noise of -115 dBc/Hz at 10 MHz offset, which is 7.2 dB better than the best [2] of all previous publications. Besides, compared with previous >60 GHz MMW VCOs [2], [4]–[6], [8], it is also found that the proposed VCO obtains the best FOM taking FTR into account [4] of -182/-178.8 dBc/Hz at 1/10 MHz offset, which is attributed to the removal of the low-Q varactor in the tunable oscillator (see Table I).

### REFERENCES

- H. Wang, "A 50 GHz VCO in 0.25 μm CMOS," in *ISSCC Tech. Dig.*, Feb. 2001, pp. 372–373.

- [2] C. Cao and K. K. O, "Millimeter-Wave voltage-controlled oscillators in 0.13 μm CMOS technology," *IEEE J. Solid-State Circuits*, vol. 41, no. 6, pp. 1297–1304, Jun. 2006.

- [3] J. Kim, J. O. Plouchart, N. Zamdmer, R. Trzcinski, K. Wu, B. J. Gross, and M. Kim, "A 44 GHz differentially tuned with 4 GHz tuning range in 0.12 µm SOI CMOS," in *ISSCC Tech. Dig.*, Feb. 2005, pp. 416–417.

- [4] D. D. Kim, J. Kim, J. O. Plouchart, C. Cho, W. Li, D. Lim, R. Trzcinski, M. Kumar, C. Norris, and D. Ahlgren, "A 70 GHz manufacturable complementary LC-VCO with 6.14 GHz tuning range in 65 nm SOI CMOS," in *ISSCC Tech. Dig.*, Feb. 2007, pp. 540–541.

- [5] P. C. Huang, M. D. Tsai, H. Wang, C. H. Chen, and C. S. Chang, "A 114 GHz VCO in 0.13 μm CMOS technology," in *ISSCC Tech. Dig.*, Feb. 2005, pp. 404–405.

- [6] C. Cao, E. Seok, and K. K. O, "192 GHz push-push VCO in 0.13 μm CMOS," *Electron. Lett.*, vol. 42, pp. 208–210, Feb. 2006.

- [7] F. Ellinger, T. Morf, G. V. Buren, C. Kromer, G. Sialm, L. Rodoni, M. Schmatz, and H. Jsckel, "60 GHz VCO with wideband tuning range fabricated on VLSI SOI CMOS technology," in *IEEE MTT-S Int. Dig.*, Jun. 2004, pp. 1329–1332.

- [8] D. Huang, W. Hant, N. Y. Wang, T. W. Ku, Q. Gu, R. Wang, and M. C. F. Chang, "A 60 GHz CMOS VCO using on-chip resonator with embedded artificial dielectric for size, loss and noise reduction," in *ISSCC Tech. Dig.*, Feb. 2006, pp. 1218–1227.

- [9] H. Wang, "A 9.8 GHz back-gate tuned VCO in 0.35 μm CMOS," in ISSCC Tech. Dig., Feb. 1999, pp. 406–407.

- [10] R. Murji and M. J. Deen, "Noise contributors in 7.2 GHz low-power VCO with automatic amplitude control," in *Proc. IEEE RFIC Symp.*, Jun. 2005, pp. 407–410.