## A 0.6V pure MOS voltage Reference for Bio-medical applications with 40ppm/0c temperature drift

R Nagulapalli, K.Hayatleh, S. Barker, S.Raparthy, N Yassine, F J Lidgey

This paper exploits the well-known CMOS beta multiplier circuit to synthesize a voltage reference, which is well suitable for low voltage and ultra-low power bio-medical applications. The present technique uses only MOS transistors to generates PTAT and CTAT currents. Self-biasing technique has been used to minimize the temperature and power supply dependency. A prototype in 65nm CMOS has been developed, at room temperature it is generating 404mV reference voltage with 2.6mV drift over wide temperature range (from -40 to 125°C). This has been designed to operate with a power supply voltage down to 0.6V and consumes 1.4uA current from the supply. The simulated temperature coefficient is  $40 ppm/^{0}C$ . Circuit occupies 0.0039 mm2 area.

Introduction: A low voltage bandgap reference, specifically one that can operate on low voltage is always challenging. There is a growing requirement that operates in wide range applications including filters, memory, data converters, bio-medical applications [1]. Portable and wearable bio-medical devices are capable of detecting signals in areas such as electrocardiography(ECG) and electroencephalography(EEG), sensing these sensitive signals require high precision ADC (~12 bit), which requires highly accurate and low power voltage reference circuit.

The fundamental operating principle of a reference circuit is to generate scaled combination PTAT and CTAT current/voltage to generate temperature independent voltage. There have been several attempts to build this concept. A typical low voltage bandgap [2] uses BJT's to generate PTAT current and to fabricate in the standard CMOS process parasitic vertical PNP Bipolar Junction Transistor (BJT) has been used. This has three problems, one is these transistors are having poor current gain  $(\beta)$  and sensitive to process variation which could lead to temperature drift of the reference voltage. The second problem is the power supply voltage requirement, Vbe of the BJT (~0.7V) doesn't scale with the process and limits the supply voltage. The third problem is BJT bias current is significantly high compared to the counterpart (MOSFET), which is a big problem the for the bio-medical and wearable application. Hence there is a clear motivation for pure MOS transistor based designs.

Peaking current source has been modified as bandgap reference by exploiting the difference between Vgs of two transistors [3], but this requires cascading of transistors hence not suitable for low voltage and poor power supply rejection, which demands a Voltage Regulator. Another method is to generate reference based on extrapolated MOSFET threshold voltage (Vth) at very low temperature to realize low voltage operation [4], but this has unacceptable process variation which requires calibration. [5][6] are based on mutual cancellation of mobility and threshold voltage, but it is difficult to track both variations and often very sensitive to the transistor models very strongly, which might create yield problem while going for mass production. Most of the designs use op-amps in the core circuit to achieve high performance such as temperature independence, power supply insensitivity, but they come at the expense of power and area [7]. These designs require voltage headroom's also, which makes them not suitable for low voltage applications. This paper explores standard beta multiplier circuit to generate PTAT and CTAT currents and finally bandgap reference voltage generation. Some of the key metrics differentiate our work from the state of art is low power, low voltage, and less complexity. The rest of the paper organized as follows. Section 2 introduces the beta multiplier circuit and qualitative treatment of its PTAT and CTAT nature, Section 3 describes proposed reference circuit and implementation details. Finally, section 4 summarizes the simulation results and layout of the prototype

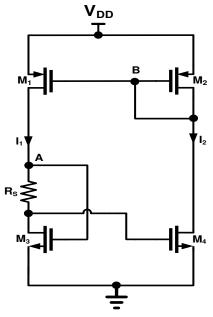

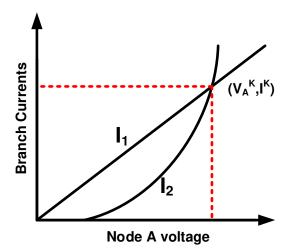

2. Beta Multiplier: Fig:1 shows the beta multiplier (constant gm) conventional circuit [8]. The fundamental principle of working is to create a voltage drop equal to the difference between the V<sub>GS</sub> of two transistors carrying same current but different sizes (W/L). Transistor  $M_3$ , $M_4$  connected in a such a way that  $V_{gs3}$ - $V_{gs4}$  defines current through Rs. The current mirror formed by M2,M1 will force the same current through Transistors M3,M4. Though this is a very common circuit, feedback mechanism in this circuit is very subtle. Fig:2 shows the I-V characteristics of M<sub>3</sub>,M<sub>4</sub>. From the figure, circuit settles at the intersecting point of the two curves. During the circuit converging to the

desired operating, it can be either side of the intersecting point. If the current lesser than the desired one means  $I_1 > I_2$  and vice versa. If  $I_1 - I_2 > 0$ , then circuit current must increase. Current can be increased by increasing voltage of the node A. So feedback should work in such a way that somehow node A has to increase if circuit detects I<sub>1</sub>-I<sub>2</sub>>0 and vice versa. Since M<sub>1</sub>,M<sub>3</sub> connected in series, node A can detect the current difference and it increases according to i1-i2 polarity hence by connecting Node A to gate of the M3, circuit acts as negative feedback circuit.M<sub>3</sub> aspect ratio (W/L) must be higher than M4, because V<sub>gs3</sub> has to be lesser than V<sub>gs4</sub>. To save power this circuit has been designed in the deep sub-threshold region by increasing the devices sizes and controlling resister R<sub>s</sub>.

Drain current of the NMOS operating in the sub-threshold region can be expressed as follows.

$$I_D = \frac{w}{L} I_0 exp\left(\frac{v_{gs} - v_{th}}{\eta v_T}\right) \left(1 - exp\left(\frac{-v_{ds}}{v_T}\right)\right)$$

(1) Where  $I_o = \mu_n C_{ox}(\eta - 1) V_T^2$ , and W is the width is the length,  $\mu_n$  is

electron mobility,  $C_{ox}$  is gate oxide capacitance,  $\eta$  is sub-threshold slope factor,  $V_T$  is thermal voltage,  $V_{th}$  is threshold voltage. For Vds>4VT (~100mV at room temperature), vds term in (1) is very less and Id is

almost independent of vds, it is expressed as

$$I_D = \frac{w}{L} I_0 exp\left(\frac{v_{gs} - v_{th}}{\eta v_T}\right)$$

$$V_{gs} = V_{th} + \eta V_T \ln\left(\frac{I_d}{\frac{w}{L}I_0}\right)$$

(2)

$$V_{gs} = V_{th} + \eta V_T \ln \left( \frac{I_d}{\frac{W}{I_0}} \right)$$

(3)

Fig. 1 Beta Multiplier circuit

Fig. 2 V-I characteristics of the beta multiplier

The circuit configuration as shown in fig:1(a) constrains the difference between vgs of M3, M4 in a relation given as follows.

$$V_{gs3} - V_{gs4} = I_1 R_s (4)$$

Substituting (3) into (4) results the transistor current as follows.

$$I_1 R_s = \eta V_T \ln \left[ \frac{\left(\frac{W}{L}\right)_4}{\left(\frac{W}{L}\right)_2} \right] \tag{5}$$

If the aspect ratio of M<sub>4</sub> is β times higher than M<sub>3</sub>, then current can be expressed as

$$I_1 = \frac{\eta V_T \ln(\beta)}{R_S} \tag{6}$$

From (6), the voltage drop across Rs is PTAT, because thermal voltage (KT/q) increases with temperature. A PTAT current carrying Transistor gate to source voltage (Vgs) and threshold voltage (Vth) decreases with temperature [12], because increasing temperature will increase electrons thermal energy and requires less voltage to invert the channel in the MOSFET and it can be approximated as a first order polynomial with a negative slope as follows.  $V_{gs}(T){\sim}V_{gs}(T_0)+K_{th}(\frac{T}{T_o}-1)$

$$V_{gs}(T) \sim V_{gs}(T_0) + K_{th}(\frac{T}{T_-} - 1)$$

(7)

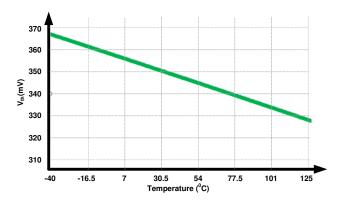

Where Kth is temperature coefficient of  $V_{\rm gs}$ . Fig. 3 shows the simulated gate to source voltage of the transistor wrt temperature., it has been showing CTAT nature with -0.3mV/°C temp coefficient.

Fig. 3 Gate to source voltage wrt temperature

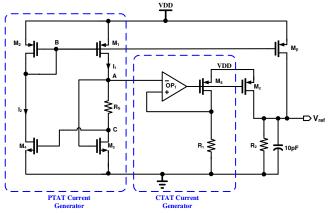

3. Proposed Bandgap reference circuit: As explained in the introduction, the idea of bandgap reference is scaled summation of PTAT and CTAT current's and convert into voltage. From the section 2, Beta multiplier bias current is having PTAT nature. Unfortunately, CTAT current is not available in beta multiplier, but Vgs3 will have CTAT nature, using a conventional voltage to current converter formed by OP<sub>1</sub>,M<sub>5</sub>,R<sub>1</sub> will create CTAT current through M5.Fig:2 shows the proposed full schematic of the bandgap reference. It contains Beta multiplier, V to I converter and current summation network. Mp carries PTAT current and Mc carries CTAT and hence the voltage across R2 is temperature independent voltage. To have a flexible design and minimize the resister values, used scaling factors  $\alpha_1$  and  $\alpha_2$  in the current mirrors  $M_1, M_p$  and  $M_5, M_c$  respectively.

Current through  $M_p$  is given by  $\alpha_1 \frac{V_{gs3}}{R_1}$

Voltage across R2 is given by the following expression

$$V_{\text{ref}} = \left[ \alpha_1 \frac{\eta V_T \ln(\beta)}{R_S} + \alpha_2 \frac{V_{gs3}}{R_1} \right] R_2$$

$$= \left( \alpha_1 \eta V_T \ln(\beta) + \frac{R_s}{R_1} \alpha_2 V_{gs3} \right) \frac{R_2}{R_s}$$

(8)

Fig. 4 Proposed bandgap Reference

For minimizing the temperature coefficient of the reference voltage,  $\frac{\partial V_{\text{ref}}}{\partial r} = 0$  at a known temperature. Hence by differentiating (8) we can

$$\alpha_1 \frac{R_1}{R_s} \frac{\partial V_T}{\partial T} \ln(\beta) + \alpha_2 \frac{\partial V_{gs3}}{\partial T} = 0 \tag{9}$$

deduce the following condition.  $\alpha_1 \frac{R_1}{R_s} \frac{\partial V_T}{\partial T} \ln(\beta) + \alpha_2 \frac{\partial V_{gs3}}{\partial T} = 0 \qquad (9)$  At room temperature  $\frac{\partial V_T}{\partial T} = 0.087 mV/^0 C$  and from previous section  $\frac{\partial V_{gs3}}{\partial T} = -0.3 mV/^{0} \text{C}$ . We have chosen  $\alpha_{1} = \frac{1}{3}$ ,  $\alpha_{2} = 1$  for the design flexibility and  $\beta$ =24 for the layout matching between M<sub>3</sub>, M<sub>4</sub>. Substituting these values into (9) we can show that  $\frac{R_{1}}{R_{s}}$ =3.255 to keep a perfect balance between CTAT, PTAT current and hence minimum temperature drift.

Fig. 5 Self-bias CTAT generator

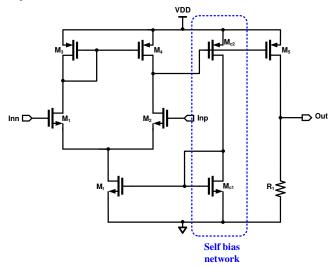

CTAT circuit is a voltage to current converter with Vgs as input. As shown in Fig:4, OP<sub>1</sub> adjusts the current through M5 until the voltage drop across R1 equals to the Vgs of the M3. The bottle neck here is any offset in the opamp will also convert as current, which will create an error in the desired CTAT current, hence opamp needs to design with ultra-low offset. Increasing device sizes in the opamp will decrease the offset, but due to inverse square law relation between offset and device area [10], this method occupies a lot of silicon area. Very-efficient and well known way of minimizing the offset will be chopper stabilization method but this needs a clock generator and ripple filter [11]. Self-bias is one way of biasing analog circuits which will have minimal offset, less temperature drift, so we have chosen self-bias scheme [9] and Fig:5 shows the detailed implementation of the circuit. M<sub>1</sub>,M<sub>2</sub>,M<sub>3</sub>,M<sub>4</sub>,M<sub>t</sub> forms the opamp and M<sub>5</sub>,R<sub>1</sub> forms the current converter. M<sub>c2</sub>, Mc<sub>1</sub> transistors produce bias voltage required for the Mt by sensing the output of the opamp. Unfortunately, self-biasing needs start up circuit to kick the circuit from undesired zero current operating point, for simplicity start-up circuit hasn't shown in fig:5.

Fig. 6 Self-bias CTAT open-loop response

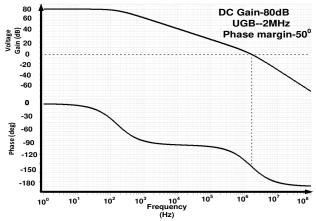

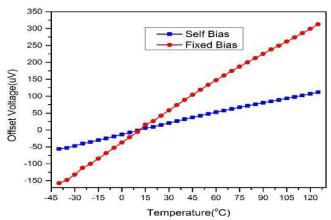

Fig:6 shows the open loop frequency response of the CTAT current generator, which has been designed with 80dB dc gain to minimize the systematic offset and 50° phase margin for a well-behaved transient response. To assess the efficiency of the self-bias strategy, opamp offset variation with temperature has been simulated and compared with a fixed bias (means Mt bias has been derived from a diode connected transistor carrying fixed current). Fig:7 shows the offset of the opamp, which shows 3x improvement with self-bias scheme.

Fig. 7 Simulated Offset of the self-bias opamp

## 4. Bandgap reference simulation results:

Proposed circuit has been implemented in 65nm 1-poly 8-metal CMOS technology, Table-1 shows the parameters of the transistors and resisters used in the proposed voltage reference circuit.

TABLET

| Transistors       |                |                   |                |  |  |

|-------------------|----------------|-------------------|----------------|--|--|

| Bandgap Reference |                | Self-Bias Opamp   |                |  |  |

| Component<br>Name | W/L<br>(um/um) | Component<br>Name | W/L<br>(um/um) |  |  |

| $M_1$             | 42/3.2         | $M_1$             | 5/2            |  |  |

| $M_2$             | 42/3.2         | M <sub>2</sub>    | 5/2            |  |  |

| M <sub>3</sub>    | 48/3           | M <sub>3</sub>    | 8/3            |  |  |

| $M_4$             | 2/3            | M <sub>4</sub>    | 8/3            |  |  |

| M <sub>5</sub>    | 32/3           | Mt                | 10/2           |  |  |

| Mc                | 32/3           | M <sub>c1</sub>   | 5/2            |  |  |

| $M_p$             | 14/3.2         | M <sub>c2</sub>   | 8/3            |  |  |

| Resisters      |                 |  |

|----------------|-----------------|--|

| Component Name | Resistance (KΩ) |  |

| Rs             | 70              |  |

| $R_1$          | 227.85          |  |

| R <sub>2</sub> | 312             |  |

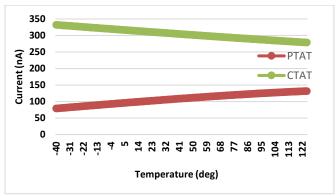

Simulations have been performed on layout extracted netlist and results as follows. Fig:8 shows the CTAT and PTAT, scaled summation of these currents produces reference voltage according to the equation (9).

Fig. 8 CTAT and PTAT currents.

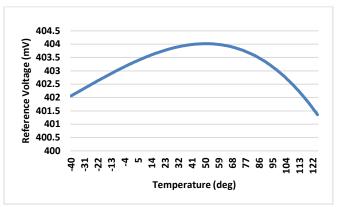

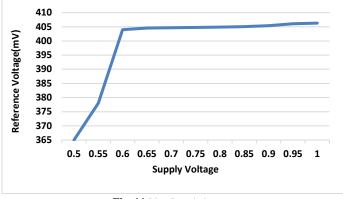

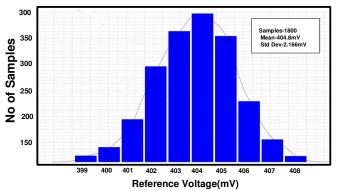

Fig.9 shows the bandgap reference voltage (voltage across R<sub>2</sub>) variation from -40°C to 125°C. At room temperature reference voltage is 404mV, the maximum deviation of the voltage over full temperature range is 2.64mV means 0.65% accuracy and this design achieves 40ppm/°C while powered from 0.6V supply. The circuit starts working properly when power supply voltage greater than or equal to 0.6V. Minimum working power supply voltage 0.6V limited by CTAT generator opamp. In the supply voltage range from 0.6 to 1V, reference voltage changes by 2.3mV means the supply or line sensitivity is 1.8%/V. Yield is the main parameter for volume semiconductor products, hence Monte Carlo variation is critical results for any sensitive circuits like the present one. Fig:11 depicts the histogram of the reference voltage, showing 2.166mV standard deviation with a mean of 404mV.

Fig. 9 Bandgap reference voltage wrt temperature.

Fig. 11 Line Regulation.

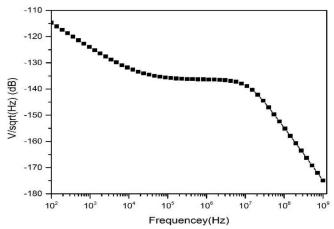

Fig:12 shows the simulated power spectral density (PSD) of the reference voltage. From the noise analysis of the circuit, flicker noise of transistor  $M_3$ , $M_4$  and channel thermal noise of the CTAT generator

opamp (OA<sub>1</sub>) are the dominate noise contributors. The summary of the performance listed in table II.

Fig. 11 Simulated distribution

Fig. 12 Simulated PSD of the output voltage.

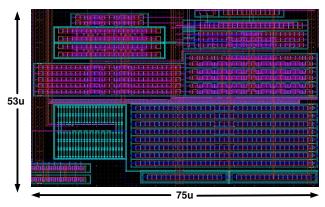

The layout of the proposed circuit is shown in Fig. 13, and the active area is 75um\*53um. Every transistor has been laid with proper care towards Mismatch. Special care has been taken for well-proximity effect (WPE) and Shallow trench isolation (STI), by adding enough dummies for each device and keeping MOSFET away from NWELL [13].

Fig. 13 Layout of the proposed Technique

TABLE II Performance Summary

| i ciroimance summary    |            |                     |  |  |

|-------------------------|------------|---------------------|--|--|

| Parameter               | Value      | Units               |  |  |

| Minimum Supply Voltage  | 0.6        | V                   |  |  |

| Current consumption     | 1.4        | uA                  |  |  |

| Output Voltage          | 404        | mV                  |  |  |

| Temperature range       | -40 to 125 | °C                  |  |  |

| Temperature Coefficient | 40         | ppm/ <sup>0</sup> C |  |  |

| Integrated Noise (.1-10KHz) | 41   | uV              |

|-----------------------------|------|-----------------|

| Technology                  | 65   | nm              |

| Area                        | 3975 | um <sup>2</sup> |

Conclusion: A low voltage bandgap reference circuit has been proposed and demonstrated 40ppm/<sup>0</sup>C temperature coefficient. With the help of Sub-threshold MOSFET current equation, closed form for the output voltage has been derived and it is closely matching with the simulation results. A transistor level Demonstration with the layout shown and all results have been explained in the last section.

R. Nagulapalli, K. Hayatleh, S. Barker and F J Lidgey (Faculty of Technology, Design and Environment, Oxford Brookes University, Wheatley Campus, Oxford, OX33 1HX, UK) E-mail: khayatleh@brookes.ac.uk

## References

- 1. Hui Zhang et al., "Design of an Ultra-Low Power SAR ADC for Biomedical Applications", IEEE International Conference on Solid-State and Integrated Circuit Technology, pp. 460-462, November 2010

- 2. H. Banba, H. Shiga, A. Umezawa, T. Tanzawa, S. Atsumi and K. Sakui, "A CMOS Bandgap Reference Circuit with Sub-1 -V Operation," IEEE Journal of Solid-state Circuits, vol. 34, pp. 670-674, May 1999.

- 3. Cheng M H, Wu Z W. Low-power low-voltage reference using peaking current mirror circuit. Electron Lett, 2005, 41(10): 572

- 4. W. G. B. S. Colombo D and S. P, "Voltage reference design using 1V power supply in 0.13um cmos technology," Latin American Symposium on Circuits and Systems, pp. 1–4, 2013.

- 5. L.Najafizadeh and I. Filanovsky, "Towards a Sub-1V CMOS Voltage Reference," International Symposium on Circuits and Systems, pp. 53–56, May 2004.

- 6. I. Filanovsky and A. Allam, "Mutual Compensation of Mobility and Threshold Voltage Temperature Effects with Applications in CMOS circuits," IEEE trans. Circuits and Systems I, pp. 876–884, 2001.

- 7. G. Palmisano, G. Palumbo, S. Pennisi, "Design Procedure for Two-Stage CMOS Tran Conductance Operational Amplifiers: A Tutorial" in Analog Integrated Circuits and Signal Processing, vol. 27, pp. 179-189, 2001.

- 8. Song Liu and R. Jacob Baker, "Process and Temperature Performance of a CMOS Beta-Multiplier Voltage Reference", Midwest Symposium on Systems and Circuits, August 09-12, 1998, South Bend, Indiana.

- 9. R. T. Perry, S. H. Lewis, A. P. Brokaw, T. R. Viswanathan, "A 1.4 V supply CMOS fractional bandgap reference", *IEEE J. Solid-State Circuits*, vol. 42, no. 10, pp. 2180-2186, Oct. 2007.

- 10. M. J. Pelgrom, A. C. J. Duinmaijer, and A. P. G. Welbers, "Matching properties of MOS transistors," IEEE J. Solid-State Circuits, vol. 24, pp. 1433–1439, Oct. 1989

- 11. F. Witte, K. Makinwa, J. Huijsing, Dynamic Offset Compensated CMOS Amplifiers, New York:Springer, 2010.

- 12. Wang A, Highsmith CB, Chandrakasan AP. Sub-threshold Design for Ultra Low-Power Systems. Springer: New York, 2006.

13. P. G. Drennan, M. L. Kniffin, and D. R. Locascio, "Implications of proximity effects for analog design," in Proc. IEEE Custom Integrated Circuits Conf., Sep. 2006, pp. 169–176.