## 8.7 A 1-to-6Gb/s Phase-Interpolator-Based Burst-Mode CDR in 65nm CMOS

Behrooz Abiri<sup>1</sup>, Ravi Shivnaraine<sup>1</sup>, Ali Sheikholeslami<sup>1</sup>, Hirotaka Tamura<sup>2</sup>, Masaya Kibune<sup>2</sup>

<sup>1</sup>University of Toronto, Toronto, Canada <sup>2</sup>Fujitsu Laboratories, Kawasaki, Japan

Burst-mode clock and data recovery circuits (BMCDR) are widely used in passive optical networks (PON) [1] and as a replacement for conventional CDRs in clock-forwarding links to reduce power [2]. In PON, a single CDR performs the task of clock and data recovery for several burst sequences, each originating from a different source. As a result, the BMCDR is required to lock to an incoming data stream within tens of UIs (for example 40ns in GPON). Previous works use either injection locking [3, 4] or gated VCO [5, 6] to achieve this fast locking. In both cases, the control voltage of the CDR's VCO is generated by a reference PLL with a matching VCO to guarantee accurate frequency locking. However, any component mismatch between the two VCO's results in a frequency offset between the reference PLL frequency and the CDR's VCO frequency, and hence in a reduction of the CDR's tolerance for consecutive identical digits (CID). For example, [7] reports a frequency offset of over 20MHz (2000ppm) for 10Gb/s operation. We present a BMCDR that is based on phase interpolation (PI), eliminating the possibility of local frequency offset between the reference and recovered clock. We demonstrate 1 to 6Gb/s operation in 65nm CMOS with a locking time of less than 1UI.

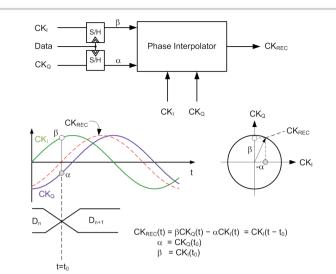

The principle of operation for the proposed PI-based BMCDR is illustrated in Fig. 8.7.1. Since the main function of a BMCDR is to align the rising edge of the clock with the data transition, we use the data to sample-and-hold (S/H) two quadrature clocks (CK<sub>1</sub> and CK<sub>0</sub>) with a pair of dual-edge-triggered S/H circuits. The samples of CK<sub>1</sub> and CK<sub>0</sub> at a data transition, denoted by  $\beta$  and  $\alpha$  respectively, are then used to interpolate between CK<sub>1</sub> and CK<sub>0</sub>. This, as shown on Fig. 8.7.1, produces a recovered clock (CK<sub>REC</sub>) with a rising edge that is aligned with the data transition. To demonstrate this analytically, assume  $sin(2\pi ft)$  and  $-cos(2\pi ft)$  represent CK<sub>1</sub> and CK<sub>0</sub> respectively. A data transition at  $t = t_0$  yields the PI coefficients  $\alpha = CK_0(t_0) = -cos(2\pi ft_0)$  and  $\beta = CK_1(t_0) = sin(2\pi ft_0)$ . As a result,  $CK_{REC}(t) = \beta CK_0(t) - \alpha CK_1(t) = sin(2\pi f(t-t_0))$  which is a clock whose zero crossing coincides with the data transition.

In our implementation, CK<sub>I</sub> and CK<sub>Q</sub> are provided externally; however, in an integrated system CK<sub>I</sub> and CK<sub>Q</sub> may be provided from a PLL or be generated from the forwarded clock. In the case of using a received clock, there is no frequency mismatch between CK<sub>I</sub>/CK<sub>Q</sub> and the embedded clock in the data. When using a PLL, a small frequency offset may be present between CK<sub>I</sub>/CK<sub>Q</sub> and the input due to a frequency error in the PLL reference. For sufficient transition density, the PI's output phase is updated at every data transition, hence any frequency offset between data and the reference clock is tracked.

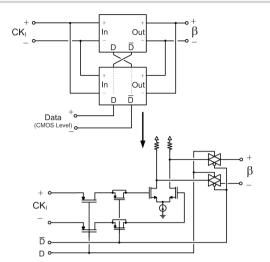

Figure 8.7.2 shows the circuit implementation of the dual-edge triggered S/H. Dual-edge sampling is implemented by connecting the outputs of two S/Hs operating at opposite data edges. Each S/H is implemented as a master/slave configuration triggered by either the rising or the falling edge of data. The S/Hs are able to track up to 6GHz clock signals and as such no extra capacitor besides the existing parasitic capacitance is required. A buffer is inserted between the pass transistors and the transmission gates to prevent charge sharing and to avoid any kickback from the output transmission gates to the input pass gates. To provide rail-to-rail levels for switching, a CML-to-CMOS converter is placed before the S/Hs.

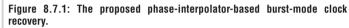

The circuit implementation of the analog PI is shown in Fig. 8.7.3. A differential trans-conductance stage is used to convert the coefficients ( $\alpha$  and  $\beta$ ) to current. The tails currents of CK<sub>I</sub> and CK<sub>Q</sub> are used as weighting factors in the PI. The operation of — $\alpha$ CK<sub>I</sub> +  $\beta$ CK<sub>Q</sub> is performed in current mode at the nodes of the resistors and then converted to an output voltage, CK<sub>REC</sub>. Since  $\alpha$  and  $\beta$  are differential signals, their signs can be changed. This allows the PI to create phases from 0° to 360°. Immunity to charge injection from the S/H is enhanced by providing inputs to the PI differentially.

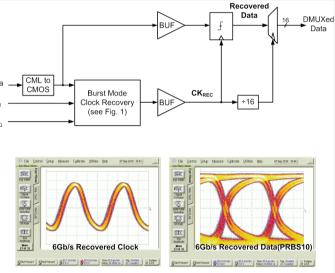

Figure 8.7.4 shows the block diagram of the entire receiver along with the recovered data for a 6Gb/s PRBS10 input. The output of the clock recovery unit is buffered to drive the input of the clock divider and flip-flop. To compensate for the delay of the buffer in the clock path, a replica of the  $CK_{REC}$  buffer is placed in the data path. The recovered clock and data are buffered further (not shown) to be observed off-chip for direct probing. The measured peak-to-peak clock jitter is 24ps and the eye opening for recovered data is 500mV. The CDR recovers a 6Gb/s PRBS7 sequence with a BER of less than 10<sup>-12</sup> in the presence of a 100MHz frequency offset between  $CK_I/CK_0$  and the input.

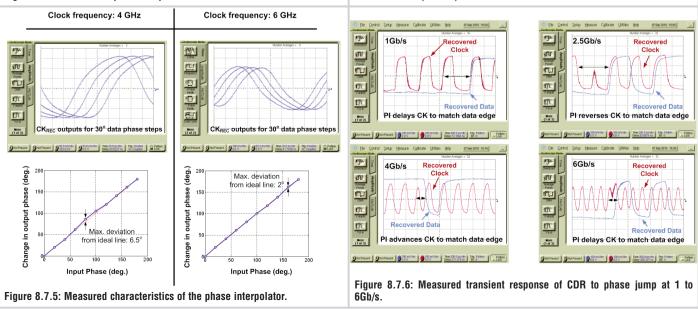

Figure 8.7.5 shows the measured characteristics of the PI. The input data has been phase shifted and the corresponding incremental phase shift of phase interpolator output at 4GHz and 6GHz has been recorded. At 4GHz and 6GHz, the recovered clock is shown for 30° input phase steps. The maximum deviation from ideal interpolation is  $6.5^{\circ}$  at 4GHz and 2° at 6GHz. The PI's latency and unequal delay between the clock path and the data path may produce a phase offset in the CDR. At 6Gb/s this delay was simulated to be less than one tenth of a UI and as such was left uncompensated.

To measure the time it takes for the clock edge to align with the data edge (locking time), a deliberate frequency offset is introduced. This frequency offset combined with a long CID introduces a phase jump that allows the CDR locking behaviour to be observed (Fig. 8.7.6). In the 1Gb/s and 6Gb/s cases, the clock is delayed by the PI in order to align with the data edge. In the 2.5Gb/s case, the clock is reversed whereas in the 4Gb/s case the clock is advanced. A Centellax OTB3P1A PRBS generator is used to create PRBS10 patterns from 1 to 6Gb/s. An Agilent DCA-J 81600C digital communication analyzer (with 8611A 20GHz electrical module) is used to capture sharp phase transitions in the recovered clock.

The chip is fabricated in a 65nm CMOS process. The receiver area is  $250 \times 70 \mu m^2$ , of which  $50 \times 70 \mu m^2$  is occupied by the clock recovery circuitry (S/H and PI). The chip operates from a 1.2V supply and consumes a total power of 22mW (excluding output drivers), of which 3.8mW is consumed by the clock recovery circuit.

## Acknowledgement:

The authors acknowledge the use of the University of Toronto's Advanced Digital Systems Lab and thank Saeid Rezaei for his help with the measurements.

## References:

[1] C. Liang and S. Liu, "A 20/10/5/2.5Gb/s Power-scaling Burst-Mode CDR Circuit Using GVC0/Div2/DFF Tri-mode Cells," *ISSCC Dig. Tech. Papers*, pp. 224-608, Feb., 2008.

[2] N. Miura, Y. Kohama, Y. Sugimori, H. Ishikuro, T. Sakurai, and T. Kuroda, "An 11Gb/s Inductive-Coupling Link with Burst Transmission," *ISSCC Dig. Tech. Papers*, pp. 298-614, Feb., 2008.

[3] J. Lee and M. Liu, "A 20Gb/s Burst-Mode CDR Circuit Using Injection-Locking Technique," *ISSCC Dig. Tech. Papers*, pp. 46-586, Feb., 2007.

[4] K. Maruko, T. Sugioka, H. Hayashi, Zhiwei Zhou, Y. Tsukuda, Y. Yagishita, H. Konishi, T. Ogata, H. Owa, T. Niki, K. Konda, M. Sato, H. Shiroshita, T. Ogura, T. Aoki, H. Kihara, and S. Tanaka, "Burst-Mode CDR Using Dual-Edge Injection-Locked Oscillator," *ISSCC Dig. Tech. Papers*, pp. 364-365, Feb., 2010.

[5] M. Nogawa, K. Nishimura, S. Kimura, T. Yoshida, T. Kawamura, M. Togashi, K. Kumozaki, and Y. Ohtomo, "A 10 Gb/s Burst-Mode CDR IC in 0.13µm CMOS," *ISSCC Dig. Tech. Papers*, pp. 228-229, Feb., 2005.

[6] L. Cho, C. Lee, and S. Liu, "A 33.6-to-33.8Gb/s Burst-Mode CDR in 90nm CMOS," *ISSCC Dig. Tech. Papers*, pp. 48-49, Feb., 2007.

[7] J. Terada, K. Nishimura, S. Kimura, H. Katsurai, N. Yoshimoto, and Y. Ohtomo, "A 10.3125Gb/s Burst-Mode CDR Circuit using a  $\Delta\Sigma$  DAC," *ISSCC Dig. Tech. Papers*, pp. 226-227, Feb., 2008.

8

Figure 8.7.2: Dual edge triggered sample and hold.

Figure 8.7.4: Receiver block diagram (top) and measured 6Gb/s recovered clock and data (bottom).

## **ISSCC 2011 PAPER CONTINUATIONS**

| Δ Clock Recovery 50×70µm   B BUF/0FF/DeMUX 200×70µm   C BERT 60×30µm   D CML Output Drivers 90×140µm   D CML Output Drivers 90×140µm |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Locking Method Gated VCO Injection Lock Injection Lock Phase Interpolator   Locking time 5UI 1UI < 20UI < 1UI   Power 1.2W 102mW 12.4mW 22mW   (cDR Core) (CDR Core) (CDR Core + DMUX)                                               |  |

| Figure 8.7.7: Die micrograph and comparison table.                                                                                                                                                                                   |  |

| rigure 6.7.7. Die interographi and comparison table.                                                                                                                                                                                 |  |

|                                                                                                                                                                                                                                      |  |