## Presented at the 2001 International Solid State Circuits Conference February 5, 2001

## A 10,000 Frames/s 0.18 μm CMOS Digital Pixel Sensor with Pixel-Level Memory

Stuart Kleinfelder, SukHwan Lim, Xinqiao Liu, Abbas El Gamal

> Stanford University Stanford CA 94305

In a Digital Pixel Sensor (DPS), each pixel has an ADC, all ADCs operate in parallel, and digital data is directly read out of the image sensor array as in a conventional digital memory [1]. The DPS architecture offers several advantages over analog image sensors including better scaling with CMOS technology due to reduced analog circuit performance demands and the elimination of column fixed-pattern noise and column readout noise. With an ADC per pixel, massively parallel conversion and high-speed digital readout become possible, completely eliminating analog readout bottlenecks. This benefits traditional high speed imaging applications and enables new imaging enhancement capabilities such as multiple sampling for increasing sensor dynamic range [2]. Achieving acceptable pixel sizes using DPS, however, requires the use of a 0.18 µm or below CMOS process, which is challenging due to reduced supply voltages and increased leakage currents [3].

This paper describes a 352x288 CMOS DPS with pixel-level digital memory fabricated in a standard digital 0.18 µm CMOS technology. The objectives of our design are: (i) to explore image sensor design in a 0.18 µm technology and demonstrate the scalability potential of DPS, (ii) to demonstrate the high frame rate potential of DPS by breaking both the 1 Giga-pixels/s and the 10,000 frames/s (fps) continuous full frame parallel ("snap-shot") image acquisition speed milestones, and (iii) to explore the benefits of pixel-level digital memory, e.g., pipelining for faster readout and focal-plane processing.

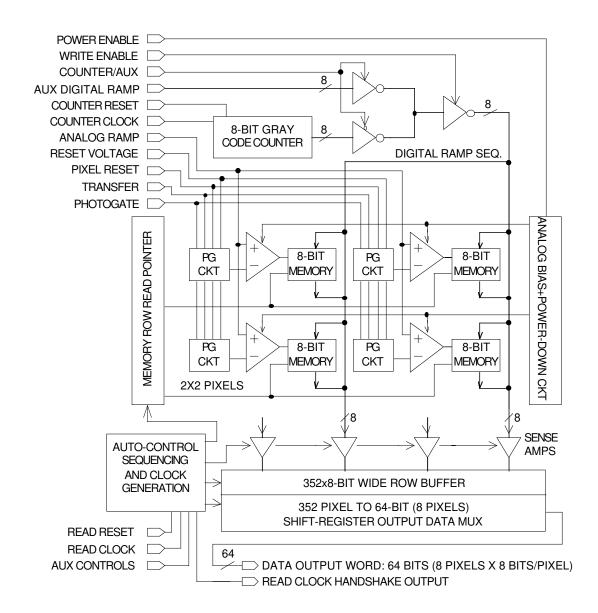

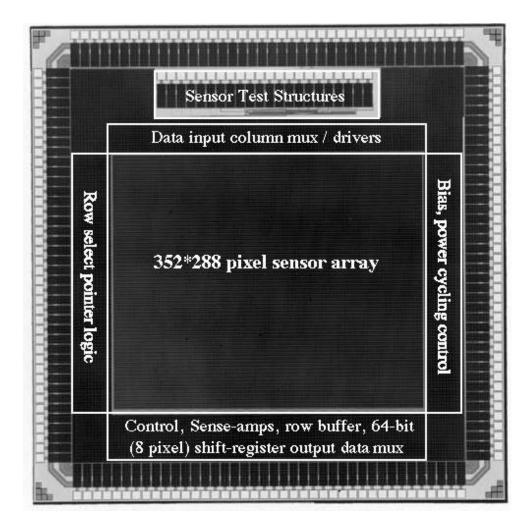

A block diagram of the DPS chip is shown in Figure 6.1.1. The core is a 352x288 array of pixels, each containing an nMOS photogate circuit, a comparator, and an 8-bit memory. The inputrelated periphery consists of an 8-bit Gray code counter, column drivers and multiplexers. Control periphery includes row-select pointer for addressing the pixel-level memory, comparator power down circuits, and timing control and clock generation circuits. Output periphery includes column sense-amps for reading the pixel-level memory, and an output multiplexing shift register.

Sensor operation can be divided into four main phases: reset, integration, ADC, and readout (Figure 6.1.2). At low to moderate frame rates (< 5,000 fps) much flexibility can be exercised regarding chip timing. For example, all phases can be kept separate to prevent noise due to analog to digital conversion and readout from corrupting the analog signals during charge integration and reset. Digital CDS can also be performed externally with an additional A/D conversion and readout immediately after reset. When operating at the highest speeds (>5,000 fps), it may be important to maximize integration time to collect as much light as possible. In this case, the reset and integration phases of each frame can be overlapped with the readout of the previous frame.

Pixel-level single-slope A/D conversion is simultaneously performed for all pixels after standard photogate integration and charge transfer. The analog ramp signal is generated off-chip and globally distributed to the pixel-level comparators. The 8-bit Gray-coded digital ramp sequence is generated by the on-chip counter and distributed via the memory bit lines. Each comparator fires as the ramp exceeds its signal value and the corresponding digital code is latched into the pixel-level memory. Alternatively, a digital ramp sequence that is generated off-chip can be used, allowing other conversion strategies such as logarithmic compression and expansion.

The pixel values are read out of the memory one row at a time using the read row-pointer and column sense-amps. Each row is then shifted out, while the next row is read out of the memory. To reach over 1 Giga pixels/s sustained throughput a 64-bit-wide readout bus operating at 167MHz is used. The readout operation is coordinated by on-chip control logic operating off of a frame reset strobe and a single clock. Since full-frame conversion and readout can be accomplished in under 100  $\mu$ s, average power consumption may be significantly reduced at low frame rates by powering down the comparators using on-chip digitally controlled power-down circuitry.

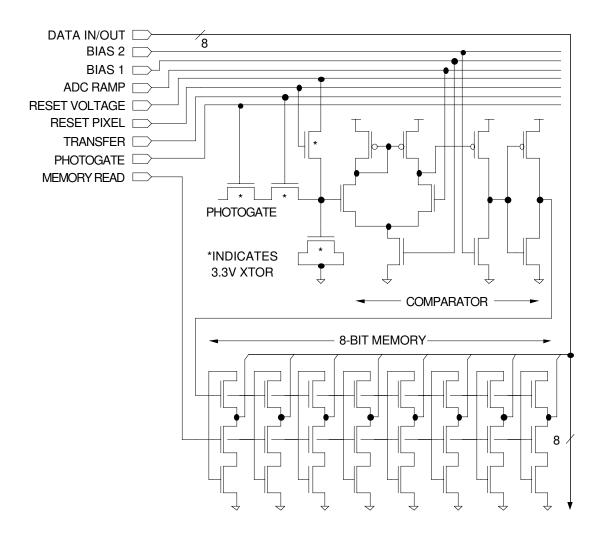

Each pixel includes an nMOS photogate, transfer and reset gates, a storage capacitor, a threestage comparator and 8-bit 3T dynamic memory cells (Figure 6.1.3). Photogate is used to achieve acceptable conversion gain. Thick oxide 3.3V transistors are used for the photogate, transfer gate, storage capacitor, and reset transistors to combat the high gate and sub-threshold leakage currents and the low supply voltage problems of the thin oxide 1.8V transistors. The comparator consists of a differential amplifier stage followed by two single-ended gain stages. It is designed to provide 10-bits of resolution at an input swing of 1V and worst case settling time of 80ns. This provides the flexibility to perform 8-bit A/D conversion down to 0.25V range in ~25µs, which is needed for high-speed, low light, operation. The 3T DRAM is designed for a maximum data hold time of 10 ms. This required the use of large gate length access transistors and holding the bit lines around Vdd/2 to combat the high transistor off-currents. Single-ended charge-redistribution column sense-amps are used for robustness against voltage coupling between the closely spaced bit lines. The comparator and pixel-level memory circuits can be electrically tested by applying analog signals to the sense node through the "Reset Voltage" signal, performing A/D conversion and reading out the digitized values.

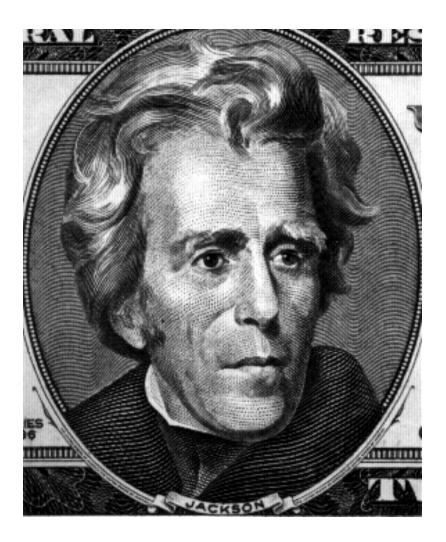

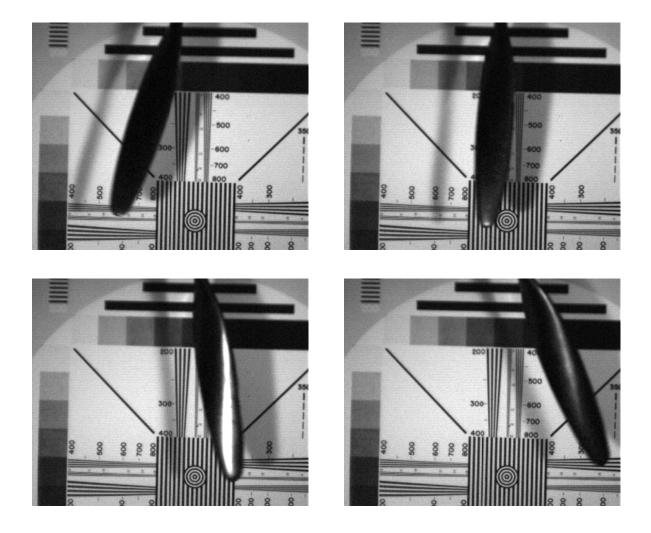

Figure 6.1.4 summarizes the main chip and sensor characteristics and performance. Figure 6.1.5 shows a typical image taken using ~1ms integration time (1,000 fps), while Figure 6.1.6 shows a sample image sequence taken at 10,000 fps, or >1 Giga-pixels/s continuous rate. It depicts a propeller rotating at ~2200 rpm in front of a motionless resolution chart, where every tenth frame is shown. A die photo-micrograph of the chip is shown in Figure 6.1.7.

## Acknowledgements:

The authors acknowledge the support of Kodak, Canon, HP, Agilent, Interval Research, and TSMC and the many contributions of Ting Chen, Khaled Salama, Hui Tian and Brian Wandell.

## References:

[1] A. El Gamal, D. Yang, and B. Fowler: "Pixel level Processing - Why?, What?, and How?" Proceedings of SPIE Vol.3650, pp. 2-13, Jan. 1999.

[2] D. Yang, A El Gamal, B. Fowler, H. Tian: "A 640x512 CMOS Image Sensor with Ultra Wide Dynamic Range Floating Point Pixel-Level ADC," Journal of Solid State Circuits, Vol. 34, No. 12, pp. 1821-1834, December 1999.

[3] H.-S. Wong, "Technology and Device Scaling Considerations for CMOS Imagers," IEEE Transactions on Electron Devices, vol. 43, no. 12, pp. 2131-2141, 1996.

Figure 6.1.1: DPS Block Diagram.

Figure 6.1.2: Simplified timing diagram (photodiode mode).

Figure 6.1.3: DPS pixel schematic.

| Technology:                             | 0.18 µm 5-metal CMOS           |

|-----------------------------------------|--------------------------------|

| Die size:                               | 5 mm by 5 mm                   |

| Array size:                             | 352 by 288 (CIF)               |

| Number of Transistors:                  | ~3.8 million                   |

| Output readout architecture:            | 64-bit bus @ 167MHz            |

| Maximum sustained output rates:         | >1 Gpixel/s, >10,000 fps       |

| Power dissipation, max @ 10K fps:       | ~50 mW                         |

| Pixel size:                             | 9.4 μm by 9.4 μm               |

| Photodetector type:                     | nMOS Photogate                 |

| Sensor fill factor:                     | 15 %                           |

| Transistors per pixel:                  | 37 incl. photogate and cap.    |

| ADC architecture:                       | Pixel-level 8-bit single-slope |

| ADC typical range and conversion time:  | 1 V, ~25 μs                    |

| ADC integral non-linearity:             | 0.22% (0.56 LSB)               |

| Dark current:                           | 130 mV/s; 10 nA/cm2            |

| Conversion gain:                        | 13.1 µV/e-                     |

| Sensitivity:                            | 0.107 V/lux.s                  |

| FPN, rms in dark with CDS, 1K fps:      | 0.027% (0.069 LSB)             |

| Temporal noise, rms, dark, CDS, 1K fps: | 0.15% (0.38 LSB)               |

Figure 6.1.4: DPS specifications and performance.

Figure 6.1.5: Sample image at 1,000 fps.

Figure 6.1.6: Video sequence at 10,000 fps, every 10th frame.

Figure 6.1.7: DPS die photograph.