## This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# A 100-Channel 1-mW Implantable Neural Recording IC

Zou, Xiaodan; Liu, Lei; Cheong, Jia Hao; Yao, Lei; Li, Peng; Cheng, Ming-Yuan; Goh, Wang Ling; Rajkumar, Ramamoorthy; Dawe, Gavin Stewart; Cheng, Kuang-Wei; Je, Minkyu

2013

Zou, X., Liu, L., Cheong, J. H., Yao, L., Li, P., Cheng, M.-Y., et al. (2013). A 100-Channel 1-mW Implantable Neural Recording IC. IEEE Transactions on Circuits and Systems I: Regular Papers, 60(10), 2584-2596.

https://hdl.handle.net/10356/81707

https://doi.org/10.1109/TCSI.2013.2249175

© 2013 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. The published version is available at: [doi:http://dx.doi.org/10.1109/TCSI.2013.2249175].

Downloaded on 26 Aug 2022 02:46:00 SGT

### A 100-Channel 1-mW Implantable Neural Recording IC

Xiaodan Zou, Lei Liu, Jia Hao Cheong, *Member, IEEE*, Lei Yao, *Member, IEEE*, Peng Li, Ming-Yuan Cheng, Wang Ling Goh, *Senior Member, IEEE*, Ramamoorthy Rajkumar, Gavin Stewart Dawe, Kuang-Wei Cheng, *Member, IEEE*, and Minkyu Je, *Senior Member, IEEE*

Abstract—This paper presents a fully implantable 100-channel neural interface IC for neural activity monitoring. It contains 100-channel analog recording front-ends, 10 multiplexing successive approximation register ADCs, digital control modules and power management circuits. A dual sample-and-hold architecture is proposed, which extends the sampling time of the ADC and reduces the average power per channel by more than 50% compared to the conventional multiplexing neural recording system. A neural amplifier (NA) with current-reuse technique and weak inversion operation is demonstrated, consuming 800 nA under 1-V supply while achieving an input-referred noise of 4.0 μV<sub>rms</sub> in a 8-kHz bandwidth and a NEF of 1.9 for the whole analog recording chain. The measured frequency response of the analog front-end has a high-pass cutoff frequency from sub-1 Hz to 248 Hz and a low-pass cutoff frequency from 432 Hz to 5.1 kHz, which can be configured to record neural spikes and local field potentials simultaneously or separately. The whole system was fabricated in a 0.18-µm standard CMOS process and operates under 1 V for analog blocks and ADC, and 1.8 V for digital modules. The number of active recording channels is programmable and the digital output data rate changes accordingly, leading to high system power efficiency. The overall 100-channel interface IC consumes 1.16-mW total power, making it the optimum solution for multi-channel neural recording systems.

Index Terms—Multi-channel neural recording system, biomedical application, high power efficiency, power and area trade-off, dual S/H, low-noise neural amplifier, current reuse, NEF, SAR ADC, capacitor-less LDO

#### I. INTRODUCTION

Simultaneous recording of neuropotentials from the brain over a large number of electrodes provides an effective

Manuscript received September 28, 2012. This work was supported by the Science and Engineering Research Council of A\*STAR (Agency for Science, Technology and Research), Singapore, under SERC grant number: 1021710162.

X. Zou and K.-W. Cheng were with the Institute of Microelectronics, A\*STAR (Agency for Science, Technology and Research), Singapore. X. Zou is now with Qualcomm CDMA Technologies Asia-Pacific Pte. Ltd. (e-mail: xiaodanzou@gmail.com). K.-W. Cheng is now with the National Cheng Kung University, Taiwan.

L. Liu, J. H. Cheong, L. Yao, P. Li, M.-Y. Cheng, and M. Je are with the Institute of Microelectronics, A\*STAR (Agency for Science, Technology and Research), Singapore. (jemk@ime.a-star.edu.sg). L. Liu is also with the Nanyang Technological University, Singapore. M. Je is also with the National University of Singapore, Singapore.

W. L. Goh is with the Nanyang Technological University, Singapore.

R. Rajkumar and G. S. Dawe are with the Department of Pharmacology, Yong Loo Lin School of Medicine, National University Health System; Neurobiology and Ageing Programme, Life Sciences Institute, National University of Singapore; SINAPSE, Singapore Institute for Neurotechnology, Singapore.

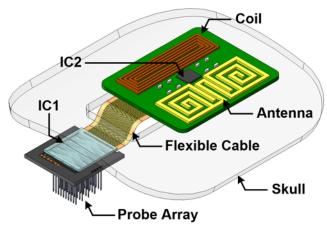

Fig. 1. Fully implantable wireless neural recording microsystem (not drawn to scale).

way for neuroscientists and clinicians to study the brain state dynamics and understand the nature of neurophysiological behaviors. It has a wide range of applications, where the most exciting one currently is the development of brain-controlled neural prostheses. Recent clinical trials with paralyzed human volunteers have shown that it is possible to restore limb movement by such neuroprosthetic devices [1]-[3]. This calls for the development of an ultra-low-power implantable neural recording microsystem, like the one shown in Fig. 1. It consists of a 10×10 neural probe array, a multi-channel neural recording interface IC (IC1), a wireless power and data link IC (IC2), and a flexible cable to exchange recorded data, extracted DC power, and digital control and clock signals between IC1 and IC2. In this paper, the system and circuit design of the IC1 is presented.

Effective and reliable neurological researches and diagnoses rely on multi-channel recordings from a large population of neurons. High-density recording systems with 100 channels to as many as 256 channels have been recently reported [4]–[7]. Since any amount of excessive heat dissipation by the recording microsystem induces damage to the surrounding tissue when it is implanted in the brain, the power consumption of the high-density recording electronics should be strictly restrained. In addition, implantable devices are usually powered through wireless power transfer links to obviate the need of large-capacity batteries or skin-piercing wires. The specific absorption rate of living tissue sets a stringent limit on power budget of the implant. Meanwhile, chip area is also an important constraint for implantable

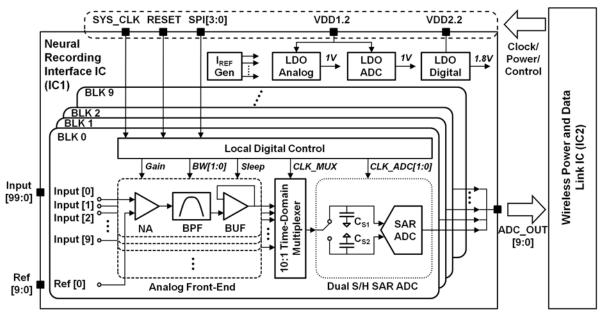

Fig. 2. System architecture of the neural interface IC.

devices to minimize surgical damage. The simultaneous requirements of low power consumption, minimum chip area, and a large number of recording sites impose a critical challenge to IC designers.

A conventional multi-channel neural recording interface IC requires signal conditioning and digitization blocks, which are usually realized by low-noise preamplifiers and ADCs. A successive approximation register (SAR) ADC is widely adopted in biomedical recording systems due to its high energy efficiency, while providing moderate resolution and conversion speed. Due to chip area restraint, one ADC is usually shared among multiple recording channels by employing a time-domain multiplexer [7]-[9]. Recently reported sensor interface ICs have put much effort into reducing the power consumption of individual functional blocks, such as the low-noise neural amplifier and the ADC, which can be realized with the power consumption of a few μW [7], [10]. However, little has been done in optimizing the overall system architecture to minimize the total system power. For example, a buffer preceding the ADC can draw tens of µW due to the shortened sampling time of the ADC in the conventional multi-channel system architecture, which simply overrides the consumption by the preamplifier and ADC and results in a high consumption of the total system power [7]. In [11], a design methodology for the optimized multi-channel neural recording IC was proposed to provide a systematic way to determine key system-level design parameters. It helps designers to achieve the minimum powerarea product for the entire IC within the limit of the conventional architecture.

Some reported designs adopt data compression algorithm to reduce the transmitted data rate to minimize the power consumption [6]. However, this approach may lose some useful information and lead to inaccurate outcome. The complete raw recording data is preferred for the following

neural activity processing and analysis. An alternative solution to reduce the system power is implementing one ADC for each analog recording channel [12]. By doing so, the sampling time of the ADC is greatly extended and the power consumption of the system is minimized. However, this approach will significantly increase the total chip area due to the large area occupied by a large number of SAR ADCs.

In this paper, we present a 100-channel power- and areaefficient neural interface IC for a fully implantable wireless neural recording microsystem. The IC contains 10 recording blocks and power management circuits. Each of the 10 recording blocks consists of 10 analog recording chains, one SAR ADC and one digital control module. A power- and areaefficient multi-channel system structure is proposed with dual sample-and-hold (S/H) circuits, leading to more than 10 times of power saving in the ADC buffer compared to that in the conventional multi-channel recording system. Meanwhile, the increment of the chip area is kept to a minimum. The neural amplifier employs current-reuse technique, achieving an inputreferred noise of 4.0 µV<sub>rms</sub> in 8-kHz bandwidth and a Noise Efficiency Factor (NEF) of 1.9. A 9-bit ADC with one redundant bit is implemented for every 10 analog recording chains. Three low-dropout regulators (LDOs) are integrated to provide separate regulated DC supplies to the analog recording chains, ADCs and digital control blocks. The overall system was fabricated using 0.18-µm standard CMOS process and consumes 1.16-mW total power.

The paper is organized as follows. Section II describes the system architecture of the multi-channel neural interface IC. The detailed circuit designs of the analog recording chains, ADCs and LDOs are presented in Sections III, IV and V, respectively. Section VI reports the measurement results and Section VII concludes the paper.

#### II. SYSTEM ARCHITECTURE

Fig. 2 shows the overall system architecture of the 100channel neural interface IC. There are 10 neural recording blocks for conditioning and digitizing the captured neural signals. Each recording block contains 10 analog recording chains. After multiplexed by a time-domain multiplexer, the conditioned analog signals are then digitized by the following 9-bit SAR ADC. A digital control unit in each recording block provides all the clock sequences and control signals. Note that the overall configuration and timing control is managed by the central digital controller residing in the IC2. The local control unit in each recording block of the IC1 communicates with the central controller through the serial peripheral interface (SPI). LDOs and a current reference generator provide stable DC power and necessary current biases to the whole neural interface IC. The DC supply voltages of 1.2 V and 2.2 V are extracted from wireless RF power in IC2 and sent to IC1 via the flexible cable, as illustrated in Fig. 1. Two LDOs (LDO Analog and LDO ADC in Fig. 2) generate 1-V regulated DC voltage from the 1.2-V supply, and the other LDO (LDO Digital) provides 1.8-V voltage from the 2.2-V DC input.

As shown in Fig. 2, each analog recording channel consists of a low-noise neural amplifier, a BPF, and a unity-gain buffer. Usually, the bandwidth of the biomedical recording system is defined by the 3-dB cutoff frequency  $f_{3dB}$  of the low-noise preamplifier according to the equation,

$$f_{3dB} = \frac{g_m}{C_C \cdot A_V} \tag{1}$$

where  $g_m$  is the transconductance,  $C_C$  is the compensation capacitor, and  $A_V$  is the mid-band gain of the neural amplifier. Low input referred noise requires a large  $g_m$ , leading to a large  $C_C$  of tens of pF, and consequently a large chip area [13]. In order to solve this problem, the system bandwidth in this design is determined by the second stage BPF, where its input-referred noise is not critical and hence its  $g_m$  can be set much smaller than that of the preamplifier. By doing so, a smaller  $C_C$  of a few pF is enough to meet the system bandwidth requirement [14].

Local field potentials (LFPs) and neural spikes are two types of neuropotential signals that are commonly studied to understand cortical activities. The LFPs have relatively large amplitudes of 100  $\mu V_{pp}$  to 1  $mV_{pp}$  and occupy a low frequency range from sub-1 Hz to about 100 Hz. For the neural spikes, they are usually observed with amplitudes of tens or hundreds of μV<sub>pp</sub> and frequencies ranging from 300 Hz to 5 kHz. A versatile recording system should be able to record either the LPFs or neural spikes seperately, or both simutaneouly. In the proposed system, both high-pass and low-pass cutoff frequencies of the BPF can be programmed to support different recording modes. In order to enhance the system dynamic range, a programmable gain function should be implemented. One method to adjust the system gain is changing the feedback capacitance of the BPF. However, this approach also changes the BPF bandwidth and hence the system bandwidth accordingly. In this design, the system gain is controlled by the neural amplifier, as its bandwidth variation

will not affect the system performance because its bandwith is much larger than the system bandwidth. Since the BPF bandwidth is set to match the neural signal frequency, an dedicated buffer is implemented to drive the multiplexer and the sample-and-hold (S/H) circuit of the ADC. By partitioning the different functions of system gain adjustment, bandwith control, and ADC drive as described, the design focus for each individual block is explicit and design requirements become relaxed. This effectivly helps to achieve optimal system performance and power consumption.

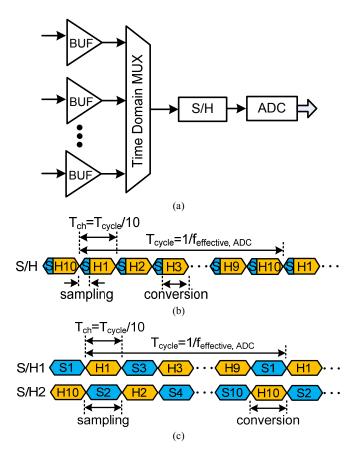

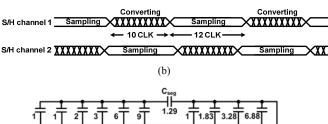

Most of the recently reported works have focused on the power optimization of individual circuit blocks, such as the neural preamplifier and ADC, which are implemented with the power consumption of sub-µW to a few µW. However, without a carefully designed system architecture, some auxiliary circuits may easily draw excessive current and override the low consumption of key building blocks, resulting in high total power consumption. In conventional multichannel biomedical recording system, the ADC is usually shared by multiple analog recording channels to save chip area, as illustrated in Fig. 3(a). A typical timing diagram of one S/H circuit shared by 10 channels is shown in Fig. 3(b). According to Nyquist criterion, the effective sampling rate of the ADC for each channel needs to be at least 2fsignal, where  $f_{signal}$  is the maximum frequency of the input neural signal. As a result, the time period for ADC to finish digitization of one analog channel is  $T_{ch} = 1 / (2f_{signal} \times 10)$ . Taking a 9-bit ADC for example, the sampling time of the traditional SAR ADC is  $T_{ch}/10$ , which is only 1 µs for 5-kHz input signal. This sampling time will decrease further if higher oversampling ratio or higher-resolution ADC is needed. As a result, large driving capability is required for the preceding buffer. As reported in [7] with the conventional multiplexing structure, the buffer draws 20.3-µA current while the preamplifier consumes only 2 µA. It is obvious that the buffer is a dominant power consumer in the system and more effort is needed to minimize the buffer current. One approach to extend the sampling time and reduce the system power is employing one dedicated ADC for each channel [12]. However, this will result in large chip area, which is not desirable for implantable high-density recording devices.

In order to achieve low power and small chip area, a dual S/H scheme for multi-channel system is proposed, as illustrated in Fig. 2. There are two S/H circuits connected to each ADC, and they work in an alternate manner. That is, when one S/H is holding the output of one recording channel for conversion, the other S/H is sampling the output of the next channel. By adopting the dual S/H architecture, the sampling time of the ADC is extended from  $T_{ch}/10$  to  $T_{ch}$ , as the S/H actions are conducted in parallel mode instead of serial mode in the conventional multi-channel system. The timing diagram of the proposed dual S/H ADC is shown in Fig. 3(c). Compared to Fig. 3(b), the extension of the sampling period of the proposed structure is clearly demonstrated. As the power consumption of the buffer dominates in the conventional multi-channel system with single S/H, the system power reduction with the dual S/H approach is

Fig. 3. (a) Conventional multi-channel recording system with a shared ADC. (b) S/H timing diagram of the conventional system. (c) Timing diagram of the proposed dual S/H system architecture.

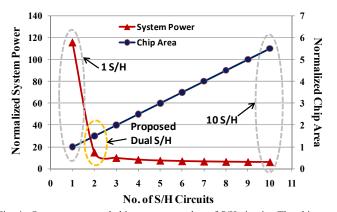

Fig. 4. System power and chip area vs. number of S/H circuits. The chip area is normalized to the system area with a single S/H circuit. The system power is normalized to the ADC buffer power consumption in the dual S/H system.

prominent. Using the proposed system architecture, a buffer with 1.2- $\mu A$  current fulfills the sampling time requirement, leading to a less than 5  $\mu W$  average power for each channel including the ADC.

To further demonstrate the high power and area efficiency of the proposed architecture, we estimate the system power and chip area when one ADC is shared by 10-channel, with varying number of S/H circuits, and plot the results in Fig. 4. It shows that chip area increment is linear with the number of S/H circuits. However, the system power is strongly nonlinear.

When the number of S/H circuits increases from 1 to 2, the system power decreases dramatically. Fig. 4 clearly emphasizes the optimal power-area trade-off of the proposed dual S/H structure.

Besides the full-throughput operation mode with all the 100-recording channels turned on, the neural interface IC can be also configured with 10, 20 or 50 active channels, while the rest are in sleep mode. One way to realize the partialthroughput operation mode is to select 1, 2 or 5 ADCs working in full load. However, this will limit the selection flexibility of the recording sites, as turning off one ADC means all the data from the 10 analog channels attached to it will be lost. In this design, the 10 ADCs are always activated and the partial-throughput operation mode is achieved by varying the number of active analog recording chains attached to the ADC. Since the ADC supports a smaller number of analog channels, the clock frequency of the ADC is reduced accordingly. This results in better performance and lower power consumption of the ADCs as they now operate at much lower frequency compared to the full-load mode. Note that the sampling frequency for each analog channel is kept constant despite the change of the ADC clock frequency. For the partial-throughput operation mode, any 1, 2 or 5 channels can be selected freely from the 10 channels attached to the ADC, while the other unselected channels stay in sleep mode and consume about 0.5 µW per channel.

#### III. ANALOG RECORDING CHAINS

#### A. Low-Noise Neural Amplifier

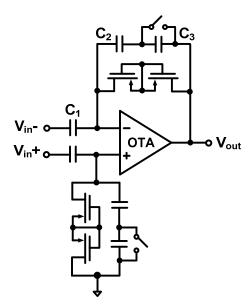

The neural amplifier is one of the most critical components in the neural recording system, and its schematic is shown in Fig. 5. A capacitive feedback topology with pseudo-resistors is chosen to achieve low power and low noise. The gain of the amplifier can be set at 34 dB and 40 dB by the switch associated with  $C_3$  ( $C_1$ =20 pF,  $C_2$ = $C_3$ =400 fF). Since the low-pass cutoff frequency of the system is determined by the second-stage BPF, the bandwidth of the neural amplifier is set to be slightly larger than the signal bandwidth.

The design of the OTA in the neural amplifier is of particular importance, where power consumption and inputreferred noise are the two most important factors. The NEF is introduced to measure the trade-off between these two factors, and defined by the following equation [15],

$$NEF = V_{rms,in} \sqrt{\frac{2 \cdot I_{tot}}{\pi \cdot U_T \cdot 4kT \cdot BW}}$$

(2)

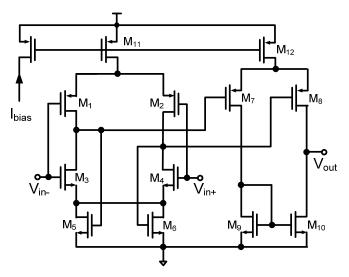

where  $V_{rms,in}$  is the root-mean-square (RMS) value of the inputreferred noise,  $I_{tot}$  is the total supply current of the amplifier,  $U_T$  is the thermal voltage, k is the Boltzman constant, T is the absolute temperature, and BW is the amplifier bandwidth in hertz. The lower NEF means the better power-noise trade-off. To achieve a good noise performance with limited power budget, current-reuse technique is an attractive choice, where both NMOS and PMOS transistors are stacked in the same current branch to obtain double  $g_m$  [16], as shown in Fig. 6.

Fig. 5. Schematic of the low-noise neural amplifier.

Fig. 6. Schematic of the low-noise OTA used in the neural amplifier.

Meanwhile, a subthreshold operation provides high  $g_m$  efficiency, and has been widely adopted in biomedical recording systems.

Using the EKV model [17] which is valid in all operation regions, the  $g_m$  of a MOS transistor in deep subthreshold region is approximated as

$$g_m \cong \frac{I_D}{nU_T} \tag{3}$$

where n is the slope factor with a typical value of 1.5 and  $I_D$  is the drain current. The current noise power spectral density of MOSFETs operating in subthreshold region [18] is modeled as

$$\overline{i_n^2} = 4kT\gamma g_m = 4kT\gamma \frac{I_D}{nU_T}.$$

(4)

$\gamma$  is the thermal noise coefficient, which is 2/3 for transistor in strong inversion region and 1/2 in weak inversion region. The input-referred voltage noise of an ideal differential pair in subthreshold region without current-reuse technique can be

derived as

$$\overline{v_{ni,no-reuse}^2} = \frac{2\overline{i_{ni}^2}}{(g_m)^2} = 8kT\gamma \frac{nU_T}{I_D}.$$

(5)

When the current-reuse technique is applied, assuming that all the four input transistors have the same  $g_m$  value and all the other conditions remain the same, the input-referred noise becomes

$$\overline{v_{ni,reuse}^2} = \frac{4\overline{i_{ni}^2}}{(2g_m)^2} = 4kT\gamma \frac{nU_T}{I_D}.$$

(6)

It shows that the input-referred noise power is reduced by half when the current-reuse scheme is applied, compared to the circuit without it.

In this design, a fully differential current-reuse OTA is employed as shown in Fig. 6. The current-reuse technique is employed at the input stage to achieve required noise performance with minimum current. The four input transistors are biased in weak inversion region to maximize  $g_m/I_d$  and further enhance the current efficiency. Large gate areas ( $W/L = 300 \, \mu \text{m}/2 \, \mu \text{m}$  for NMOS and 200  $\, \mu \text{m}/1 \, \mu \text{m}$  for PMOS) are chosen to suppress the 1/f noise.  $M_5$  and  $M_6$  provide a common-mode feedback and fix the output DC level of the first stage. In the second stage, PMOS transistors are chosen as the input pair to reduce the 1/f noise. The input-referred thermal noise of this OTA is given by

$$\overline{v_{n,thermal}^{2}} \approx 2 \times \frac{4kT}{(g_{m1,2} + g_{m3,4})} \times \left[ \gamma_{wi} + \frac{\gamma_{si}g_{m5,6} + \gamma_{wi}g_{m7,8}}{g_{m1,2} + g_{m3,4}} + \frac{\gamma_{wi}g_{m9,10}^{2}}{(g_{m1,2} + g_{m3,4})g_{m7,8}} \right] \times \Delta f$$

(7)

where  $\Delta f$  is the bandwidth of the amplifier. It is clear that the large  $g_{m1,2}+g_{m3,4}$  will minimize the noise contributions from M<sub>5</sub>–M<sub>10</sub>. Hence, 80% of the total amplifier current is allocated to the input stage. M<sub>1</sub>–M<sub>4</sub> and M<sub>7</sub>–M<sub>8</sub> are biased in weak inversion region to maximize the  $g_m$  efficiency, while M<sub>5</sub>, M<sub>6</sub>, M<sub>9</sub> and M<sub>10</sub> are biased in strong inversion region to minimize their thermal noise contribution.

When the neural amplifier is in sleep mode, its quiescent current is reduced from 800 nA to 160 nA. This non-zero sleep current maintains the DC level at each node of the OTA near the normal operation voltage and helps to achieve fast recovery when the amplifier is activated. In addition, the neural amplifier operating in the sleep mode has a minimum bandwidth of 300 Hz, which can be also used for LFP signal recording.

#### B. Band-Pass Filter and Unity-Gain Buffer

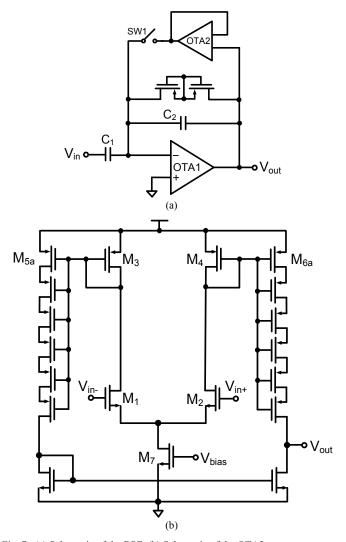

As discussed in Section II, the BPF determines the system bandwidth. At the same time, it provides an additional gain of 10 to enhance the system dynamic range. Fig. 7(a) shows the schematic of the BPF, which has the AC-coupled input and closed-loop configuration. Both low-pass and high-pass cutoff frequencies of the BPF are programmable. The low-pass cutoff frequency is determined by the 3-dB roll-off frequency

Fig. 7. (a) Schematic of the BPF. (b) Schematic of the OTA2.

Fig. 8. Schematic of the OTA used in the unity gain buffer.

of the OTA1, and is programmed by the DC bias current of OTA1. The low-pass cutoff frequency can be set at 300 Hz for LFP recording or at 5 kHz to include the neural spikes within the system bandwidth.

The desired high-pass cutoff frequencies for the BPF are sub-1 Hz and 300 Hz to fit the recording bandwidth of LPF and neural spikes respectively. While it is easy to achieve an ultra-low high-pass cut-off frequency by employing the widely

used pseudo-resistors, it is difficult to obtain well controlled 300-Hz cut-off frequency as the resistance generated by the pseudo-resistor is highly susceptible to process variations. In order to solve this problem, an ultra-small- $g_m$  OTA is implemented in the feedback path of the BPF [19] as shown in Fig. 7(a). The OTA2 is connected in unity-gain configuration and designed with very narrow unity-gain bandwidth, such that the signal within the bandwidth of the OTA2 is fed back to the negative input node of the OTA1 and eventually rejected by the BPF. The bandwidth of the OTA2 is determined by its quiescent current, and can be controlled with much higher accuracy than the resistance of the pseudo-resistors. When the switch in series with the OTA2 is disconnected, the high-pass cutoff frequency of the BPF is set to sub-1Hz, which is determined by the pseudo-resistors.

The schematic of the OTA2 is shown in Fig. 7(b). A series-parallel current division structure is used to achieve ultra-low  $g_m$  [20]. The DC current in  $M_7$  is about 2 nA and the W/L ratio of  $M_3$  and  $M_4$  is 7 times of the W/L ratio of  $M_{5a}$  and  $M_{6a}$ , and the 6 serially connected PMOS transistors have all identical sizes. This results in a current of about 30 pA in the right and left branches. By using this ultra-low- $g_m$  OTA2, the BPF is designed to have a simulated high-pass cutoff frequency at 300 Hz.

Following the BPF is a unity-gain buffer and its OTA schematic is shown in Fig. 8. Both NMOS and PMOS transistors are adopted for the input pair to achieve rail-to-rail input swing. A class-AB output stage [21] is implemented by using a pseudo-resistor  $M_R$  and a capacitor  $C_1$ . This output topology achieves very large slew rate with small DC current, as the charging or discharging current to the load is not limited by the quiescent current of the output stage. By using the proposed OTA for the unity-gain buffer, combined with the dual S/H structure, only  $1.2\text{-}\mu\text{A}$  current is sufficient to fulfill the settling time requirement of the ADC. When the recording chain is put into sleep mode, the unity-gain buffer is fully turned off to conserve power.

#### IV. SAR ADC DESIGN

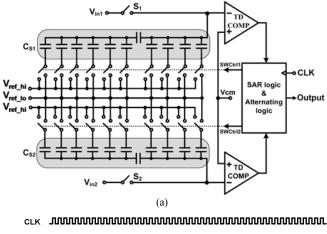

The architecture of the 9-bit alternating SAR ADC is shown in Fig. 9 (a). The ADC mainly consists of four building blocks: a time domain (TD) comparator, a capacitor array, a switch array, and a logic circuit. This 9-bit alternating ADC digitizes ten analog input signals and generates one serial digital output. Based on the proposed dual S/H structure, two S/H channels are implemented. It is achieved using two sets of sampling switches, TD comparators, and capacitor arrays. Only one set of SAR logic is implemented. The ADC first samples the input  $V_{in1}$  from the channel 1 through the switch  $S_1$  onto the capacitor array  $C_{S1}$  while the channel 2 capacitor array  $C_{S2}$  undergoes the bit conversion of  $V_{in2}$ . During the next cycle, the channel 1 will enter the conversion phase and the channel 2 will go into sampling of the next analog input channel according to the timing diagram in Fig. 9(b).

A non-binary redundant algorithm is utilized in the SAR ADC design to improve the accuracy and noise rejection

Fig. 9. (a) Architecture of the 9-bit alternating SAR ADC. (b) Timing diagram of the alternating SAR ADC. (c) Architecture of the segmented capacitor array.

Fig. 10. Schematic of the output-capacitor-less LDO with high-loop-gain current-mode feedback.

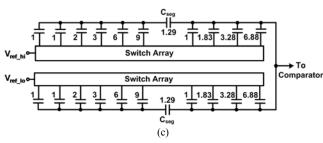

performance [22], [23]. One redundant bit is introduced in this design. The capacitors in the array are sized based on the optimum non-binary redundant bit weights obtained through extensive simulation [24]. To reduce the total size of capacitors, the segmented capacitor array is introduced. The unit capacitance used is 0.24 pF occupying the area of 12  $\mu$ m by 12  $\mu$ m when implemented by the MIM capacitor. This value was determined considering the noise requirement as well as the parasitic capacitance effect. A time-domain comparator reported in [25] is used to further reduce the power consumption. The reference voltages  $V_{ref\_hi}$  and  $V_{ref\_lo}$  are generated from the 1-V supply using a resistive voltage divider and buffered using a self-regulated voltage reference

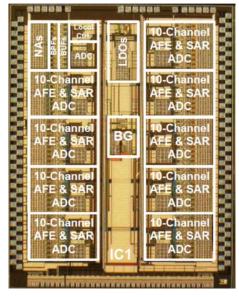

Fig. 11. Die micrograph of the neural interface IC.

buffer [26].

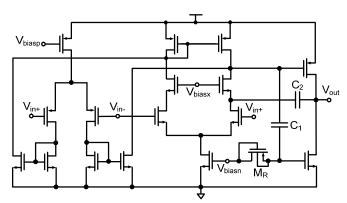

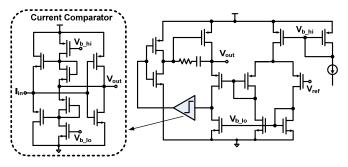

#### V. POWER MANAGEMENT

The overall system power is provided by the IC2 via flexible cable, as described in Section I. The rectifiers in IC2 output two levels of DC voltage, which are then regulated by the low-power capacitor-less LDOs in the IC1. As shown in Fig. 10, the LDO has two gain stages in its current feedback loop to increase the loop gain which stabilizes the LDO under low-output-power condition, and non-linear circuits are used to reduce the power consumption. A flipped voltage follower (FVF) structure is utilized to achieve low output impedance and hence loop stability without the need of an off-chip capacitor [27]. However, such a structure has limitation in its loop gain which in turn limits the load regulation performance of the LDO and stability when the load current is very small (e.g.  $< 50 \mu A$ ). In order to improve the loop gain, a two-stage current-mode feedback loop is introduced. The output voltage variation is converted to current by the FVF and compared with a current reference using a current comparator [28]. The output of the current comparator controls the switching of a thick-gate charge pump to charge/discharge the gate voltage of the output driver MOSFET. The two-stage current-mode feedback improves the loop gain of the LDO to 50 dB.

The current comparator [29] utilizes a source follower as the input stage and a CMOS inverter as the positive feedback to have lower input resistance and short response time. However, there exists a deadband region in which the two input transistors are both turned off and the input resistance is high. In this LDO, the current comparator utilizes the structure in [28] which solves this problem by biasing the input transistors to be always on.

As the input impedance of the current comparator is low, it does not introduce additional low-frequency poles to the circuit. As a result, the LDO remains stable without an off-chip capacitor even at no load current. Since the LDO consists

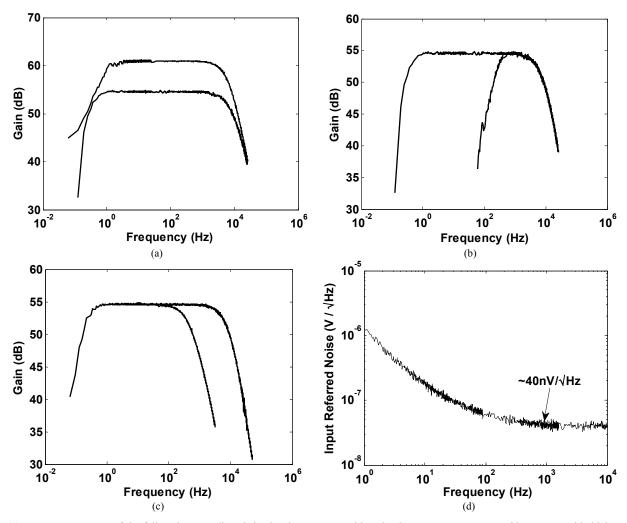

Fig. 12. (a) Frequency response of the full analog recording chain showing programmable gain. (b) Frequency response with programmable high-pass cutoff frequency. (c) Frequency response with programmable low-pass cutoff frequency. (d) Input-referred noise of the full analog recording chain.

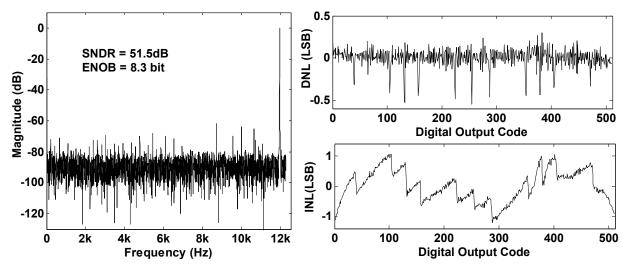

Fig. 13. Measured ADC performance. Output spectrum (SNDR and ENOB) and nonlinearity (DNL and INL).

of non-linear circuit blocks such as the current comparator and charge pump, it consumes very low power and achieves high power efficiency even under low-load condition.

#### VI. MEASUREMENT RESULTS

The 100-channel neural recording interface IC has been fabricated using a standard 0.18-µm CMOS process and the

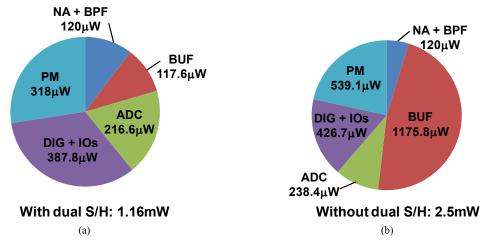

Fig. 14. Power breakdown of the overall neural interface IC with and without dual S/H scheme.

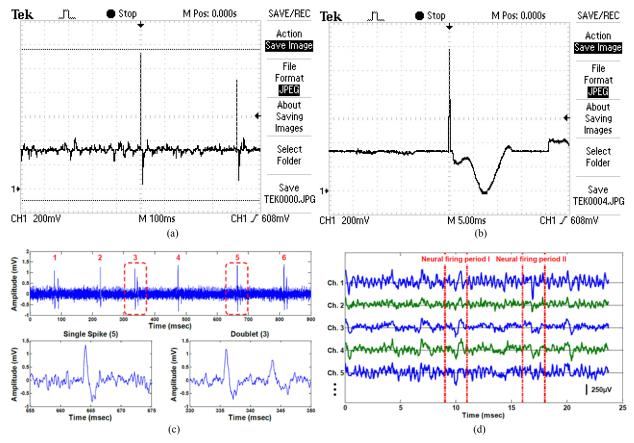

Fig. 15. in vivo testing results of the overall interface IC. (a) Stimulation artifacts and their responses. (b) Zoomed-in stimulation artifact and neural response. (c) Spontaneous neural signal acquisition with a glass electrode from an anesthetized rat. (d) Multi-channel neural signal recording with a NeuroNexus electrode from a freely behaving rat.

die micrograph is shown in Fig. 11. The dimension of the fabricated IC is 4.7 mm by 6 mm, including pads. The system is tested under 1 V for the analog channels and ADC, and 1.8 V for the digital control module. The measurement results of the overall neural interface IC are described in detail in the following sections.

#### A. Analog Recording Chains

The mid-band gain of the system can be set at either 54.6 dB or 60.6 dB as plotted in Fig. 12(a). The measured high-pass cutoff frequency is 0.38 Hz if only the pseudo-resistor presents in the feedback path of the BPF, and it can be altered to 248 Hz when OTA2 is connected. By programming the high-pass cutoff frequency, the LFP signal can be either recorded or removed. The low-pass cutoff frequency of the

|                          | Harrison<br>[5]   | Chae<br>[7] | Lee<br>[32]          | Rabaey<br>[30] | Walker<br>[33] | Chang<br>[34] | This work                                       |

|--------------------------|-------------------|-------------|----------------------|----------------|----------------|---------------|-------------------------------------------------|

| Supply voltage (V)       | 3.3               | ±1.65       | ±1.5                 | 0.5            | 1.2            | 0.5 / 1       | 1 / 1.8                                         |

| Process                  | 0.5 μm            | 0.35 μm     | 0.5 μm               | 65 nm          | 0.13 μm        | 0.25 μm       | 0.18 μm                                         |

| System gain (dB)         | 60                | 57 – 60     | 67.8 / 78            | -              | 40 / 55        | 37.5 – 57.5   | 54.8 / 60.9                                     |

| High-pass<br>cutoff (Hz) | 30 – 1k           | 0.1 - 200   | 0.1 – 1k             | DC / 300       | 0.3            | 0.5 (tunable) | 0.38 / 248                                      |

| Low-pass<br>cutoff (Hz)  | 5k                | 2k – 20k    | 8k                   | 300 / 10k      | 10k            | 18k (tunable) | 432 / 5.1k                                      |

| Noise (μV)               | 5.1               | 4.9         | 4.32                 | 4.9            | 2.2            | 4.26 / 5.62   | 4.0 (whole chain)                               |

| NEF                      | -                 | -           |                      | 5.99           | 5              | 5.2 / 1.69*   | 1.9 (whole chain)                               |

| NEF <sup>2</sup> VDD     | -                 | -           |                      | 17.96          | 30             | 27 / 2.86*    | 3.6 (whole chain)                               |

| THD                      | -                 | -           |                      | -              |                |               | 1% @ 0.9-V output                               |

| CMRR (dB)                |                   | 90          | 134                  | 75             |                | 35            | > 60                                            |

| PSRR (dB)                |                   | 80          | 62.7                 | 64             |                | 48            | > 70                                            |

| Sampling rate (kS/s)     | 15                | 640         | 58 – 709             | 20             | 31.25          | 31.25         | 24.5 – 245                                      |

| SNDR (dB)                | -                 | -           |                      | -              | 60.3           | 45.14         | 51.5                                            |

| No. of bits              | 10                | 6 – 9       |                      | 8              | 10             |               | 9.5                                             |

| ENOB                     |                   |             | 8.3                  | 7.15           |                | 7.2           | 8.3                                             |

| INL/DNL                  | 0.6 / 0.6         |             |                      |                |                | 0.75 / 0.5    | 1.2 / 0.55                                      |

| No. of channels          | 100               | 128         | 32                   | 1              | 96             | 16            | 100                                             |

| Total power (mW)         | 4.3<br>(one ADC)  | 3           | 1.2 (without<br>ADC) | 0.005          | 6.5            | 0.2           | 1.16 (including loss<br>in power<br>management) |

| Chip area (mm²)          | 27.7<br>(one ADC) | 51.8        | 16.2                 | 0.013          | 25             | 2.88          | 28.2                                            |

TABLE 1. MEASURED PERFORMANCE SUMMARY AND COMPARISON OF THE PROPOSED NEURAL INTERFACE IC WITH STATE-OF-THE-ART DESIGNS.

system is determined by the  $g_m$  value of the OTA1 in the BPF, and can be set at 432 Hz or 5.1 kHz as shown in Fig. 12(c). As a result, the neural spikes and the LFP can be recorded either separately or simultaneously by choosing different bandwidth configurations.

The input-referred noise spectrum of the overall neural recording channel is depicted in Fig. 12(d). The noise floor is about 40 nV/ $\sqrt{\text{Hz}}$  measured at 1 kHz, and the RMS value of the input-referred noise is 4.0  $\mu V_{rms}$ , when integrated from 1 Hz to 8 kHz. The measured NEF of the whole analog chain is 1.9, which is the lowest to the best of our knowledge. The NEF of the stand-alone neural amplifier will be even lower than this value if the noise from the BFP and the unity-gain buffer is not counted in.

Considering the constantly decreasing operation voltage of the preamplifier, the popular NEF metric has been modified to the following equation [30] [31],

$$NEF^{2} \cdot VDD = V_{rms,in}^{2} \left( \frac{2 \cdot P_{total}}{\pi \cdot kT / q \cdot 4kT \cdot BW} \right)$$

(8)

which is dependent on the power consumption rather than the current. The *NEF*<sup>2</sup>*VDD* of this design is only 3.6, which is much lower or comparable to other state-of-the-art designs, indicating an optimal noise-power trade-off.

#### B. ADC

The measurement results of the SAR ADC are shown in Fig. 13. The input dynamic range of the ADC is from 250 mV to 750 mV. Vref\_lo, Vcm and Vref\_hi (Fig. 9(a)) are set to 250 mV, 500 mV and 750 mV, respectively and the clock

frequency for the ADC is set to 540 kHz. Fig. 13 shows the measured signal-to-noise-and-distortion ratio (SNDR), differential nonlinearity (DNL), and integral nonlinearity (INL) performances of the dual S/H SAR ADC for a 12-kHz sinusoidal input. The ADC achieves 51.5 dB of SNDR which corresponds to 8.3 bits of the effective number of bits (ENOB). The DNL and INL of the ADC are  $\pm 0.55$  LSB and  $\pm 1.2$  LSB, respectively. The total power consumption of the ADC is 8.39  $\mu W$  when it supports two analog recording channels. When all of the 10 analog recording channels are activated, the ADC clock frequency is 2.7 MHz and the ADC total power is 21.66  $\mu W$ .

#### C. System Performance

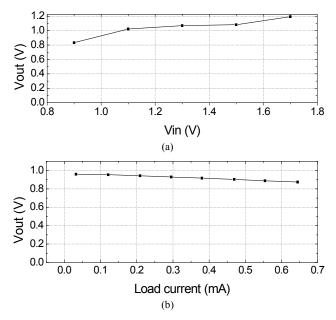

Table I summarizes the performance of the overall 100channel neural interface IC and makes a comparison with other state-of-the-art designs. All the listed numbers for analog modules of this design in Table I are obtained from the output of the unity-gain buffer. The total power consumption of the overall 100-channel interface IC is only 1.16 mW including the loss in the power management module. The system power allocation with dual S/H scheme is displayed in Fig. 14(a). The power management module takes about 30% of the total power with 70% efficiency. Fig. 16 shows the line and load regulation of the LDO. The LDO achieves a line regulation of 3%/V and a load regulation of 0.6 mV/mA. The 100 analog recording chains consume about 20% of the total power, and the ADCs take about 19%. The rest of power is dissipated by the digital modules, including the digital control blocks, digital buffers and I/O pads. On the other hand, if without the

<sup>\*</sup>The numbers are for the preamplifier only, while the numbers in the proposed design are for the whole analog recording chain.

Fig. 16. (a) Line regulation and (b) load regulation measurement results of LDO.

dual S/H structure, the system power can raise up to 2.5 mW as shown in Fig. 14(b), with about 50% of consumption is taken by the unity-gain buffer. This is due to the significantly shortened sampling time of the ADC, which necessitates high driving capability of the buffer. The numbers in Fig. 14(b) are estimated based on theoretical analysis. Compared to the conventional single S/H structure, the proposed dual S/H system architecture reduces the total system power by more than 50% and improves the system power efficiency significantly.

#### D. In vivo testing

To further verify the functionality of the fabricated neural recording system, in vivo neural signal acquisitions have been performed. First, field evoked potential recording was carried out and Fig. 15(a) shows the sample recordings from the medial perforant path-dentate gyrus monosynaptic pathway [35]. Two stimulus artifacts with 400-ms interval and the paired pulse inhibition of the negative waveform (characteristic of the dendritic recording in the aforesaid pathway) were illustrated in Fig. 15(a), and the neural response was observed as shown in the zoomed-in picture, Fig. 15(b). Second, spontaneous neural activities were also captured using a glass electrode from dorsal raphae nucleus (DRN), as shown in Fig. 15(c). The biphasic waveform and occurrence of doublets confirms the recording electrode position in the DRN [36]. The above-mentioned experiments were conducted in unconscious rats. Further, multi-channel neural signals were also recorded successfully from nucleus incertus (NI), in a freely moving rat chronically implanted with a NeuroNexus probe. The acquired neural signals are depicted in Fig. 15(d), where neural spikes from the NI [37] are clearly observed.

#### VII. CONCLUSION

This paper has demonstrated a mili-watt 100-channel neural recording interface IC. A dual S/H system architecture is proposed which extends the sampling time of the ADC by 10 times and effectively reduces the system power by more than 50% compared to the conventional multi-channel neural recording system. A three-stage analog recording chain was implemented, which helps to achieve optimal system performance. The system was designed with programmable gain and bandwidth so that neural spikes and LFP can be recorded simultaneously or separately. The current-reuse technique and weak-inversion operation are employed to achieve high power efficiency for the neural amplifier, resulting in a system NEF of 1.9, which is one of the lowest among state-of-the-art designs. A low-power ADC with a redundant bit was implemented and a capacitor-less LDO was integrated to complete the functionality of the interface IC. in vivo neural signals were successfully acquired using the developed prototype. The optimal system power and small chip area make the developed interface IC especially suitable for fully implantable multi-channel neural recording microsystems [38].

#### REFERENCES

- L. R. Hochberg, M. D. Serruya, G. M. Friehs, et al., "Neuronal Ensemble Control of Prosthetic Devices by a Human with Tetraplegia", *Nature*, vol. 442, pp. 164–171, Jul. 2006.

- [2] A. B. Schwartz, "Cortical Neural Prosthetics", Ann. Rev. Neuroscience, vol. 27, pp. 487–501, Jul. 2004.

- [3] A. B. Schwartz, X. T. Cui, D. J. Weber, and D. W. Moran, "Brain-Controlled Interfaces: Movement Restoration with Neural Prosthetics", Neuron, vol. 52, pp. 205–220, 2006.

- [4] R. Shulyzki, K. Abdelhalim, A. Bagheri, C. Florez, P. Carlen, and R. Genov, "256-site active neural probe and 64-channel responsive cortical stimulator," in *Custom Integrated Circuits Conference (CICC)*, 2011 IEEE, 2011,pp. 1-4.

- [5] R. R. Harrison, P. T. Watkins, R. J. Kier, R. O. Lovejoy, D. J. Black, B. Greger, and F. Solzbacher, "A Low-Power Integrated Circuit for a Wireless 100-Electrode Neural Recording System", *IEEE J. Solid-State Circuits*, vol. 42, pp. 123–133, Jan. 2007.

- [6] A. Bonfanti, M. Ceravolo, G. Zambra, R. Gusmeroli, T. Borghi, A.S. Spinelli, and A.L. Lacaita, "A multi-channel low-power IC for neural spike recording with data compression and narrowband 400-MHz MC-FSK wireless transmission," *IEEE European Solid-State Circuits Conference*, pp.330-333, Sept. 2010.

- [7] M. Chae, W. Liu, Z. Yang, T. Chen, J. Kim, M. Sivaprakasam, and M. Yuce, "A 128-Channel 6 mW Wireless Neural Recording IC with on-the-Fly Spike Sorting and UWB Transmitter", in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2008, pp. 146–147.

- [8] R. H. Olsson, D. L. Buhl, A. M. Sirota, G. Buzsaki, and K. D. Wise, "Band-Tunable and Multiplexed Integrated Circuits for Simultaneous Recording and Stimulation with Microelectrode Arrays", *IEEE Trans. Biomed. Eng.*, vol. 52, pp. 1303–1311, Jul. 2005.

- [9] R. H. Olsson III and K. D. Wise, "A Three-Dimensional Neural Recording Microsystem with Implantable Data Compression Circuitry," *IEEE J. Solid-State Circuits*, vol. 40, pp. 2796–2804, Dec. 2005.

- [10] H. Wu and Y. P. Xu, "A 1V 2.3μW Biomedical Signal Acquisition IC", in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2006, pp. 58–59.

- [11] M. S. Chae, W. Liu, and M. Sivaprakasam, "Design Optimization for Integrated Neural Recording Systems," *IEEE J. Solid-State Circuits*, vol. 43, pp. 1931–1939, Sep. 2008.

- [12] R. M. Walker, H. Gao, P. Nuyujukian, K. Makinwa, K. V. Shenoy, T. meng, and B. Murmann, "A 96-Channel Full Data Rate Direct Neural

- Interface in 0.13µm CMOS," in *Symp. VLSI Circuits Dig. Tech. Papers*, Jun. 2011, pp. 144–145.

- [13] X. Zou, X. Xu, L. Yao, and Y. Lian, "A 1-V 450nW Fully Integrated Programmable Biomedical Sensor Interface Chip," *IEEE J. Solide-State Circuits*, vol. 44, pp. 1067–1077, Apr. 2009.

- [14] X. Zou, W.-S. Liew, L. Yao, and Y. Lian, "A 1V 22µW 32-Channel Implantable EEG Recording IC," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2010. pp. 126–127.

- [15] R. R. Harrison and C. Charles, "Low-Power Low-Noise CMOS Amplifier for Neural Recording Applications," *IEEE J. Solid-State Circuits*, vol. 38, no. 6, pp. 958–965, Jun. 2003.

- [16] L. Liu, X. Zou, W. L. Goh, R. Ramamoorthy, G. Dawe, and M. Je, "800 nW 43 nV/√Hz neural recording amplifier with enhanced noise efficiency factor," *Electronics Lett.*, vol. 48, no. 9, pp. 479–480, Apr. 2012.

- [17] C. C. Enz, F. Krummenacher, and E. A. Vittoz, "An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications," *Analog Integr. Circuits Signal Process.*, vol. 8, pp. 83–114, Jul. 1995.

- [18] B. Gosselin, M. Sawan, and C. A. Chapman, "A Low-Power Integrated Bioamplifier With Active Low-Frequency Suppression," *IEEE Trans. Biomed. Circuits Syst.*, vol.1, no.3, pp.184–192, Sep. 2007.

- [19] R. R. Harrison, G. Santhanam, and K. V. Shenoy, "Local Field Potential Measurement with Low-Power Analog Integrated Circuit," in *Proc. 26th Annu. Int. Conf. IEEE Eng. Med. Biol.*, Sep. 2004, pp. 4067–4070.

- [20] A. Arnaud, R. Fiorell, and C. Galup-Montoro, "Nanowatt, sub-ns OTAs, with sub-10-mV input offset, using series-parallel current mirrors," *IEEE. J. Solid-State Circuits*, vol. 41, no. 9, pp. 2009–2018, Sep. 2006.

- [21] E. Lopez-Morillo, R. G. Carvajal, J. Galan, J. Ramirez-Angulo, A. Lopez-Martin, and E. Rodriguez-Villegas, "A low-voltage lowpower QFG-based sigma-delta modulator for electroencephalogram applications," in *Proc. IEEE Biomed. Circuits Syst. Conf.*, 2006, pp. 571–574.

- [22] M. Hesener, T. Eichler, A. Hanneberg, D. Herbison, F. Kuttner, and H. Wenske, "A 14 b 40 MS/s redundant SAR ADC with 480 MHz clock in 0.13 μm CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2007, pp. 248–600.

- [23] S. M. Chen and R. W. Brodersen, "A 6-bit 600-MS/s 5.3-mW asynchronous ADC in 0.13- μm CMOS," *IEEE J. Solid-State Circuits*, vol. 41,no. 12, pp. 2669–2680, Dec. 2006.

- [24] J. H. Cheong, K. L. Chan, P. B. Khannur, K. T. Tiew, and M. Je, "A 400-nW 19.5-fJ/Conversion-step 8-ENOB 80-kS/s SAR ADC in 0.18µm CMOS," *IEEE Tran. Circuit Syst.II, Exp. Briefs*, vol. 58, no. 7, pp. 407–411, Jul. 2011.

- [25] S.-K. Lee, S.-J. Park, Y. Suh, H. J. Park, and J. Y. Sim, "A 1.3μW 0.6V 8.7-ENOB Successive Approximation ADC in a 0.18μm CMOS," in Symp. VLSI Circuits Dig. Tech. Papers, Jun. 2009, pp. 242–243.

- [26] Z. Cao, S. Yan, and Y. Li, "A 32 mW 1.25 GS/s 6b 2b/Step SAR ADC in 0.13 µm CMOS," *IEEE J. Solid-State Circuits*, vol. 44, no. 3, pp. 862–873, Mar. 2009.

- [27] T. Karnik, B. A. Bradley, C. Parsons, D. Finan, S. Borkar, and P. Hazuch, "Area-efficient linear regulator with ultra-fast load regulation," IEEE J. Solid-State Circuits, vol. 40, pp. 933–940, Apr. 2005.

- [28] A. T. K. Tang and C. Toumazou, "High performance CMOS current comparator," *Electron. Letters*, vol. 30, no. 1, pp. 5-6, 1994.

- [29] H. Traff, "Novel Approach to High Speed CMOS Current Comparators," *Electronics Lett.*, vol. 28, no. 3, pp. 310-312, 1992.

- [30] R. Muller, S. Gambini, and J. M. Rabaey, "A 0.013mm<sup>2</sup> 5μW DC-Coupled Neural Signal Acquisition IC with 0.5V supply," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2011, pp. 302–303.

- [31] R. Muller, S. Gambini, and J. M. Rabaey, "A 0.013mm<sup>2</sup>, 5 μW, DC-Coupled Neural Signal Acquisition IC With 0.5 V Supply," *IEEE Journal of Solid-State Circuits*, vol. 47, no.1, pp. 232–243, Jan. 2012.

- [32] S. B. Lee, H.-M. Lee, M. Kiani, U.-M. Jow, and M. Ghovanloo, "An Inductively Powered Scalable 32-Channel Wireless Neural Recording System-on-a-Chip for Neuroscience Applications," *IEEE J. Solid-State Circuits*, vol. 4, pp. 360–371, Dec. 2010.

- [33] R. M. Walker, H. Gao, P. Nuyujukian, K. Makinwa, K. V. Shenoy, T. Meng, and B. Murmann, "A 96-Channel Full Data Rate Direct Neural Interface in 0.13μm CMOS," in Symp. VLSI Circuits Dig. Tech. Papers, Jun. 2011, pp. 144–145.

- [34] S.-I. Chang, K. AlAshmouny, M. McCormick, Y.-C. Chen, and E. Yoon, "BioBolt: A Minimally-Invasive Neural Interface for Wireless Epidural Recording by Intra-Skin Communication," in *Symp. VLSI Circuits Dig. Tech. Papers*, Jun. 2011, pp. 146–147.

- [35] V. A. Markevich, G. A. Grigoryan, G. S. Dawe, and J. D. Stephenson, "Theta driving both inhibits and potentiates the effects of nicotine on dentate gyrus responses," *Neurosci. Behav. Physiol.*, vol. 37, pp. 403– 409. May 2007.

- [36] M. Hajós, K. A. Allers, K. Jennings, T. Sharp, G. Charette, A. Sík, and B. Kocsis, "Neurochemical identification of stereotypic burst-firing neurons in the rat dorsal raphe nucleus using juxtacellular labelling methods," *Eur. J. Neurosci.*, vol. 25, no. 1, pp. 119–126, Jan. 2007.

- [37] A. Nuñez, A. Cervera-Ferri, F. Olucha-Bordonau, A. Ruiz-Torner, and V. Teruel, "Nucleus incertus contribution to hippocampal theta rhythm generation," *Eur. J. Neurosci.*, vol. 23, no. 10, pp. 2731–2738, May 2006.

- [38] K. Cheng, X. Zou, J. H. Cheong, R.-F. Xue, Z. Chen, L. Yao, H.-K. Cha, S. J. Cheng, P. Li, L. Liu, L. Andia, C. K. Ho, M.-Y. Cheng, Z. Duan, R. Rajkumar, Y. Zheng, W. L. Goh, Y. Guo, G. Dawe, W.-T. Park, and M. Je, "100-Channel Wireless Neural Recording System with 54-Mb/s Data Link and 40%-Efficiency Power Link," in *IEEE Asian Solid State Circuits Conference (A-SSCC) Dig. Tech. Papers*, Nov. 2012, pp. 185–188.

Xiaodan Zou received the B.Eng. and Ph.D. degree in electrical engineering from the National University of Singapore (NUS) in 2005 and 2010, respectively. Since 2010, she has been with the Institute of Microelectronics, Agency for Science, Technology and Research (A\*STAR), Singapore. Her research interest is mainly on low-power, low-noise analog circuit design and system development for biomedical applications. Since 2012, She has been with Qualcomm CDMA Technologies Asia-Pacific Pte. Ltd.

Lei Liu received the B.Eng degree with First Class honor in electrical and electronic engineering from Nanyang Technological University Singapore in 2008. From 2008 to 2009, he worked as product engineer on NAND flash memory characterization in Micron Semiconductor Asia. Since 2009, he has been working towards a Ph.D. degree in IC design in the Nanyang Technological University. His research involves the design and implementation of low-power neural integrated interfaces, focusing mainly in low-noise amplifiers, low-power circuit

techniques, and biotelemetry.

Jia Hao Cheong (M'12) received the B.Eng. and Ph.D. degrees in electrical and electronic engineering from Nanyang Technological University (NTU), Singapore, in 2005 and 2009 respectively. Since 2009 he has been with Institute of Microelectronics (IME), Agency for Science, Technology and Research (A\*STAR), Singapore as a Scientist in the Biomedical IC group. Since he joined IME, he has worked on the development of wireless implantable sensor ASIC for blood flow measurement and for neural signal recording, as well as ultrasound

imaging front-end ASIC. His research interests include biomedical circuit and system, low-power analog & mixed-signal circuit and system and oversampled ultrasound beamforming. He was awarded the Best Student Paper Award in IEEE International Conference on Electron Devices and Solid-state Circuits (EDSSC) 2008.

Lei Yao (S'09–M'10) received the B.S. degree in applied physics from University of Science and Technology of China, Hefei, China, in 2004, the M.Eng. degree in microelectronics and solid-state electronics from Shanghai Institute of Microsystems and Information Technology, Chinese Academy of Sciences, Shanghai, in 2007, and the Ph.D. degree in electrical and computer engineering from McGill University, Montreal, QC, Canada, in 2010. Since 2010 he has been with Institute of Microelectronics (IME), Agency for Science, Technology and

Research (A\*STAR), Singapore as a Scientist in the Biomedical IC group, working on the neural recording and stimulation circuit and system design. His current research interests include analog & mixed-signal integrated circuit and system design for biomedical applications.

Peng Li was born in Linyi, China in 1983. He received the B.Eng. degree in Electronic Information Engineering from South-Central University for Nationalities, China, in 2008 and the M.Sc degree in signal processing from Nanyang Technological University (NTU), Singapore, in 2010. Since 2010, he has been working for Institute of Microelectronics (IME), Agency for Science, Technology and Research (A\*STAR), Singapore as a research engineer in the Biomedical IC group. Since he joined IME, he has worked on digital ASIC design for

neural signal recording system and muscle stimulation system. His research interests include digital communications and digital signal processing.

Ming-Yuan Cheng received the B.S. degree from the National Yunlin University of Science and Technology, Taiwan in 2000, the M.S. degree from National Cheng Kung University, Taiwan in 2002, and the Ph.D. degree from National Taiwan University, Taiwan, in 2009, all in mechanical engineering.

From 2009 to 2010, he was a postdoctoral fellow in National Taiwan University, Taiwan. In 2010, he joined Institute of Microelectronics, A\*STAR, Singapore, where he is currently a scientist and bio-

packaging group leader in miniaturized medical devices department, IME.

His research interests include microelectromechanical system, biopackaging, flexible tactile sensing arrays, sensorized guide wire, microfluidic devices, and miniaturized medical devices.

Wang Ling Goh (SM'09) received the B.Eng. degree in electrical and electronic engineering and Ph.D. degree in microelectronics from Queen's University of Belfast, Belfast, U.K. in 1990 and 1995, respectively. She was a Research Engineer at the Northern Ireland Semiconductor Research Centre while working toward the Ph.D. degree. She joined the school of electrical and electronic engineering, Nanyang Technological University, Singapore, as a Lecturer in 1996, and became an Associate Professor in 2004. Her research interests include digital/mixed-

signal IC design, telemetry circuits, neural recording ICs, and 3-D IC.

Ramamoorthy Rajkumar received a PhD in Neuropharmacology from the Birla Institute of Technology & Science (BITS), Pilani, India, in 2009. Since then, he has been working as a Postdoctoral Fellow in the Department of Pharmacology, National University of Singapore, where he is carrying out preclinical in vivo electrophysiological and behavioural investigations. His foci of research are Neuropsychopharmacology

and Systems Neuroscience. In addition, he has been actively involved in testing of novel acquisition systems developed for rodent electrophysiological studies. He has to his credit many research and review articles in journals of international repute

Gavin Stewart Dawe completed a PhD in Pharmacology at the Institute of Psychiatry, King's College London, University of London, United Kingdom, in 1995. After postdoctoral research at the Institute of Psychiatry he worked in industry with ReNeuron Limited and Eli Lilly and Company before joining the National University of Singapore (NUS), where he is currently an Associate Professor in the Department of Pharmacology, Yong Loo Lin School of Medicine, National University Health

System, a member of the NUS Graduate School for Integrative Sciences and Engineering, and a principal investigator under the Neurobiology and Ageing Programme, Life Sciences Institute, and the Singapore Institute for Neurotechnology (SINAPSE). His laboratory investigates the neuropharmacology of drugs for mental health disorders with systems neurobiology, behavioural neuroscience, electrophysiological and optogenetic approaches. He has won a number of research awards including the National University of Singapore Young Investigator Award 2002 and the GlaxoSmithKline Academic Centre for Excellence Research Award 2010.

**Kuang-Wei Cheng (S'07-M'10)** received the B.S. and M.S. degrees from the National Taiwan University, Taipei, Taiwan, in 2000 and 2002, respectively, and the Ph.D. degree from the University of Washington, Seattle, in 2009, all in electrical engineering.

From 2002 to 2004, he was with MediaTek Inc., Hsinchu, Taiwan. In 2010, he worked at Institute of Microelectronics, A\*STAR, Singapore as a Senior Research Engineer and later became the Acting Principal Investigator of Biomedical IC Group in Integrated Circuits & Systems Laboratory. He is

currently an assistant professor at National Cheng Kung University, in Tainan, Taiwan, where he is focusing on low power analog and RF IC design for wireless communications and biomedical systems.

Dr. Cheng was a recipient of the Best Student Paper Award of IEEE Radio Frequency Integrated Circuits (RFIC) symposium in 2009 and Analog Devices Outstanding Student Designer Award in 2008.

Minkyu Je (S'97-M'03-SM'12) received the M.S. and Ph.D. degrees, both in Electrical Engineering and Computer Science, from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1998 and 2003, respectively. In 2003, he joined Samsung Electronics, Giheung, Korea, as a Senior Engineer and worked on multimode multi-band RF transceiver SoCs for GSM/GPRS/EDGE/WCDMA standards.

Since 2006 he has been with Institute of Microelectronics (IME), Agency for Science,

Technology and Research (A\*STAR), Singapore, and is currently working as a Senior Scientist and leading the Integrated Circuits and Systems Laboratory. Since he joined IME, he has led various projects developing low-power 3D accelerometer ASICs for high-end medical motion sensing applications, readout ASICs for nanowire biosensor arrays detecting DNA/RNA and protein biomarkers for point-of-care diagnostics, ultra-low-power sensor node SoCs for continuous real-time wireless health monitoring, and wireless implantable sensor ASICs for medical devices, as well as low-power radio SoCs and a MEMS interface/control SoCs for consumer electronics and industrial applications. His main research areas are low-power analog & mixed-signal circuits and systems interfacing with bio and MEMS sensors, circuit design and multi-functional system integration with novel devices and technologies, wireless telemetry circuits and systems for biomedical applications, and heterogeneous 3D IC systems. He has more than 130 peer-

reviewed international conference and journal publications in the areas of sensor interface IC, wireless IC, biomedical microsystem, 3D IC, device modeling and nanoelectronics. He also has more than 20 patents issued or filed

He is a Program Manager of NeuroDevices Program under A\*STAR Science and Engineering Research Council (SERC) and an Adjunct Assistant Professor in the Department of Electrical and Computer Engineering at National University of Singapore (NUS). He currently serves on the Technical Program Committee of the IEEE International Solid-State Circuits Conference (ISSCC).