## 7.6 A 128-Channel 6mW Wireless Neural Recording IC with On-the-Fly Spike Sorting and UWB Tansmitter

Moosung Chae<sup>1</sup>, Wentai Liu<sup>1,2</sup>, Zhi Yang<sup>1</sup>, Tungchien Chen<sup>1,3</sup>, Jungsuk Kim<sup>1</sup>, Mohanasankar Sivaprakasam<sup>1</sup>, Mehmet Yuce<sup>4</sup>

'University of California at Santa Cruz, Santa Cruz, CA <sup>2</sup>National Chiao-Tung University, Hsinchu, Taiwan <sup>3</sup>National Taiwan University, Taipei, Taiwan <sup>4</sup>University of New Castle, Callaghan, Australia

Simultaneous neural signal recording from many neurons has a wide range of applications ranging from the study of the complex biological neural networks to brain controlled neural prostheses to treat spinal cord injuries by restoring limb movement [1]. Wireless transmission of the recorded signals combined with on-chip neural spike sorting (a recording electrode senses the activity of an ensemble of neurons) is required for miniaturized and untethered neural recording systems. For neural prosthetic applications where the neural signals are translated to command signals for muscle stimulation, on-the-fly spike sorting and calibration is crucial for effective restoration of limb movement. Also, all these critical functions should be low power and wirelessly powered or operated on rechargeable battery.

Recently reported ICs for neural recording have features of simultaneous multiple channel recording [2,3], wireless data telemetry (spike information for 100 channels and raw data for one channel) [4], on-chip spike detection [4,5]. But a fully-integrated IC with simultaneous recording, on-chip spike detection and sorting and versatile wireless telemetry (raw and compressed data) has not been reported yet. This paper presents one such system with the capability to record, process and wirelessly transmit multiple neural signals real-time.

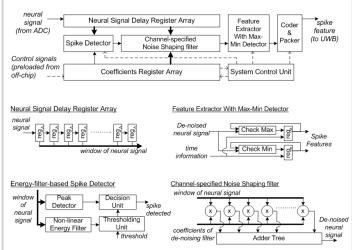

The chip is composed of eight 16-channel front-end blocks, data serializing circuits, a DSP for on-chip spike sorting, digital MUX, encoder, UWB TX, and bias generators (Fig. 7.6.1). The chip operates in one of the two modes. In sorting mode, a selected channel is connected to the on-the-fly spike sorting block and the extracted features of the spikes are transmitted for off-chip classification. In streaming mode, all the sampled data from the 128 channels are recorded and transmitted without any additional processing.

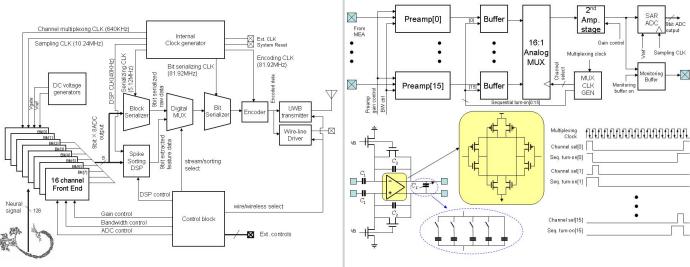

The front-end block consists of preamplifiers, buffers, an analog MUX, a second amplifier and a SAR-ADC (Fig. 7.6.2). The amplifiers are designed to have variable gain and bandwidth to meet the requirement of biological experiments. 16-to-1 multiplexing is chosen to minimize the power-area product of the entire system [6]. The preamplifier uses ac-coupling to reject the large dc offset occurring at the electrode-tissue interface [4]. The gain of the preamplifier is 40dB, and the second amplifier following the analog multiplexer provides an additional gain of 17dB to 20dB according to external controls. The high frequency roll-off of the preamplifier is variable from 2kHz to 20kHz in 16 steps by varying the load capacitance C<sub>L</sub>. The low frequency roll-off is variable from 0.1Hz to 200Hz by changing the gate voltage V<sub>B</sub> of the NMOS used as bias resistors. The gate voltage provided by the bias generator is variable from 600mV to 1V by 50mV steps. A fully-differential self-biased OTA enables a large 90dB CMRR and 80dB PSRR with  $4.9\mu V_{rms}$  input-referred noise. Each preamplifier draws only 2µA and each buffer draws 20.3µA to drive the analog multiplexer. The amplifier after the multiplexer driving 10pF draws 40.6µA. A large reduction in power consumption is achieved by the sequential turn-on method in front-end blocks by 71% (7.5mW). Due to the time-multiplexing architecture of the system, not all the channels have to be turned on. Therefore, only two of the 16 channels are turned on at any one time. For example, only the first and second channels are turned on when a sample from the first channel is digitized (Fig. 7.6.2). A SAR-ADC is used for sampling and digitizing multiplexed signals at 40kSample/s/channel resulting in 640kSample/s. The resolution of the ADC can be adjusted from 6 to 9 bits. The reference voltage for the ADC is supplied by the bias generators and variable from 100mV to 500mV by 50mV steps.

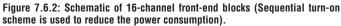

Traditional spike feature extraction algorithms, such as principal component analysis (PCA), require frequent training through thou-

sands of spike sequences [7]. Thus more than 1Mb/channel memory is required, which precludes a small area and low power implementation. Previous on-chip spike detections [3-5] use thresholding circuitry that would result in information loss of the features of the neural signals. Figure 7.6.3 shows the algorithm that enables the on-chip spike feature extraction. A noise shaping filter is used to reduce the neuronal noise as well as manifest neurons' geometry signatures. This filter combined with a max-min detector extracts the features, and enables the subsequent classification schemes to produce more precise clusters than PCA.

Figure 7.6.4 shows the on-chip on-the-fly spike detection and feature extraction engine. The 9 bit serial ADC output containing the time-multiplexed neural signals is fed to the spike detection and sorting units. The serial output data after the sorting consists of spike features in the form of three 9 bit scores per action potential. The data is processed, encoded and fed to the UWB TX on-the-fly within 41 cycles (1.025ms). The clustering of the scores received at the UWB RX is done off-chip. The coefficients register array is pre-loaded with 32 values, 9 bits each, which are computed within a few seconds of the initial recordings.

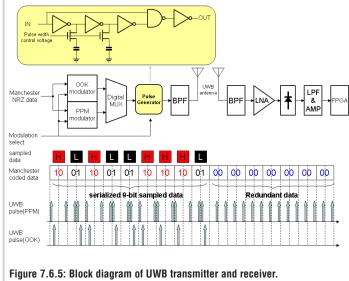

The 3.1 to 10.6GHz spectrum assigned by the FCC for unlicensed use of ultra-wideband devices offers an opportunity for short range, high data rate wireless communication. Impulse radio type UWB uses short pulses for transmission and this makes the TX design very simple, small-area, and low-power while providing data bandwidths of up to 90Mb/s for the simultaneous recording of more than 100 channels. These features make the impulse radio UWB one of the best candidates for the wireless telemetry for multi-channel neural recording systems [8]. The sampled and serialized data is Manchester encoded and then OOK or PPM modulated. Redundant data is inserted between every sampled data packet to be distinguished at the receiver side. Short pulses are generated according to the modulated signal, passed through a BPF for the transmitted signal to fit under the FCC emission mask and fed into the off-chip UWB antenna. The UWB RX was built from off-the-shelf components since it is outside the biological systems. The received signal is passed through a BPF whose center frequency is 4GHz, and then amplified by the LNA stages. A diode and a LPF down converts the UWB signal to low-frequency and the baseband data is finally recovered by an FGPA (Fig. 7.6.5).

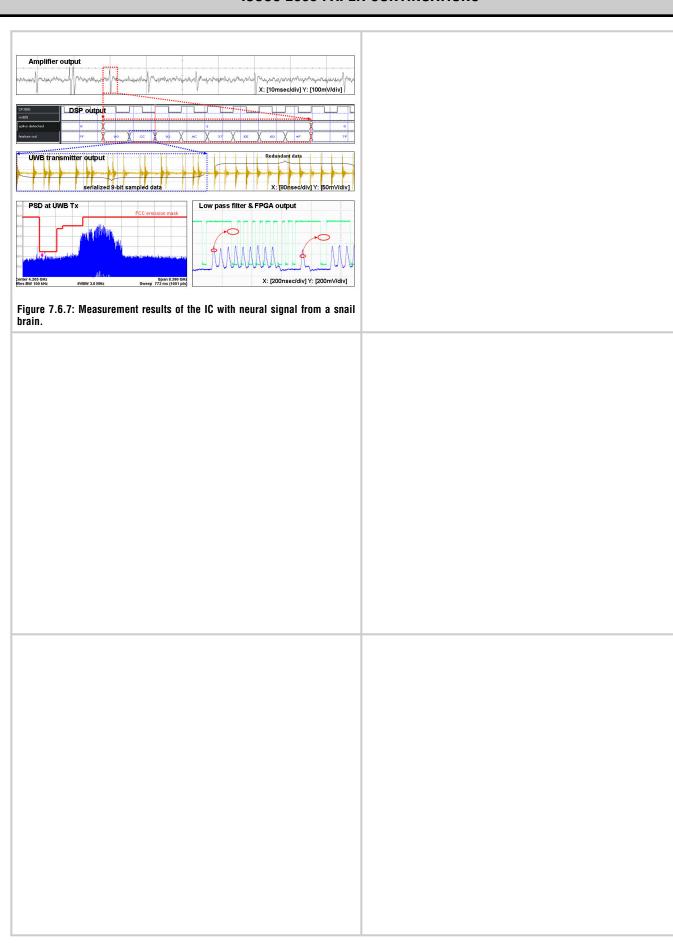

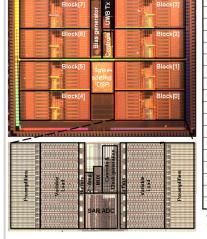

The IC was fabricated in a  $0.35\mu m$  4M2P CMOS process and the chip size is  $8.8\times7.2 mm^2$  (Fig. 7.6.6). The measured power consumption of the entire chip is 6mW from  $\pm 1.65 V$  when operating in streaming mode. The 8 front-end blocks consume 50% of the total power. The UWB TX consumes 1.6mW with PPM modulation. The power consumption of the DSP block is only 0.1mW. The chip was first tested with signal generators to evaluate the performance of each circuit block and measurement results are summarized in Fig. 7.6.7. Extracelluar recordings were made from a dissected snail brain to verify the functionality of the entire system. Waveforms at the output of amplifier, spike sorting, UWB TX, UWB RX were monitored by the built-in test circuits (Fig. 7.6.7).

## References:

A. B. Schwartz, "Cortical Neural Prosthetics," Annual Review of Neuroscience, vol. 27, pp. 487-501, July 2004.

J. N. Y. Aziz, et al., "Brain-Silicon Interface for High-Resolution in vitro

[2] J. N. Y. Aziz, et al., "Brain-Silicon Interface for High-Resolution in vitro Neural Recording," *IEEE Trans. on Biomedical Circuits and Systems*, vol. 1, no. 1, pp. 56-62, March 2007.

[3] Y. Perelman, R. Ginosar, "An Integrated System for Multichannel Neuronal Recording With Spike/LFP Separation, Integrated A/D Conversion and Threshold Detection," *IEEE Trans. on Biomedical Engineering*, vol. 54, no. 1, pp. 130-137, Jan. 2007.

[4] R. R. Harrison, et al., "A Low-Power Integrated Circuit for a Wireless 100-Electrode Neural Recording System," *IEEE J. Solid-State Circuits*, vol. 42, no. 1, pp. 123-133, Jan. 2007.

[5] A. M. Sodagar, K. D. Wise, K. Najafi, "A Fully Integrated Mixed-Signal Neural Processor for Implantable Multichannel Cortical Recording," *IEEE Trans. on Biomedical Engineering*, vol. 54, no. 6, pp. 1075-1088, June 2007.

[6] M. Chae, W. Liu, G. Wang, M. Sivaprakasam, "Design Methodology for an Integrated Low Power Neural Recording System," BMES Annual Fall Meeting, Oct. 2006.

[7] M. S. Lewicki, "A Review of Methods for Spike Sorting: the Detection and Classification of Neural Action Potentials," *Network: Comput. Neural Syst.*, vol. 9, pp. R53-R78, 1998.

[8] M. R. Yuce, W. Liu, M. Chae, J. Kim, "A Wideband Telemetry Unit for Multi-Channel Neural Recording Systems," *IEEE ICUWB*, pp. 612-617, Sept. 2007.

Figure 7.6.1: Block diagram of the integrated neural recording system.

Figure 7.6.3: Proposed spike sorting algorithm.

Figure 7.6.4: Block diagram of an on-line spike sorting engine.

| 3                |

|------------------|

|                  |

| V <sub>rms</sub> |

| 3                |

| 3                |

| z~ 200Hz *       |

| z ~ 20KHz *      |

| 3 ~ 20dB *       |

| bits *           |

| (sample/sec      |

| W                |

| ops              |

| w                |

| 5V               |

| W                |

| um 4M2P CMOS     |

| m ×7.2mm         |

|                  |

Measured performance

Figure 7.6.6: Chip micrograph and performance summary.

Continued on Page 603

## **ISSCC 2008 PAPER CONTINUATIONS**