# A 2.6 nW, 0.45 V Temperature - Compensated Subthreshold CMOS Voltage Reference

# Luca Magnelli

Dipartimento di Elettronica, Informatica e Sistemistica, Università della Calabria

# Felice Crupi

Dipartimento di Elettronica, Informatica e Sistemistica, Università della Calabria

# **Pasquale Corsonello**

Dipartimento di Elettronica, Informatica e Sistemistica, Università della Calabria

## **Calogero Pace**

Dipartimento di Elettronica, Informatica e Sistemistica, Università della Calabria

### Giuseppe Iannaccone

Dipartimento di Ingegneria dell'Informazione: Elettronica, Informatica, Telecomunicazioni, Università di Pisa

L.Magnelli, F.Crupi, P.Corsonello, C.Pace, G. Iannaccone, *A 2.6 nW, 0.45 V Temperature -Compensated Subthreshold CMOS Voltage Reference,* IEEE Journal of Solid-State Circuits, **46**, 2, pp.465-474 (2011).

# A 2.6 nW, 0.45 V Temperature-Compensated Subthreshold CMOS Voltage Reference

Luca Magnelli, Felice Crupi, Pasquale Corsonello, *Member, IEEE*, Calogero Pace, and Giuseppe Iannaccone, *Senior Member, IEEE*

Abstract—A voltage reference circuit operating with all transistors biased in weak inversion, providing a mean reference voltage of 257.5 mV, has been fabricated in 0.18  $\mu$ m CMOS technology. The reference voltage can be approximated by the difference of transistor threshold voltages at room temperature. Accurate subthreshold design allows the circuit to work at room temperature with supply voltages down to 0.45 V and an average current consumption of 5.8 nA. Measurements performed over a set of 40 samples showed an average temperature coefficient of 165 ppm/°C with a standard deviation of 100 ppm/°C, in a temperature range from 0 to 125 °C. The mean line sensitivity is ≈0.44%/V, for supply voltages ranging from 0.45 to 1.8 V. The power supply rejection ratio measured at 30 Hz and simulated at 10 MHz is lower than −40 dB and −12 dB, respectively. The active area of the circuit is ≈0.043 mm².

Index Terms—Voltage reference, subthreshold circuit, ultra-low power, temperature compensation, CMOS analog design.

#### I. INTRODUCTION

DUBTHRESHOLD circuits are becoming increasingly popular in low-power low-voltage design. Thanks to the power savings offered, they are particularly attractive in portable scenarios, such as wearable medical devices [1] or passive RFIDs, where energy optimization is of the utmost importance. Moreover, self-powered energy-harvesting systems [2], used to provide power for applications like wireless microsensors and biomedical implants, also employ subthreshold operation to reduce energy consumption. Those power requirements are mostly met by means of supply voltage reduction allowed by subthreshold operation. However, devices biased in subthreshold are much more sensitive to temperature variations and to process variability, in particular to threshold voltage dispersion. This is therefore a challenge for the designer to devise and employ circuit compensation techniques.

Manuscript received April 29, 2010; revised October 25, 2010; accepted October 27, 2010. Date of publication December 20, 2010; date of current version January 28, 2011. This paper was approved by Associate Editor Lucien Breems. This work was supported in part by the Consiglio Regionale della Calabria under the project *Programma di stages per i migliori giovani laureati della Calabria:* L.R. n. 08/2007, art. 3 L.R. n. 26/2004.

- L. Magnelli is with the Dipartimento di Elettronica, Informatica e Sistemistica, Università della Calabria, I-87036 Arcavacata di Rende (CS), Italy (e-mail: luca.magnelli@deis.unical.it).

- F. Crupi, P. Corsonello, and C. Pace are with the Dipartimento di Elettronica, Informatica e Sistemistica, Università della Calabria, I-87036 Arcavacata di Rende (CS), Italy.

- G. Iannaccone is with the Dipartimento di Ingegneria dell'Informazione: Elettronica, Informatica e Telecomunicazioni, Università di Pisa, I-56122 Pisa (PI), Italy (e-mail: g.iannaccone@iet.unipi.it).

Digital Object Identifier 10.1109/JSSC.2010.2092997

Voltage references are broadly used in analog and digital systems to generate a DC voltage independent of Process, supply Voltage and Temperature (PVT) variations. The most common solution for on-chip integration is the Bandgap Voltage Reference (BGR), which can be implemented in standard CMOS technology exploiting parasitic vertical BJTs. Conventional BGRs generate a nearly temperature independent reference, of about 1.25 V, and therefore they require a higher supply voltage, which might not meet the low-voltage constraints for low-power applications. However, several solutions, exploiting the BGR principle, have been implemented that ensure sub-1V operation [3]. In [4]–[6] the reference voltage is lowered by means of resistive subdivision. As an alternative approach, floating gate structures have been used to realize high precision programmable voltage references, as in the case of [7], where subthreshold operation allowed a minimum power consumption of 1.35  $\mu$ W. Most often forward biased PN-junctions of BGRs are substituted with MOSFETs biased in the subthreshold region [8]–[10]. Thus, a supply voltage  $(V_{DD})$  of 0.6 V and a power consumption of 9  $\mu$ W are achieved. Other solutions have been implemented in standard CMOS technology, without exploiting the traditional BGR principle [11]–[15]. Subthreshold operation allowed sub-1  $\mu$ W power consumption [12]–[15] and sub-1V operation [14], [15].

In this work, subthreshold operation is exploited to minimize both the power consumption and the supply voltage. A new CMOS voltage reference configuration, based on a temperature compensation technique derived from the subthreshold regime of operation, is described. Within the circuit, n-channel MOS-FETs with two different threshold voltages are present and the reference voltage value can be approximated, in last analysis, to the difference of those two threshold voltages at room temperature. Measurements on silicon confirm that the proposed configuration allows minimum power consumption about one order of magnitude lower than the best solutions found in the literature. Among the compared circuits, the proposed configuration is characterized by the lowest supply voltage.

This paper is organized as follows: in Sections II and III the principle of operation of the proposed voltage reference and the circuit configuration realized are described in detail; dynamic range and power consumption considerations are discussed in Section IV; in Section V measurement results are shown and compared with low-power low-voltage competitors.

#### II. OPERATING PRINCIPLE

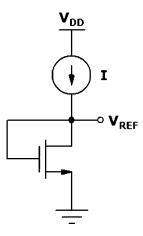

A voltage reference can be simply represented by a current source and a diode connected NMOS, as shown in Fig. 1. Such a structure has been adopted in [14], where the load nMOS works

Fig. 1. Scheme of principle of a simple voltage reference.

in the saturation region providing a temperature compensated reference voltage  $(V_{\rm REF})$  higher than its threshold voltage  $(V_{\rm th})$  at room temperature.

In this work we exploited the subthreshold operation of the load transistor, in order to obtain  $V_{\rm REF} < V_{\rm th}$  and, consequently, to further reduce the supply voltage of the overall voltage reference circuit. It is worth noting that biasing the load nMOS in subthreshold region in [14] would not allow temperature compensation, consequently even the current source solution adopted in this work is different from the one used in [14].

Investigating the subthreshold behaviour of the load, a formula for the injected current, compensating the reference voltage dependence on temperature, can be obtained. The I-V characteristics of an nMOS operating in subthreshold region is given by

$$I_D = S\mu V_T^2 \exp\left(\frac{V_{\rm GS} - V_{\rm th}}{mV_T}\right) \left[1 - \exp\left(-\frac{V_{\rm DS}}{V_T}\right)\right] \quad (1)$$

where  $S=(W/L)C_{\rm OX}$  (W/L is the transistor aspect ratio and  $C_{\rm OX}$  is the gate oxide capacitance per unit area),  $\mu$  is the electron mobility,  $V_T=k_B\,T/q$  is the thermal voltage ( $k_B$  is the Boltzmann constant, q the elementary charge and T the absolute temperature),  $V_{\rm th}$  is the MOSFET threshold voltage, m the subthreshold slope parameter,  $V_{\rm GS}$  and  $V_{\rm DS}$  are the gate-to-source and the drain-to-source voltages, respectively. From (1), for  $V_{\rm DS} \geq 4V_T$ ,  $I_D$  becomes almost independent of  $V_{\rm DS}$ , thus  $V_{\rm REF}$  can be approximated by

$$V_{\text{REF}} = V_{\text{GS}} = V_{\text{th}} + mV_T \ln \left(\frac{I_D}{S\mu V_T^2}\right).$$

(2)

Let us note that, at a first approximation,  $V_T(T)$ ,  $V_{\rm th}(T)$  and  $\mu(T)$  introduce dependence on temperature. As shown in (3), it is usually assumed that  $V_{\rm th}$  decreases linearly with temperature [16]:

$$V_{\rm th} = V_{\rm th}(T_0) + (k_{t1} + k_{t2}V_{\rm BS})(T/T_0 - 1)$$

(3)

where  $V_{\rm th}(T_0)$  is the threshold voltage at the reference temperature  $(T_0 \cong 300.15^{\circ}{\rm K}), V_{\rm BS}$  is the body-to-source voltage of the transistor. Temperature coefficients  $k_{t1}$  and  $k_{t2}$  have negative values.

In order to have a temperature compensated output reference voltage, the following condition must be satisfied:

$$\frac{\partial V_{\text{REF}}}{\partial T} = 0. {4}$$

Based on (2), a simple solution of (4) can be obtained by generating the current  $I_D$  with the following temperature dependence:

$$I_D(T) = \alpha \mu T^2 \tag{5}$$

Therefore, imposing (4) a value for a (constant with temperature) can be found. Substituting it in (2) and remembering that  $V_{\rm BS}=0$  V in the scheme of Fig. 1, the reference voltage becomes

$$V_{\text{REF}} = V_{\text{th}}(T_0) + |k_{t1}|.$$

(6)

However, the above solution does not ensure subthreshold operation for the active load.

For this reason, more detailed analysis has to be done, considering for the current source the more general form  $I(T) = \alpha \mu T^2 f(T)$ . Substituting it in (2), the condition (4) becomes a differential equation in f(T):

$$\frac{\partial V_{\text{REF}}}{\partial T} = \frac{k_{t1}}{T_0} + m \frac{k_B}{q} \ln \left( \frac{\alpha}{S(k_B/q)^2} \right) + m \frac{k_B}{q} \left\{ \ln (f(T)) + \frac{T}{f(T)} \frac{\partial}{\partial T} (f(T)) \right\} = 0.$$

(7)

In order to achieve temperature compensation the term in curly brackets in (7) should be constant with temperature. A possible solution for f(T) could be simply a constant, but this would lead to the case found in (5). Another solution, which can ensure subthreshold operation, can be written as

$$I_D(T) = \alpha \mu T^2 \exp\left(\frac{AT + B}{CT}\right) \tag{8}$$

where A,B and C are constant with temperature. This solution has been chosen since it was easy to generate with a subthreshold MOSFETs based current reference, as will be clear in the next section. It is worth noting that the current reference used in [14] does not allow implementing (8), therefore, in that case, it is not possible to compensate temperature effects by biasing the load in subthreshold regime. Substituting (8) in (2), from (4) an expression for a can be found which leads to the temperature-compensated reference voltage

$$V_{\text{REF\_OPT}} = V_{\text{th}}(T_0) + |k_{t1}| + m \frac{k_B}{q} \frac{B}{C}.$$

(9)

In this case, if the term B/C is negative, differently from (6), the load transistor can work in subthreshold region. In the next section we will show how to implement a circuit configuration like the one in Fig. 1, based on the proposed operating principle.

#### III. ELECTRICAL CONFIGURATION

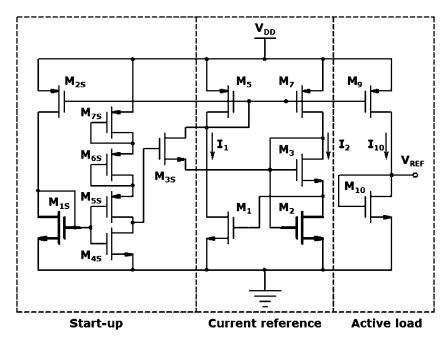

The architecture of the proposed voltage reference is illustrated in Fig. 2. The self-biased current source has no resistors and works with all MOSFETs in the subthreshold region. It generates the current to be injected in the load transistor  $(M_{10})$

Fig. 2. Proposed CMOS voltage reference circuit.

TABLE I PROCESS PARAMETERS

| Technology | UMC 0.18-μm CMOS process.                                    |                       |                       |  |  |  |

|------------|--------------------------------------------------------------|-----------------------|-----------------------|--|--|--|

|            | Voltage range                                                | V <sub>th</sub> -NMOS | V <sub>th</sub> -PMOS |  |  |  |

| SVT-MOSFET | $0 \text{ V} \le V_{GS}, V_{DS},  V_{BS}  \le 1.8 \text{ V}$ | 0.320 V               | -0.456 V              |  |  |  |

| HVT-MOSFET | $0 \text{ V} \le V_{GS}, V_{DS},  V_{BS}  \le 3.3 \text{ V}$ | 0.600 V               | -0.720 V              |  |  |  |

${\bf TABLE~II}$   ${\bf TRANSISTOR~SIZES~OF~THE~CURRENT~REFERENCE~AND~THE~ACTIVE~LOAD}$

| Transistor      | Value (W/L)                                                                                 |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------|--|--|--|

| $\mathbf{M}_1$  | 8 μm / 50 μm                                                                                |  |  |  |

| M <sub>2</sub>  | $100 \ \mu \text{m} / 24 \ \mu \text{m} = (50 \ \mu \text{m} / 24 \ \mu \text{m}) \times 2$ |  |  |  |

| M <sub>3</sub>  | 2 μm / 2 μm                                                                                 |  |  |  |

| M <sub>5</sub>  | $68 \mu \text{m} / 50 \mu \text{m} = (17 \mu \text{m} / 50 \mu \text{m}) \times 4$          |  |  |  |

| M <sub>7</sub>  | $52 \mu m / 50 \mu m = (26 \mu m / 50 \mu m) \times 2$                                      |  |  |  |

| M <sub>9</sub>  | 97 $\mu$ m / 29 $\mu$ m = (48.5 $\mu$ m / 29 $\mu$ m) × 2                                   |  |  |  |

| M <sub>10</sub> | 1.5 μm / 50 μm                                                                              |  |  |  |

branch. A start-up circuit has been added as a precautionary measure to ensure bias in the desired state.

Table I summarizes information about the technology chosen to implement the proposed circuit. In particular, the table contains the allowed voltage ranges and the threshold voltage values of both Standard  $V_{\rm th}$  (SVT) and High  $V_{\rm th}$  (HVT) MOSFET models.

Table II shows the size of transistors in the current reference and in the active load.

#### A. Current Reference

The purpose of the current generator in Fig. 2 is to provide a current, as independent as possible of supply voltage variations, which compensates temperature effects on  $V_{\rm REF}$ .

A current in the form (8) can be obtained taking into account a linear combination of nMOS  $V_{\rm GS}$  voltages in the subthreshold region. Among the possible solutions for the current reference we chose a self-biased configuration where only three subthreshold operated NMOSs,  $\rm M_{1-3}$ , perform such  $V_{\rm GS}$  combination, giving

$$V_{\text{GS2}} = V_{\text{GS1}} + V_{\text{GS3}}.$$

(10)

In the current reference, PMOSFETs  $\mathrm{M}_5$  and  $\mathrm{M}_7$  form a subthreshold current mirror providing ratioed currents  $I_2/I_1 = (W/L)_7/(W/L)_5 = a$ . All the transistors in the proposed solution are SVT-MOSFETs, except for  $\mathrm{M}_2$  and  $\mathrm{M}_{1\mathrm{S}}$ , which are HVT-MOSFETs. In order to ensure subthreshold operation for the whole current source, for  $\mathrm{M}_2$  a high  $V_{\mathrm{th}}$  device was chosen. Using (2), (9) becomes

$$m_2 V_T \ln \left( \frac{I_2}{S_2 \mu_2 V_T^2} \right) = \Delta V_{\text{th}} + m_3 V_T \ln \left( \frac{I_2}{S_3 \mu_3 V_T^2} \right) + m_1 V_T \ln \left( \frac{I_1}{S_1 \mu_1 V_T^2} \right)$$

(11)

where  $\Delta V_{\rm th} = V_{\rm th1} + V_{\rm th3} - V_{\rm th2}$ . Assuming that electron mobilities in (11) are identical ( $\mu \approx \mu_1 \approx \mu_2 \approx \mu_3$ ) and using  $I_2 = aI_1$ , the current flowing in the left branch of the current generator can be evaluated from (11) as

$$I_1 = Q^{1/\Sigma_m} \mu V_T^2 \exp\left(-\frac{\Delta V_{\text{th}}}{V_T \Sigma_m}\right)$$

(12)

where  $Q=a^{m_2-m_3}(S_3^{m_3}S_1^{m_1}/S_2^{m_2})$  and  $\Sigma_m=m_1+m_3-m_2$ . Considering the  $V_{\rm th}$  thermal behaviour shown in (3), it can be concluded that the subthreshold current reference architecture in Fig. 2 generates a current in the form (8).

The stability of  $V_{\rm REF}$  with  $V_{\rm DD}$  variations mainly depends on the current generator's insensitivity to supply voltage variations. This characteristic is achieved by means of the self-biased current source architecture, where the high impedance elements per branch ( $M_7$  and  $M_1$ ) are capable of absorbing supply voltage variations leaving their current almost unchanged [17].

Significant improvement of the reference voltage line sensitivity and the power supply rejection ratio (PSRR) can be obtained by using an additional current mirror, in the self biased current reference circuit [12]. The use of additional current mirrors in the current generator, which add transistors in stack increasing the minimum achievable  $V_{\rm DD}$ , were avoided.

#### B. Active Load

The generated current is then mirrored into a diode connected transistor through  $M_9$ . The current mirror gain can be expressed as  $I_{10}/I_1 = (W/L)_9/(W/L)_5 = c$ . Therefore, with  $M_{10}$  working in the subthreshold region, the reference voltage becomes, from (2) and (12),

$$V_{\text{REF}} = V_{\text{th}10} + m_{10}V_T \ln \left\{ Q^{1/\Sigma_m} \frac{c}{S_{10}} \right\} - \frac{m_{10}}{\Sigma_m} \Delta V_{\text{th}}. \quad (13)$$

The temperature dependence of the reference voltage is firmly related to the thermal behaviour of  $V_T$  and  $V_{\rm th}$ . According to the linear approximation made in (3), setting  $\partial V_{\rm REF}/\partial T=0$ , a value of  $(W/L)_{10}$  for temperature compensation can be extracted as

$$\left(\frac{W}{L}\right)_{10\text{OPT}} = \frac{Q^{1/\Sigma_m} c/C_{\text{OX}10}}{\exp\left\{\frac{q}{k_B T_0} \left[\frac{1}{\Sigma_m} \left(K + k_{t2,3} V_{\text{BS}3}\right) - \frac{k_{t1,10}}{m_{10}}\right]\right\}}$$

(14)

where  $K = k_{t1,1} + k_{t1,3} - k_{t1,2}$  ( $k_{t1,i}$  and  $k_{t2,i}$  are the threshold voltage temperature coefficients of the i-th transistor).

Hence, satisfying (13),  $V_{\text{REF}}$  becomes

$$\begin{aligned}

& \left[ V_{\text{th}10}(T_0) + |k_{t1,10}| + \frac{m_{10}}{\Sigma_m} (V_{\text{th}2}(T_0) + |k_{t1,2}|) \\

& - \left[ \frac{m_{10}}{\Sigma_m} (V_{\text{th}1}(T_0) + V_{\text{th}3}(T_0) \\

& + |k_{t1,1}| + |k_{t1,3}| + |k_{t2,3}| V_{\text{BS}3}) \right].

\end{aligned} (15)$$

The term indicated in square brackets ensures subthreshold operation of  $M_{10}$ .

As is clear from (15), the reference voltage value only depends on process parameters. A simpler expression for  $V_{\text{REF\_OPT}}$  can be obtained considering that, as usual, the m parameters of different NMOSFETs biased in the subthreshold region have similar values (then  $m_{10}/\Sigma_m \approx 1$ ) and  $k_{t1,1} \approx k_{t1,2} \approx k_{t1,3} \approx k_{t1,10}$ . Therefore, the reference voltage value can be approximated to the threshold voltage difference

between an HVT-NMOS ( $V_{\rm th2}$ ) and an SVT-NMOS ( $V_{\rm th1}$ ) or  $V_{\rm th3}$ ). For the technology chosen this difference is enough for the subthreshold operation of  $M_{10}$  and, consequently, it is possible to exploit the temperature compensation theory developed in the first section. The mean reference voltage measured is 257.5 mV, about 23 mV lower than the roughly predicted value. This difference is mainly due to the increase of the threshold voltage of  $M_3$  caused by both body effect and the effect of lateral pocket implants ( $M_3$  has a medium channel length of 2  $\mu$ m).

The active load aspect ratio, for temperature compensation, predicted by (14), for the chosen technology, neglecting the body effect on  $M_3$ , is 0.0273, while the one chosen after circuit simulation for temperature coefficient optimization, is  $(W/L)_{10}=1.5~\mu\text{m}/50~\mu\text{m}=0.030$ . The good agreement confirms the validity of the proposed theoretical approach for subthreshold temperature compensation.

#### IV. DESIGN CONSIDERATIONS

#### A. Dimensioning for Minimum Current Consumption

The minimum current consumption is not limited by the operating region of transistors inside the proposed configuration. Thanks to subthreshold operation, all  $|V_{\rm GS}|$  values are smaller than the absolute value of MOSFET threshold voltages. Recalling (2), it can be stated that, in principle, there is no lower limit for the current supplied in the subthreshold voltage reference of Fig. 2. Nevertheless, the proposed temperature compensation technique imposes a lower bound for the generated current, as explained in the following.

The total current drawn from the power supply, neglecting the current flowing in the start-up circuit, can be expressed as the sum of the currents injected into the current source and the active load branches:

$$I_{\text{DD}} = I_1(1+a+c) = I_1B.$$

(16)

From (12) and (14), we can rewrite  $I_{\rm DD}$  as

$$I_{\rm DD} = \frac{A}{E} \frac{B}{c} \left(\frac{W}{L}\right)_{10\rm OPT} \tag{17}$$

wherein with A and E we indicate the process and temperature dependent parameters found in (12) and (14), respectively:

$$A = \mu V_T^2 \exp\left(-\frac{\Delta V_{\text{th}}}{V_T \Sigma_m}\right)$$

(15)

$$\frac{1}{E} = C_{\text{OX}10} \exp\left\{\frac{q}{k_B T_0} \left[\frac{1}{\Sigma_m} (K + k_{t2,3} V_{\text{BS}3}) - \frac{k_{t1,10}}{m_{10}}\right]\right\}.$$

(18)

The remaining terms in (17) only rely on MOSFET aspect ratios. In order to reduce the power consumption, while compensating temperature effects on the reference voltage, the load aspect ratio resulting from (12) should not exceed the minimum derivable for the technology chosen:  $W_{\rm MIN}/L_{\rm MAX}$ . Moreover, to further reduce  $I_{\rm DD}$ , the term B has to be minimized (from (16),  $B_{\rm MIN} \sim 1$ ), whereas the current mirror gain c has to be maximized (i.e.,  $c_{\rm MAX} = (W_{\rm MAX}/L_{\rm MIN})/(W_{\rm MIN}/L_{\rm MAX})$ ).

#### B. Minimum Supply Voltage

Considering the voltage reference configuration in Fig. 2, the supply voltage will redistribute as a sum of a  $V_{\rm DS}$  and a  $V_{\rm GS}$  in the branches of both current reference and active load. Although subthreshold operation does not limit the minimum  $V_{\rm GS}$  achievable, in order to generate a current and hence a reference voltage, as independent as possible of  $V_{\rm DD}$  variations, the high impedance transistors (i.e.,  $M_1$ ,  $M_7$  and  $M_9$ ) should absorb at least a  $V_{\rm DS} \sim 4V_T$ . The maximum working temperature of the proposed circuit is  $125^{\circ}{\rm C}$ , therefore, the minimum  $V_{\rm DS}$  value able to ensure proper operation, even at that temperature, becomes  $4V_T=137~{\rm mV}$ . Consequently, by generating a current (12) so that, in each branch,  $V_{\rm GS} \ll 4V_T$ , a minimum supply voltage of  $4V_T$  can be achieved with a similar voltage reference architecture regardless of the process technology chosen.

Nevertheless, in our specific case, the gate-to-source voltage of  $\rm M_{10}$ , obtained for temperature compensation, is process dependent and its value cannot be minimized. So, the minimum  $V_{\rm DD}$ , ensuring a  $|V_{\rm DS}| > 4V_T$  for  $\rm M_9$ , will be

$$V_{\text{DDMIN}} \ge V_{\text{REF\_OPT}} + 4V_T.$$

(19)

Since the mean reference voltage measured is 257.5 mV, it follows that  $V_{\rm DDMIN}$ , for the subthreshold circuit configuration in Fig. 2, will be equal or higher than 395 mV, considering the thermal voltage value at the maximum operating temperature. Obviously, the higher  $V_{\rm DDMIN}$ , the more accurate the approximation done in (2) for  $M_9$  and, as a consequence, the smaller the circuit line sensitivity.

From measurements, proper operation was observed with  $V_{\rm DD} \geq 450$  mV, which is the smallest obtained so far for voltage reference circuits.

#### C. Sensitivity to Supply Voltage Variations

A common parameter used for the evaluation of the reference voltage sensitivity to  $V_{\rm DD}$  variations is the line sensitivity. It is defined as  ${\rm LS}=(\Delta V_{\rm REF}/\Delta V_{\rm DD})/V_{\rm REF}(\%)$ , where  $\Delta V_{\rm DD}$  is the  $V_{\rm DD}$  range of operation (1.8 V - 0.45 V = 1.35 V for the proposed circuit),  $\Delta V_{\rm REF}$  is the absolute variation of the reference voltage, in the  $V_{\rm DD}$  range considered, and  $V_{\rm REF}$  stands for the mean output value. The line sensitivity optimization starts from the minimization of  $\Delta V_{\rm REF}$ . From Figs. 1 and 2, it is clear that it can be easily translated in the minimization of  $I_{10}$  variations.

Neglecting the effect of the term in square brackets in (1) (i.e., considering a  $V_{\rm DS} \geq 4V_T$ ), we can rewrite the subthreshold drain current, highlighting the  $V_{\rm DS}$  dependence:

$$I_D = I_0 \exp\left(\frac{V_{\rm GS}}{mV_T}\right) \exp\left(\frac{\lambda_D V_{\rm DS}}{mV_T}\right) \tag{20}$$

in which  $I_0$  summarizes the product between the aspect ratio and the process and temperature parameters found in (1) and  $\lambda_D$  is the drain-induced barrier lowering (DIBL) factor [18]. Subthreshold operated MOSFETs do not suffer from channel length modulation, therefore, for  $V_{\rm DS} \geq 4V_T, I_D$  will depend on  $V_{\rm DS}$  only because of the DIBL effect. As is well known, the DIBL effect significantly decreases with increasing channel length.

The  $\Delta V_{\rm DD}$  will cause a  $\Delta V_{\rm DS} = V_{\rm DSMAX} - V_{\rm DSMIN}$  on the high impedance transistor in the branch. Assuming constant  $V_{\rm GS}$ , the resulting  $I_D$  variation will be characterized by a maximum to minimum ratio  $I_{\rm DMAX}/I_{\rm DMIN} = \exp(\lambda_D \Delta V_{\rm DS}/mV_T)$ . Recalling (2), the  $\Delta V_{\rm REF}$  owing to  $V_{\rm DD}$  variations can be written as

$$\Delta V_{\text{REF}} = m_{10} V_T \ln \left( \frac{I_{\text{DMAX}}}{I_{\text{DMIN}}} \right)$$

$$= \frac{m_{10}}{m^*} \lambda_D \Delta V_{\text{DS}} \approx \lambda_D \Delta V_{\text{DS}}$$

(21)

where  $m^*$  is the subthreshold slope factor of the high impedance transistor.

Therefore, the line sensitivity can be rewritten as

LS

$$\approx \frac{\lambda_D}{V_{\rm REF}} \frac{\Delta V_{\rm DS}}{\Delta V_{\rm DD}} \% \approx \frac{\lambda_D}{V_{\rm REF}} \%.$$

(22)

As expected, for line sensitivity minimization, the high impedance transistors in the proposed configuration (i.e.,  $M_1$ ,  $M_7$ ,  $M_9$ ) should be as long as possible, in order to improve the stability of the generated current and, therefore, the one of  $V_{\rm REF}$ .

The result found in (22) not only gives a quick evaluation of the expected line sensitivity of the proposed voltage reference configuration, but can also be extended to every voltage reference architecture operated in subthreshold region, where only one high impedance transistor per branch is present. Such architectures are very common in ultra low voltage solutions, where the reduction of transistor stacks helps in lowering the minimum  $V_{\rm DD}$  achievable. In [14], where a two-transistor stack per each branch is present, a minimum  $V_{\rm DD}$  of 0.9 V was attained.

The DIBL factor was measured for a pMOS of the same channel length as  $\rm M_{9}$ , the transistor that absorbs  $V_{\rm DD}$  variations in the active load branch, obtaining a  $\lambda_{D}$  of about 0.001. From (21), therefore, the expected LS is 0.388%/V, only 13% different from the measured mean line sensitivity, due mostly to the subthreshold slope factor difference between pMOS and NMOS, which we assumed equal in (21).

#### D. Process Variations

The generated voltage (15) is a linear combination of threshold voltages parameters. As usually happens in low-power CMOS integrated voltage [12]–[15], the reference voltage is process dependent. Thus, neglecting matching errors in (14), the accuracy of the output voltage is mainly due to the accuracy of threshold voltages of transistors  $M_1$ ,  $M_3$ ,  $M_2$ ,  $M_{10}$ . Process variations are generally distinguished in WIthin Die (WID or intra-die) variations and Die to Die (D2D or inter-die) variations [12]. The first type of variations causes mismatch between transistors of the same chip and influences the relative accuracy of transistor parameters. Careful layout techniques [19] and large transistor W/L [20], can help to reduce those effects. D2D variations, instead, influence the absolute accuracy of transistor parameters and their effects are not compensated in the proposed configuration.

Threshold voltage measurements over a set of forty SVT-NMOSs, with a W/L of  $12~\mu\text{m}/50~\mu\text{m}$ , were performed. Each transistor belongs to a different die and is placed within the same

voltage reference dies. The average and the standard deviation values obtained are 318.5 mV and 6.7 mV, respectively. Expressing  $V_{\rm REF\_OPT}$  as the threshold voltage difference between an HVT-NMOS and an SVT-NMOS, the standard deviation of  $V_{\rm REF\_OPT}(\sigma_{\rm VREF})$  can be approximated with

$$\sigma_{\text{VREF}} = \sqrt{\sigma_{\text{HVT}}^2 + \sigma_{\text{SVT}}^2} \tag{23}$$

where  $\sigma_{\rm HVT}$  and  $\sigma_{\rm SVT}$  are the  $V_{\rm th}$  standard deviations of an HVT-NMOS and an SVT-NMOS, respectively. In (23) has been implicitly assumed that the variation processes of the two  $V_{\rm th}$  s are independent, i.e., their covariance is zero. Moreover, assuming that  $\sigma_{\rm HVT}=\sigma_{\rm SVT}=\sigma_{V_{\rm th}}$ , it is easy to evaluate the standard deviation of the voltage reference as

$$\sigma_{\text{VREF}} \approx \sqrt{2}\sigma_{V_{\text{th}}}.$$

(24)

The  $\sigma_{\rm VREF}$  obtained from (24) is 9.5 mV, only 0.5 mV lower than the measured one. This testifies that the main contributor to the voltage reference inaccuracies are the nMOS threshold voltage variations.

On the other hand, since the threshold voltage dependence of temperature,  $\partial V_{\rm th}/\partial T$  has small dependence on process variations, as demonstrated in [12], even the temperature coefficient of the reference voltage will benefit from a similar behaviour with process variations.

#### V. MEASUREMENT RESULTS

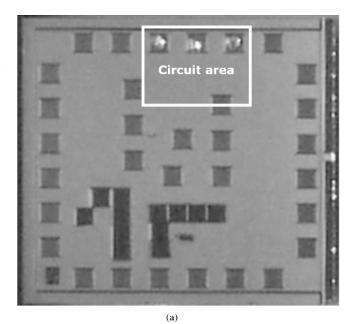

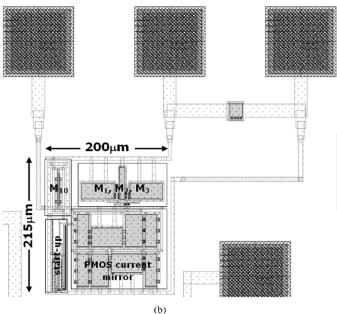

A set of 40 prototype chips, from three separate runs, were successfully implemented in UMC 0.18- $\mu$ m, 1.8 V/3.3 V, CMOS process. The circuit photo and the corresponding layout are shown in Fig. 3(a) and (b), respectively. The occupied chip area is only  $\approx 0.0430 \text{ mm}^2$ , thanks mainly to the reduced number of transistors in the core of the circuit (current reference and active load subsections).

Wafer-level DC measurements have been performed using a Cascade SUMMIT 11861B prober equipped with a Temptronic chuck temperature controller and a Keithley 4200-SCS semiconductor parameter analyzer.

In this section, measurement results of a chip with typical behaviour are discussed and compared with best performing low-power low-voltage solutions found in the literature, subsequently a statistical analysis of the performance, regarding the 40 samples fabricated, is presented. As a typical performance chip, the one with the median temperature coefficient (TC) was chosen, since it is, commonly, the most critical figure of merit for voltage reference circuits. However, as will be clear from statistical analysis, those typical results are very close to the average ones.

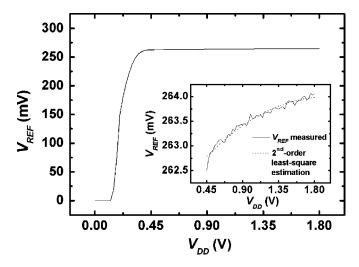

In Fig. 4, the  $V_{\rm REF}-V_{\rm DD}$  characteristic at room temperature is reported. The circuit starts working properly with  $V_{\rm DD}=0.45~\rm V$ . In the supply voltage range from 0.45 V to 1.8 V a mean reference voltage of 263.5 mV is generated. In this supply voltage range, the output voltage changes at most by 1.6 mV, thus leading to a line sensitivity of 0.440%/V.

The current consumption changes slightly with  $V_{\rm DD}$ , at room temperature it varies from 7.0 nA to 7.9 nA in the supply voltage range under consideration. Therefore, under the above-mentioned operating conditions, the minimum power

Fig. 3. (a) Chip photo. (b) Layout of the proposed CMOS voltage reference circuit.

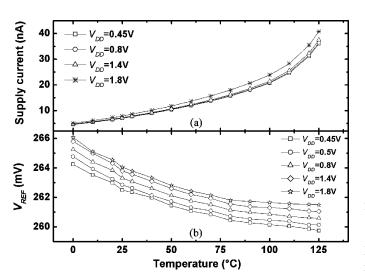

consumption is just 3.2 nW. In Fig. 5(a) the measured values of the current drawn from the power supply, in the temperature range between 0°C and 125°C, are shown. The supply current increases with temperature according to (12), reaching 36.0 nA at  $V_{\rm DD}=0.45~{\rm V@125°C}$ , and 40.8 nA at  $V_{\rm DD}=1.8~{\rm V@125°C}$ .

The reference voltage dependence on temperature is shown in Fig. 5(b). Averaging the  $V_{\rm REF}$  variation on the  $V_{\rm DD}$  range considered, it results  $\approx$ 4.7 mV, leading to an average TC of 142 ppm/°C. From Fig. 5(b), it is clear that the TC is quite independent of  $V_{\rm DD}$ .

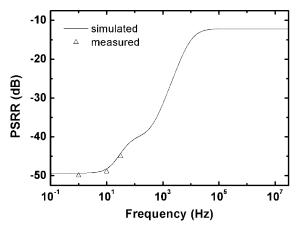

The measured and simulated PSRR values at room temperature, at minimum supply voltage, are illustrated in Fig. 6. Because of the very high value of the output impedance of the circuit, PSRR measurements have been performed by connecting

Fig. 4. Measured output voltage as a function of power supply at room temperature and zoom in the  $V_{\rm DD}$  operating range.

Fig. 5. (a) Supply current versus temperature for different supply voltages. (b) Temperature dependence of the generated reference voltage for different supply voltages.

the voltage reference output to a CMOS operational amplifier (TLC2201). Indeed, from post-layout simulations, the evaluated output impedance ( $Z_{\rm OUT}$ ) is 55 M $\Omega//0.3$  pF, higher than typical input impedance of commercial oscilloscope probes. The opamp input capacitance ( $C_{\rm IN}$ ) is about 20 pF (considering packaged amplifiers, generally,  $C_{\rm IN}$  does not go below 10 pF) and forms a low-pass filter with  $Z_{\rm OUT}$  having a -3 dB frequency of 144 Hz. For this reason, the high output impedance of the circuit did not allow an accurate measurement of the PSRR for frequencies above 30 Hz. However, from Fig. 6, it is clear that the simulation results are in good agreement with the measurements obtained.

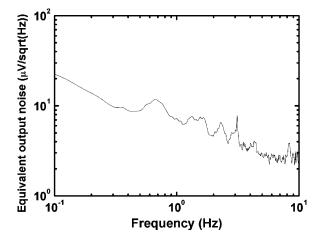

The measured equivalent output noise amplitude, without filtering capacitors, is shown in Fig. 7. At 10 Hz its value is  $2.3 \,\mu\text{V}/\sqrt{\text{Hz}}$  and the root mean square voltage noise, measured in a bandwidth from 0.1 Hz to 10 Hz, is 22.0  $\mu\text{V}$ .

It is clear that the designed circuit can only drive high impedance loads such as the capacitive loads offered by

Fig. 6. PSRR at room temperature, for  $V_{\rm DD} = 0.45~{\rm V}$ .

Fig. 7. Measured equivalent output noise  $(V/\sqrt{Hz})$  from 0.1 Hz to 10 Hz.

MOSFET-based comparators or buffers. Most often voltage references do not drive directly loads, as in the case of voltage supply circuits [21].

Table III summarizes the measurement results of the typical performance chip and compares them with the best low voltage, low power voltage references found in literature, implemented in standard CMOS process. From the comparison it results that the proposed configuration achieves the lowest supply voltage and current dissipation, thus leading to at least a  $10\times$  reduction in power consumption with respect to the other proposed solutions. Moreover, those results are obtained while preserving competitive line sensitivity, temperature coefficient, PSRR and area occupation.

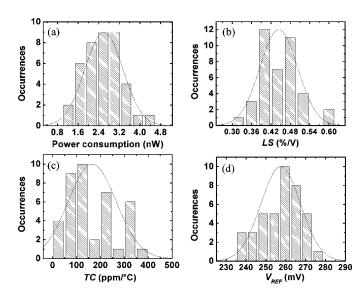

Measurements were carried out on a set of 40 samples. In Table IV, a brief summary of the statistical analysis results, reporting most relevant figures of merit, is given. In particular mean  $(\mu)$  and standard deviation  $(\sigma)$  values of the temperature coefficient (TCAVG), the line sensitivity (LS), the power consumption at  $V_{\rm DD}=0.45$  V  $(P_{\rm DISS})$  and the reference voltage  $(V_{\rm REF})$  at room temperature were reported. TCAVG and  $V_{\rm REF}$  refer to the averaged values on the  $V_{\rm DD}$  range considered. In Fig. 8 the distributions of these parameters are shown. To our knowledge, detailed statistical information about key performance indicators like TC, LS or power consumption, are not given in works concerning low power voltage references. For

|                                         | Proposed configuration    | Ref. [14]                       | Ref. [15]        | Ref. [8]               | Ref. [12]   | Ref. [13]                           | Ref. [11]               |

|-----------------------------------------|---------------------------|---------------------------------|------------------|------------------------|-------------|-------------------------------------|-------------------------|

| Technology                              | 0.18μm CMOS               | 0.35μm CMOS                     | 0.18μm CMOS      | 0.18μm CMOS            | 0.35μm CMOS | 0.35μm CMOS                         | 0.6μm CMOS              |

| Supply voltage (V)                      | 0.45 to 2                 | 0.9 to 4                        | 0.6 to 2.3       | 0.85 to 2.5            | 1.4 to 3    | 1.1 to 4                            | 1.4 to 3                |

| Supply current (µA)  @ room temperature | 0.007@0.45V<br>0.008@1.8V | 0.040@0.9V<br>0.055@4V          | <0.040@0.7V<br>- | 3.882@0.85V<br>average | 0.2143@1.4  | ~0.021@1.1V<br>~0.024@4V            | <9.7                    |

| V <sub>REF</sub> (mV)                   | 263.5                     | 670                             | ~220             | 221                    | 745±25      | 96.6±4.0 vers-1<br>108.9±3.1 vers-2 | 309.3±19.26             |

| TC (ppm/°C)                             | 142                       | 10                              | 127              | 194                    | 7           | 11.4 - [-20:80], vers-1             | 36.9                    |

| T range(°C)                             | [0:125]                   | [0:80]                          | [-20:100]        | [-20:120]              | [-20:80]    | 9.2 - [-20:80], vers-2              | [0:100]                 |

| Line Sensitivity<br>(%/V)               | 0.440                     | 0.270                           | ~2.730           | 0.905                  | 0.002       | 0.090, vers-1<br>0.170, vers-2      | 0.083                   |

| PSRR (dB)                               | V <sub>DD</sub> =0.45V    | $V_{DD}\!\!=\!\!0.9 \mathrm{V}$ | -                | -                      | $V_{DD}=2V$ | $V_{DD}=3V$                         | $V_{DD} = 1.4 \text{V}$ |

| Low freq [≤100Hz]                       | -45.0                     | -47                             | -41              | _                      | -45         | <-60                                | -47                     |

| High freq [≥10MHz]                      | ( -12.2 sim.)             | -40                             | -                | -                      | ~ -22@10kHz | <-40                                | -20                     |

| Die area (mm²)                          | 0.0430                    | 0.0450                          | 0.0040           | 0.0238                 | 0.0550      | 0.0189 , vers-1<br>0.0193 , vers-2  | 0.0550                  |

TABLE III

COMPARISON WITH LOW-VOLTAGE LOW-POWER CMOS VOLTAGE REFERENCES

Fig. 8. Distributions of the most relevant figures of merit for the 40 measured samples: (a) Power consumption @25°C and  $V_{\rm DD}=0.45~\rm V$ . (b) Line sensitivity @25°C. (c) Temperature coefficient. (d) Generated voltage reference @25°C.

TABLE IV STATISTICAL ANALYSIS OF PERFORMANCE

| Number of samples                     | 40 from thre | 40 from three separate runs |  |  |

|---------------------------------------|--------------|-----------------------------|--|--|

|                                       | μ            | σ                           |  |  |

| TC <sub>AVG</sub> (ppm/°C)            | 165          | 100                         |  |  |

| LS (%/V) @ 25°C                       | 0.444        | 0.058                       |  |  |

| P <sub>diss</sub> (nW) @ 0.45V & 25°C | 2.6          | 0.7                         |  |  |

| V <sub>REF</sub> (mV) @ 25°C          | 257.5        | 10.0                        |  |  |

this reason it was not possible to compare the statistical results in detail.

The mean power consumption at the minimum  $V_{\rm DD}$  and at room temperature is 2.6 nW and it remains lower than 5 nW in the worst case (see Fig. 8(a)). However, even in that case,

the proposed circuit continues to achieve the lowest power consumption, considering that the best low power solutions reported in literature do not go below 23 nW [13].

The line sensitivity distribution, in the  $V_{\rm DD}$  range from 0.45 V to 1.8 V, is shown in Fig. 8(b) and the mean value is 0.444%/V. It varies from a minimum value of 0.329%/V to a maximum value of 0.606%/V.

The best  $TC_{AVG}$  is 39 ppm/°C, which means an average variation of the output voltage of 1.2 mV in the temperature range from 0°C to 125°C. The worst  $TC_{AVG}$  (357 ppm/°C), instead, gives an average variation of about 12 mV. From Fig. 8(c) it is evident that the TC is the quantity with the largest dispersion, indeed, the coefficient of variation  $\sigma/\mu$  is  $\approx$ 61%. The temperature coefficient is a very sensitive parameter, in [6] a 4-bit trimming network is used to optimize it, by changing resistor values after fabrication.

Fig. 8(d) shows the distribution of  $V_{\rm REF}$  at room temperature. The  $\sigma/\mu$  is 3.9%, such spread in reference voltage is higher in the proposed circuit than when using BGRs, e.g., in [22] the  $\sigma/\mu$  is around 1.5%. However, the proposed solution exhibits a power consumption and a minimum supply voltage significantly lower compared to bandgap-like circuits.

#### VI. CONCLUSION

An ultra low voltage, extremely low power voltage reference circuit fabricated in the UMC 0.18-\$\mu m\$ CMOS process, is presented. The circuit works with all transistors in subthreshold operation, thus allowing a remarkable reduction of minimum supply voltage and power consumption. In this sense, the proposed solution represents a significant advance in low power low voltage reference circuit design: the power dissipation is only 2.6 nW, which is about one order of magnitude lower than that of the best results found in the literature, and the minimum supply voltage for correct operation falls to 0.45 V. In addition, a temperature compensation technique and a simple model for line sensitivity prediction in subthreshold-operated voltage reference circuits is presented and demonstrated. The extremely low power and low voltage features of the proposed circuit make

it very attractive for ultra low power battery-operated electronic applications.

#### ACKNOWLEDGMENT

The authors wish to thank S. Pierro and G. Staino for technical support.

#### REFERENCES

- M. Tavakoli, L. Turicchia, and R. Sarpeshkar, "An ultra-low-power pulse oximeter implemented with an energy-efficient transimpedance amplifier," *IEEE Trans. Biomed. Circuits Syst.*, vol. 4, no. 1, pp. 27–38, Feb. 2010.

- [2] E. O. Torres and G. A. Rincón-Mora, "A 0.7-μm BiCMOS Electrostatic Energy-Harvesting System IC," *IEEE J. Solid-State Circuits*, vol. 45, no. 2, pp. 483–496, Feb. 2010.

- [3] H. Banba, H. Shiga, A. Umezawa, T. Miyaba, T. Tanzawa, S. Atsumi, and K. Sakui, "A CMOS bandgap reference circuit with sub-1-V operation," *IEEE J. Solid-State Circuits*, vol. 34, no. 5, pp. 670–674, May 1999.

- [4] H. Neuteboom, B. M. J. Kup, and M. Janssens, "A DSP-based hearing instrument IC," *IEEE J. Solid-State Circuits*, vol. 32, no. 11, pp. 1790–1806, Nov. 1997.

- [5] K. N. Leung and P. K. T. Mok, "A sub-1-V 15 ppm/°C CMOS bandgap voltage reference without requiring low threshold voltage device," *IEEE J. Solid-State Circuits*, vol. 37, no. 4, pp. 526–530, Apr. 2002.

- [6] J. Doyle, Y. J. Lee, Y.-B. Kim, H. Wilsch, and F. Lombardi, "A CMOS subbandgap reference circuit with 1-V power supply voltage," *IEEE J. Solid-State Circuits*, vol. 39, no. 1, pp. 252–255, Jan. 2004.

- [7] B. K. Ahuja, H. Vu, C. A. Laber, and W. H. Owen, "A very high precision 500-nA CMOS floating-gate analog voltage reference," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2364–2372, Dec. 2005.

- [8] P.-H. Huang, H. Lin, and Y.-T. Lin, "A simple subthreshold CMOS voltage reference circuit with channel-length modulation compensation," *IEEE Trans. Circuits Syst. II, Expr. Briefs*, vol. 53, no. 9, pp. 882–885, Sep. 2006.

- [9] G. Giustolisi, G. Palumbo, M. Criscione, and F. Cutri, "A low-voltage low power voltage reference based on subthreshold MOSFETs," *IEEE J. Solid-State Circuits*, vol. 38, no. 1, pp. 151–154, Jan. 2003.

- [10] I. Akita, K. Wada, and Y. Tadokoro, "A 0.6-V dynamic biasing filter with 89-dB dynamic range in 0.18-μm CMOS," *IEEE J. Solid-State Circuits*, vol. 44, no. 10, pp. 2790–2799, Oct. 2009.

- [11] K. N. Leung and P. K. T. Mok, "A CMOS voltage reference based on weighted  $\Delta V_{\rm GS}$  for CMOS low-dropout linear regulators," *IEEE J. Solid-State Circuits*, vol. 37, no. 1, pp. 146–150, Jan. 2003.

- [12] K. Ueno, T. Hirose, T. Asai, and Y. Amemiya, "A 300 nW, 15 ppm/°C, 20 ppm/V CMOS voltage reference circuit consisting of subthreshold MOSFETs," *IEEE J. Solid-State Circuits*, vol. 44, no. 7, pp. 2047–2054, Jul. 2009.

- [13] W. Yan, W. Li, and R. Liu, "Nanopower CMOS sub-bandgap reference with 11 ppm/°C temperature coefficient," *Electron. Lett.*, vol. 45, no. 12, pp. 627–629, Jun. 2009.

- [14] G. De Vita and G. Iannaccone, "A sub-1-V, 10 ppm/°C, nanopower voltage reference generator," *IEEE J. Solid-State Circuits*, vol. 42, no. 7, pp. 1536–1542, Jul. 2007.

- [15] H. Wang and Q. Ye, "A CMOS voltage reference without resistors for ultra-low power applications," in *Proc. 7th Int. Conf. ASIC 2007 (ASICON'07)*, Oct. 22–25, 2007, pp. 526–529.

- [16] I. M. Filanovsky and A. Allam, "Mutual compensation of mobility and threshold voltage temperature effects with applications in CMOS circuits," *IEEE Trans. Circuits Syst. I, Fund. Theory Appl.*, vol. 48, no. 7, pp. 876–884, Jul. 2001.

- [17] F. Maloberti, Analog Design for CMOS VLSI Systems. Boston, MA: Kluwer Academic, 2001.

- [18] S. G. Narendra and A. Chandrakasan, Leakage in Nanometer CMOS Technologies. New York: Springer, 2006.

- [19] A. Hastings, The Art of Analog Layout. Englewood Cliffs, NJ: Prentice-Hall, 2001.

- [20] B. Razavi, Design of Analog CMOS Integrated Circuits. New York: McGraw Hill, 2001.

- [21] M. Oljaca and B. Baker, "How the voltage reference affects ADC performances, Part 2," *Analog Application J.* 2009, Texas Instruments Inc. [Online]. Available: http://www.ti.com/aaj

- [22] V. Gromov, A. J. Annema, R. Kluit, J. L. Visschers, and P. Timmer, "A radiation hard bandgap reference circuit in a standard 0.13 μm CMOS technology," *IEEE Trans. Nucl. Sci.*, vol. 54, no. 6, pp. 2727–2733, Dec. 2007.

**Luca Magnelli** received the B.S.E.E. and M.S.E.E. degrees from the University of Calabria, Rende, Italy, in 2004 and 2006, respectively. He is currently working toward the Ph.D. degree at the University of Pisa, Italy.

From March 2007 to August 2008, he worked as informative systems analyst on technologies for air traffic management with Techno Sky S.r.l., an ENAV company. Since October 2008, he has been with the Department of Electronics, Computer and System Sciences (DEIS), University of Calabria,

working on subthreshold analog integrated circuits, with particular focus on voltage references and op amps. His research interests are in ultra-low power, low voltage CMOS circuits.

**Felice Crupi** received the M.S. degree in electronic engineering from the University of Messina, Messina, Italy, in 1997, and the Ph.D. degree from the University of Firenze, Firenze, Italy, in 2001.

Since 2002, he has been with the Dipartimento di Elettronica, Informatica e Sistemistica, Università della Calabria, Rende, Italy, as an Associate Professor of electronics. Since 1998, he has been a repeat Visiting Scientist with the Interuniversity Micro-Electronics Center (IMEC), Leuven, Belgium. In 2000, he was a Visiting Scientist with the

IBM Thomas J. Watson Research Center, Yorktown Heights, NY. In 2006, he was a Visiting Scientist with the Universitat Autonoma de Barcelona, Barcelona, Spain. His main research interests include reliability of CMOS devices, modeling and simulation of CMOS devices, electrical characterization techniques for solid state electronic devices, the design of ultra low noise electronic instrumentation and the design of extremely low power CMOS circuits. He has authored and coauthored more than 70 papers published in peer-reviewed journals and more than 50 papers published in international conference proceedings. His publications have been cited more than 650 times and his h-index is equal to 14 (Scopus's source). He serves as a reviewer for leading journals and conferences in the field of electronic devices. He has been the Coordinator of research projects at national and international level.

**Pasquale Corsonello** (M'97) was born in 1964. He received the Master degree in electronics engineering from the University of Naples, Italy, in 1988.

He joined the Institute of Research on Parallel Computer System (IRSIP) of National Council of Research of Italy, working on the design and modeling of electronic transducers for high precision measurement. In 1992, he joined the Department of Electronics, Computer Sciences and Systems, University of Calabria, Italy, where he was involved in application specific IC design. In 1997, he joined

the Department of Electronics Engineering and Applied Mathematics of the University of Reggio Calabria. Currently, he is an Associate Professor of electronics at the Department of Electronics Computer Science and Systems of the University of Calabria, Rende, Italy. His main research interests are in high performance circuits, reconfigurable computing and VLSI design.

Calogero Pace was born in Palermo, Italy, in 1965. He received the degree in electronic engineering in 1990 from the University of Palermo and, in 1994, the Doctoral degree in electronic engineering, computer science and telecommunications from the same university.

In 1996 he joined the University of Messina as an Assistant Professor and in 2002 he moved to the University of Calabria, where he is currently an Associate Professor of electronics. During his career, he has contributed to research lines regarding thin film

deposition techniques, design of devices based on their properties, 2-D and 3-D microlithographic patterning on metals and dielectrics, characterization of advanced MOSFET such as multiple gate (FinFET) and high mobility (Ge). He is currently involved in research projects on: design of low noise electronic instrumentation dedicated to wafer-level characterization of electronic devices; development of multisensor systems using advanced algorithms (Support Vector Machine) for "Electronic Nose" applications; reliability of power MOSFET under space radiation conditions; He has been the Coordinator of the Italy–Israel international project RHESSA on the radiation hardness of electronic devices and systems for space applications. He is author of about 90 scientific works, 49 of which were published in refereed journals, and two patents. He is Associate Editor-in-Chief of the *International Journal of Engineering and Industries*.

**Giuseppe Iannaccone** (M'98–SM'10) received the M.S. and Ph.D. degrees in electrical engineering from the University of Pisa, Pisa, Italy, in 1992 and 1996, respectively.

In 1996, he took a permanent position as a Researcher with the Italian National Research Council, and in the same year, he obtained a faculty position at the Electrical Engineering Department, University of Pisa, as an Assistant Professor, where he has been an Associate Professor of electronics since January 2001. His interests include transport and noise in

nanoelectronic and mesoscopic devices, development of device modeling and TCAD tools, and the design of extremely low-power circuits and systems for RFID and ambient intelligence scenarios. He has authored and coauthored more than 130 papers published in peer-reviewed journals and more than 90 papers in proceedings of international conferences.

Dr. Iannaccone has coordinated several European and national projects involving multiple partners and has acted as the Principal Investigator in several research projects funded by public agencies at the European and national levels and by private organizations. He is on the technical committee of several international conferences and serves as a Referee for leading journals in the fields of condensed-matter physics, device electronics, and circuit design.