# A 2-D Analytical Model for Double-Gate Tunnel FETs

Mahdi Gholizadeh and Seyed Ebrahim Hosseini

*Abstract*— This paper presents a 2-D analytic potential model for double-gate (DG) tunnel field effect transistors (TFETs) by solving the 2-D Poisson's equation. From the potential profile, the electric field is derived and then the drain current expression is extracted by analytically integrating the band-to-band tunneling generation rate over the tunneling region. The model well predicts the potential, subthreshold swing (SS), and transfer and output characteristics of DG TFETs. We analyze the dependence of the tunneling current on the device parameters by varying the gate oxide dielectric constant, gate oxide thickness, body thickness, channel length and channel material and also demonstrate its agreement with TCAD simulation results. The SS which describes the switching behavior of TFETs, is derived from the current expression. The comparisons show that the SS of our model well coincides with that of simulations.

*Index Terms*—Analytical model, band-to-band tunneling (BTBT), BTBT generation rate, double-gate (DG) tunnel field effect transistor (TFET), electric field, mobile charge, Poisson's equation, subthreshold swing (SS).

# I. INTRODUCTION

**T** HAS been highlighted that increasing power density is a challenge for continued MOSFET scaling, due to nonscalability of subthreshold swing (SS). The SS of a MOSFET is limited to 60 mV/decade, which causes the leakage current to increase. One of the promising devices to replace the MOSFET for lowpower applications is the tunnel field effect transistor (TFET), which has demonstrated the potential to surmount the SS limit of MOSFETs [1]–[5]. The operation principle of the TFETs relies on the band-to-band tunneling (BTBT) of electrons, so that they are able to operate as steeper switches at lower supply voltages [6].

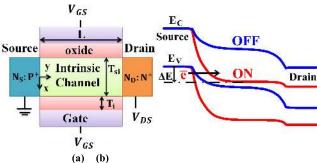

The cross-sectional view of an n-type double-gate (DG) TFET is shown in Fig. 1(a). The energy band profile in the OFF and ON-state is shown in Fig. 1(b). When a positive gate voltage is applied, the conduction band of the channel goes down and a sufficiently high lateral electric field is created at the source-channel junction. This electric field forces the electrons to tunnel from the occupied valence-band states of the source to the unoccupied conduction-band states of the channel.

The authors are with the Department of Electrical Engineering, Ferdowsi University of Mashhad, Mashhad 91779-48974, Iran (e-mail: mahdi.gholizadeh@stu.um.ac.ir; ehosseini@um.ac.ir).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2014.2313037

V<sub>GS</sub> (a) (b) Fig. 1. (a) Schematic diagram of a symmetric DG n-TFET with x-y coordinates. (b) Energy band profile of an n-TFET in the OFF and ON state.

$\Delta E$  is the energy pass window between  $E_{V,\text{SOURCE}}$  and  $E_{C,\text{CHANNEL}}$ .

The performance of TFETs has been simulated using 2-D TCAD simulations [1]–[6]. However, a physics-based analytical model is essential for better understanding of the device operation and facilitates compact modeling for circuit-level studies. It is also useful to obtain fast results.

Several analytical studies on TFETs have been carried out in [7]-[19]. Some 1-D analytical models without considering the impact of the drain voltage have derived the drain current [7]–[9]. Many 2-D studies on TFET modeling analytically calculate the tunneling generation rate using 2-D electric field, but the tunneling current is computed by numerically integrating over the volume of the device [10]-[13]. In some pseudo-2-D analytical models [14], [15], the tunneling current has analytically been derived. They have assumed that the electric field is constant over both the tunneling distance (along the channel) and depth of the device (perpendicular to the channel) in their models, whereas simulations and different analytical models such as [10] and [12] demonstrate that the distribution of the electric field is nonuniform in the channel. In a different method in [16], Landauer approach is used to derive the dc characteristics of TFETs. In this model, the width of the energy pass window  $\Delta E$  [Fig. 1(b)] is considered to have a linear relationship with the gate voltage, but in fact increasing the gate voltage leads to a rise in the voltage drop across the gate oxide. Therefore, increasing of the gate voltage leads to less increase in the width of the energy pass window  $(\Delta E)$ .

In this paper, we develop a 2-D analytical model to derive analytical expressions for different electrical parameters of DG TFETs i.e., potential profile, SS, and transfer and output characteristics. In our calculations, the influences of the mobile

0018-9383 © 2014 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Manuscript received May 11, 2013; revised December 19, 2013, February 4, 2014, and March 12, 2014; accepted March 18, 2014. Date of current version April 18, 2014. The review of this paper was arranged by Editor M. Ieong.

charges on the potential profile and the drain bias on the current are considered. The model also predicts the impacts of structural parameters which is useful to provide a design insight. This paper is organized as follows. In Section II the potential profile and lateral electric field are derived using fully 2-D solution of the Poisson's equation. In Section III using Kane's model, an analytical expression for the current is extracted by integrating the BTBT generation rate over the tunneling region. Then, from the current expression, the SS is derived. The analytic model is validated by comparing it with TCAD simulation results for different sets of parameters in Section IV.

# II. 2-D POISSON'S EQUATION SOLUTION

In this section, an accurate solution to the Poisson's equation with considering the mobile charge term is presented. The structure of the DG TFET is shown in Fig. 1(a). The Poisson's equation in the channel is written as

$$\frac{\partial^2 \psi}{\partial x^2} + \frac{\partial^2 \psi}{\partial y^2} = \frac{q}{\varepsilon_{\rm si}} n_i \exp\left(\frac{\psi - V}{V_t}\right) \tag{1}$$

where  $\psi(x, y)$  is the electrostatic potential in the intrinsic channel,  $\varepsilon_{si}$  is the permittivity of the silicon,  $n_i$  is the intrinsic carrier density,  $V_t$  is the thermal voltage and V is the electron quasi-Fermi potential. According to [2], the electrostatic potential using superposition principle will be written as

$$\psi(x, y) = v(x) + \psi_1(x, y)$$

(2)

where v(x) is the solution of 1-D Poisson's equation

$$\frac{\partial^2 v}{\partial x^2} = \frac{q}{\varepsilon_{\rm si}} n_i \exp\left(\frac{v - V}{V_t}\right). \tag{3}$$

As described in [21], v(x) can be obtained by twice integrating (3)

$$v(x) = V - 2V_t \ln\left(\frac{T_{\rm si}}{2\beta}\sqrt{\frac{qn_i}{2\varepsilon_{\rm si}V_t}}\cos\left(\frac{2\beta}{T_{\rm si}}x\right)\right). \tag{4}$$

For a given  $V_{GS}$ ,  $\beta$  can be solved from

$$\frac{V_{\rm GS} - \Delta \phi - V}{2V_t} - \ln\left(\frac{2}{T_{\rm si}}\sqrt{\frac{2\varepsilon_{\rm si}V_t}{qn_i}}\right)$$

$$= \ln\beta - \ln(\cos(\beta)) - \frac{2\varepsilon_{\rm si}T_i}{\varepsilon_i T_{\rm si}}\beta \tan(\beta) \quad (5)$$

where  $\Delta \phi$  is work function difference between the gate electrode and the semiconductor and  $\varepsilon_i$  is the permittivity of the insulator. Since the current flows mainly along the channel from the source to the drain, the electron quasi-Fermi potential is almost constant in x-direction and varies only in y-direction [21]. For DG-MOSFETs, V is assumed to be constant in the channel direction except at the end of channel where it reaches  $V_{\text{DS}}$  [22]. Similar to MOSFETs, TFETs simulations demonstrate that V in the channel length direction stays constant (equal to  $V_{\text{DS}}$ ) except at the beginning of the channel. This causes v(x) to be nearly constant in the y-direction except near the source junction.  $\psi_1(x, y)$  is the solution to the 2-D Laplace equation

$$\frac{\partial^2 \psi_1}{\partial x^2} + \frac{\partial^2 \psi_1}{\partial y^2} = 0.$$

(6)

The solution of the Laplace equation is given by

$$u_1(x, y) = u_L(x, y) + u_R(x, y).$$

(7)

where  $u_R$  and  $u_L$  can be written as  $u_R = \sum_{n=1}^{\infty} u_{Rn}(x, y)$ and  $u_L = \sum_{n=1}^{\infty} u_{Ln}(x, y)$  where  $u_{Rn}(x, y)$  and  $u_{Ln}(x, y)$  are Eigen functions that are obtained as follows [23]:

$$u_{Rn}(x, y) = c_n \frac{\sinh(\pi y/\lambda_n)}{\sinh(\pi L/\lambda_n)} \sin\left(\frac{n\pi}{2} + \frac{\pi x}{\lambda_n}\right)$$

(8)

$$u_{Ln}(x, y) = b_n \frac{\sinh\left(\pi (L - y)/\lambda_n\right)}{\sinh(\pi L/\lambda_n)} \sin\left(\frac{n\pi}{2} + \frac{\pi x}{\lambda_n}\right).$$

(9)

where  $\lambda_n$  are Eigen values which are obtained from

$$\varepsilon_{\rm si} \tan\left(\frac{\pi T_i}{\lambda_n}\right) = \varepsilon_i \tan\left(\frac{n\pi}{2} - \frac{\pi T_{\rm si}}{2\lambda_n}\right).$$

(10)

According to [23], we obtain the first-order coefficients as

$$b_{1} = \frac{2\lambda_{1}^{2}\tan(\pi T_{i}/\lambda_{1})\sin(\pi T_{\text{si}}/2\lambda_{1})}{\pi^{2}T_{i}\left(\frac{T_{\text{si}}}{2} + \frac{\sin(\pi T_{\text{si}}/\lambda_{1})}{\sin(2\pi T_{i}/\lambda_{1})}T_{i}\right)}(\varphi_{\text{SC}} - V_{\text{GS}} + \Delta\phi)$$

(11)

$$c_{1} = \frac{\sin(\pi T_{\rm si}/2\lambda_{1})}{\left(\frac{T_{\rm si}}{2} + \frac{\sin(\pi T_{\rm si}/\lambda_{1})}{\sin(2\pi T_{i}/\lambda_{1})}T_{i}\right)} \times \left(\frac{-4V_{t}\lambda_{1}}{\pi}\ln(\cos(\beta_{d})) - \frac{2\lambda_{1}^{2}}{\pi^{2}}\frac{\upsilon\left(\frac{T_{\rm si}}{2}\right) - \varphi_{\rm DC}}{T_{i}}\tan(\pi T_{i}/\lambda_{1})\right)$$

(12)

where  $\varphi_{SC}$  and  $\varphi_{DC}$  are built-in potentials at the source and drain junctions, respectively. For a given  $V_{GS}$ ,  $\beta_d$  is obtained from (5). For symmetric DG structures, even order coefficients are zero [23]. The expression for the potential in the channel considering the first-order Eigen function is

$$\psi(x, y) = v(x) + \cos(\pi x/\lambda_1) \\ \times \left(\frac{b_1 \sinh(\pi (L-y)/\lambda_1) + c_1 \sinh(\pi y/\lambda_1)}{\sinh(\pi L/\lambda_1)}\right).$$

(13)

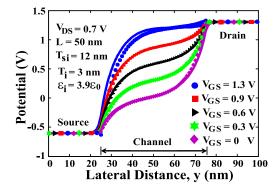

Fig. 2 demonstrates the surface potential under different gate voltages. At high  $V_{GS}$  due to the inversion of the channel, the potential is pinned to the drain voltage. As Fig. 2 shows, the agreement of the model and simulation can be easily seen and the model well captures the effect of the mobile charges.

The lateral electric field  $E_y(x, y)$  is found by differentiating the electrostatic potential expression

$$E_{y}(x, y) = \left(-\frac{\pi}{\lambda_{1}}b_{1}\frac{\cosh\left(\pi\left(L-y\right)/\lambda_{1}\right)}{\sinh(\pi L/\lambda_{1})} + \frac{\pi}{\lambda_{1}}c_{1}\frac{\cosh\left(\pi y/\lambda_{1}\right)}{\sinh(\pi L/\lambda_{1})}\right) \times \cos\left(\pi x/\lambda_{1}\right) \cdot (14)$$

As mentioned earlier, v(x) almost stays constant in the *y*-direction, therefore its derivative is zero. Indeed, for well-scaled devices, the dominant tunneling paths are lateral.

Fig. 2. Surface potential obtained from the model (symbols) and simulations (lines) at different gate voltages. The threshold voltage  $V_{\text{TH}}$  according to the definition in [16] is 0.6 V. ( $\varepsilon_{\text{si}} = 11.8 \varepsilon_0$ ,  $\Delta \phi = 0$ ,  $\varphi_{\text{SC}} = -0.6$  V, and  $\varphi_{\text{DC}} = 0.6$  V).

Therefore, it is reasonable to assume tunneling takes place primarily along the channel length direction, as discussed in [11] and [14]. Therefore, the lateral electric field has only been taken into account in the calculations. The lateral electric field shows a nonuniform behavior along the source-channel junction. It reaches its maximum value at the channel surface and gradually decreases to its minimum value at the middle of channel. This is because the channel underneath the gate is more influenced by the gate voltage than depths of the channel. On the contrary, the highest value of  $E_{y}(x, y)$  in (14) is at the middle of the channel. The reason behind this disagreement is due to considering only the first-order Eigenfunction. Although the first-order Eigenfunction works well to describe the channel potential, as shown in Fig. 2, the higher order terms play a more important role on capturing a sharper potential profile at the source-channel junction, which strongly influence the electric field profile [11]. On the other hand, considering the higher order terms extremely complicates the analytic solution and it is difficult to derive a straightforward expression for the current. Therefore, there is a tradeoff between the precision and simplicity. In order to overcome the tradeoff, we apply the impacts of the higher order terms to the first-order term through Taylor series expansion.

Based on the potential solution, the full expression for the lateral electric field is written as

$$E_{y}(x, y) = \sum_{n=1}^{\infty} \left( -\frac{\pi}{\lambda_{n}} b_{n} \frac{\cosh\left(\pi (L-y)/\lambda_{1}\right)}{\sinh(\pi L/\lambda_{n})} + \frac{\pi}{\lambda_{n}} c_{n} \frac{\cosh\left(\pi y/\lambda_{1}\right)}{\sinh(\pi L/\lambda_{n})} \right) \sin\left(\frac{n\pi}{2} + \frac{\pi x}{\lambda_{n}}\right).$$

(15)

Because of vanishing even order coefficients,  $\sin(n\pi/2 + \pi x/\lambda_n)$  is equivalent to  $\pm \cos(\pi x/\lambda_n)$ . The term  $\cos(\pi x/\lambda_n)$  can be expanded using Taylor series expansion as

$$\cos(\pi x/\lambda_n) = 1 - \frac{(\pi x/\lambda_n)^2}{2!} + \frac{(\pi x/\lambda_n)^4}{4!} - \cdots$$

(16)

Defining  $k_n$  as

$$k_n = -\frac{\pi}{\lambda_n} b_n \frac{\cosh\left(\pi \left(L - y\right)/\lambda_n\right)}{\sinh(\pi L/\lambda_n)} + \frac{\pi}{\lambda_n} c_n \frac{\cosh\left(\pi y/\lambda_n\right)}{\sinh(\pi L/\lambda_n)}$$

(17)

and substituting (16) and (17) into (15), we obtain

$$E_{y}(x, y) = (k_{1} - k_{3} + k_{5} - \cdots) + (-k_{1}(\pi/\lambda_{1})^{2} + k_{3}(\pi/\lambda_{3})^{2} - k_{5}(\pi/\lambda_{5})^{2} + \cdots)\frac{x^{2}}{2!} + (k_{1}(\pi/\lambda_{1})^{4} - k_{3}(\pi/\lambda_{3})^{4} + k_{5}(\pi/\lambda_{5})^{4} - \cdots)\frac{x^{4}}{4!} + \cdots$$

(18)

Solving (10) results in  $\lambda_1/\lambda_n \sim n$  [23] Therefore (18) becomes

$$E_{y}(x, y) = (k_{1} - k_{3} + k_{5} - \dots) \times \left(1 + \left(\frac{\pi}{\lambda_{1}}\right)^{2} \frac{x^{2}}{2!} \times \left(\frac{-k_{1} + 9k_{3} - 25k_{5} + \dots}{k_{1} - k_{3} + k_{5} - \dots}\right) + \left(\frac{k_{1} - 81k_{3} + 625k_{5} - \dots}{k_{1} - k_{3} + k_{5} - \dots}\right) \times \left(\frac{\pi}{\lambda_{1}}\right)^{4} \frac{x^{4}}{4!} + \dots\right) (19)$$

Using a proper fitting parameter N, (19) can be approximated as the following expression:

$$E_{y}(x, y) = Nk_{1}\left(1 + \frac{\omega_{1}^{2}x^{2}}{2!} + \frac{\omega_{2}^{4}x^{4}}{4!} + \cdots\right) \cong Nk_{1}\cosh(\omega_{1}x)$$

(20)

where  $\omega_1$  can be approximated as  $\omega_1 = \pi/\lambda_1$  Therefore the lateral electric field is expressed as

$$E_{y}(x, y) = N\left(-\frac{\pi}{\lambda_{1}}b_{1}\frac{\cosh\left(\pi\left(L-y\right)/\lambda_{1}\right)}{\sinh(\pi L/\lambda_{1})} + \frac{\pi}{\lambda_{1}}c_{1}\frac{\cosh\left(\pi y/\lambda_{1}\right)}{\sinh(\pi L/\lambda_{1})}\right)\cosh\left(\frac{\pi}{\lambda_{1}}x\right).$$

(21)

As (21) indicates getting closer to the channel surface, the lateral electric field increases.

# **III. DRAIN CURRENT DERIVATION**

In this section, we obtain analytical expressions for the drain current and SS. The most widely used model to calculate the tunneling current is the Kane model [24], which determines the BTBT generation rate of carrier tunneling from the valence band of the source to the conduction band of the channel, as

$$G_{\rm BTBT} = AE^D \exp\left(-\frac{B}{E}\right)$$

(22)

where E is the electric field; D is 2.5 for the indirect and 2 for the direct tunneling processes; A and B are the tunneling process-dependent parameters. This paper develops an analytical model for indirect tunneling process; however, it can be easily extended to the direct tunneling process. The drain current can be computed as [18]

$$I = q \int AEE_{\text{avg}}^{D-1} \exp\left(-B/E_{\text{avg}}\right) dV$$

(23)

where E is the local electric field and  $E_{avg}$  is the average electric field. In this paper we aim at analytically calculating the tunneling current.

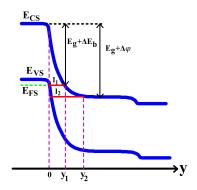

Fig. 3. Energy band diagram along the y-direction during ON-state.  $l_1$  and  $l_2$  are the lengths of the shortest and longest tunnel paths, respectively.

*E* is computed from (21). Since electron tunneling takes place mainly at the source-channel junction, the second term in (21) is negligible and thereby  $E_y$  is written as

$$E_{y}(x, y) = N\left(-\frac{\pi b_{1}}{4\lambda_{1}\sinh(\pi L/\lambda_{1})}\right)\exp\left(\pi (L-y)/\lambda_{1}\right)\exp\left(\frac{\pi}{\lambda_{1}}x\right).$$

(24)

The average electric field can be written as

$$E_{\rm avg} = E_g / (q l_{\rm path}) \tag{25}$$

where  $l_{\text{path}}$  is the length of tunneling path and varies from  $l_1$  to  $l_2$  [Fig. (3)]. Due to high doping concentration, the source depletion region is ignored, therefore  $l_1 = y_1$  and  $l_2 = y_2$ . At  $y = y_1$ , the difference between the source conduction band and channel conduction band is  $E_g + \Delta E_b$ , where  $\Delta E_b = E_{\text{VS}} - E_{\text{FS}}$ . Similarly, at  $y = y_2$ , the difference between the source conduction band reaches  $E_g + \Delta \varphi$ , where  $\Delta \varphi = E_{\text{VS}} - E_{\text{FC}}$ .

Inserting the local and average electric fields in (23) yields

$$I = q \int_{-\frac{T_{si}}{2}}^{\frac{T_{si}}{2}} \int_{y_1}^{y_2} AN\left(-\frac{\pi b_1 \exp\left(\pi L/\lambda_1\right)}{4\lambda_1 \sinh\left(\pi L/\lambda_1\right)}\right) \frac{E_g^{D-1}}{q^{D-1}y^{D-1}}$$

$$\exp\left(-\pi y/\lambda_1\right) \exp\left(\frac{\pi}{\lambda_1}x\right) \exp\left(\frac{-qB}{E_g}y\right) dy dx.$$

(26)

The channel width is 1  $\mu$ m in the model and simulations. In (26), y ranges from  $y_1$  to  $y_2$ , in this interval variation of the exponential term is dominant compared with polynomial term  $(1/y^{D-1})$  [18]. Therefore, we perform integration over exponential term to compute the drain current

$$I = -\frac{qAN E_g^{D-1}}{\left(\frac{qB}{E_g} + \frac{\pi}{\lambda_1}\right)q^{D-1}} \left(-\frac{\pi b_1 \exp\left(\pi L/\lambda_1\right)}{4\lambda_1 \sinh\left(\pi L/\lambda_1\right)}\right)$$

$$\left(\frac{2\lambda_1}{\pi} \left(\exp\left(\frac{T_{\text{si}}\pi}{2\lambda_1}\right) - 1\right)\right) (S(y_2) - S(y_1)) \tag{27}$$

where S(y) is defined as

$$S = \frac{\exp\left(-\left(\frac{qB}{E_g} + \frac{\pi}{\lambda_1}\right)y\right)}{y^{D-1}}.$$

(28)

Due to exponential term in (28) and also  $y_2 > y_1$ , it is straightforward to show  $S(y_1) \gg S(y_2)$ . Ignoring  $S(y_2)$ , it is sufficient to compute  $y_1$ . At  $y_1$ , the channel potential reaches  $(E_g + \Delta E_b)/q$ . Computing  $y_1$  requires inverting potential distribution equation. Since the charge concentration near the source-channel junction is negligible [5], the potential distribution along the *x*-axis can be written as  $v(x) = V_{\text{GS}} - \Delta\varphi$ . Inserting this value in the potential distribution equation and ignoring the second term  $(c_1 \sinh(\pi y/\lambda_1))$  due its small contribution at the source-channel junction,  $y_1$  can be obtained as

$$y_1 = L - \frac{\lambda_1}{\pi} \sinh^{-1} \left( \frac{\frac{E_g + \Delta E_b}{q} + \psi(x, 0) - V_{\text{GS}} + \Delta \phi + V_{\text{eff}}}{b_1 \cos\left(\frac{\pi T_{\text{si}}}{2\lambda_1}\right) / \sinh\left(\frac{\pi L}{\lambda_1}\right)} \right)$$

(29)

where  $V_{\text{eff}}$  takes care of the error introduced with deriving (29),  $0 < V_{\text{eff}} < 0.15$ .

The effects of the drain bias appear at the higher order terms [11]; furthermore, we do not completely consider the impacts of the highorder harmonics in the calculations. Thus, a correction factor (F) is needed to compensate the impact of the drain bias. We employ the correction factor used in [15], but the difference here is that we add  $V_{GS}$  in the denominator of the exponential term in order to avoid the effect of the drain bias at low  $V_{GS}$

$$F = 1 - \frac{2}{\left(1 + \exp\left(\frac{V_{\rm DS}}{V_{\rm GS}}\right)\right)}.$$

(30)

Note that when  $V_{GS}$  tends to be zero, F tends to unity.

Subthreshold swing is an important parameter to describe the switching behavior of transistors. From the current expression it can be expressed as

$$SS = \left(\frac{d \log(I)}{d V_{GS}}\right)^{-1}.$$

(31)

By rewriting (11) as  $b_1 = h(\varphi_{SC} - V_{GS} + \Delta \varphi)$  and neglecting *F* because of its small variations at low gate voltages, the SS is obtained as

$$SS = \ln 10 \left( \frac{1}{V_{GS} - \Delta \phi - \varphi_{SC}} - \left( \frac{B}{E_g} + \frac{\pi}{\lambda_1} + \frac{1.5}{L_1} \right) \frac{dL_1}{dV_{GS}} \right)^{-1}$$

(32)

where  $dL_1/dV_{GS}$  is obtained as

$$\frac{dL_1}{dV_{\rm GS}} = -\frac{\lambda_1 \sinh\left(\frac{\pi L}{\lambda_1}\right)}{\pi h \cos\left(\frac{\pi T_{\rm si}}{2\lambda_1}\right)} \left(\frac{E_g + \Delta E_b + V_{\rm eff}}{(\varphi_{\rm SC} + \Delta \phi - V_{\rm GS})^2}\right) \\ \times \frac{1}{\sqrt{1 + \sinh\left(\frac{\pi (L - L_1)}{\lambda_1}\right)^2}}.$$

(33)

It is observed that unlike MOSFETs, the SS of TFETs is a function of the gate voltage.

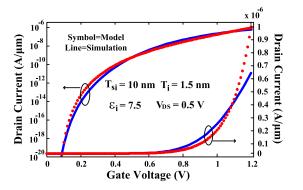

Fig. 4.  $I-V_{GS}$  characteristic. The drain current is plotted on logarithmic (left) and linear (right) scales (L = 50 nm, N = 0.1, and  $\Delta \phi = -0.5$ ).

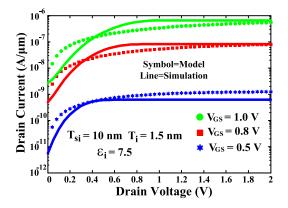

Fig. 5.  $I-V_{\text{DS}}$  characteristics of the DG TFET at different gate voltages (L = 50 nm, N = 0.1, and  $\Delta \phi = -0.5 \text{ V}$ ).

#### IV. MODEL VALIDATION

In this section we validate the proposed model by comparing it with 2-D TCAD simulations. We evaluate the efficacy of the model by varying the gate oxide dielectric constant, gate oxide thickness, body thickness channel length and channel material. We employed the nonlocal tunneling model to simulate TFET current. The source and drain doping concentrations are  $10^{20}$  cm<sup>-3</sup> and  $10^{18}$  cm<sup>-3</sup>, respectively, and the channel is intrinsic. The default parameters for the Kane model are  $A = 4 \times 10^{14} \text{ cm}^{-1/2} \text{V}^{-5/2} \text{s}^{-1}$  and  $B = 1.9 \times 10^7 \text{ V/cm}$  [25]. Fig. 4 shows the  $I-V_{GS}$  characteristic of a DG TFET calculated by the model and simulations. It is observed that our model well captures both the subthresold and superthreshold currents. Fig. 5 shows the output characteristic of the device at different gate voltages. The model predicts the saturation current very well and also it shows a qualitative agreement in the linear regime.

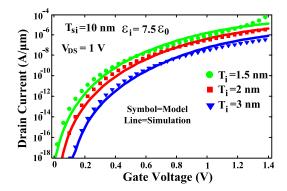

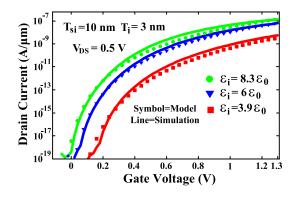

In order to improve the ON-current  $(I_{ON})$  and achieve high ON to OFF current ratios  $(I_{ON}/I_{OFF})$  in TFETs, gate oxide thickness reduction and high-k dielectric materials are usually employed. We investigate the model with different gate oxide thicknesses and gate oxide dielectrics in Figs. 6 and 7. With reducing  $T_i$  and increasing  $\varepsilon_i$ , higher  $I_{ON}$ , steeper subthreshold slope, and higher  $I_{ON}/I_{OFF}$  is achieved [1]. Our model well predicts the changes of  $I-V_{GS}$  characteristics induced by varying  $T_i$  and  $\varepsilon_i$ . The reduction of the bulk capacitive effects also can increase the current which can be obtained by

Fig. 6.  $I-V_{GS}$  characteristics for Si DG TFETs as function of gate oxide thickness. The values of N used for comparisons are 0.1 for  $T_i = 1.5$  nm, 0.1 for  $T_i = 2$  nm and 4 for  $T_i = 3$  nm (L = 50 nm and  $\Delta \phi = -0.6$ ).

Fig. 7.  $I-V_{\rm GS}$  characteristics for Si DG TFETs as function of gate oxide dielectric. The values of N used for comparisons are 4 for  $\varepsilon_i = 3.9\varepsilon_0$ , 4 for  $\varepsilon_i = 6\varepsilon_0$ , 1 for  $\varepsilon_i = 8.3\varepsilon_0$  (L = 50 nm and  $\Delta \phi = -0.7$  V).

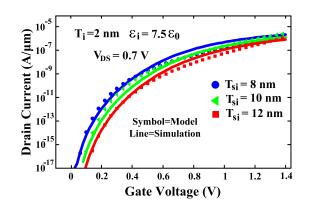

Fig. 8.  $I-V_{GS}$  characteristics for Si DG TFETs as function of body thickness. The values of N used for comparisons are 1 for  $T_{si} = 8 \text{ nm}$ , 1 for  $T_{si} = 10 \text{ nm}$  and 0.1 for  $T_{si} = 12 \text{ nm}$  (L = 50 nm and  $\Delta \phi = -0.6 \text{ V}$ ).

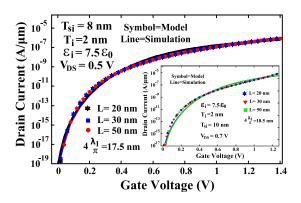

decreasing the body thickness [1], as shown in Fig. 8. We also examined the gate length scaling with the analytical model. The DG TFETs exhibit extremely lower shift in their  $I-V_{GS}$ characteristics, due to short channel effects, than their DG MOSFETs counterparts at the gate lengths longer than four times their natural scaling lengths  $(4\lambda_1/\pi)$  [11]. In Fig. 9 the drain current for two different structures at the gate lengths longer than their  $4\lambda_1/\pi$  have been plotted and the accuracy of our model can be easily seen.

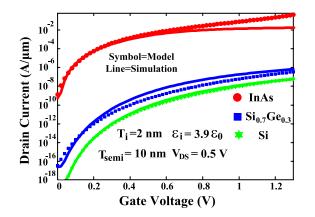

Although in this model we used silicon as the channel material in calculations, we can also apply the model for

Fig. 9.  $I-V_{\text{GS}}$  characteristics for various gate lengths. DG TFETs exhibit lower shift in their  $I-V_{\text{GS}}$  characteristics at gate lengths longer than  $(4\lambda_1/\pi)N = 1$  for both plots  $(\Delta\phi = -0.6 \text{ V})$ .

Fig. 10.  $I-V_{GS}$  characteristic for different semiconductor materials. InAs  $(\Delta \phi = -0.125 \text{ V}, N = 10)$ , Si<sub>0.7</sub>Ge<sub>0.3</sub>  $(\Delta \phi = -0.09 \text{ V} \text{ and } N = 10)$ , and Si  $(\Delta \phi = -0.7 \text{ V} \text{ and } N = 4)$ .  $T_{\text{semi}}$  is the body thickness.

TABLE I SUBTHRESHOLD SWING VALUES AT DIFFERENT GATE VOLTAGES FOR TWO DIFFERENT STRUCTURES

Structure 1:  $T_{si} = 10 \text{ nm}, T_i = 1.5 \text{ nm}, \varepsilon_i = 3.9 \varepsilon_0, \Delta \phi = 0.66 \text{V}, \text{N}=1$

Structure 2:  $T_{si} = 12 nm$ ,  $T_i = 3 nm$ ,  $\varepsilon_i = 7.5 \varepsilon_0$ ,  $\Delta \phi = 0.8$ V, N=1

|                | $V_{GS}(\mathbf{V})$   | 0.0 | 0.1 | 0.2 | 0.3 | 0.4 |

|----------------|------------------------|-----|-----|-----|-----|-----|

| Structure<br>1 | Simulation<br>(mV/dec) | 9.5 | 36  | 59  | 81  | 110 |

|                | Model<br>(mV/dec)      | 10  | 32  | 57  | 84  | 112 |

| Structure<br>2 | Simulation<br>(mV/dec) | 31  | 54  | 74  | 98  | 120 |

|                | Model<br>(mV/dec)      | 26  | 48  | 71  | 96  | 122 |

other materials such as III–V semiconductors. We used InAs and  $Si_{0.7}Ge_{0.3}$ , which have direct and indirect transitions respectively, as alternatives to Si in the model. Fig. 10 shows that the model can be apply for different direct and indirect-bandgap semiconductor materials. When applying the model for direct-bandgap materials the values of *D*, *A*, and *B* are adjusted.

Table I lists the SS calculated by the model and simulations for two different structures. The model well predicts the low subthreshold values (>60 mV/decade) observed in TFETs as well as the dependence of the SS on the gate voltage and shows a good match with simulation results.

### V. CONCLUSION

In this paper, a 2-D analytical model for DG TFETs has been developed. This model takes into account the influences of all the structural parameters, i.e.,  $T_{si}$ ,  $T_i$ ,  $\varepsilon_i$ ,  $\varepsilon_{si}$ , and Ltogether with the biases in the calculations and predicts well the effects of them. We included the mobile charge term in the solution of the Poisson's equation. Comparing the model results for different electrical parameters, i.e., potential profile, BTBT generation rate, SS,  $I-V_{GS}$  and  $I-V_{DS}$  characteristics, with the simulation results shows a good agreement.

## REFERENCES

- K. Boucart and A. M. Ionescu, "Double-gate tunnel FET with high- κ gate dielectric," *IEEE Trans. Electron Devices*, vol. 54, no. 7, pp. 1725–1733, Jul. 2007.

- [2] C.-H. Shih and N. D. Chien, "Sub-10-nm tunnel field-effect transistor with graded Si/Geheterojunction," *IEEE Electron Device Lett.*, vol. 32, no. 11, pp. 1498–1500, Nov. 2011.

- [3] L. Lattanzio, L. D. Micheilis, and A. M. Ionescu, "Complementary germanium electron-hole bilayer tunnel FET for sub-0.5-V operation," *IEEE Electron Device Lett.*, vol. 33, no. 2, pp. 167–169, Feb. 2012.

- [4] A. Mallik and A. Chattopadhyay, "Tunnel field-effect transistors for analog/mixed-signal system-on-chip applications," *IEEE Trans. Electron Devices*, vol. 59, no. 4, pp. 888–894, Apr. 2012.

- [5] A. Mallik and A. Chattopadhyay, "Drain-dependence of tunnel fieldeffect transistor characteristics: The role of the channel," *IEEE Trans. Electron Devices*, vol. 58, no. 12, pp. 4250–4257, Dec. 2011.

- [6] S. H. Kim, S. Agarwal, Z. A. Jacobson, P. Mathue, C. Hu, and T. J. K. Liu, "Tunnel field-effect transistor with raised germanium source," *IEEE Electron Device Lett.*, vol. 31, no. 10, pp. 1107–1109, Oct. 2010.

- [7] N. N. Mojumder and K. Roy, "Band-to-band tunneling ballistic nanowire FET: Circuit-compatible device modeling and design of ultra-low-power digital circuits and memories," *IEEE Trans. Electron Devices*, vol. 56, no. 10, pp. 2193–2201, Oct. 2009.

- [8] W. Vandenberghe, A. Verhulst, G. Groeseneken, B. Soree, and W. Magnus, "Analytical model for a tunnel field-effect transistor," in *Proc. MELECON*, 2008, pp. 923–928.

- [9] M. M. M. Elahi, K. Ahmed, and M. S. Islam, "An improved analytical model of current in tunnel field effect transistor," in *Proc. ICECE*, 2012, pp. 802–805.

- [10] M. G. Bardon, H. P. Neves, R. Puers, and C. V. Hoof, "Pseudotwo dimensional model for double-gate tunnel FETs considering the junctions depletion regions," *IEEE Trans. Electron Devices*, vol. 57, no. 4, pp. 827–834, Apr. 2010.

- [11] L. Liu, D. Mohata, and S. Datta, "Scaling length theory of double-gate interband tunnel field-effect transistors," *IEEE Trans. Electron Devices*, vol. 57, no. 4, pp. 827–834, Apr. 2012.

- [12] M. J. Lee and W. Y. Choi, "Analytical model of single-gate silicon on insulator (SOI) tunneling field effect transistors (TFETs)," *Solid State Electron.*, vol. 63, no. 1, pp. 110–114, Sep. 2011.

- [13] A. Pan, S. Chen, and C. O. Chui, "Electrostatic modeling and insights regarding multigate lateral tunneling transistors," *IEEE Trans. Electron Devices*, vol. 60, no. 9, pp. 2712–2720, Sep. 2013.

- [14] A. Pan and C. O. Chui, "A quasi-analytical model for double-gate tunneling field-effect transistors," *IEEE Electron Device Lett.*, vol. 33, no. 10, pp. 1468–1470, Oct. 2012.

- [15] L. Zhang, J. He, and M. Chan, "A compact model for double-gate tunneling field-effect transistors and its implications on circuit behaviors," in *Proc. IEDM*, 2012, pp. 143–146.

- [16] B. Bhushan, K. Nayak, and V. R. Rao, "DC compact model for SOI tunnel field-effect transistors," *IEEE Trans. Electron Devices*, vol. 59, no. 10, pp. 2635–2642, Oct. 2012.

- [17] L. Zhang, X. Lin, J. He, and M. Chan, "An analytical charge model for double-gate tunnel FETs," *IEEE Trans. Electron Devices*, vol. 59, no. 12, pp. 3217–3223, Dec. 2012.

- [18] A. S. Verhulst, D. Leonelli, R. Rooyackers, and G. Groeseneken, "Drainvoltage dependent analytical model of tunnel field-effect transistors," *J. Appl. Phys.*, vol. 110, no. 2, pp. 024510-1–024510-10, Jul. 2011.

- [19] A. S. Verhulst, B. Soree, D. Leonelli, W. G. Vandenberghe, and G. Groeseneken, "Modeling the single-gate, double-gate, and gate-allaround tunnel field effect transistor," *J. Appl. Phys.*, vol. 107, no. 2, pp. 024518-1–024518-8, Jul. 2010.

- [20] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices. Cambridge, U.K.: Cambridge Univ. Press, 1998.

- [21] Y. Taur, X. Liang, W. Wang, and H. Lu, "A continuous, analytic draincurrent model for DG MOSFETs," *IEEE Electron Device Lett.*, vol. 25, no. 2, pp. 107–109, Feb. 2004.

- [22] Q. Chen, E. M. Harrell, and J. D. Meindl, "A physical shortchannel threshold voltage model for undoped symmetric doublegate MOSFETs," *IEEE Trans. Electron Devices*, vol. 50, no. 7, pp. 1631–1637, Jul. 2003.

- [23] X. P. Liang and Y. Taur, "A 2-D analytical solution for SCEs in DG MOSFETs," *IEEE Trans. Electron Devices*, vol. 51, no. 9, pp. 1385–1391, Sep. 2004.

- [24] E. O. Kane, "Zener tunneling in semiconductors," J. Phys. Chem. Solids, vol. 12, no. 2, pp. 181–188, Jan. 1960.

- [25] ATLAS User's Manual, Silvaco Inc., Santa Clara, CA, USA, 2010.

Seyed Ebrahim Hosseini received the B.Sc. degree in electrical engineering from the Isfahan University of Technology, Isfahan, Iran, the M.Sc. degree from Tarbiat Modarres University, Tehran, Iran, and the Ph.D. degree in electrical engineering from the Sharif University of Technology, Tehran, in 2001. He is currently an Associate Professor of Electronics Engineering with the Ferdowsi University of Mashhad, Mashhad, Iran.

**Mahdi Gholizadeh** received the B.Sc. degree in electrical engineering from the Shahid Chamran University of Ahvaz, Ahvaz, Iran, and the M.Sc. degree in electrical and electronic engineering from the Ferdowsi University of Mashhad, Mashhad, Iran, in 2011 and 2014, respectively.

His current research interests include design, simulation, fabrication, and characterization of ultralowpower devices.