# A 23-GHz Low-Phase-Noise Digital Bang–Bang PLL for Fast Triangular and Sawtooth Chirp Modulation

Dmytro Cherniak, *Student Member, IEEE*, Luigi Grimaldi<sup>®</sup>, Luca Bertulessi<sup>®</sup>, Roberto Nonis, Carlo Samori, *Fellow, IEEE*, and Salvatore Levantino<sup>®</sup>, *Senior Member, IEEE*

Abstract—This paper describes a 23-GHz digital bang-bang phase-locked loop (PLL) fabricated in 65-nm CMOS for millimeter-wave frequency-modulated continuous-wave radars. The presented circuit aims to generate a fast sawtooth chirp signal that grants significant advantages with respect to the more conventional triangular waveform. Such a signal, however, features a very large bandwidth that requires the adoption of a two-point injection scheme. This paper, after intuitively discussing how the nonlinearity of the digitally controlled oscillator affects the accuracy of frequency modulation, presents a novel automatic pre-distortion engine, operating fully in background, which linearizes the tuning characteristic. The 19.7-mA fractional-N PLL having an rms jitter of 213 fs and an in-band fractional spur of -58 dBc is capable of synthesizing fast chirps with 173-MHz/ $\mu$ s maximum slope and an idle time of less than 200 ns after an abrupt frequency step with no over or undershoot.

*Index Terms*—Bang-bang phase detector, digital phase-locked loop (DPLL), frequency-modulated continuous wave (FMCW), nonlinearity, pre-distortion.

### I. INTRODUCTION

**N** EW millimeter-wave (mm-wave) applications, including automotive radars, presence and motion detection, and gesture recognition, are stimulating the development of low-cost radar sensors in CMOS [1]–[4]. The high cutoff frequency of transistors in modern scaled CMOS technologies allows integration of the mm-wave RF transceiver together with a comprehensive digital core required for the sensor DSP. Fig. 1 shows the block diagram of an mm-wave frequencymodulated continuous-wave (FMCW) radar transceiver. Range sensing is based on the measurement of the time-of-flight  $t_d$  of the electro-magnetic wave reflected by an object at distance R from the transceiver:  $t_d = 2R/c$ , where c is the speed of light. In practical applications, direct measurement of  $t_d$  is a costly process, because a difference of tens of picoseconds

Manuscript received May 9, 2018; revised July 24, 2018; accepted August 25, 2018. This paper was approved by Guest Editor Harish Krishnaswamy. (*Corresponding author: Salvatore Levantino.*)

D. Cherniak is with the Dipartimento di Elettronica, Informazione e Biongegneria, Politecnico di Milano, 20133 Milan, Italy, on leave from Infineon Technologies AG, 9500 Villach, Austria.

L. Grimaldi, L. Bertulessi, C. Samori, and S. Levantino are with the Dipartimento di Elettronica, Informazione e Biongegneria, Politecnico di Milano, 20133 Milan, Italy (e-mail: salvatore.levantino@polimi.it).

R. Nonis is with Infineon Technologies AG, 9500 Villach, Austria. Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2018.2869097

Fig. 1. FMCW radar transceiver architecture.

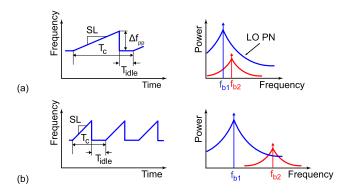

should be sensed to resolve a centimeter resolution. The typical solution is to use a linearly frequency-modulated signal, i.e., a chirp, and sense the frequency difference,  $f_b$ , between transmitted and reflected waves, rather than a time difference, thus significantly reducing the required bandwidth at the baseband (e.g., from 10 GHz to 100 MHz). If the chirp has a slope SL, the receiver detects the beat frequency  $f_b = SL \cdot 2R/c + 2f_v v/c$ , where  $f_v$  is the carrier frequency and v is the relative velocity. The first term in the above equation is proportional to time-of-flight  $t_d$ , while the second term is defined by the Doppler shift. Reducing the period of the chirp  $T_c$  allows faster target identification as well as range and velocity sensing. Moreover, it increases the maximum unambiguous velocity  $\Delta v_{\text{max}} = c/(4f_vT_c)$  [5]. However, as the chirp period decreases, the impact of the idle time (time between two consecutive chirps as shown in Fig. 2) on the overall power efficiency of the system becomes more important as the power of the RF front-end is wasted during the idle time.

Another advantage of fast chirps is related to the multiple-target scenario depicted in Fig. 1, where two different beat frequencies have to be detected. As the difference in the received power from the two objects depends on their relative radar cross section and can be as large as 60 dB [6], the phase noise of the modulator, up-converted around the most powerful tone, can severely degrade the weaker signal. As it is schematically shown in Fig. 2, if the chirp is faster, then the two beat tones will be more separated in frequency, relaxing phase noise requirements.

<sup>0018-9200 © 2018</sup> IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Fig. 2. Modulation signal and power spectrum at IF output in (a) slow-chirp and (b) fast-chirp cases.

Typically, triangular chirps are preferred to sawtooth ones, because at least two slopes (e.g., SL and -SL) are needed to detect both the range and speed of the target. In practice, (N+1) different slopes have to be adopted to cope with an N-target scenario. The adoption of several different slopes obviously decreases the radar power efficiency and increases the design complexity [7], [8]. Sawtooth chirps would instead entail the highest power efficiency, as chirp duration can be maximized for the same slope SL. Speed and N-target detection can be solved if the sawtooth chirp is fast enough to make the Doppler shift negligible within the period  $T_c$ . The detection of targets and respective distances is done within a single chirp by means of a fast Fourier transform (FFT), so called range FFT. While the relative speed of targets can be detected by tracking the phase progression of a single range-FFT bin over a number of chirps [5].

None of the recently published high-performance chirp generators in CMOS [3], [7]-[9] implemented as frequencymodulated phase-locked loops (PLLs) is able to support fast sawtooth modulations. Because of its sharp drop, a sawtooth chirp requires a much wider bandwidth than a triangular one with the same slope and twice the period. This feature does not allow generating the signal by simply modulating the division factor of the PLL that in other respects would be the optimal solution. The reason is that the low-pass transfer function of the PLL usually shows a bandwidth well below the one required, a fact that causes severe *linear* distortion. The problem can be mitigated by injecting the modulation signal in two different points of the PLL, the so-called two-point injection technique [10], and employing some sort of calibration to match the two paths [11]. This aspect has made attractive the adoption of digital PLLs (DPLLs) as frequency modulators [2], [12]-[14]. Unfortunately, large bandwidth is only one of the requirements to achieve a fast linear sawtooth chirp. Nonlinear distortion is the second source of errors in the modulation. For frequency components of the modulation signal lying beyond the PLL bandwidth, the nonlinearity of PLL building blocks generates a distorted modulation even in a PLL with a two-point injection scheme [15]. A fast sawtooth is, clearly, severely affected by this mechanism, since most of its power is typically contained in a spectrum portion well above the PLL bandwidth.

In this paper, we introduce a 23-GHz DPLL for fast chirp generation, in which a wide bandwidth is obtained by

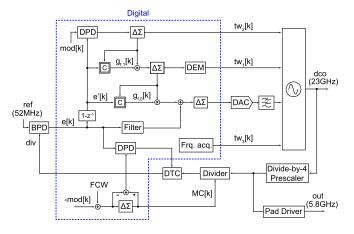

Fig. 3. Frequency modulator based on a DPLL.

Fig. 4. Modulation signal and error in the case of finite bandwidth.

adopting the two-point injection technique, while, at the same time, the nonlinear tuning curve of the digitally controlled oscillator (DCO) is calibrated in background by means of a novel digital predistortion (DPD) algorithm running fully in the background [16]. This paper is organized as follows. Section II describes the PLL modulator. Section III introduces the analysis of the impact of DCO nonlinearity on modulation accuracy, while Section IV describes the novel adaptive DPD scheme and Section V the simulation results. Section VI describes the architecture of the DPLL and the design of building blocks, while measurement results are shown in Section VII. Section VIII draws pertinent conclusions.

## **II. PLL WITH TWO-POINT-INJECTION SCHEME**

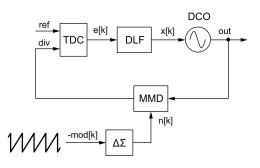

Fig. 3 shows a DPLL-based FMCW modulator, in which the modulation signal mod[k], sampled at reference rate, changes the fractional-N division factor of the PLL, thus varying its output frequency with fine resolution. The output frequency follows the slow variations of mod[k], only within the PLL bandwidth, while the faster components of mod[k] are low-pass filtered by the PLL transfer function. The (linear) distortion of the chirp due to the finite PLL bandwidth is pictorially sketched in Fig. 4, assuming a sawtooth-like mod[k]. The chirp error  $\epsilon_{chirp}$  is defined as

$$\epsilon_{\rm chirp} = \frac{\Delta f_{\rm chirp}}{\Delta f_{pp}} \tag{1}$$

where  $\Delta f_{\text{chirp}}$  if the difference between the ideal and the actual frequency and  $\Delta f_{pp}$  is the peak-to-peak frequency deviation as depicted in Fig. 4. The chirp error changes due to the chirp itself, but an accurate radar systems typically require peak errors below 0.1%.

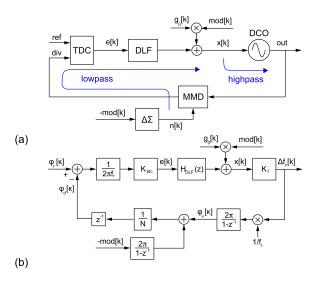

Fig. 5. DPLL-based FMCW modulator. (a) Architecture with two-point injection. (b) Its linearized model.

Of course, the most critical situation occurs after the abrupt frequency step, where the output frequency variation significantly deviates from the ideal one and the PLL settles with finite time constant. To enable fast sawtooth modulation (e.g.,  $T_c < 10 \ \mu$ s), the required PLL bandwidth may range tens or even hundreds of megahertz [15], impossible to achieve with standard crystal references (e.g., at about 40–50-MHz frequency). Not to mention that the PLL is also required to exhibit low phase noise, which is typically achieved at narrow bandwidth. To circumvent this issue and allocate time for PLL settling, a portion of the chirp after the abrupt jump, lasting an idle time  $T_{idle}$ , is not exploited for radar detection. In practice, the part of the usable chirp may shrink down to 50% of  $T_c$  and the power dissipated during the idle time is wasted.

A solution to decouple loop and modulation bandwidth in a PLL is to inject the modulation signal into two points of the loop [10]. Fig. 5(a) recalls the basic idea, where mod[k] directly modulates the tuning port of the DCO, while -mod[k] is injected into the feedback path by modulating the division factor. Fig. 5(b) depicts the linearized model of a PLL with two-point injection technique. Signals  $\phi_p$ ,  $\phi_d$ , and  $\phi_r$  represent the phase of the DCO clock, divided-by-N clock, and reference clock  $f_r$ , respectively. The gain of DCO and time-to-digital converter (TDC) is denoted as  $K_f$  and  $K_{tdc}$ , respectively. From Fig. 5(b), it can be seen that the linear superposition of the transfer functions from both modulation inputs to the variation of the output frequency  $\Delta f_v$  (high pass via the DCO and low pass via the divider) is the desired all-pass one over the whole Nyquist band. In the ideal case of perfect matching between the two transfer functions, it is  $\Delta f_v = \text{mod}[k] \cdot f_r$  where  $\Delta f_v$  is the variation of the output frequency, and  $f_r$  the reference frequency. Moreover, in the two-point topology, mod[k] does not ideally appear at the input of the TDC, because the signal injected into the feedback path cancels out the one injected into the DCO. This property allows the adoption of a single-bit TDC [15].

In practice, the mismatch between the two transfer functions, arising from component spreads, requires some sort of calibration, which can be achieved by multiplying the modulation signal by a digital gain  $g_0$  [2], [17], as shown in Fig. 5. All-pass transfer from mod[k] to output frequency is obtained when the coefficient  $g_0$  is such that  $g_0 \cdot K_f = f_r$ , where  $K_f$ is the DCO gain (or resolution) in [Hz/bit]. Reference [11] employed a least-mean square (LMS) algorithm running in background to automatically calibrate  $g_0$ .

## **III. NONLINEARITY EFFECTS**

Matching between injection paths is mandatory to avoid linear distortion in the two-point modulation scheme. However, the nonlinearity of PLL building blocks, mainly the DCO nonlinear tuning curve, also affects the accuracy of the output frequency modulation. In the presence of nonlinearity, the above-recalled calibration based on a single coefficient, or gain,  $g_0$  is not effective to achieve high accuracy.

A DCO is typically implemented with an *LC* resonator, whose capacitance *C* is divided in several unit capacitances, that can be connected or disconnected from the resonator. Nonlinearity in the DCO frequency characteristic mainly arises from two main sources: The first one is the systematic nonlinear link between the tank capacitance *C* and the output (angular) frequency, i.e.,  $1/\sqrt{LC}$ . The second one is the mismatch among the unit capacitors of the tank, a situation completely equivalent to what happens in digital-toanalog converters (DACs) [18]. In principle, the issue of the  $1/\sqrt{LC}$  nonlinearity could be addressed by properly scaling the capacitors in the coarse bank. However, on the one hand, this would not solve the capacitor mismatch issue (or it might even worsen it) and, on the other hand, would complicate the layout of the DCO.

DCO nonlinearity does not play a major role during standard DPLL operation, since the amount of tuning range exploited is small and the impact of nonlinearity is suppressed by the feedback loop. In other words, the tuning input of the DCO varies within a limited range in lock condition. Instead, when a fast and large modulation is applied, the output frequency has to quickly change along a wide range. Therefore, a large portion of the nonlinear tuning curve is exploited and the loop is unable to mitigate nonlinearity because of the fast operation. This behavior is intrinsic to the two-point scheme, since the high-pass injection path practically operates the DCO as it was in the open-loop condition.

Even if the tank capacitance is a linear function of the digital tuning word (in the case of switched capacitors) or of the tuning voltage (in the case of varactors), the systematic nonlinearity  $1/\sqrt{LC}$  always occurs. Though the nonlinearity of the  $1/\sqrt{(1+x)}$  function is mild and it may be expected to produce negligible errors when the frequency range is a few percent of the center frequency, it becomes problematic in the case of a sawtooth frequency modulation. To get an intuitive picture, let us consider a sawtooth from  $f_{min}$  to  $f_{max}$  frequency.<sup>1</sup> Let us also denote  $K_{f,min}$  and  $K_{f,max}$  the DCO gain evaluated at  $f_{min}$  and  $f_{max}$ , respectively. The calibration

<sup>&</sup>lt;sup>1</sup>This is obtained with a sawtooth digital waveform mod[k] swinging from 0 to  $\Delta f_{pp}/f_r$ , where  $\Delta f_{pp} = f_{max} - f_{min}$ , since the PLL output frequency increases by  $f_r$  each time mod[k] is incremented by one.

Fig. 6. Impact of DCO nonlinearity. (a) Tuning characteristic. (b) Output frequency. (c) Chirp error.

loop estimates a gain  $g_0$  that matches the average gain of the DCO. Along the ramp of the sawtooth, this inaccurate calibration produces negligible effects, because the low-pass injection path is mainly exploited. However, as soon as the modulation undergoes the step variation from  $f_{\text{max}}$  down to  $f_{\text{min}}$  and  $K_f$  abruptly jumps from  $K_{f,\text{max}}$  to  $K_{f,\text{min}}$ , the PLL is momentarily in a condition where the high-pass path is exploited and a mismatch between the two injection path exists. As shown in Fig. 6, the output frequency deviates from the expected shape, and the error is recovered within some time constants of the PLL.<sup>2</sup> The variation of  $K_f$  along the tuning curve is significant. In fact, if x is the tuning word and f the DCO frequency,  $K_f = df/dx = (-f/2C) \cdot (dC/dx)$ , and if the tank capacitance increment (dC/dx) is constant over the tuning range, we get  $K_{f,\text{max}}/K_{f,\text{min}} \approx (f_{\text{max}}/f_{\text{min}})^3$ .

It is difficult to mathematically analyze the impact of DCO nonlinearity on chirp error, as the system is nonlinear. Nevertheless, a simplified mathematical model is useful to gain some additional insights. To this purpose, we can consider a perfectly linear DCO featuring a mismatched gain. Let us denote  $\epsilon_{K_f} = (K_{f,\max}/K_{f,\min} - 1)$  the relative error. Relying on the linear model of the DPLL with two-point injection depicted in 5(b), we can evaluate the *z*-transform of the chirp error  $\epsilon_{\text{chirp}}[k]$  from (1) as a function of the *z*-transform of the modulating signal mod[k]. For this analysis, the DCO gain is altered as  $K_f(1 + \epsilon_{K_f})$ , while the coefficient  $g_0$  is still equal to  $g_0 = K_f/f_r$ . The resulting chirp error is

$$\epsilon_{\text{chirp}}(z) = \frac{\text{mod}(z)[f_r - H_{\text{PLL}}(z)]}{\Delta f_{pp}}$$

$$= \frac{\epsilon_{K_f}}{1 + \epsilon_{K_f}} \cdot \frac{\text{mod}(z) \cdot f_r}{\Delta f_{pp}} \cdot \frac{1}{1 + G_{\text{loop}}(z)} \quad (2)$$

<sup>2</sup>This problem could be avoided if  $g_0$  were adjusted immediately to the new value. This is however impossible, since, to be stable, the LMS loop has to be slower than the PLL response.

where  $H_{\text{PLL}}(z)$  is the z-domain transfer function from the modulation signal mod[k] to the variation of the output frequency  $\Delta f_v$  (ideally a factor  $f_r$ ), the  $G_{\text{loop}}(z)$  is the PLL loop gain, and  $f_r$  the reference frequency [15]. Equation (2) quantifies the sensitivity of the chirp error to the DCO gain perturbation  $\epsilon_{K_f}$ , which models the mismatch between the two injection paths. As the last term in (2) is a frequency response with high-pass shape and bandwidth equal to PLL bandwidth, (2) implies that  $\epsilon_{chirp}[k]$  is obtained after scaling and high-pass shaping mod[k]. In practice, the system is insensitive to the DCO gain mismatch at slow mod[k] variations (within the PLL bandwidth), but it suffers from it at fast mod[k] (outside the PLL bandwidth). When the sawtooth signal abruptly changes as a step function, mod[k] drops from  $\Delta f_{pp}/f_r$  to zero and the DCO exhibits a mismatched gain with error  $\epsilon_{K_f}$ . Therefore, from (2), we can estimate  $\epsilon_{chirp}[k]$  to be a signal with an initial step of height equal to  $\epsilon_{K_f}/(1+\epsilon_{K_f})$ , which is about  $\epsilon_{K_f}$  for small errors, followed by a recovery transient set by the PLL time constant, as schematically shown in Fig. 6. Combining the previous results, the peak error is

$$\epsilon_{\text{chirp,max}} \approx \epsilon_{K_f} \approx \left(\frac{f_{\text{max}}}{f_{\text{min}}}\right)^3 - 1.$$

(3)

Thus, an error of about 15% can be estimated for a frequency deviation of 5%.

The second important source of nonlinearity, the element mismatch, is schematically sketched in Fig. 6 as a step in the DCO characteristic. Following the same argument used in the previous discussion, the error  $\epsilon_{chirp}$  induced in the ramp is too fast and is recovered within some PLL time constants. If  $C_0$  is the tank capacitance before the step corresponding to frequency  $f_v$  and  $\Delta C_{mm}$  is the error of the capacitor that is switched ON, the peak  $\epsilon_{chirp}$  can be approximated as follows:

$$\epsilon_{\rm chirp,max} \approx \frac{\Delta C_{mm}}{2C_0} \cdot \frac{f_v}{\Delta f_{pp}}.$$

(4)

For a relative modulation depth  $\Delta f_{pp}/f_v$  of 5%, a capacitor mismatch of 0.1% would cause an error of about 2%.

## IV. AUTOMATIC DIGITAL PRE-DISTORTION

An adaptive DPD of the modulation signal mod[k] will be adopted to compensate the DCO nonlinearity. If a nonlinear function links the DCO tuning word tw to the output frequency  $f_v$ , the DPD should estimate the inverse of this function (which is assumed to be monotonic), and then use it to remap the modulation signal mod[k] to the tuning word tw. The values of the inverse function are a finite set of numbers, denoted here as  $\{c_i\}$ . DPD implementations based on polynomial correction or look-up table (LUT) have been presented [2]. Usually, the LUT approach is preferred to the polynomial correction, for its lower hardware complexity and accuracy required in the estimation of the coefficients. However, both the techniques require periodic re-calibration to track temperature and supply fluctuations. An adaptive DPD has been introduced in [19] with the purpose of linearizing the characteristic of the digital-to-time converter (DTC), and then successfully applied to pre-distort the DCO tuning curve

CHERNIAK et al.: 23-GHz LOW-PHASE-NOISE DIGITAL BANG-BANG PLL

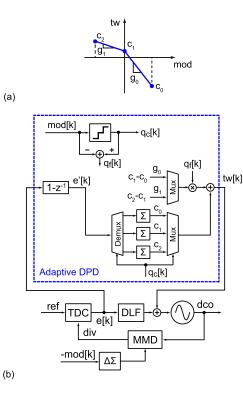

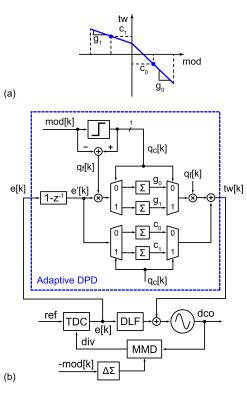

Fig. 7. Adaptive PWL DPD in [11] for the two-gain case. (a) Estimated inverse function. (b) Block diagram.

in [20]. Instead of estimating each point of the inverse curve, which would require large hardware resources, a piecewise linear (PWL) pre-distortion of the nonlinear characteristic is performed, which is only a subset of the  $c_i$  points of the inverse characteristic estimated. Then,  $c_i$  are linearly interpolated to get the entire characteristic. Of course, the inverse function calculated in this fashion is not exactly the inverse function of the DCO characteristic, even if  $c_i$  were accurately evaluated. However, PWL DPD helps mitigate integral nonlinearity with limited hardware resources [19].

The previously reported DPD scheme is schematically shown in Fig. 7, where, for the sake of simplicity, only two sections of the piecewise characteristic are considered. After coarsely quantizing the modulation signal mod[k] into a three-level word  $q_c[k]$ , the latter is correlated with the first difference e'[k] of the TDC output.<sup>3</sup> In this way, the average correction needed in each of the three regions of mod[k],  $c_0$ ,  $c_1$ , and  $c_2$ , is estimated. To properly scale also the least-significant bits of mod[k],  $q_f[k]$ , the slopes  $g_0$  and  $g_1$  of the PWL curve in Fig. 7(a) are simply obtained by the difference of the  $c_i$ coefficients. Unfortunately, in the latter approach, the LMS loops estimating  $c_i$  may interact with each other (i.e.,  $c_1$ with  $c_2$  and so forth) through the calculation of the slopes  $g_i$ (i.e.,  $g_2 = c_2 - c_1$ ). To avoid this issue, which slows down the coefficient convergence and in some cases may lead to instability, the  $g_i$  gains have to be calculated and used only after the  $c_i$  settle and then recalculated cyclically to track variations.

Fig. 8. Proposed adaptive PWL DPD for the two-gain case. (a) Estimated inverse function. (b) Block diagram.

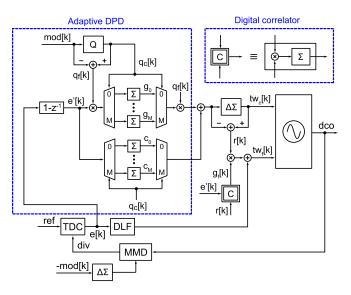

Fig. 9. Practical implementation of the presented adaptive PWL DPD: multi-gain and multi-bank DCO case.

The solution presented here, instead, decouples the estimate of the coefficients  $c_i$  from the estimate of the  $g_i$ gains. As depicted in Fig. 8, the correlation between the quantization error  $q_f[k]$  and e'[k] is exploited to estimate the  $g_i$ . In this way, though the number of LMS loops is higher (in general almost doubled), the coefficients within  $c_i$  bank no longer interact with each other and the LMS algorithm can operate fully in background. Fig. 9 presents the block diagram of the practical adaptive PWL DPD in the multi-gain case, when a DCO with two capacitor banks is used.

<sup>&</sup>lt;sup>3</sup>The first difference is needed to account for the intrinsic integration between mod[k], controlling frequency, and e[k], being proportional to phase error.

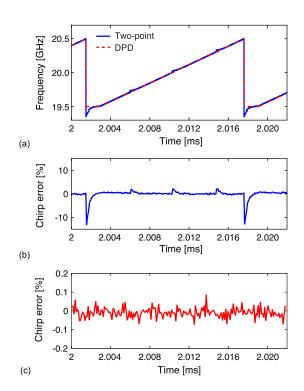

Fig. 10. Simulation results of the system in Fig. 9. (a) Demodulated output frequency. (b) Chirp error disabling DPD. (c) Chirp error enabling DPD.

An additional  $g_f$  gain is estimated to match the coarse and the fine DCO characteristics [11]. Although the gain of the fine bank changes along the DCO coarse characteristic and this would require a multi-gain estimation even in the fine bank, this effect is negligible with the used 5% chirp amplitude.

## V. SIMULATION RESULTS

To confirm the intuitive picture provided in Section III and assess the functionality of the presented adapative DPD scheme, the DPLL-based FMCW modulator in Fig. 9 was simulated, where 16  $g_i$  and 16  $c_i$  coefficients are estimated. The DCO was modeled at the behavioral level including both the systematic capacitance-to-frequency nonlinearity and the mismatch-induced nonlinearity. In particular, a 10-bit DCO where every 128th element contains a mismatch of 10 LSBs was accounted for. A sawtooth waveform with a  $\Delta f_{pp}$  = 1 GHz around a 20-GHz carrier is generated. Fig. 10 presents the simulation results of the DPLL disabling the DPD (in practice, the conventional two-point modulation scheme in Fig. 5) and enabling the presented DPD scheme. The chirp error over time in Fig. 10(b) shows the predicted steps with relatively slow recovery at both the sawtooth abrupt step (because of systematic nonlinearity) and at each random step in the tuning characteristic (because of element mismatch). The chirp error  $\epsilon_{chirp.max}$  at the abrupt step predicted from (3) of about 15% is close to the simulated peak error of about 13%. Fig. 10(c) shows the chirp error when DPD is enabled. The obtained results demonstrate that DPD effectively linearizes the DCO characteristic significantly reducing the chirp error. Finally, Fig. 11 reports the transient of the  $g_i$  and  $c_i$  coefficients from start-up to settling, using the training signal shown

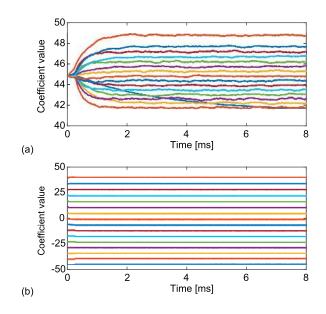

Fig. 11. Simulated convergence of the DPD coefficients for the system in Fig. 9 from start-up to settling. (a)  $\{g_i\}$  gains. (b)  $\{c_i\}$  coefficients.

Fig. 12. Block diagram of the implemented FMCW modulator.

in Fig. 10(a). The DPD requires about 2 ms to bring the chirp error below 0.1%. This is because about 100 periods of the training sequence are needed to achieve the required accuracy of the coefficients estimation [24]. Although one of the  $g_i$  coefficients in Fig. 10(a) has a slower convergence, its impact on the chirp error is negligible, as it refers to the boundary of the DCO characteristic.

# VI. PLL DESIGN

The implemented PLL-based FMCW modulator is presented in Fig. 12. The DPLL is based on a binary phase detector (BPD) (or single-bit TDC), which operation in random noise regime is enabled by means of a DTC, which is employed to cancel the quantization noise introduced by a second-order digital  $\Delta\Sigma$  modulator driving the feedback frequency divider [21]. To ensure low spur and phase noise operation, the DTC is also pre-distorted with DPD [19]. The feedback frequency divider is fed with a prescaled-by-four version of the DCO output clock, which allows a low-power

CHERNIAK et al.: 23-GHz LOW-PHASE-NOISE DIGITAL BANG-BANG PLL

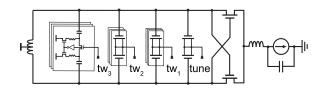

Fig. 13. DCO circuit schematic.

implementation in CMOS logic. The modulation signal mod[k]is simultaneously added to the frequency control word and applied to the coarse tuning bank of the DCO. The DPD scheme, which was presented in Section V, is applied to the coarse modulation bank, since its mismatch and nonlinearity are the most significant ones. The DPD was implemented with 16 segments as a compromise between the accuracy of the nonlinearity correction and the hardware overhead based on the DCO characteristic from post-layout simulations. The driving scheme of the finer banks is based on cancellation of the quantization error introduced in the coarser bank. A firstorder digital  $\Delta \Sigma$  modulator is employed as a quantizer at each modulation bank, since its quantization noise can be effectively utilized for the estimation of  $g_{f,0}$  and  $g_{f,1}$  gains (shown in Fig. 12) required to relate the characteristics of each bank [11].

To achieve fine frequency resolution, the finest bank is implemented as a cascade of a DAC and an analog low-pass *RC* filter, driving a varactor. A separate bank is dedicated to the frequency-acquisition loop. The PLL is fed with a 52-MHz clock, which is used to clock the digital core. The 5.8-GHz output of the divide-by-four prescaler that feeds a pad driver is used for testing. This relaxes the bandwidth requirements for the signal analyzer, because it scales down by four also the peak-to-peak deviation  $\Delta f_{pp}$  of the frequency modulation.

The circuit schematic of the DCO is depicted in Fig. 13. To ensure robust start-up without additional circuitry, a class-B oscillator topology with an nMOS cross-coupled differential pair has been preferred over a class-C implementation. The main tank inductor is implemented as a single-turn coil with a center-tap connected to the supply voltage and with five turns of a top metal layer connected in parallel. A tail filter made of a 75-pH spiral inductor and a 10-pF capacitor is employed to filter the noise of the tail current source, as well as to provide higher impedance at the second-harmonic frequency similar to the concept proposed in [22]. The oscillator features four different digitally controlled capacitor banks. The coarsest bank, implemented using switched metal-metal capacitors, is dedicated to coarse frequency tuning. The finer banks, dedicated to modulation, are implemented using digitally controlled MOS varactors. The finest tuning bank is implemented using an analog-tuned MOS varactor. DCO frequency is centered at around 22 GHz, which is a couple of GHz away from the center of the 24-GHz FMCW radar band because of some inaccuracy in the parasitic extraction. The achieved tuning range is about 17%.

The DTC is realized in a current-mode logic as a cascade of a buffer with capacitive DAC load followed by a slope regeneration buffer. The capacitive DAC is implemented using digitally controlled MOS varactors segmented in coarse and

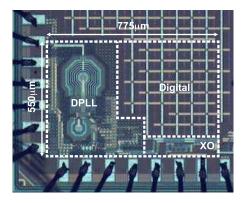

Fig. 14. Die photograph.

Fig. 15. Measured phase noise spectra in both integer-N and fractional-N modes at the divider-by-four output.

fine banks. The DTC covers about 150-ps range with a fine resolution of about 300 fs. The fine bank of the DTC is driven by a digital  $\Delta\Sigma$  modulator that shapes its quantization noise, which is further filtered by the digital loop filter. This allows keeping DTC quantization noise significantly below other noise contributors.

## VII. MEASUREMENT RESULTS

The prototype has been fabricated in a standard 65-nm LP CMOS process with no ultra-thick metal layer option. The analog and the digital portions of the chip whose photograph is shown in Fig. 14 occupy approximately the same share of the total 0.42 mm<sup>2</sup> area. The output of the frequency divider by four is used to carry out all the measurements. The output of the pad driver is wire bonded to the test board and used for testing. This setup reducing the output frequency to around 5.8 GHz simplifies both phase-noise measurement, which does not require external mixers, and modulation-analysis measurement, as it scales down by four the modulation depth.

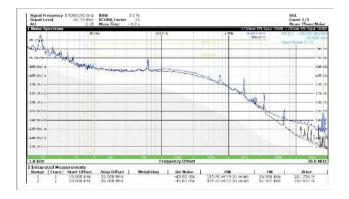

The phase noise spectra in integer- and fractional-N modes measured by an R&S FSWP phase-noise analyzer are shown in Fig. 15. In both the cases, the in-band noise plateau is at about -102 dBc/Hz and the phase noise at 1 MHz offset from the carrier at 5.928 GHz is about -112 dBc/Hz. The latter corresponds to about -100 dBc/Hz at 1-MHz offset when referred to the actual DCO output at 23.712 GHz. In the fractional-N mode, the far-out phase noise exhibits a slight

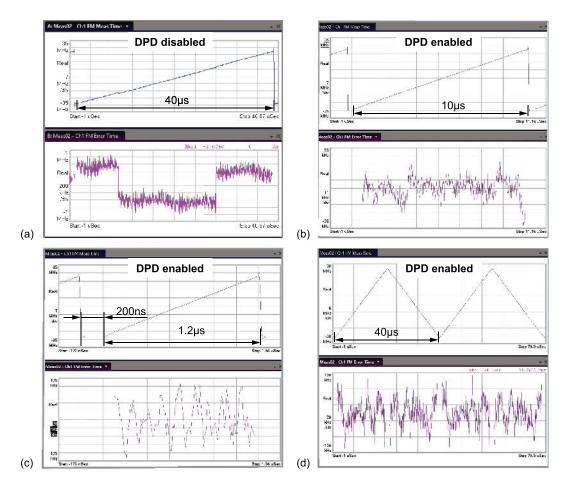

Fig. 16. Chirp measurements at divider-by-four output. (a)  $40-\mu s$  sawtooth with single-gain calibration (no DPD). (b)  $10-\mu s$ -sawtooth with DPD. (c)  $1.2-\mu s$  sawtooth with DPD. (d)  $40-\mu s$  triangular with DPD.

increment, increasing the absolute jitter from 213 fs (in the integer-N mode) to about 242 fs (in the fractional-N mode). In-band fractional spur is below -58 dBc [16].

An Anritsu MS2850A featuring 1-GHz demodulation bandwidth has been employed as a vector signal analyzer (VSA). To assess the efficacy of the DPD, the modulator has been at first tested without enabling the adaptive DPD. A single gain for each bank of the DCO is estimated, which corrects for mismatches between coarse and fine banks, but leaves the mismatches among the elements of the coarse bank and the systematic nonlinearity uncorrected. Fig. 16(a) shows the demodulated frequency signal for a sawtooth chirp with 40- $\mu$ s period and 52-MHz frequency deviation at the output of the divide-by-four block (equivalent to 208 MHz at the DCO output) and the corresponding frequency error. The effects of DCO nonlinearity are clearly visible in the scope, and the peak chirp error is about 1.058 MHz, which is about 2% with respect to the peak-to-peak chirp deviation.

The following figures [Fig. 16(b) and (c)] present instead the measurements when the adaptive DPD is enabled. The peak-to-peak frequency deviation is 52 MHz in both the cases (equivalent to 208 MHz at the DCO output). In Fig. 16(b), the chirp rise time is 10  $\mu$ s, the resulting peak frequency error is below 50 kHz (equivalent to 200 kHz at the DCO output), which is less than 0.1% of the maximum frequency

Fig. 17. Abrupt 52-MHz frequency step at the end of the sawtooth modulation, measured at the divider-by-four output.

deviation, and the rms chirp error is 0.06%. Fig. 16(c) shows the same frequency deviation covered in only 1.2  $\mu$ s, which results in a state-of-the-art chirp slope of 173 MHz/ $\mu$ s at the DCO output. In this case, the peak error is below 100 kHz (i.e., below 0.2%). The circuit can generate also triangular chirps: Fig. 16(d) shows the demodulated waveform for a 40- $\mu$ s period. The effectiveness of the proposed technique, CHERNIAK et al.: 23-GHz LOW-PHASE-NOISE DIGITAL BANG-BANG PLL

|                                       | This Work                                                 | [2]         | [14]             | [23]            | [3]             | [9]         | [4]                    |

|---------------------------------------|-----------------------------------------------------------|-------------|------------------|-----------------|-----------------|-------------|------------------------|

| Architecture                          | BBPLL+TPM                                                 | ADPLL+TPM   | HPLL+TPM         | ADPLL+TPM       | Analog PLL      | DPLL        | Analog<br>cascaded PLL |

| Freq. range<br>[GHz]                  | 20.4-24.6                                                 | 56.4 - 63.4 | 12.2 - 26.4      | 8.4-9.4         | 75–83           | 36.3-38.2   | 76-81                  |

| Technology                            | 65nm CMOS                                                 | 65nm CMOS   | 32nm<br>SOI-CMOS | 65nm CMOS       | 130nm<br>BiCMOS | 40nm CMOS   | 45nm CMOS              |

| Ref. freq. [MHz]                      | 52                                                        | 40          | 133              | 276.8           | 125             | 120         | 40                     |

| Chirp type                            | Saw-tooth/<br>Triangular                                  | Triangular  | Triangular       | Triangular      | Saw-tooth       | Triangular  | Saw-tooth              |

| Chirp duration $[\mu s]$              | 1.2-315                                                   | 420-8200    | 1300             | 5-220           | 50–225          | 50-2000     | 40                     |

| Saw-tooth idle time $[\mu s]$         | 0.2                                                       | n/a         | n/a              | n/a             | 15              | n/a         | 15                     |

| Max. chirp $\Delta f_{pp}$<br>[MHz]   | 208                                                       | 1220        | 8000             | 956             | 8000            | 500         | 4000                   |

| Max. chirp slope<br>[MHz/µs]          | 173                                                       | 4.76        | 10               | 32.6            | 100             | 9.1         | 100                    |

| RMS freq. error <sup>†</sup><br>[kHz] | $\begin{array}{c} 124/112 \\ (0.06\%/0.05\%) \end{array}$ | 384 (0.03%) | n/a              | 1900<br>(0.12%) | 3200<br>(0.04%) | 820 (0.16%) | n/a                    |

| Phase noise*<br>[dBc/Hz]              | -90                                                       | -87.7       | -79.3            | -86.2           | -97             | -73.7       | -91                    |

| Spur level [dBc]                      | -58                                                       | -62         | n/a              | n/a             | n/a             | -55         | n/a                    |

| Power [mW]                            | 19.7                                                      | 48          | 30               | 14.8            | 590             | 68          | n/a                    |

| Area [mm <sup>2</sup> ]               | 0.42                                                      | 2.2         | 0.28             | 0.18            | 4.42            | 0.18        | n/a                    |

TABLE I Performance Comparison

\* At 1-MHz offset referred to a 79GHz carrier.

<sup>†</sup> At max. chirp slope.

Fig. 18. Spectra of the modulated carrier with 52-MHz peak-to-peak frequency deviation at the divider-by-four output. (a) Sawtooth. (b) Triangular chirp.

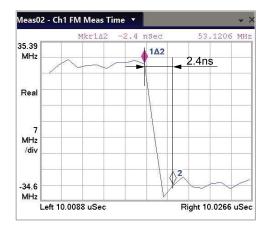

to achieve very fast modulation, is probably even better demonstrated in Fig. 17 that highlights the falling edge of the demodulated frequency signal of Fig. 16(c). The idle time required to match the 0.1% error specification is lower than 2.4 ns with no over or undershoot, thanks to the introduced DPD circuit that allows to exploit completely the two-point modulation technique.

Finally, the spectra of the carrier-modulated by sawtooth and triangular signals, with 52-MHz frequency deviation in both the cases, measured with a Keysight PXA spectrum analyzer are shown in Fig. 18. Comparing the presented chirp generator with other state-of-the-art CMOS and BiCMOS implementations in Table I, we can conclude that the presented DPLL with two-point injection and DCO predistortion is able to generate chirps with the largest maximum slope at better than 0.1% linearity, at competitive phase-noise and power consumption levels.

# VIII. CONCLUSION

This paper has presented a 23-GHz FMCW modulator based on a DPLL with two-point injection, which is capable of fast sawtooth and triangular chirp generation. The impact of DCO nonlinearity, induced by systematic capacitance-to-frequency nonlinearity and element mismatches, on chirp linearity has been analyzed. A novel DPD algorithm of the DCO has been introduced, which operates fully in background, provides robust convergence, and enables fast sawtooth chirp generation with linearity better than 0.1%, slopes up to 173 MHz/ $\mu$ s, and idle time that can be reduced to just 2.4 ns with no over or undershoot.

#### ACKNOWLEDGMENT

The authors would like to thank Infineon Technologies AG for supporting this research and Anritsu Corporation for providing the VSA measurement setup.

#### REFERENCES

I. Nasr et al., "A highly integrated 60 GHz 6-channel transceiver with antenna in package for smart sensing and short-range communications," *IEEE J. Solid-State Circuits*, vol. 51, no. 9, pp. 2066–2076, Sep. 2016.

- [2] W. Wu, R. B. Staszewski, and J. R. Long, "A 56.4-to-63.4 GHz multirate all-digital fractional-N PLL for FMCW radar applications in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 49, no. 5, pp. 1081–1096, May 2014.

- [3] J. Vovnoboy, R. Levinger, N. Mazor, and D. Elad, "A fully integrated 75–83 GHz FMCW synthesizer for automotive radar applications with -97 dBc/Hz phase noise at 1 MHz offset and 100 GHz/mSec maximal chirp rate," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Honolulu, HI, USA, May 2017, pp. 96–99.

- [4] B. P. Ginsburg *et al.*, "A Multimode 76-to-81 GHz automotive radar transceiver with autonomous monitoring," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2018, pp. 158–159.

- [5] D. E. Barrick, "FM/CW radar signals and digital processing," NOAA, Silver Spring, MD, USA, Tech. Rep. ERL 283-WPL 26, Jul. 1973.

- [6] S. Trotta *et al.*, "An RCP packaged transceiver chipset for automotive LRR and SRR systems in SiGe BiCMOS technology," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 3, pp. 845–860, Mar. 2012.

- [7] H. Jia *et al.*, "A 77 GHz frequency doubling two-path phased-array FMCW transceiver for automotive radar," *IEEE J. Solid-State Circuits*, vol. 51, no. 10, pp. 2299–2311, Oct. 2016.

- [8] J. Park, H. Ryu, K.-W. Ha, J.-G. Kim, and D. Baek, "76–81-GHz CMOS transmitter with a phase-locked-loop-based multichirp modulator for automotive radar," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 4, pp. 1399–1408, Apr. 2015.

- [9] D. Weyer, M. B. Dayanik, S. Jang, and M. P. Flynn, "A 36.3-to-38.2 GHz -216 dBc/Hz<sup>2</sup> 40 nm CMOS fractional-N chirp synthesizer PLL with continuous-time bandpass delta-sigma time-to-digital converter," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2018, pp. 250–251.

- [10] M. J. Underhill and R. I. H. Scott, "Wideband frequency modulation of frequency synthesisers," *Electron. Lett.*, vol. 15, no. 13, pp. 393–394, Jun. 1979.

- [11] G. Marzin, S. Levantino, C. Samori, and A. L. Lacaita, "A 20 Mb/s phase modulator based on a 3.6 GHz digital PLL With -36 dB EVM at 5 mW Power," *IEEE J. Solid-State Circuits*, vol. 47, no. 12, pp. 2974–2988, Dec. 2012.

- [12] Y. Wang *et al.*, "A 260-mW ku-band FMCW transceiver for synthetic aperture radar sensor with 1.48-GHz bandwidth in 65-nm CMOS technology," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 11, pp. 4385–4399, Nov. 2017.

- [13] M. Huang *et al.*, "A CMOS delta-sigma PLL transmitter with efficient modulation bandwidth calibration," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 7, pp. 1716–1725, Jul. 2015.

- [14] M. Ferriss, B. Sadhu, A. Rylyakov, H. Ainspan, D. Friedman, "A 12-to-26 GHz fractional-N PLL with dual continuous tuning LC-D/VCOs," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2016, pp. 196–197.

- [15] D. Cherniak, C. Samori, R. Nonis, and S. Levantino, "PLL-based wideband frequency modulator: Two-point injection versus pre-emphasis technique," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 3, pp. 914–924, Mar. 2018.

- [16] D. Cherniak, L. Grimaldi, L. Bertulessi, C. Samori, R. Nonis, and S. Levantino, "A 23 GHz low-phase-noise digital bang-bang PLL for fast triangular and saw-tooth chirp modulation," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2018, pp. 248–249.

- [17] R. Yu et al., "A 5.5 mA 2.4-GHz two-point modulation Zigbee transmitter with modulation gain calibration," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Sep. 2009, pp. 375–378.

- [18] E. Alvarez-Fontecilla, C. Venerus, and I. Galton, "Multi-rate DEM with mismatch-noise cancellation for DCOs in PLLs," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 10, pp. 3125–3137, Oct. 2018.

- [19] S. Levantino, G. Marzin, and C. Samori, "An adaptive pre-distortion technique to mitigate the DTC nonlinearity in digital PLLs," *IEEE J. Solid-State Circuits*, vol. 49, no. 8, pp. 1762–1772, Aug. 2014.

- [20] N. Markulic *et al.*, "A DTC-based subsampling PLL capable of selfcalibrated fractional synthesis and two-point modulation," *IEEE J. Solid-State Circuits*, vol. 51, no. 12, pp. 3078–3092, Dec. 2016.

- [21] D. Tasca, M. Zanuso, G. Marzin, S. Levantino, C. Samori, and A. L. Lacaita, "A 2.9–4.0-GHz fractional-N digital PLL with bang-bang phase detector and 560-fs<sub>rms</sub> integrated jitter at 4.5-mW power," *IEEE J. Solid-State Circuits*, vol. 46, no. 12, pp. 2745–2758, Dec. 2011.

- [22] L. Iotti, A. Mazzanti, F. Svelto, "Insights into phase-noise scaling in switch-coupled multi-CoreLCVCOs for E-band adaptive modulation links," *IEEE J. Solid-State Circuits*, vol. 52, no. 7, pp. 1703–1718, Jul. 2017.

- [23] H. Yeo, S. Ryu, Y. Lee, S. Son, and J. Kim, "A 940 MHz-bandwidth 28.8 μs-period 8.9 GHz chirp frequency synthesizer PLL in 65 nm CMOS for X-band FMCW radar applications," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2016, pp. 238–240.

[24] D. Cherniak, L. Grimaldi, C. Samori, and S. Levantino, "Adaptive digital

- [24] D. Cherniak, L. Grimaldi, C. Samori, and S. Levantino, "Adaptive digital pre-emphasis for PLL-based FMCW modulators," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, Florence, Italy, Jun. 2018, pp. 1–5.

- [25] M. C. Budge and M. P. Burt, "Range correlation effects in radars," in *Proc. Rec. IEEE Nat. Radar Conf.*, Lynnfield, MA, USA, Apr. 1993, pp. 212–216.

**Dmytro Cherniak** (S'15) was born in Kiev, Ukraine, in 1987. He received the B.S. and M.S. degrees in electronic engineering from the Kiev Polytechnic Institute, National Technical University of Ukraine, Kiev, in 2008 and 2010, respectively. He is currently pursuing the Ph.D. degree in electronic engineering with the Politecnico di Milano, Milan, Italy.

His current interests include digital phase-locked loop techniques, precise timing references, adaptive filtering, jitter theory, and stochastic processes.

Luigi Grimaldi was born in Rome, Italy, in 1992. He received the B.S. and M.S. degrees in electrical engineering from the Politecnico di Milano, Milan, Italy, in 2013 and 2015, respectively, where he is currently pursuing the Ph.D. degree in electrical engineering. In his Ph.D. activity, he is involved in frequency synthesis based on digital fractional-N PLL for new generation wireless communication standards.

His current interests include digital phase-locked loop techniques, jitter theory, and digital calibration techniques.

Luca Bertulessi was born in Bergamo, Italy, in 1991. He received the B.S. and M.S. degrees in electrical engineering from the Politecnico di Milano, Milan, Italy, in 2013 and 2015, respectively, where he is currently pursuing the Ph.D. degree.

He was a Research Assistant from 2015 to 2016 involved in the design of high-efficiency oscillators and digital frequency synthesizers in the CMOS technology for wireless applications. His current research interests include mm-wave oscillators, digitally intensive fractional-N frequency synthesiz-

ers, and direct modulation techniques for future 5G applications.

**Roberto Nonis** was born in Udine, Italy, in 1977. He received the M.S. and Ph.D. degrees from the University of Udine, Udine, in 2002 and 2007, respectively, involved in modeling and design of integrated circuits for frequency synthesis.

From 2006 to 2007, he held a post-doctoral position at Agere Systems Inc., Allentown, PA, USA, where he was involved in the design of highspeed, low-power dynamic comparators for ADCs. In 2007, he joined the Clock and Interfaces Systems Group, Infineon Technologies AG, Villach, Austria,

as an Analog-Mixed Signal Designer, and currently leads the group with a focus on precision oscillators, analog and digital frequency synthesizers, and high-speed serial interfaces in advance CMOS technologies.

Dr. Nonis is currently a member of the Technical Program Committee of the International Solid-State Circuit Conference.

**Carlo Samori** (M'98–SM'08–F'17) was born in 1966. He received the Laurea degree in electrical engineering and the Ph.D. degree in electronics and communications from the Politecnico di Milano, Milan, Italy, in 1992 and 1995, respectively.

From 1997 to 2002, he has been a Consultant for Bell Labs, Murray Hill, NJ, USA, and then for Agere Systems, Allentown, PA, USA. Since 1996, he has been a Professor with the Politecnico di Milano, where he is currently a Full Professor of electrical engineering. He is initially involved in high-speed

low-noise front-end circuits for photodetectors, and then in the area of design and analysis of integrated circuits for communications both in bipolar and in the CMOS technology. Among his works, he contributed to a time-variant theory of phase noise generation in *LC*-tuned VCO, and he collaborated to the design of several low phase noise VCO in the bipolar and CMOS technology. He has contributed to the design of fractional- and integer-N PLLs for multistandard WLAN applications. He has co-authored about 100 papers in international journals and conferences. In 2007, he published, as a Co-Author, the book *Integrated Frequency Synthesizers for Wireless Systems* (Cambridge University Press). His current research interests include frequency synthesizers and data converters.

Dr. Samori is a member of the TPC for the European Solid-State Circuits Conference. He is a Distinguished Lecturer of the IEEE. He served on the Technical Program Committee for the IEEE International Solid-State Circuits Conference and as Guest Editor for the IEEE JOURNAL OF SOLID-STATE CIRCUITS in 2015.

Salvatore Levantino (S'99–M'02–SM'16) received the Laurea (*cum laude*) and Ph.D. degrees in electrical engineering from the Politecnico di Milano, Milan, Italy, in 1998 and 2001, respectively.

He was a Consultant with Bell Labs, Lucent Technologies, Inc., Murray Hill, NJ, USA, from 2000 to 2002. Since 2005, he has been an Assistant Professor and subsequently an Associate Professor of electrical engineering with the Politecnico di Milano. He has co-authored over 100 scientific papers and *Integrated Frequency Synthesizers for*

*Wireless Systems* (Cambridge Univ. Press, 2007). He holds six patents. His current research interests include wireless transceivers, frequency synthesizers, and data converters.

Dr. Levantino was a Steering Committee Member of the Radio-Frequency Integrated Circuits (RFIC) Symposium from 2015 to 2017. He is currently serving as the IEEE SSCS Distinguished Lecturer and as a Committee Member of the Student Research Preview Program for the International Solid-State Circuits Conference (ISSCC). He is currently a TPC Member of the RFIC Symposium and the European Solid-State Circuits Conference (ESSCIRC). He was a Guest Editor for the IEEE JOURNAL OF SOLID-STATE CIRCUITS in 2016 and an Associate Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS–I from 2014 to 2015 and for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS–II from 2012 to 2013.