Delft University of Technology

## A 25A Hybrid Magnetic Current Sensor with 64mA Resolution, 1.8MHz Bandwidth, and a Gain Drift Compensation Scheme

Jouyaeian, Amirhossein; Fan, Qinwen; Motz, Mario; Ausserlechner, Udo; Makinwa, Kofi A.A.

DOI 10.1109/ISSCC42613.2021.9365767

Publication date 2021 **Document Version**

Final published version

Published in

2021 IEEE International Solid-State Circuits Conference, ISSCC 2021 - Digest of Technical Papers

## Citation (APA)

Jouyaeian, A., Fan, Q., Motz, M., Ausserlechner, U., & Makinwa, K. A. A. (2021). A 25A Hybrid Magnetic Current Sensor with 64mA Resolution, 1.8MHz Bandwidth, and a Gain Drift Compensation Scheme. In 2021 IEEE International Solid-State Circuits Conference, ISSCC 2021 - Digest of Technical Papers (pp. 82-84). [9365767] (Digest of Technical Papers - IEEE International Solid-State Circuits Conference; Vol. 64) Institute of Electrical and Electronics Engineers (IEEE). https://doi.org/10.1109/ISSCC42613.2021.9365767

### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

#### Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository

## 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

## 5.6 A 25A Hybrid Magnetic Current Sensor with 64mA Resolution, 1.8MHz Bandwidth, and a Gain Drift Compensation Scheme

Amirhossein Jouyaeian<sup>1</sup>, Qinwen Fan<sup>1</sup>, Mario Motz<sup>2</sup>, Udo Ausserlechner<sup>2</sup>, Kofi A. A. Makinwa<sup>1</sup>

<sup>1</sup>Delft University of Technology, Delft, The Netherlands <sup>2</sup>Infineon Technologies, Villach, Austria

Magnetic current sensors are used in switched-mode power supplies and motor drivers, where both galvanic isolation and wide bandwidth (BW) are desired. In CMOS, Hallgeffect sensors are widely used, but their resistance results in a fundamental trade-off between BW and resolution. Coils have a differentiating characteristic and so can achieve much wider BW and resolution, but cannot sense DC.

By using Hall sensors for low frequencies and coils for high frequencies, wide-band hybrid sensors can be realized [1,2]. In [1], two Hall/coil pairs sense the differential magnetic field around a current rail, thus rejecting CM external fields. The sensor achieves 480mA<sub>rms</sub> resolution from DC to 3MHz, while dissipating 38.5mW. However, its front-end senses coil voltage, which limits its high-frequency dynamic range (DR), and requires a DC servo loop based on a large (10 $\mu$ F) external capacitor. In [2], the front-end senses the current of a single coil, and thus achieves wider bandwidth (15.3MHz), at the expense of robustness to CM fields. Moreover, its Hall and coil paths are combined off-chip, and it achieves lower resolution (710mA<sub>rms</sub>) and dissipates more power (63.5mW).

This work presents a hybrid current sensor that measures the differential field around a lead-frame-based current rail. By sensing coil current and employing a pole-zero cancellation scheme, its front-end achieves high DR and resolution without external components. Compared to [1], it achieves similar BW (1.8MHz), but with 7.5× better resolution ( $64mA_{rms}$ ), 2× less power dissipation (19.5mW) and 50% less chip area  $(4.6mm^2)$ .

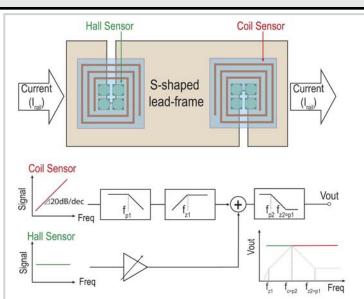

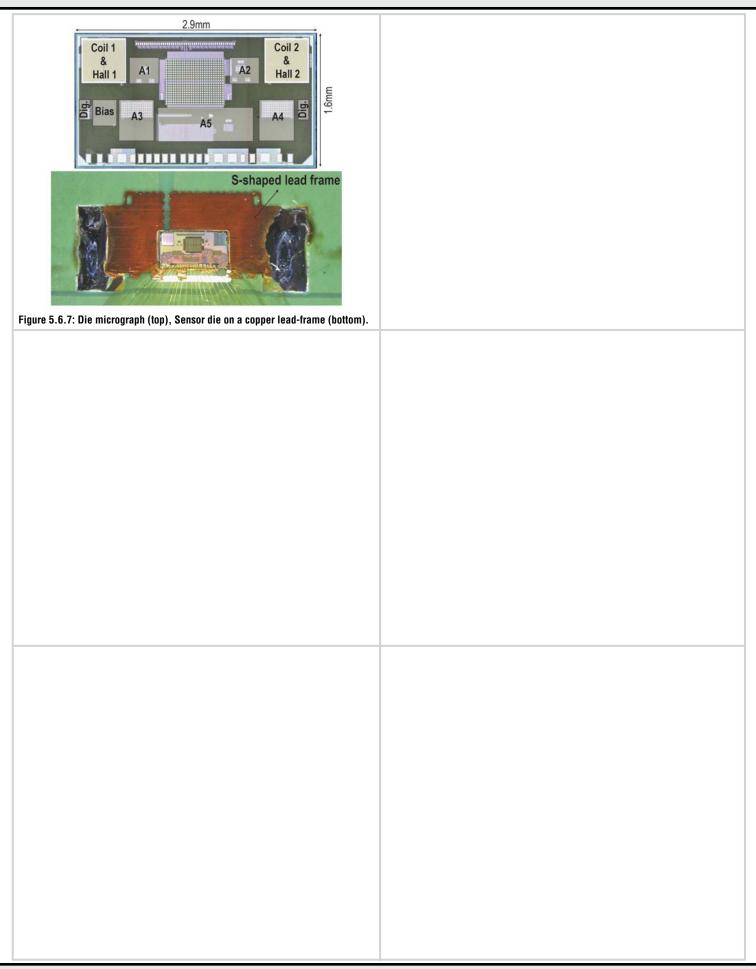

$\stackrel{\neg}{\rightarrow}$  As shown in Fig. 5.6.1 (top), the current rail consists of a low-resistance (250µ $\Omega$ )  $\stackrel{\neg}{\rightarrow}$  S-shaped lead-frame, which concentrates the magnetic field seen by its two Hall/coil  $\stackrel{\neg}{\rightarrow}$  pairs (by about 2× compared to a straight rail) [3]. Each Hall sensor consists of 4  $\stackrel{\neg}{\rightarrow}$  spinning-current Hall plates connected in parallel. The currents in the plates are designed  $\stackrel{\neg}{\rightarrow}$  to flow in different directions, resulting in a significant reduction of offset and stress  $\stackrel{\neg}{\rightarrow}$  sensitivity [3].

A simplified block diagram of the Hall and coil paths is shown in Fig. 5.6.1 (bottom). Since coil current is proportional to the derivative of lead-frame current ( $I_{rail}$ ), the coil path consists of a two-stage integrator. The 1<sup>st</sup> stage is a transimpedance amplifier with a pole at  $f_{p1}$ , which ensures that high-frequency components of  $I_{rail}$  do not cause its output to clip. To block offset, its output is AC-coupled to the 2<sup>nd</sup> stage, where it is combined with the output of the Hall path. The 2<sup>nd</sup> stage implements a pole at  $f_{p2}$  and a zero at  $f_{z2} = f_{p1}$ , thus realizing a coil path with a pole at  $f_{p2}$ . By appropriately setting the noise is filtered above the crossover frequency  $f_c = f_{p2}$ , which is chosen to balance the genoise contributions of the coil and Hall paths.

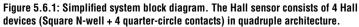

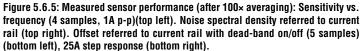

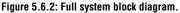

$_{2}^{\circ}$  A more detailed schematic of the current sensor is shown in Fig. 5.6.2, and the corresponding Bode plots are shown in Fig. 5.6.3. The 1<sup>st</sup> stage of the coil path (A<sub>1</sub>) realizes f<sub>p1</sub> = 200kHz (R<sub>1</sub>C<sub>1</sub>). Above this frequency, C<sub>1</sub> (25pF) limits its output swing to  $\approx$  -1.125V when I<sub>rall</sub> ~25A. The 2<sup>sd</sup> stage (A<sub>2</sub>) realizes f<sub>p2</sub> = 200kHz (R<sub>3</sub>C<sub>3</sub>) and f<sub>p2</sub> = 10kHz (R<sub>4</sub>C<sub>3</sub>). The coil path thus behaves like an integrator with a 10kHz pole, as shown in Fig. 5.6.3 (left). Although this could be done in a single stage, R<sub>1</sub> would be very large (3MΩ), which, together with the low coil resistance R<sub>coil</sub> (3.3kΩ), would cause the output of A<sub>1</sub> the to clip on its own offset (~2mV). The proposed architecture allows R<sub>1</sub> to be small (32kΩ), resulting in ~20mV offset at the output of A<sub>1</sub>. This is then blocked by C<sub>2</sub> (260pF), which cogether with R<sub>2</sub> (480kΩ) defines a pole at 1.25kHz, and thus has a negligible effect above f<sub>c</sub>. The offset of the 2<sup>nd</sup> stage is amplified by a gain of 2 (R<sub>4</sub>=R<sub>LPF1</sub>+R<sub>LPF2</sub>), and so

it also has a negligible effect (~4mV) on the front-end's output offset. To ensure robustness to spread, the time constants  $R_1C_1$  and  $R_3C_3$  are realized by the same type of components. Also, the large temperature coefficient (TC = 0.36%/K) of  $R_{coll}$  is cancelled by realizing  $R_{1,3}$  with silicided n-poly resistors (TC = 0.31%/K).  $R_2$  is implemented with a p-poly resistor, whose low TC (-0.02%/K) leads to an overall coil-path TC of 0.03%/K.

To minimize the power consumption of their biasing circuitry, the two spinning Hall sensors are stacked (Fig. 5.6.2). The TC of their sensitivity is compensated by biasing them with a temperature-dependent current (~4mA at room temperature) derived from

two trimmable currents with positive ( $I_{PTC}$ ) and negative ( $I_{NTC}$ ) TCs, as shown in Fig. 5.6.2. These are implemented by forcing PTAT and CTAT voltages  $\varDelta V_{GS}$  and  $V_{GS}$ , generated by a pair of subthreshold biased PMOS transistors, across two resistors.

Figure 5.6.3 (right) shows the transfer function of the various stages of the Hall path. To reduce Hall sensor offset, the spinning-current technique is employed, in which the Hall voltage is up-modulated to twice the spinning frequency ( $2f_s = 100$ kHz), while its offset remains at DC [1]. Due to the lead-frame's dimensions, the distance between the two Hall sensors is rather large (-2.4 mm). To maintain signal integrity, their outputs are boosted by local capacitively-coupled amplifiers (CCAs) with a gain of 50 ( $A_{3,4}$ ), before being summed and demodulated by a similar CCA ( $A_5$ ), which also has a gain of 50.  $A_2$  then combines the outputs of the Hall and coil paths. The CCAs use switched-resistors to realize large DC feedback resistances (>1GQ), which establish zeros (-500Hz) that block the offsets of the Hall sensors and  $A_{3,4}$ . The up-modulated offset of  $A_5$  only experiences unity gain, and is filtered by a 50kHz LPF realized by  $R_{LPF1}$ ,  $R_{LPF2}$ . After each spinning-current transition, deadband switches at the virtual ground of  $A_5$  are used to block the resulting thermal settling transients of the Hall sensors, thus reducing their residual offset [4].

$A_{1,2}$  are Miller-compensated amplifiers, with folded-cascode input stages and Class-AB output stages to handle the induced coil currents, and drive external loads (20pF), respectively. To maximize their noise efficiency,  $A_{3,4}$  are telescopic current-reuse amplifiers. The equivalent input-referred noise levels of  $A_1$  and  $A_{3,4}$  are designed to match the thermal noise of  $R_{coll}$  (3.3k $\Omega$ ) and  $R_{Hall}$  (350 $\Omega$ ), respectively.

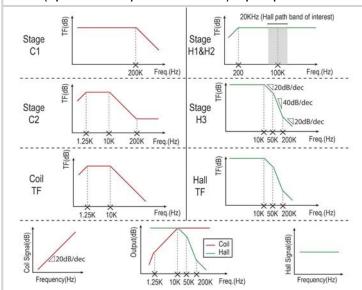

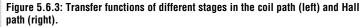

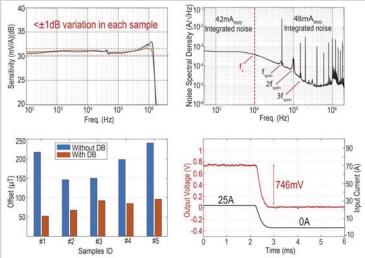

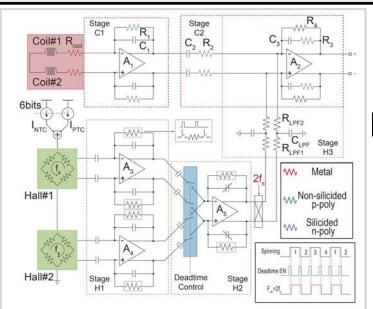

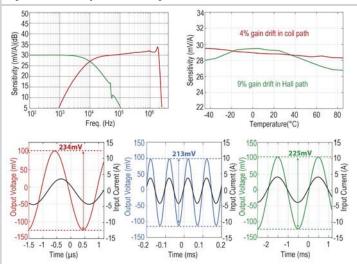

The current sensor occupies 4.6mm<sup>2</sup> in a 0.18µm CMOS process (Fig. 5.6.7, top). It draws 3.5mA from a 1.8V supply and 4mA (for the Hall sensors) from a 3.3V supply. It is isolated from the lead-frame by a non-conductive die attach (Fig. 5.6.7, bottom). The measured sensitivities of the coil and Hall paths are shown in Fig. 5.6.4, (top left). They both vary by less than 9% from -45°C to 85°C, as shown in Fig. 5.6.4 (top right). The sensor's response to 8Ann sine-wave currents at 500Hz, 10kHz and 500kHz is shown in Fig. 5.6.4 (bottom). After trimming the sensitivity of the Hall sensors (via their bias current), the current sensor's sensitivity (30mV/A) is flat to within 1dB from DC to 1MHz. This is limited by amplifier peaking and the BW of the differential-to-single-ended converter used to drive the spectrum analyzer (Fig. 5.6.5, top left). The sensor's noise spectral density is shown in Fig. 5.6.5 (top right). The total in-band noise (DC to 1.8MHz) corresponds to a resolution of  $64mA_{rms}$ , of which the coil and Hall paths contribute 26%and 74%, respectively. As shown in Fig. 5.6.4 (bottom left), the dead-band switches reduce the sensor's offset by about 2x. They also help reduce the input-referred spinning ripple to about 0.26A (74µT with the conversion rate of 283µT/A), which is similar to [1]. The sensor's response to a large current step (OA to 25A) is shown in Fig. 5.6.5, bottom right.

In Fig. 5.6.6, the sensor's performance is summarized and compared with other stateof-the-art CMOS-compatible magnetic current sensors. It achieves the highest resolution (×2.3), the lowest power (×1.8), and the highest dynamic range among hybrid sensors (+13dB), the highest FoM (×22) with off-chip current rail, as well as a wide DC to 1.8MHz BW.

#### Acknowledgement:

The authors would like to thank Zu-yao Chang for his invaluable contribution (especially in wire-bonding the chips), L. Pakula and R. van Puffelen for their help with the measurement, and Infineon Technologies for the financial support.

#### References:

[1] J. Jiang and K. Makinwa, "Multipath Wide-Bandwidth CMOS Magnetic Sensors," *IEEE JSSC*, vol. 52, no. 1, pp. 198-209, Jan. 2017.

[2] T. Funk et al., "An Integrated and Galvanically Isolated DC-to-15.3 MHz Hybrid Current Sensor," *IEEE APEC*, pp. 1010-1013, 2019.

[3] Mario Motz et al., "A Miniature Digital Current Sensor with Differential Hall Probes Using Enhanced Chopping Techniques and Mechanical Stress Compensation," *IEEE Sensors*, pp. 1-4, Oct. 2012.

[4] J. C. van der Meer et al., "A Fully Integrated CMOS Hall Sensor with a 3.65  $\mu T$   $3\sigma$  Offset for Compass Applications," *ISSCC*, pp. 246-247, Feb. 2005.

[5] Y. Li, M. Motz and L. Raghavan, "A Fast T&H Overcurrent Detector for a Spinning Hall Current Sensor With Ping-Pong and Chopping Techniques," *IEEE JSSC*, vol. 54, no. 7, pp. 1852-1861, July 2019.

[6] T. Funk and B. Wicht, "A Fully Integrated DC To 75 Mhz Current Sensing Circuit with On-Chip Rogowski Coil," *IEEE CICC*, April 2018.

[7] Allegro MicroSystems, ACS37002 Data Sheet, Accessed on Aug. 10, 2020. Available: https://www.allegromicro.com/en/products/sense/current-sensor-ics/zero-to-fifty-ampintegrated-conductor-sensor-ics/acs37002.

## ISSCC 2021 / February 16, 2021 / 9:10 AM

Figure 5.6.4: Measured performance of the Coil (Red) and Hall (Green) paths. Sensitivity vs. frequency (1A p-p) (top left). Sensitivity vs. temperature (1Ap-p @ 100Hz & 100kHz)(top right). Output transient response (after 1024× averaging) (8Ap-p @ 500kHz, 10kHz and 500Hz) (bottom left, middle, right).

| Source                    | Our work       | JSSC'17            | JSSC'19 | CICC'18                 | APEC'19                 | ACS37002 |

|---------------------------|----------------|--------------------|---------|-------------------------|-------------------------|----------|

|                           |                | [1]                | [5]     | [6]                     | [2]                     | [7]      |

| Sensor Type               | Coil +<br>Hall | Coil +<br>Hall     | Hall    | Rogowski Coil<br>+ Hall | Rogowski Coil<br>+ Hall | Hall     |

| Technology (µm)           | 0.18           | 0.18               | 0.35    | 0.18                    | 0.18                    | N/A      |

| Supply (V)                | 1.8/3.3        | 5                  | 3.3     | 1.8                     | 1.8                     | 3.3      |

| Area (mm <sup>2</sup> )   | 4.6            | 8.75               | N/A     | 3.17                    | 2.74                    | N/A      |

| Resolution (mArms)        | 64             | 480                | 480     | 150                     | 710                     | 160      |

| Input Range (Arms)        | +/- 25         | +/- 3.3<br>+/- 18ª | +/- 300 | +/- 4.1<br>+/- 40ª      | +/- 60                  | +/-66.7  |

| Dynamic Range (dB)        | 52             | 17                 | 56      | 29                      | 39                      | 52       |

| BW (MHz)                  | 1.8            | 3                  | 1.7     | 75                      | 15.3                    | 0.4      |

| Power Consumption<br>(mW) | 19.5           | 38.5               | 13.2    | 33.7                    | 63.5                    | 39.6     |

| FOMb                      | 22.5           | 0.34               | 1.02    | 99°                     | 0.48                    | 0.39     |

on appendice

<sup>b</sup>FOM = BW(MHz)/(Resolution(A<sub>rms</sub>)<sup>2</sup> × Power(mw)) <sup>c</sup>On-chip current rail

Figure 5.6.6: Performance summary and comparison with state-of-the-art CMOS magnetic current sensors.

# **ISSCC 2021 PAPER CONTINUATIONS**

2021 IEEE International Solid-State Circuits Conference Authorized licensed use limited to: TU Delft Library. Downloaded on March 22,2022 at 10:13:56 UTC from IEEE Xplore. Restrictions apply.