# A 3.3V 625 kHz switched-current multiplier

*Citation for published version (APA):* Leenaerts, D. M. W., Joordens, G. H. M., & Hegt, J. A. (1996). A 3.3V 625 kHz switched-current multiplier. *IEEE Journal of Solid-State Circuits*, *31*(9), 1340-1343. https://doi.org/10.1109/4.535421

DOI: 10.1109/4.535421

## Document status and date:

Published: 01/01/1996

### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# A 3.3 V 625 kHz Switched-Current Multiplier

D. M. W. Leenaerts, G. H. M. Joordens, and J. A. Hegt

Abstract-This paper presents a switched-current multiplier, designed for 3.3 V supply voltage, performing 0.625 M multiplications per second with a maximum nonlinearity of 0.94%. The die area is 100  $\times$  75  $\mu$ m<sup>2</sup> in a 2.4  $\mu$ m n-well CMOS process.

#### I. INTRODUCTION

▼URRENT domain techniques and especially switchedcurrent (SI) circuits are receiving more and more attention. Compared with switched-capacitor sampled-data circuits, SI circuits have a number of important advantages: they are exclusively composed of MOS transistors, switches and current sources instead of operational amplifiers, and precise linear floating capacitors, making them suitable for implementation in standard CMOS processes. As capacitors in SI technique are only used for holding voltages, SI circuits have no problems with capacitor mismatch. Furthermore, SI circuits are well suited for low-voltage applications.

A central element in SI circuits is the memory cell [1], [2] allowing for short-term storage of currents. The SI technique is often applied in filters, but its application area is rapidly growing [3] and comprises oscillators, digital-to-analog converters (DAC's), algorithmic analog-to-digital converters (ADC's), Sigma-Delta converters, cellular neural networks, etc. To the best knowledge of the authors, this paper is the first proposal for an SI multiplier.

Section II deals with the basic concept of (switched) current multipliers. In Section III the actual implementation of the multiplier using the quarter-square principle is described. Experimental results are provided in Section IV, while some concluding remarks are given in Section V.

#### II. SWITCHED-CURRENT MULTIPLIER

There is a variety of existing current domain multiplier principles, such as the translinear multiplier [4], current domain multiplier based on a Gilbert cell [5], pulse modulation multiplier [6], multiplication based on ADC/DAC conversion [7], and quarter square multiplier [8], [9]. The key to the latter principle is in the following equation:

$$(x+y)^2 - (x-y)^2 = 4xy.$$

(1)

When both x and y represent currents, two current squarers could be used. To cancel the quadratic terms completely however, the squarers should be perfectly matched. With the application of an SI memory cell, only one current squarer

The authors are with the Department of Electrical Engineering, Eindhoven University of Technology, NL 5600 MB Eindhoven, The Netherlands.

0018-9200/96\$05.00 © 1996 IEEE

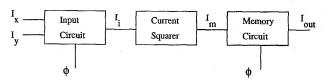

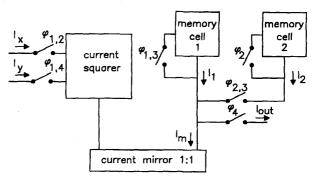

Fig. 1. Block diagram SI multiplier.

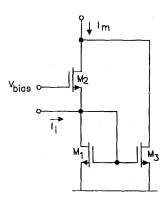

Fig. 2. Current squarer.

is required, as depicted in Fig. 1, circumventing the problem of matching. In this approach, first  $I_x$  and  $I_y$  are summed in the input circuit. The result is squared in the current squarer and temporarily stored in the memory circuit. Next  $I_x$  and  $I_y$ are subtracted. The result is squared and subtracted from the current that was stored in the memory circuit, resulting in an output current  $I_{out}$ , proportional to the product of  $I_x$  and  $I_y$ . This principle was used as a starting-point for the proposed SI multiplier. The SI multiplier of Fig. 1 is composed of three sub-circuits:

- an input circuit;

- a current squarer;

- an SI memory cell.

These three sub-circuits will be described below.

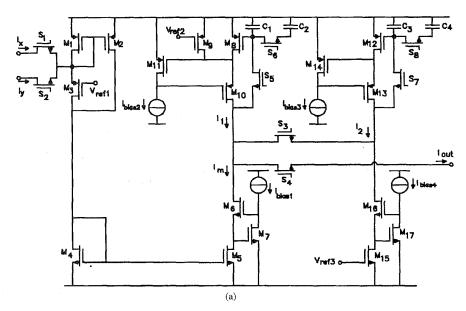

#### A. Current Squarer

For the current squarer in Fig. 1 several circuits exist, such as presented in [8]-[10]. The circuit in [10] was chosen for its simplicity and is given in Fig. 2. It has an (idealized) transfer of  $I_m = I_o + I_i^2/4I_o$  in which  $I_o$  is a constant current, which depends on  $V_{bias}$ . The transfer function of the nonidealized current squarer of Fig. 2 can in first order be approximated as

$$I_m = I_o + e_1 + \frac{(I_i + e_2)^2}{4I_o}$$

(2)

#### IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 31, NO. 9, SEPTEMBER 1996

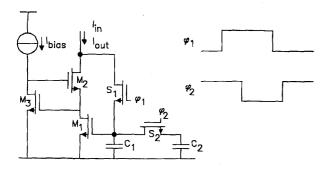

Fig. 3. Accurate SI memory cell.

where  $e_1$  represents the output offset error and error  $e_2$  the offset error at the input compared to the idealized transfer curve. Both errors are almost constant. A thorough analysis of this circuit reveals that the body effect of  $M_2$  and channel length modulation may deteriorate its performance. For that reason this circuit was slightly adapted in the actual implementation, as will be described in Section III.

#### B. Input Circuit

With the quadratic transfer characteristic given by (2), simple analysis shows that the error in the output of (1) is  $4ye_2/4I_o$ . To eliminate this error, a slightly adapted version of this principle was used, based on

$$(x+y)^2 - x^2 - y^2 = 2xy.$$

(3)

This principle has two important advantages. First, the input currents of the current squarer are  $I_x + I_y$ ,  $I_x$ , and  $I_y$ . As no subtraction of input currents is needed anymore, these currents can easily be realized using only a few switches, without the need for a current inverter with its related error. Second, the constant errors  $e_1$  and  $e_2$  of the current squarer can now completely be canceled. To realize this, four clock phases are required in which the currents  $I_x + I_y$ ,  $I_x$ , 0 (i.e., no current), and  $I_y$  are provided in turn. Applying (3) then yields

$$I_{out} = \left\{ I_0 + e_1 + \frac{(I_x + I_y + e_2)^2}{4I_o} \right\} \\ - \left\{ I_0 + e_1 + \frac{(I_x + e_2)^2}{4I_o} \right\} \\ + \left\{ I_0 + e_1 + \frac{(e_2)^2}{4I_o} \right\} \\ - \left\{ I_0 + e_1 + \frac{(I_y + e_2)^2}{4I_o} \right\} \\ = \frac{I_x I_y}{2I_o}$$

(4)

where the bracketed quantities correspond to the operations done on each of the four clock phases. Note the clock phase in which no current is provided to the current squarer is necessary to eliminate all errors. Due to the four clock phases, this multiplier is called a four-phase quarter-square SI multiplier.

Fig. 4. Block diagram four-phase quarter-square SI multiplier.

The input circuit can now be composed of only two transistors, one connected to  $I_x$  and the other to  $I_y$ .

#### C. Memory Circuit

The third sub-circuit in Fig. 1 is an SI memory cell, for which several solutions exist [1]–[3]. The SI memory cell of Fig. 3 is used here [11]. Switching transistor  $S_2$ , which has the same size as  $S_1$ , and capacitor  $C_2$  were added to reduce the clock feedthrough effects, caused by  $S_1$ . Cascode stage  $M_2$ ,  $M_3$  was added to reduce the effects due to the channel length modulation of  $M_1$ . The error at the output of the multiplier caused by this memory cell can be neglected in practice, compared to the errors caused by the nonidealities of the input circuit and the current squarer.

#### **III. ACTUAL IMPLEMENTATION**

The block diagram of the final multiplier is given in Fig. 4. In the first phase, the current  $I_x + I_y$  is squared and stored in memory cell 1. In the second clock phase,  $I_x$  is squared and stored in memory cell 2. Then in the third phase, no signal is applied to the squarer, but the contents of memory cell 2 are subtracted from that of cell 1. The output of the squarer is added to this intermediate result and the result is stored in cell 1. If in some applications a small output error is allowed, this clock phase may be skipped. In the final phase,  $I_y$  is squared and subtracted from the contents of cell 1. This result is immediately available at the output node. The described sequence is equal to the sequence as defined in (3) and (4).

The total four-phase quarter-square SI multiplier circuit is depicted in Fig. 5. A PMOS version  $(M_1-M_3)$  of the current squarer of Fig. 2 is used. In an n-well CMOS process the connection of the source of  $M_2$  to the n-well eliminates the body effect problem. The output of the current squarer is fed to a regulated cascoded current mirror  $(M_4-M_7)$ . In this way, problems caused by the finite output resistance of the current squarer due to channel length modulation were overcome. Two PMOS implementations  $(M_8-M_{11}, S_5, S_6, C_1, C_2)$  and  $(M_{12}-M_{14}, S_7, S_8, C_3, C_4)$  of the accurate SI memory cell of Fig. 3 were used. The cascoded current source  $(M_{15}-M_{17})$  was added to ensure a positive current through the second memory cell. Capacitors  $C_1$  and  $C_3$  are 0.1 pF, the other capacitors are 0.5 pF. All capacitors are implemented in double poly.

Fig. 5. Four-phase quarter-square SI multiplier circuit.

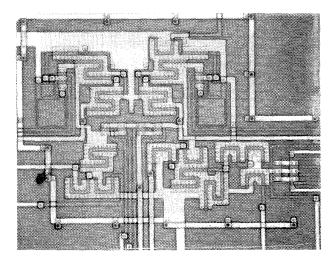

Fig. 6. Die photograph of the multiplier.

#### IV. EXPERIMENTAL RESULTS

Fig. 6 shows the die photograph of the multiplier. It occupies a 100  $\times$  75  $\mu$ m<sup>2</sup> chip area in a 2.4- $\mu$ m CMOS process. The input currents as well as the output currents were measured by means of a 16-b ADC. The output node was held at 1.6 V during measurements using an operational amplifier. The measurements were performed with a clock frequency of 2.5 MHz, corresponding to 0.625 million multiplications per second. Fig. 7(a) shows the transfer curve and Fig. 7(b) shows the absolute error, compared to the expected transfer characteristic  $I_{\text{out}} = aI_xI_y + b$  with a = 4980 A<sup>-1</sup> and  $b = 4.022 \,\mu$ A. The input current range is from -40 to 40  $\mu$ A, the maximum output current is 4.8  $\mu$ A. The total nonlinearity, defined as the absolute error divided by the maximum output swing, is 0.94%. This value is similar to

Fig. 7. Measured performances (a) output current  $(\mu A)$  versus input current  $I_x$   $(\mu A)$  and (b) absolute error  $(\mu A)$  versus input current for different currents  $I_y$ .

(b)

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 31, NO. 9, SEPTEMBER 1996

the simulated performance in [8] and measured performance of [9] but obtained at a 3.3 V power supply voltage instead of 5 V. The power dissipation for maximum input currents is 0.3 mW.

Continuous-time multipliers use several squares and their accuracy depends on the matching of these squarers. Here this matching problem is avoided by using memory cells to store intermediate results. Because this is the first attempt at designing a multiplier in SI technique, we cannot compare this design to similar ones. Its -3-dB bandwidth is much lower than continuous-time multipliers and is approximately 100 kHz. Besides the low nonlinearity, also the compactness of the circuit can be advantageous in applications. Experiments show that increasing the conversion time by a factor ten, the nonlinearity reduces to 0.2% which is of potential interest in applications where speed is not the main design issue.

#### V. CONCLUSION

In this paper, an SI multiplier is described. It consists of only one current squarer and two accurate SI memory cells. It is based on a slightly altered version of the "quarter square" principle. In this way, the problem of matching of two current squarers is circumvented, and furthermore, a number of nonidealities of the building blocks are canceled, resulting in an accurate multiplier in the current domain. Experimental results have been given to demonstrate the feasibility of the multiplier in SI design techniques. Advantages include a 3.3 V power supply voltage and a die area of  $100 \times 75 \ \mu m^2$ .

#### ACKNOWLEDGMENT

The authors wish to thank the reviewers for helpful comments. Further, they wish to thank P. Klessens for generating the layout and O. Stoelinga for setting up the measure equipment.

#### REFERENCES

- J. B. Hughes, I. C. Macbeth, and D. M. Pattullo, "Second generation switched-current signal processing," in *Proc. IEEE Int. Symp. Circuits* Systems, May 1990, pp. 2805–2808.

- [2] D. M. W. Leenaerts, A. J. Leeuwenburgh, and G. G. Persoon, "High performance SI memory cell," *IEEE J. Solid-Sate Circuits*, vol. 29, no. 11, pp. 1404–1407, 1994.

- [3] C. Toumazou, J. B. Hughes, and N. C. Battersby, "Switched-currents an analogue technique for digital technology," *IEEE Circuits and Systems Series*. London: Peregrinus, 1993, vol. 5.

- [4] E. Seevinck and R. J. Wiegerink, "Generalized translinear circuit principle," *IEEE J. Solid-State Circuits*, vol. 26, pp. 1098–1102, Aug. 1991.

- [5] L.-Y. Song, "A VLSI design methodology for artificial neural networks," Ph.D. dissertation, Univ. of Waterloo, Ontario, 1993.

- [6] D. H. Sheingold, Nonlinear Circuits Handbook. Norwood, MA: Analog Devices, 1974.

- [7] M. S. Piedade and A. Pinto, "A new multiplier-divider circuit based on switched capacitor data converters," in *Proc. IEEE Int. Symp. Circuits* and Systems, May 1990, pp. 2224–2227.

- [8] R. J. Wiegerink, "Analysis and synthesis of MOS translinear circuits," Ph.D. dissertation, Univ. of Twente, Enschede, The Netherlands, 1992.

- [9] S. Liu and C. Chang, "CMOS analog divider and four-quadrant multiplier using pool circuits," *IEEE J. Solid-Sate Circuits*, vol. 30, no. 9, pp. 1025–1029, 1995.

[10] K. Bult and H. Wallinga, "Analog CMOS computational circuits," in

- 10] K. Bult and H. Wallinga, "Analog CMOS computational circuits," in Proc. ESSCIRC'86, Sept. 1986, pp. 119–121.

- [11] H. J. Reitsma, "Development of a 12 bit digital to analogue converter using switched current techniques," Master thesis, Eindhoven University of Technology, Aug. 1993.