# Purdue University Purdue e-Pubs

Department of Electrical and Computer Engineering Faculty Publications Department of Electrical and Computer Engineering

January 2008

# A 32kb 10T subthreshold SRAM array with bitinterleaving and differential read scheme in 90nm CMOS

Ik Joon Chang

Jae-Joon Kim

Sang Phill Park

Kaushik Roy

Follow this and additional works at: http://docs.lib.purdue.edu/ecepubs

Chang, Ik Joon; Kim, Jae-Joon; Park, Sang Phill; and Roy, Kaushik, "A 32kb 10T subthreshold SRAM array with bit-interleaving and differential read scheme in 90nm CMOS" (2008). *Department of Electrical and Computer Engineering Faculty Publications*. Paper 9. http://dx.doi.org/http://dx.doi.org/10.1109/ISSCC.2008.4523220

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

## **ISSCC 2008 / SESSION 21 / SRAM / 21.7**

### 21.7 A 32kb 10T Subthreshold SRAM Array with Bit-Interleaving and Differential Read Scheme in 90nm CMOS

Ik Joon Chang<sup>1</sup>, Jae-Joon Kim<sup>2</sup>, Sang Phill Park<sup>1</sup>, Kaushik Roy<sup>1</sup>

<sup>1</sup>Purdue University, West Lafayette, IN, <sup>2</sup>IBM T.J. Watson, Yorktown Heights, NY

For robust subthreshold SRAMs, 8T or 10T subthreshold SRAMs based on single-ended read sensing have been proposed [1-3]. While the schemes in [1-3] improve the read stability and writability significantly, their single-ended sensing methods still suffer from reduced bitline swing due to bitline noise. In addition, the previous schemes do not have efficient bit-interleaving in the column structure, which is critical to cope with multiple-bit soft errors [4]. In this paper, we present a 10T subthreshold SRAM with efficient bit-interleaving for soft-error immunity and fully differential read for better stability.

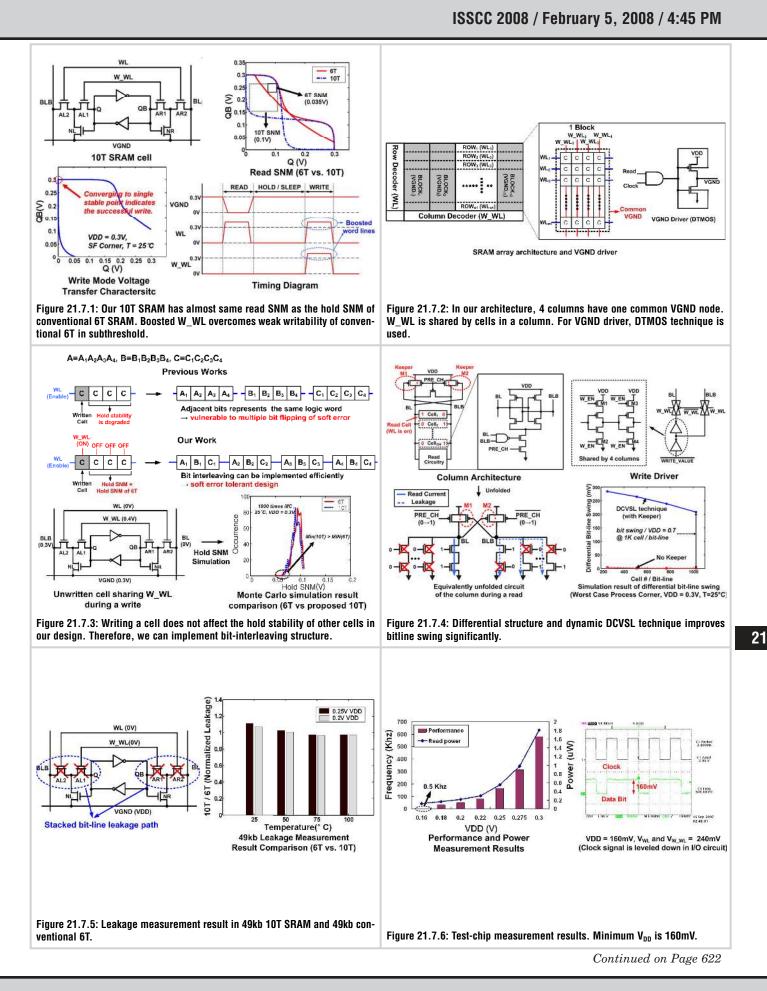

Figure 21.7.1 shows the 10T SRAM cell. In read mode, WL is enabled and VGND is forced to ground while W\_WL remains disabled as shown in the timing diagram. Since the disabled W\_WL makes the nodes 'Q' and 'QB' isolated from the bitlines during the read mode, the read static noise margin (SNM) of this 10T  $\overset{\bullet}{\mathrm{SRAM}}$ is almost same as the hold SNM of conventional 6T SRAM. During the write mode, both WL and W\_WL are enabled to transfer the write data to cell node from the bitline. To compensate weak writability,  $V_{WL}$  and  $V_{W WL}$  are boosted by 33% of 0.3V  $V_{DD}$ . Since the gate input boosting overwhelms the sizing effect in the subthreshold region, we obtain strong writability without incurring a large area penalty in spite of having series transistors. Figure 21.7.1 shows 100mV boosting gives good writability even in the worst-case process corner. To reduce the area overhead, four columns share a common VGND node (Fig. 21.7.2). The pull-down strength of VGND driver is degraded due to process variation, so the dynamic-threshold MOS (DTMOS) technique is employed to mitigate this effect. The pull-down NMOS of the VGND driver is forward-biased during read, increasing the pull-down drive current.

As shown in the array structure in Fig. 21.7.2, WL is shared by the cells in a row and W\_WL is shared by the cells in a column. Since both WL and W WL must be enabled to write a cell, each column is selected individually depending on the value of W\_WL. This unique feature can be used for bit-interleaving to reduce the multiple-bit soft errors. Soft-error rate is expected to be significantly higher in subthreshold SRAM than that in super-threshold SRAM due to the lower  $V_{DD}$  and the smaller gate capacitance in subthreshold region. Previous subthreshold SRAMs [1,2] do not allow bit-interleaving because the cells that are in the unselected columns but share the wordline with the selected cells experience significant stability degradation during write mode. Therefore, a logic word is composed of all cells sharing a wordline so that the design is exposed to multiple bit soft errors. (Fig. 21.7.3) On the other hand, in our technique, writing a cell does not affect hold stability of other cells along the same wordline since W\_WL is shared by the cells in a column. When the W\_WL of a column is raised for writing a cell, W\_WLs of other columns still stay at 0V. Hence, the rise of WL does not affect hold stability of unwritten cells sharing the WL. Monte-Carlo simulation results, shown in Fig. 21.7.3, show that the hold stability of unwritten cells sharing W\_WL does not degrade during write. Despite the influence of enabled W\_WL and VGND, the worst hold SNM shows improvement of 25% compared to conventional 6T SRAM since the pull-up of NMOS transistors (NL or NR) complements weak PMOS at FS process corner, which is the worst case corner for hold stability. Since the hold stability in adjacent cells is not affected during write, bitinterleaving is efficiently implemented in our design, achieving soft-error tolerance with conventional ECC [4].

Another characteristic of our cell is the fully differential read, which improves the bitline noise immunity significantly during read. The column structure in Fig. 21.7.4 explains the read mechanism. When read begins, the wordline of the accessed SRAM cells is raised and precharge signal (PRE\_CH) is disabled. Depending on the data value of the accessed cell, one of the precharged bitlines (BL or BLB) starts discharging. The unfolded circuit diagram, which is equivalent to a column with the worst, case leakage condition, is also shown in Fig. 21.7.4. During the read, the leakage current through unselected cells (storing complementary value to the accessed cell) impedes a successful read. In single-ended READ structure, leakage makes it difficult to distinguish a logic high and low from the developed bitline voltage [3]. Since a differential read does not solely depend on the trip voltage of an inverter, it is more tolerant to bitline leakage noise. We employ the dynamic DCVSL technique to further increase leakage tolerance. In Fig. 21.7.4, the discharge of BL turns on keeper M2 and bitline leakage current in BLB is compensated by the drive current of M2. The graph in Fig. 21.7.4 shows the effectiveness of the DCVSL differential read. The simulation results show that  $0.7V_{DD}$  bitline differential develops for 1024 cells per bitline at 25°C.

In order to achieve larger bitline swing, read circuitry using crosscoupled inverters is included per each column. The footer transistor M0 of Fig. 21.7.4 prevents malfunction induced by intradie variation inside the read circuitry. Drive current flowing through M0 is almost negligible before there is significant discharging from a bitline, excluding the influence of intra-die variation inside the read circuitry. Leakage current through a write driver reduces bitline swing, so to reduce this leakage, stacking transistors are employed (Fig. 21.7.4). Since a boosted signal is used for W\_WL and W\_EN, degradation of write stability resulting from IR-drop of the stacked NMOS structure in the write driver is almost negligible.

An alternative 10T cell with differential bitlines can also be implemented by simply adding two read transistors and the complementary bitline to the single-ended-read 8T cell [2]. That implementation, however, does not allow bit-interleaving. The unique characteristic of our cell is to allow both bit-interleaving and differential read with the same number of devices (10T) in a cell.

The SRAM test-chip is fabricated in a 90nm CMOS technology (Fig. 21.7.7). For leakage comparison, 49kb arrays are implemented for both the conventional 6T cell and our 10T cell. Fig. 21.7.5 shows that the leakage power consumption of our SRAM is close to that of the 6T cell (between  $0.96\times$  and  $1.1\times$ ) even though it has extra transistors in a cell. This is because the subthreshold leakage from the bitline to the cell node is drastically reduced by the stacking of devices in the leakage path. For performance and power measurement, a 32kb (256×128) SRAM array is implemented using the cell. As shown in Fig. 21.7.6, the design operates at 31.25kHz with a 0.18V supply and 33% boosted WL and W\_WL. With more aggressive wordline boosting of 80mV, the V<sub>DD</sub> scales down to 0.16V. At 0.16V V<sub>DD</sub>, the operating frequency is 500Hz and power consumption is 0.123 $\mu$ W.

#### Acknowledgement:

This research iss sponsored in part by SRC (1629.001) and by DARPA. We thank Keejong Kim for integration of the design into a multi-project chip; Hyun-Joong Kim for helping wire-bonding; and Samsung Scholarship Foundation.

#### References:

B.H.Calhoun, A. Chandrakasan, "A 256kb Sub-Threshold SRAM in 65nm CMOS", ISSCC Dig. Tech. Papers, pp.628-629, Feb. 2006.

N. Verma, A. Chandrakasan, "A 65nm 8T Sub-V<sub>t</sub> SRAM Employing

[2] N. Verma, A. Chandrakasan, "A 65nm 8T Sub-V<sub>t</sub> SRAM Employing Sense-Amplifier Redundancy", ISSCC Dig. Tech. Papers, pp.328-329, Feb. 2006.

[3] T. Kim, J. Liu, J. Keane, C. H. Kim, "A High-Density Subthreshold SRAM with Data-Independent Bitline Leakage and Virtual Ground Replica Scheme", *ISSCC Dig. Tech. Papers*, pp.330-331, Feb. 2006.

[4] J. Maiz, S. Hareland, K. Zhang, and P. Armstrong, "Characterization of Multi-bit Soft Error Events in Advanced SRAMs", *IEDM Dig. Tech.Papers*, pp.21.4.1-21.4.4, Dec. 2003.

978-1-4244-2011-7/08/\$25.00 ©2008 IEEE

DIGEST OF TECHNICAL PAPERS • 389

Please click on paper title to view a Visual Supplement.

# **ISSCC 2008 PAPER CONTINUATIONS**

| Technology   90nm 8-metal CMOS technology     Chip size   4 x 2 mm²     VCC min   0.16V, 500hz @ 256 cells/bit-line     Performance   166Khz @ 0.25V VDD, 25°C     Leakage Current (49kb)   1.4µA @ 0.25V, 25°C |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC min     0.16V, 500hz @ 256 cells/bit-line       Performance     166Khz @ 0.25V VDD, 25°C       Leakage Current (49kb)     1.4μA @ 0.25V, 25°C                                                               |

| Performance     166Khz @ 0.25V VDD, 25°C       Leakage Current (49kb)     1.4μA @ 0.25V, 25°C                                                                                                                   |

| Leakage Current (49kb) 1.4μΑ @ 0.25∨, 25°C                                                                                                                                                                      |

| Figure 21.7.7: Die micrograph and layout.                                                                                                                                                                       |

|                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                 |

Please click on paper title to view a Visual Supplement.