## An Ultra-Low-Quiescent-Current Dual-Mode Digitally-Controlled Buck Converter IC for Cellular Phone Applications

by

Jinwen Xiao

B.E. (Tsinghua University) 1997

A dissertation submitted in partial satisfaction of the

requirements for the degree of

**Doctor of Philosophy**

in

**Engineering-Electrical Engineering** and Computer Science

in the

**GRADUATE DIVISION**

of the

UNIVERSITY of CALIFORNIA, BERKELEY

**Committee in charge:**

Professor Seth R. Sanders, Chair Professor Ali M. Niknejad Professor Paul K. Wright

**Fall 2003**

| Chair | Date |

|-------|------|

|       |      |

|       |      |

|       |      |

|       | Date |

|       | Dute |

|       |      |

|       |      |

|       |      |

|       | Date |

|       |      |

The dissertation of Jinwen Xiao is approved:

University of California, Berkeley

Fall 2003

## An Ultra-Low-Quiescent-Current Dual-Mode Digitally-Controlled Buck Converter IC for Cellular Phone Applications

Copyright Fall 2003

by

Jinwen Xiao

#### **Abstract**

An Ultra-Low-Quiescent-Current Dual-Mode Digitally-Controlled Buck Converter IC for Cellular Phone Applications

by

### Jinwen Xiao

Doctor of Philosophy in Engineering-Electrical Engineering and Computer Science

University of California, Berkeley

Professor Seth R. Sanders, Chair

This dissertation presents a low-quiescent-current dual-mode digitally-controlled buck converter IC for cellular phone applications. In cellular phones, the load current demanded by the on-board circuitry varies from below 0.1 mA up to a few hundred mA, reflecting operation in standby and active (talk) modes. Thus, high efficiency over a wide load range is of high priority for power management units, since the total energy is limited by the capacity of a single cell Li-ion battery. A dual-mode buck converter IC, implemented with a 0.25- $\mu$ m CMOS process, takes 2 mm<sup>2</sup> active area and demonstrates equal or better regulation performance compared to state-of-the-art analog switchers. A very low quiescent current of 4  $\mu$ A is achieved experimentally, resulting in a more than three-fold reduction compared to

the leading state-of-the-art analog controllers. Consequently, a high efficiency, exceeding 70%, is achieved over a wide load range between 0.1 and 400 mA.

Professor Seth R. Sanders Dissertation Committee Chair To my parents,

your love means the whole world to me.

### Acknowledgements

First of all, I would like to express my gratitude to Professor Seth Sanders, for his patient guidance through my five years of graduate school life, for his unconditional support to my work, for his uncountable help in technical writing, and for being a wonderful role model. He is the most intelligent and unselfish person I have ever known, and I truly feel very fortunate to have had the opportunity to be his student.

Along with Professor Sanders, I would like to thank Professors Ali Niknejad, Borivoje Nikolic, and Paul Wright for serving on my qualifying exam committee. I would also like to thank Professors Sanders, Niknejad, and Wright for reading this thesis.

I would also like to thank my colleagues in Professor Sanders' group for their friendship and help over the years. Perry Tsao helped me many times on computer related problems with great patience. Angel Peterchev provided not only countless valuable technical discussions and ideas, but also shared his insight into art, and his talent for painting. Jianhui Zhang and his wife Rui Chen were a great couple to discuss any issue with. Artin Der Minassians, Matthew Senesky, Gabriel Eirea, and Wei Wang made 341 Cory Hall a fun place to work.

I greatly value the friendship and support from two other residents in 341 Cory Hall, Lixia Zhou and Jin Wang. Lixia always encouraged me when I was feeling down. She was also a very competitive company in swimming. Jin Wang helped me with valuable discussions in the area of communications and DSP, with incredible patience.

I also appreciate Tao Yang, a sincere friend since college, who provided important help

when I needed it most. Thanks to Zhanfeng Jia, Xiaotian Sun, and Jihua Huang, their friendship through the years made Berkeley a much more enjoyable place to live. I would also like to thank Weidong Cui, who helped me to gain so much insight about life. Mei Luo treated me with "Si Chuan Huo Guo" many times. Although most of the time the food was so spicy that I had to go home with a half-empty stomach, I am grateful for all the exciting conversations during the meals. Xinyan Deng is the most interesting friend I have ever known. It is unbelievable how much laugh we had together, we could have great fun even when watching the most boring movie "Northern Light". Hanging out with her, I came to realize that there were so many beautiful things in the world that I did not notice before.

Special thanks to my parents Baozhu Xiao and Guifeng Zhao, and my brother Xiang Xiao and my sister-in-law Ling Pang, for their love and support. I could never made this far without it.

This work was supported by Linear Technology, Fairchild Semiconductor, National Semiconductor, and California Micro Program. The fabrication was performed by National Semiconductor.

## **Contents**

| Li |                                                                |         | ix                                                             |    |

|----|----------------------------------------------------------------|---------|----------------------------------------------------------------|----|

| Li |                                                                |         | xii                                                            |    |

| 1  | Intr                                                           | oductio | n                                                              | 1  |

|    | 1.1                                                            | Motiva  | ation                                                          | 2  |

|    | 1.2                                                            | Resear  | rch Goals and Contributions                                    | 3  |

|    | 1.3                                                            | Thesis  | Organization                                                   | 4  |

| 2  | Ove                                                            | rview o | f DC-DC Converters for Cellular Phone Applications             | 6  |

|    | 2.1                                                            | Overv   | iew of DC-DC Converters for Portable Applications              | 7  |

|    |                                                                | 2.1.1   | Increasing Battery run-time with voltage regulators            | 7  |

|    |                                                                | 2.1.2   | Design Challenges for Portable Applications                    | 10 |

|    | 2.2                                                            | Digita  | l Control for DC-DC Converters                                 | 11 |

| 3  | System Design of Controller IC for Cellular Phone Applications |         |                                                                | 12 |

|    | 3.1                                                            | Overv   | iew of Buck Converter Operation                                | 13 |

|    |                                                                | 3.1.1   | Basics of Buck Converter                                       | 13 |

|    |                                                                | 3.1.2   | Continuous Conduction Mode                                     | 13 |

|    |                                                                | 3.1.3   | Discontinuous Conduction Mode                                  | 18 |

|    | 3.2                                                            | PWM     | Mode Power Loss Analysis                                       | 20 |

|    |                                                                | 3.2.1   | Conduction Loss                                                | 20 |

|    |                                                                | 3.2.2   | Switching Loss                                                 | 21 |

|    |                                                                | 3.2.3   | Stray Inductance Loss                                          | 28 |

|    |                                                                | 3.2.4   | Controller Quiescent Power                                     | 28 |

|    |                                                                | 3.2.5   | PWM Mode Efficiency                                            | 28 |

|    | 3.3                                                            | PFM I   | Mode Power Loss Analysis                                       | 30 |

|    |                                                                | 3.3.1   | Conduction Loss, Switching Loss, and Stray Inductive Switching |    |

|    |                                                                |         | Loss in PFM Mode                                               | 31 |

|    |                                                                | 3.3.2   | PFM Controller Quiescent Power                                 | 32 |

|   | 3.4  |                                   | C Converter System Design                     |    |  |  |

|---|------|-----------------------------------|-----------------------------------------------|----|--|--|

|   |      | 3.4.1                             | Digital Controller System Specifications      |    |  |  |

|   |      | 3.4.2                             | Output Filter Design                          |    |  |  |

|   |      | 3.4.3                             | Power Train Design                            |    |  |  |

|   |      | 3.4.4                             | Summary                                       | 34 |  |  |

| 4 | Arcl |                                   | re of the Dual-Mode Buck Converter IC         | 35 |  |  |

|   | 4.1  | -                                 | m Architecture                                | 36 |  |  |

|   | 4.2  |                                   | Mode                                          | 38 |  |  |

|   |      | 4.2.1                             |                                               | 38 |  |  |

|   |      | 4.2.2                             | ADC and DPWM                                  | 39 |  |  |

|   |      | 4.2.3                             | Digital Compensation Network                  | 40 |  |  |

|   |      | 4.2.4                             | Summary of PWM Mode                           | 42 |  |  |

|   | 4.3  | PFM N                             |                                               | 42 |  |  |

|   |      | 4.3.1                             | Ultra-Low-Power PFM Architecture              | 42 |  |  |

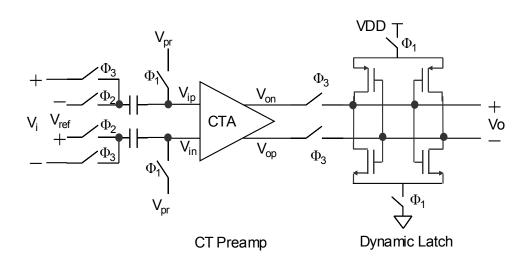

|   |      | 4.3.2                             | Ultra-Low-Power Comparator Design             | 44 |  |  |

|   | 4.4  | Voltag                            | ge Compatibility                              | 54 |  |  |

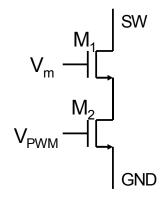

|   |      | 4.4.1                             | Cascoded Power Train                          | 54 |  |  |

|   |      | 4.4.2                             | Internal Power Management                     | 55 |  |  |

|   |      | 4.4.3                             | Internal Regulators                           | 57 |  |  |

|   |      | 4.4.4                             | Voltage Interface: Level Shifters             | 59 |  |  |

| 5 | Ana  | log-to-l                          | Digital Converter Based on Ring Oscillators   | 62 |  |  |

|   | 5.1  | Windo                             | owed ADC                                      | 63 |  |  |

|   | 5.2  | Ring-A                            | ADC                                           | 64 |  |  |

|   |      | 5.2.1                             | Frequency-supply current dependency           | 64 |  |  |

|   |      | 5.2.2                             | Ring-ADC Architecture                         | 67 |  |  |

|   |      | 5.2.3                             | Output Range and Monotonicity of the Ring-ADC | 69 |  |  |

|   |      | 5.2.4                             | Resolution of Ring-ADC                        | 73 |  |  |

|   |      | 5.2.5                             | Linearity of Ring-ADC                         | 73 |  |  |

|   |      | 5.2.6                             | Level Shifters                                | 74 |  |  |

|   |      | 5.2.7                             | Implementation of Ring-ADC                    | 75 |  |  |

| 6 | Digi | Digital Pulse Width Modulation 80 |                                               |    |  |  |

|   | 6.1  | Overv                             | iew of Digital PWM Generation Schemes         | 81 |  |  |

|   |      | 6.1.1                             | Dither and Digital PWM                        | 81 |  |  |

|   |      | 6.1.2                             | Overview of DPWM Schemes                      | 81 |  |  |

|   | 6.2  | Count                             | er-comparator DPWM                            | 83 |  |  |

|   |      | 6.2.1                             | Counter-comparator DPWM                       | 83 |  |  |

|   |      | 6.2.2                             | Fast Flip-flop Design                         | 83 |  |  |

|   | 6.3  | Ring-I                            | MUX DPWM                                      | 89 |  |  |

|   | 6.4  |                                   | arison between the Two DPWM Schemes           | 91 |  |  |

| 7  | The   | rmal Noise and Ring Oscillator Stability                             | 94  |

|----|-------|----------------------------------------------------------------------|-----|

|    | 7.1   | Oscillation Patterns in Ring Oscillators                             | 95  |

|    | 7.2   | Thermal Noise and Clock Jitter in Ring Oscillators                   | 99  |

|    | 7.3   | Thermal Noise and Stability of Ring Oscillator                       | 100 |

| 8  | Exp   | perimental Results and Conclusions                                   | 102 |

|    | 8.1   | Experimental Results                                                 | 103 |

|    | 8.2   | Comparisons and Conclusions                                          | 109 |

|    | 8.3   | Summary of Research Contributions                                    |     |

| Bi | bliog | raphy                                                                | 112 |

| A  | Out   | put Voltage Ripple Calculation for Buck Converter in Continuous Con- |     |

|    | duct  | tion Mode                                                            | 116 |

## **List of Figures**

| 3.1 | (a) Buck converter schematic, (b) switching node voltage waveform $V_x$ at steady-state                                                                      | 14 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | (a) Synchronous converter, (b) voltage and current waveforms in continu-                                                                                     | 17 |

|     | ous conduction mode                                                                                                                                          | 15 |

| 3.3 | Converter output voltage ripple with different output capacitor time con-                                                                                    |    |

|     | stant values                                                                                                                                                 | 17 |

| 3.4 | (a) Schematic of a conventional buck converter, (b) switching node voltage and inductor current waveforms in discontinuous conduction mode                   | 19 |

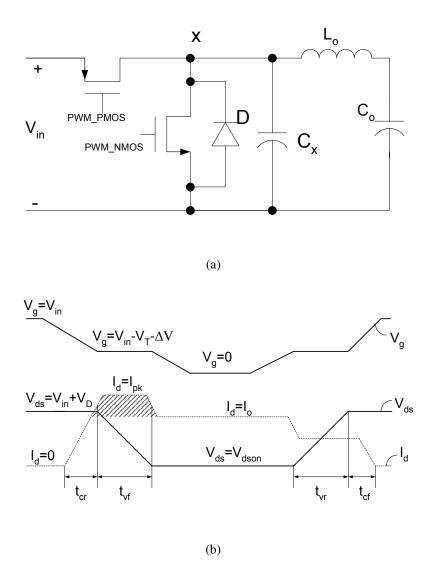

| 3.5 | (a) Schematic of buck converter with parasitic capacitor $C_x$ at the switching node, (b) hard switching transient waveforms in PMOS                         | 23 |

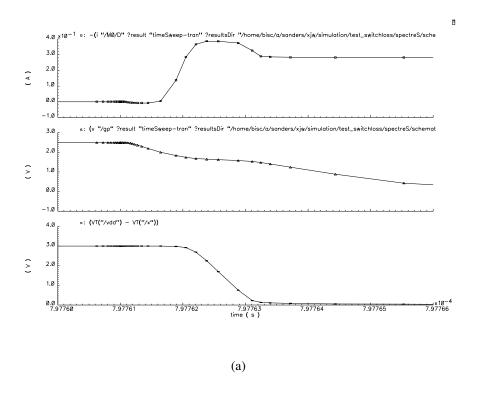

| 3.6 | Simulated transient waveforms of PMOS, the top curve being $I_d$ , middle curve $-V_q$ , bottom curve $-V_{ds}$ in each sub-figure (a) turning-on transient, |    |

|     | (b) turning-off transient                                                                                                                                    | 24 |

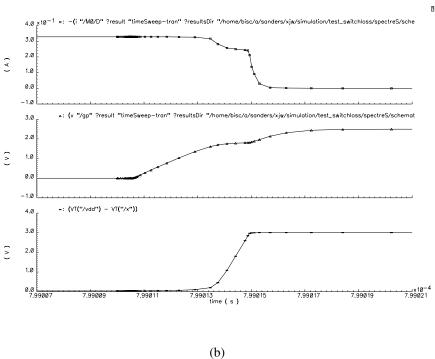

| 3.7 | Efficiency and loss versus $I_o$ , switching loss $P_s$ and conduction loss $P_c$ is                                                                         |    |

|     | each normalized to input power                                                                                                                               | 29 |

| 3.8 | Voltage and current waveforms in buck converter in PFM mode                                                                                                  | 31 |

| 4.1 | (a) System diagram of a digitally-controlled buck converter, (b) block diagram of digitally controlled buck converter IC for cellular phone applica-         |    |

| 4.2 | tions                                                                                                                                                        | 37 |

|     | the signals, and the number in the bracket is the effective bits of resolution.                                                                              | 41 |

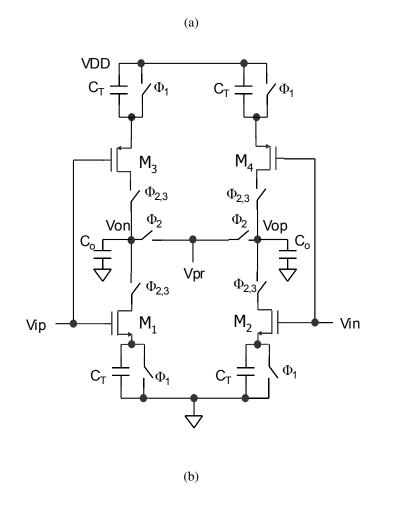

| 4.3 | Pseudo differential CT comparator, (a) CMOS CT preamplifier and dy-                                                                                          |    |

|     | namic latch, (b) schematic of the CT preamplifier                                                                                                            | 45 |

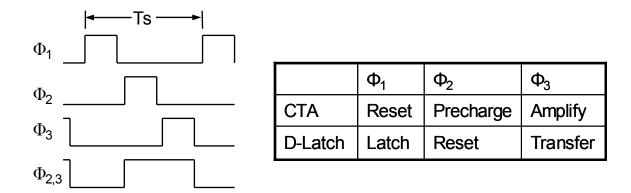

| 4.4 | Timing diagram of the pseudo differential CT comparator                                                                                                      | 46 |

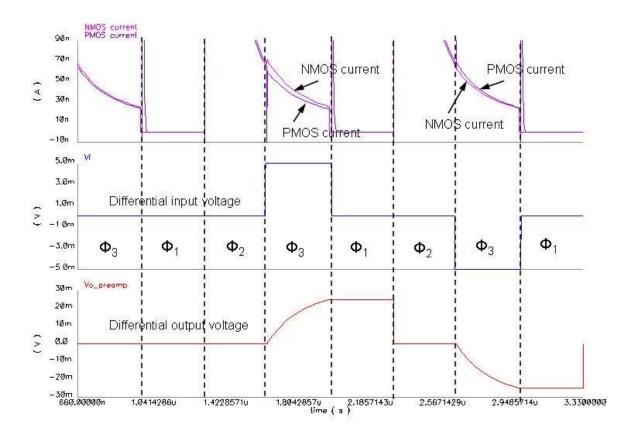

| 4.5 | Simulated waveforms of the pseudo differential CT preamplifier                                                                                               | 46 |

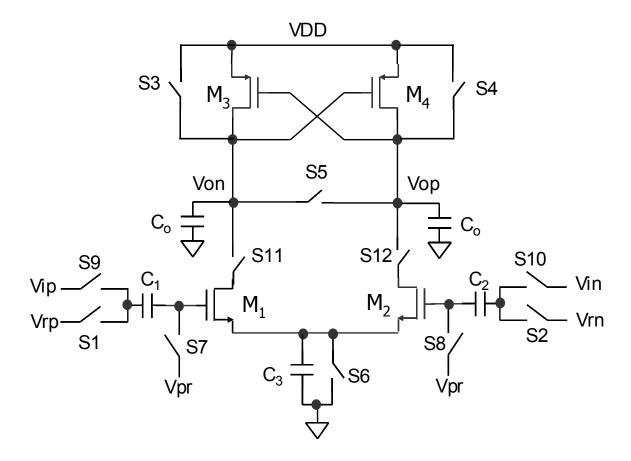

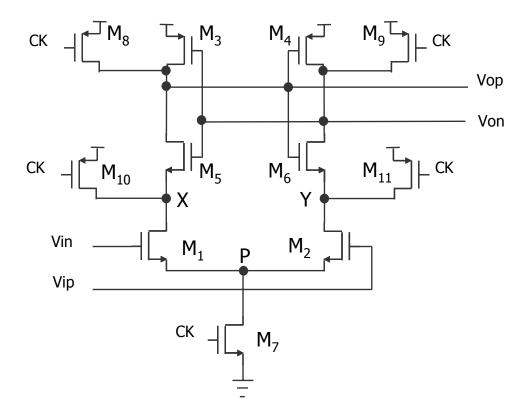

| 4.6 | Schematic of the differential zero-DC-current comparator                                                                                                     | 48 |

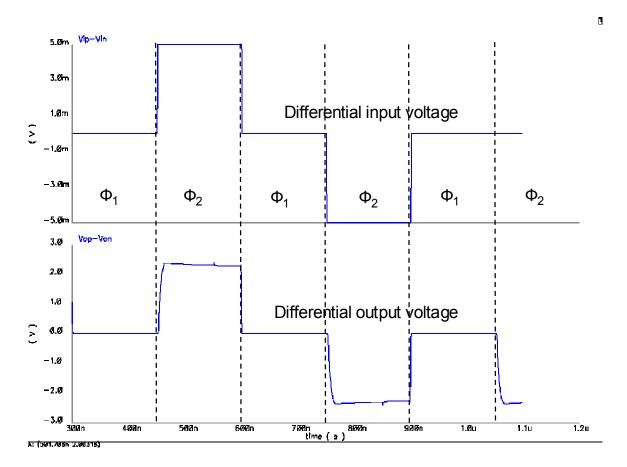

| 4.7 | Simulated waveforms of the differential zero-DC-current comparator                                                                                           | 49 |

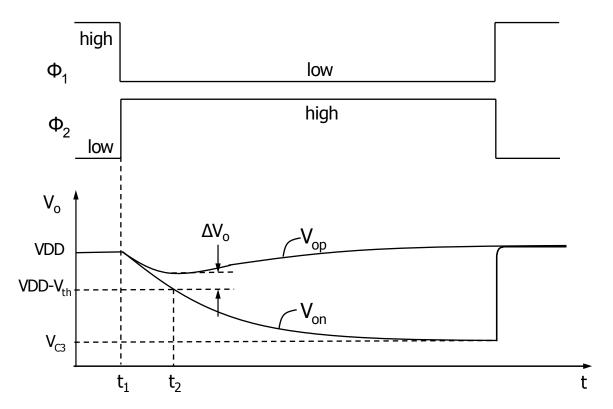

| 4.8  | Conceptual voltage waveforms at the output nodes in the differential zero-DC-current comparator.                                                                                                                                                                                                   | 50  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.9  | Schematic of zero-DC-biasing current comparator. [2]                                                                                                                                                                                                                                               | 52  |

|      | Cascode structure for low side switch                                                                                                                                                                                                                                                              | 55  |

|      | Block diagram of internal power management                                                                                                                                                                                                                                                         | 56  |

|      | Block diagram of internal voltage regulators (a) two linear regulators with different references, and the schematic of the amplifier used in the regulators, (b) two linear regulators with one reference and build-in threshold difference.                                                       | 58  |

| 4.13 | Schematic of a bootstrap circuit                                                                                                                                                                                                                                                                   | 59  |

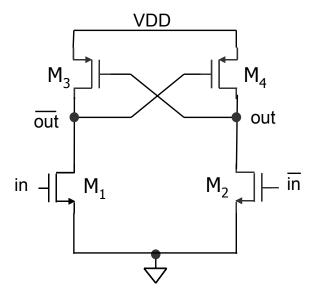

|      | Schematic of the level shifter                                                                                                                                                                                                                                                                     | 61  |

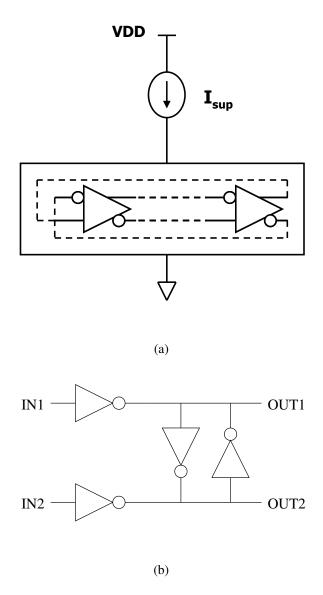

| 5.1  | (a)A 4-stage differential ring oscillator biased by a current source, (b) the delay cell in the differential ring oscillator                                                                                                                                                                       | 65  |

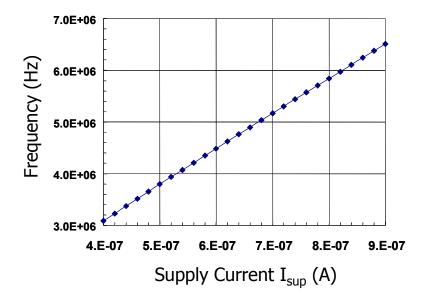

| 5.2  | Simulated frequency-current dependency of the ring oscillator in Fig. 5.1(a).                                                                                                                                                                                                                      | 66  |

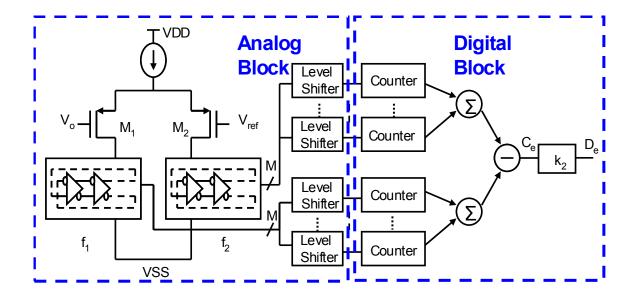

| 5.3  | Block diagram of ring-ADC                                                                                                                                                                                                                                                                          | 67  |

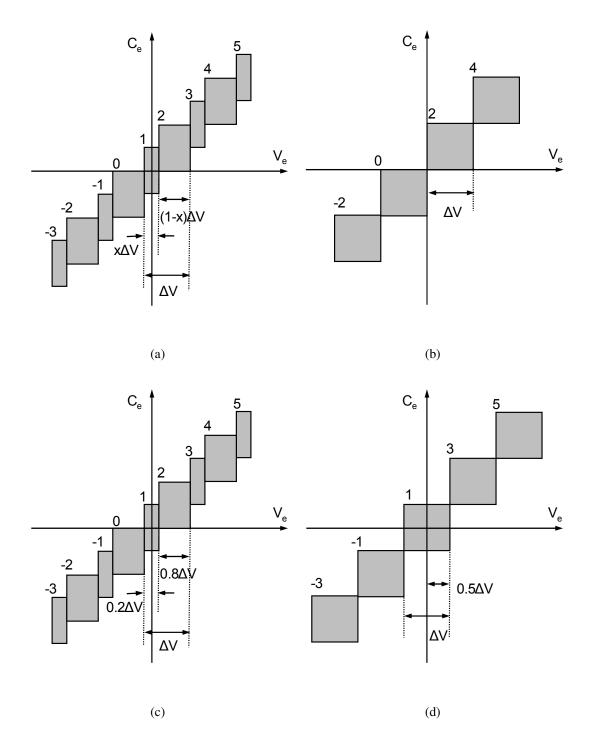

| 5.4  | Uncertainty range of output code $C_e$ (a) general form with $f_0 = (n+x)f_s$ , where n is an integer and $x \in [0,1)$ , and three special case with (b) x=0,                                                                                                                                     |     |

|      | (c)x=0.1, (d)x=0.5, respectively                                                                                                                                                                                                                                                                   | 71  |

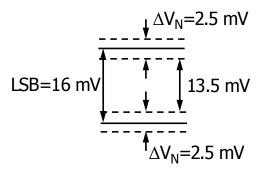

| 5.5  | The LSB of the ring-ADC and the input voltage range, $\Delta V_N$ , that may                                                                                                                                                                                                                       | / 1 |

| 5.5  | cause uncertainty in $C_e$                                                                                                                                                                                                                                                                         | 72  |

| 5.6  | Schematic of differential level shifter that converts signal swing from sub-                                                                                                                                                                                                                       | 12  |

| 5.0  | threshold to rail-to-rail                                                                                                                                                                                                                                                                          | 75  |

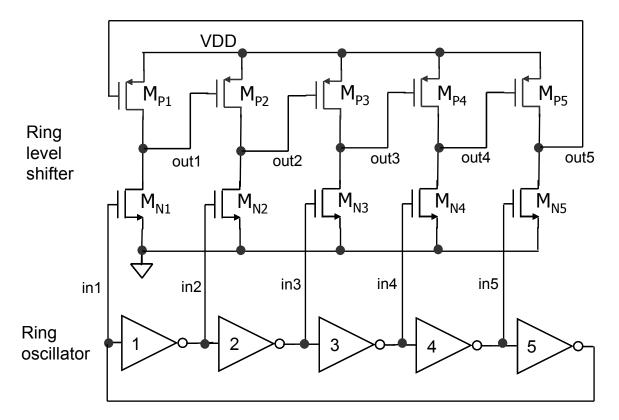

| 5.7  | Schematic of a ring level shifter connected to a 5-stage single-ended ring                                                                                                                                                                                                                         | 15  |

| 5.1  | oscillator                                                                                                                                                                                                                                                                                         | 76  |

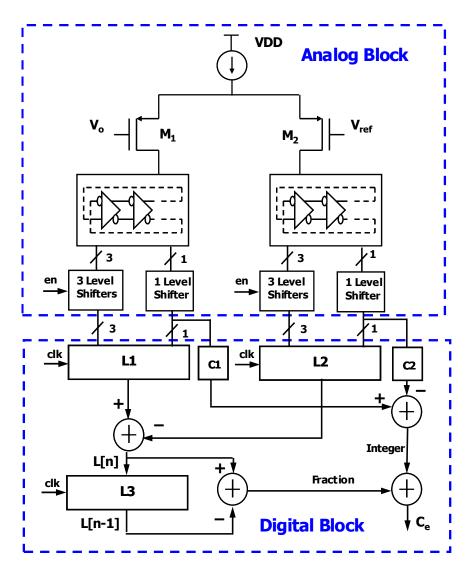

| 5.8  | Improved implementation of the ring-ADC. L1-L3 are latches, and C1 and                                                                                                                                                                                                                             | 70  |

| J.0  | C2 are counters                                                                                                                                                                                                                                                                                    | 79  |

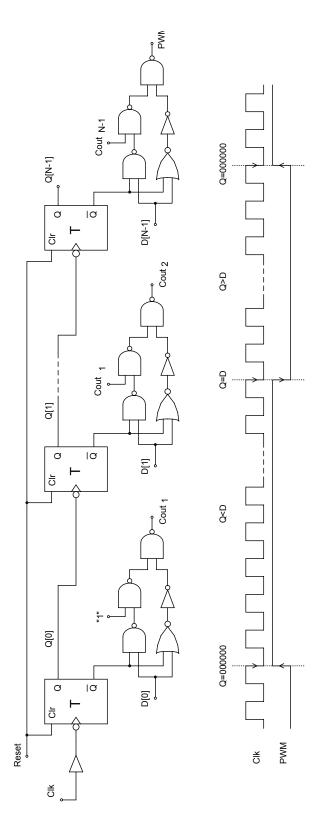

| 6.1  | Schematic of an N-bit counter-comparator DPWM with timing diagram                                                                                                                                                                                                                                  | 84  |

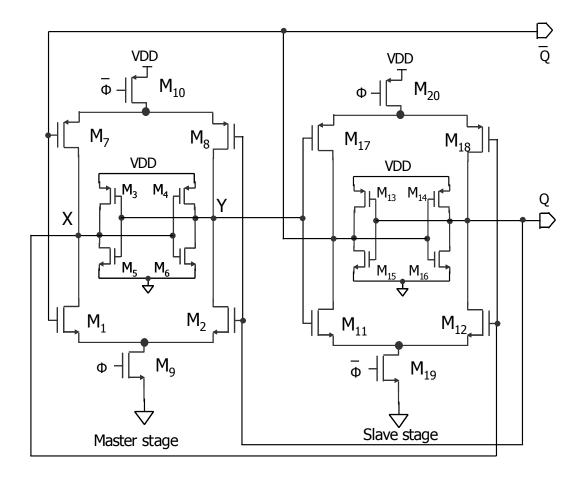

| 6.2  | Schematic of proposed master-slave T flip-flop                                                                                                                                                                                                                                                     | 85  |

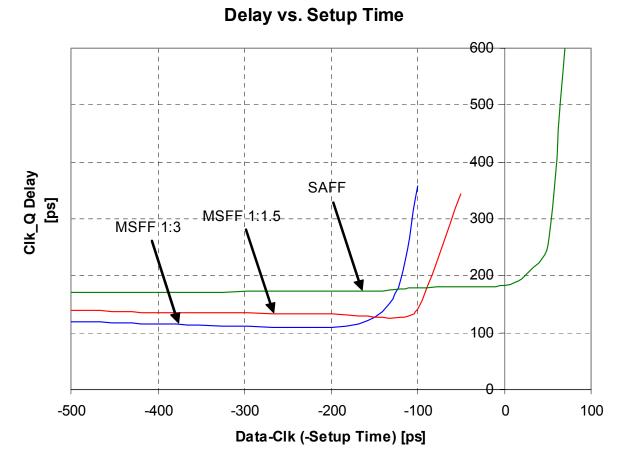

| 6.3  | Clk-Q delay vs. setup time in the MSFF and the SAFF. For the MSFF,                                                                                                                                                                                                                                 |     |

|      | delay with master-slave ratio of 1:3 and 1:1.5 are presented                                                                                                                                                                                                                                       | 87  |

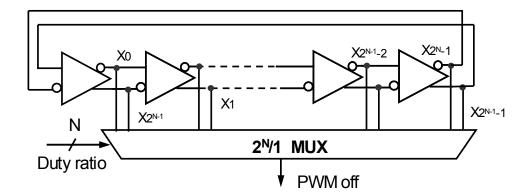

| 6.4  | Block diagram of an N-bit ring-MUX DPWM                                                                                                                                                                                                                                                            | 89  |

| 6.5  | Die photo of an 8-bit ring-MUX DPWM test chip in $0.25$ - $\mu$ m CMOS process.                                                                                                                                                                                                                    | 91  |

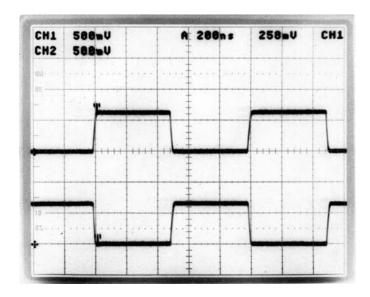

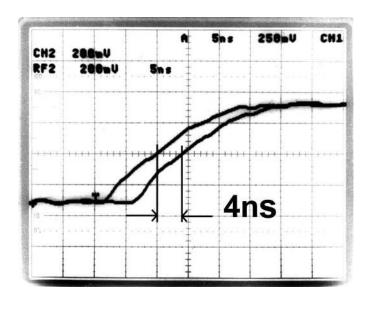

| 6.6  | Experimental waveforms of a 8-bit ring-MUX scheme (a) differential output of one ring oscillator delay stage, the two waveforms are taken from the complimentary taps of the same stage with the vertical scale being 500 mV/div, and horizontal scale being 200 ns/div, (b)resolution between two |     |

|      | adjacent outputs is 4 ns at 1 MHz oscillation frequency                                                                                                                                                                                                                                            | 92  |

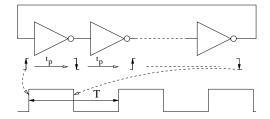

| 7.1  | Single-ended ring oscillator with fundamental oscillation mode                                                                                                                                                                                                                                     | 96  |

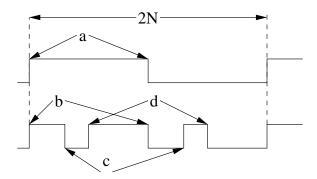

| 7.2 | Possible oscillation patterns in a ring oscillator. The upper waveform is             |   |

|-----|---------------------------------------------------------------------------------------|---|

|     | the fundamental pattern with the period of $2N$ , where "a" denotes the one           |   |

|     | pair of transition edge. The lower waveform is a pattern with 3 pairs of              |   |

|     | transition edges, where "b", "c" and "d" denote the three pairs of edges 9            | 7 |

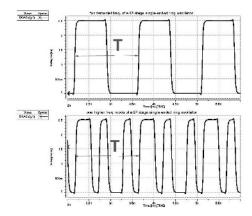

| 7.3 | Simulation results showing fundamental pattern and multi-transition pat-              |   |

|     | tern in a ring oscillator                                                             | 8 |

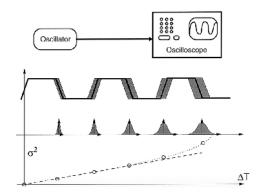

| 7.4 | Clock jitter increasing with time [3]                                                 |   |

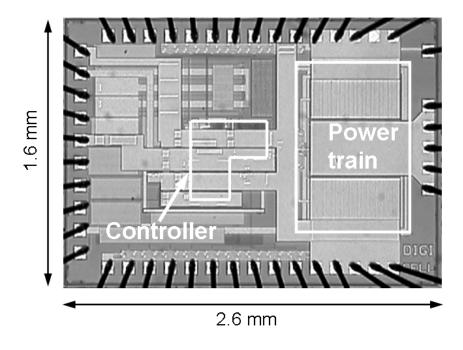

| 8.1 | Chip micrograph                                                                       | 3 |

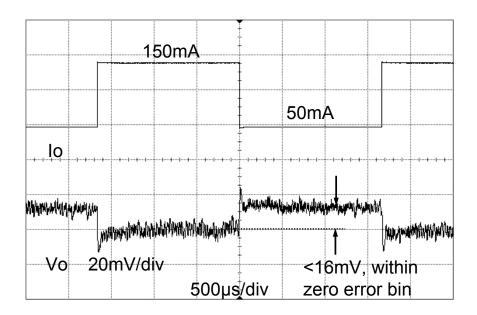

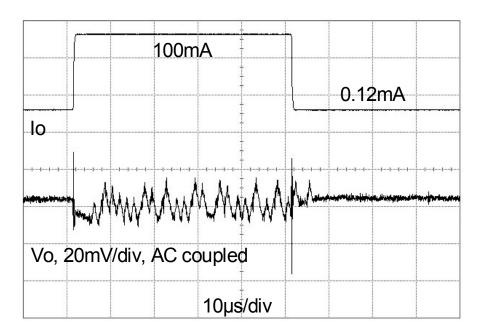

| 8.2 | Experimental load transient response with $V_{in}$ =3.2 V, $V_o$ =1.2 V, L=10 $\mu$ H |   |

|     | and C=47 $\mu$ F, (a) PWM mode response with $f_s$ =1 MHz, (b) PFM mode               |   |

|     | response with $f_{sample}$ =600 kHz                                                   | 5 |

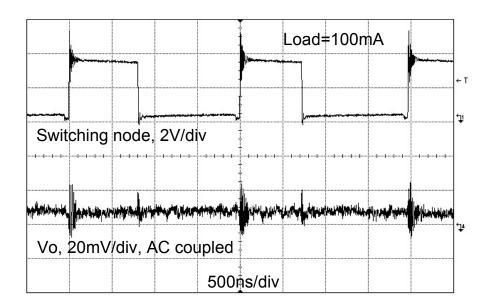

| 8.3 | Experimental steady-state response in PWM mode with $V_{in}$ =3.2 V, $V_o$ =1.2       |   |

|     | V, $I_o$ =100 mA, L=10 $\mu$ H, C=47 $\mu$ F, and $f_s$ =500 kHz                      | 6 |

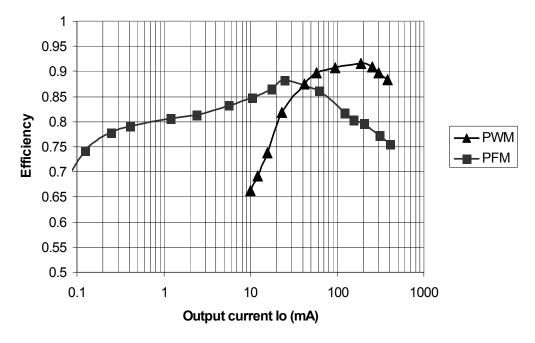

| 8.4 | Measured PWM and PFM mode buck converter efficiency vs output cur-                    |   |

|     | rent, with $V_{in}$ =4 V and $V_o$ =1.5 V                                             | 6 |

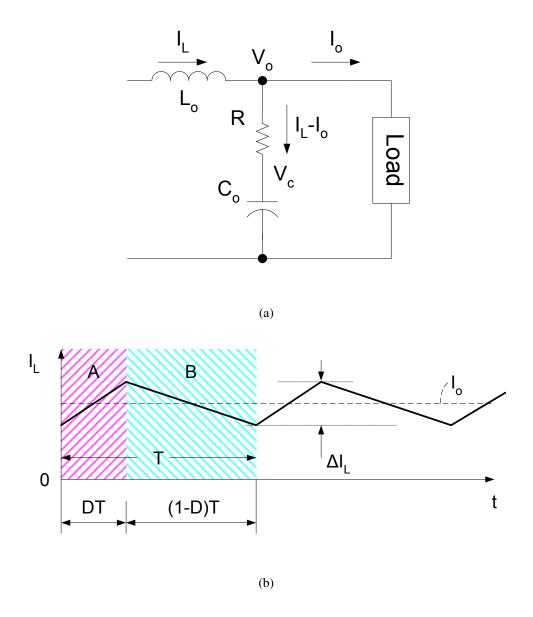

| A.1 | Buck converter in continuous conduction mode (a) schematic, (b) inductor              |   |

|     | current waveform                                                                      | 8 |

## **List of Tables**

| 3.1 | Dc-dc converter specifications for mobile phone and hand-held ratio applications. | 33  |

|-----|-----------------------------------------------------------------------------------|-----|

| 3.2 | Some system parameters derived for application specification in Table.3.1.        | 34  |

|     | PWM mode parameters                                                               |     |

|     | Comparison of the MSFF and the SAFF                                               |     |

| 8.1 | Digital controller IC pin description                                             | 104 |

| 8.2 | Chip performance summary                                                          | 108 |

| 8.3 | Comparison of LM2612 and the buck converter IC in this work                       | 109 |

## **Chapter 1**

## Introduction

### 1.1 Motivation

This dissertation presents a low-quiescent-current dual-mode digitally-controlled buck converter IC for cellular phone applications. In cellular phones, the load current demanded by the on-board circuitry varies from below 0.1 mA up to a few hundred mA, reflecting operation in standby and active (talk) modes. Thus, high efficiency over a wide load range is of high priority for power management units, since the total energy is limited by the capacity of a single cell Li-ion battery. A dual-mode buck converter IC, implemented with a 0.25- $\mu$ m CMOS process, takes 2 mm<sup>2</sup> active area and demonstrates equal or better regulation performance compared to state-of-the-art analog switchers. A very low quiescent current of 4  $\mu$ A is achieved experimentally, resulting in a more than three-fold reduction compared to the leading state-of-the-art analog controllers. Consequently, a high efficiency, exceeding 70%, is achieved over a wide load range between 0.1 and 400 mA.

In the evolution of modern portable electronic devices, digital data processing is taking an increasing role and a commensurate fraction of the power consumption. For example, in a second generation (2G) code division multiple access (CDMA) phone, the digital baseband and the memory circuit take about 10% of the total power that the handset chip set consumes. While in a third generation (3G) wide band CDMA (WCDMA) phone, this percentage is 30-50% of the overall power consumption, since functions associated with filtering and digital data streaming are now handled with digital circuitry. Thus, if the voltage regulator controller can be integrated on the same die with the digital system which it supplies, significant cost reduction can be expected. This digitally controlled buck con-

verter IC is implemented with a 0.25- $\mu$ m CMOS N-well process, and demonstrates the possibility of integrating digitally controlled power management unit with its load circuit on a digital process.

### 1.2 Research Goals and Contributions

This work is the first effort to introduce digital control for a mass market power management application — cellular phones. The main contributions of this work are:

- 1. An ultra-low-quiescent-current dual-mode digitally-controlled buck converter IC is designed. The measured quiescent current in PFM mode is  $4\mu$ A, which is a third of the leading state-of-the-art analog controllers [4]. Cellular phone standby time with each full charge of battery can be extended to up to three times, consequently.

- 2. An architecture employing internal power management is introduced to solve the conflict between the low voltage process and the high battery voltage in a cellular phone, enabling implementation of the digital controller in small feature size processes. A 0.25- $\mu$ m CMOS N-well process is used to implement the chip, demonstrating that the power management unit can be implemented in a digital process. This also indicates the possibility to integrate the power management unit with other digital systems on the same die, which can result in significant cost reduction.

- 3. Dedicated analog and digital interface modules, particularly suited for dc-dc converter applications, are developed. A ring-oscillator based windowed-ADC (ring-ADC)

has the advantage of being nearly-entirely synthesizable, easily scalable and insensitive to switching noise. An ultra-low-power digital PWM (DPWM) module based on a ring-oscillator-MUX scheme (ring-MUX) is also developed.

### 1.3 Thesis Organization

An overview on DC-DC converters is offered in Chapter 2. Design challenges for portable applications are briefly discussed, and opportunities for digital control are presented.

Chapter 3 outlines system design issues relating to buck converters. Basics of continuous conduction and discontinuous conduction modes are reviewed as background information. The power train and output filter design is briefly discussed at the end of this chapter.

Chapter 4 addresses the architecture of the dual-mode buck converter IC. The PFM controller's quiescent power is the fundamental limitation on light-load efficiency when the cellular phone is in standby mode, and the details of the low-quiescent-current PFM controller are presented, followed by discussions on design of zero-DC-current comparators. Internal power management is presented as a solution to achieve voltage compatibility.

The analog to digital converter (ADC) and the digital PWM (DPWM) are used to provide the analog and digital interface between the digital compensation network and the buck converter. A general purpose interface element can be unnecessarily expensive in

terms of power consumption and chip area, thus the design of power and area efficient interface elements becomes the key challenge of making a high performance low power digital controller. A ring-ADC that is almost entirely synthesizable is presented in Chapter 5. And, a very low power ring-MUX DPWM is described in Chapter 6. A discussion on an alternative DPWM structure based on a counter-comparator scheme is also given in Chapter 6.

Ring oscillators are used in both analog and digital interface elements. Ideally more than one oscillation pattern can appear in a ring oscillator depending on initial conditions. However, only the fundamental pattern with one transition edge is observed in experiments. A hypothesis explaining the global stability of the fundamental pattern in ring oscillators is proposed in Chapter.7.

A test IC is built with a 0.25- $\mu$ m standard CMOS N-well process, and  $4\mu$ A quiescent current is achieved experimentally in PFM mode. More experimental results are presented and conclusions are drawn in Chapter 8.

## **Chapter 2**

**Overview of DC-DC Converters for**

**Cellular Phone Applications**

# 2.1 Overview of DC-DC Converters for Portable Applications

### 2.1.1 Increasing Battery run-time with voltage regulators

For battery operated devices, inserting a voltage regulator between the battery and the CMOS digital circuits or switch-capacitor-based mixed-signal circuits significantly enhances battery run time. This is true even when using regulators with relatively low efficiency. This can be explained with the following example.

Assume a cell phone handset has 50% power dissipated in digital circuitry when the battery is fully charged, and the other 50% is dissipated in analog circuitry which has a supply-independent bias current. A single cell Li-Ion battery is used which has a maximum fully charged voltage  $V_{max}$  of 4.2 V, and an end-of-charge voltage  $V_{min}$  of 3.6 V. The digital circuit is clocked at frequency f to meet the throughput requirement. Assume the minimum supply voltage to meet the throughput requirement is 1.8 V. Thus, the dynamic loss of the digital circuit can be modeled by a equivalent resistance of value

$$R_{eff} = \frac{1}{fC} \tag{2.1}$$

where the C is the total effective switching capacitance. The power consumption in the digital circuitry  $P_d$  and current consumption  $I_d$  is given by

$$P_d = fCV^2, (2.2)$$

$$I_d = \frac{P_d}{V} = fCV, \tag{2.3}$$

where V is the supply voltage to the mixed-signal circuit. The analog circuit can be modeled by a load with constant current load  $I_a$ , thus the power consumed in the analog session is

$$P_a = I_a V. (2.4)$$

If the analog and the digital power consumptions balance at  $V=V_{max}$ , from equation (2.2) and (2.4),  $I_a$  can be written as

$$I_a = fCV_{max}. (2.5)$$

For the present, neglect the supply voltage compatibility of the digital circuit and assume the circuit runs directly from the battery without hardware damage. Then the total power drawn from the battery when the battery voltage is  $V_{batt}$  is

$$P_{batt} = P_a(V_{batt}) + P_d(V_{batt}) = fC(V_{batt} + V_{max})V_{batt}.$$

(2.6)

Assume a linear regulator is inserted between the battery and the digital circuit, and the output voltage of the regulator  $V_o$  is 1.8V. The efficiency of the linear regulator  $\eta_{lin}$  is approximately  $\frac{V_o}{V_{batt}}$ . The power delivered from the battery is

$$P_{Lin} = (P_d(V_o) + P_a(V_o))/\eta_{lin} = fC(V_o + V_{max})V_{batt}.$$

(2.7)

By comparing (2.6) and (2.7), power saving by having a linear regulator can be calculated. Consider the battery discharge range between 4.2 V and 3.6 V. When the battery is fully charged, a overall power saving of 28.6% is achieved. When the battery is at end-of-charge, the overall power saving is 12.5%.

A linear regulator is relatively simple to implement. However, the major draw back is that the efficiency scales roughly with the ratio of output voltage and input voltage. As technology development pushes digital circuitry to be implemented with processes with feature size 0.18- $\mu$ m and below, the allowable supply voltage also drops. The efficiency limit of the linear regulator becomes a more serious problem. Replacing a linear regulator with switching regulator for better efficiency is necessary in many cases.

If a switching regulator is inserted between the battery and the load circuit, the power saving is more significant. Assume a 90% efficiency of the switching regulator, the power drawn from the battery is then

$$P = (P_d + P_a)/0.9 = 1.11fC(V_o + V_{max})V_o.$$

(2.8)

The overall power saving is 66% in the fully charged battery state and 57.3% in the minimum charged state. More detailed analysis on run time enhancement is given in [5].

Besides the main task of improving battery life, inserting regulators also helps to isolate different circuit blocks that might potentially disturb each other via supply lines. The power amplifiers in cellular phones draw large pulse current and can cause a battery voltage excursion of up to 0.5 V due to inductive effects and equivalent series resistance (ESR) of the battery. The power supply rejection ratio of the voltage regulator significantly reduces the supply transient seen by the phone circuits [6].

### 2.1.2 Design Challenges for Portable Applications

For portable devices such as cellular phones, all of the energy is drawn from the limited source of a battery. The load current of the voltage regulator in a cellular phone may vary from hundreds of mA in run time to below 0.1 mA in standby time. To extend both system run time and standby time, given the same power dissipation in the baseband and RF circuit, the efficiency of the voltage regulators must be increased. Switching regulators operated in pulse width modulation (PWM) mode are preferred to linear regulators for run time. The PWM controller runs the DC-DC converter in continuous conduction mode, and high regulation quality as well as high efficiency can be achieved at high load. Cellular phone systems may stay in standby mode for most of the total operation time, and the load current in standby mode is very low. As shown later in Chapter 3, when the load becomes light, the PWM mode leads to poor efficiency due to excessive switching loss. Instead, pulse frequency modulation (PFM) can be used to achieve high efficiency at light load. In PFM mode, the converter runs in discontinuous conduction mode, and the switching frequency is proportional to the load current, resulting in reduced switching activity at light load. Most loss components of the PFM mode converter, except the quiescent power of the controller, scale roughly with the load current when the load is very light. Thus, the PFM controller quiescent power becomes the limiting factor on light load efficiency. Therefore, the design of an ultra-low quiescent current PFM control mode is the most challenging objective in cellular phone applications.

### 2.2 Digital Control for DC-DC Converters

Digital control is gaining increasing popularity as a candidate for DC-DC converters due to many advantages over analog control [7]-[14]. With most data processing done in the digital domain, digital controllers are insensitive to noise and parameter variations that might lead to inaccuracies in analog circuits. Powerful computation capability makes digital control ideal for advanced control schemes such as adaptive control and on-line selfoptimizing control which improve converter performance. Digital controllers can directly communicate with other digital function blocks and feedforward can be easily implemented which makes the controller respond faster and enables the converters to have smaller output capacitors. In fact, in some applications the controller can be embedded on the same die as the system processor whose voltage it regulate. Technology scaling enhances the already vast signal processing capability of digital controllers with faster speed and lower power consumption, while it does little for the analog counterpart. Furthermore, the design automation of digital controllers is well supported by available synthesis and layout tools, and migrating an existing design to a different process needs much less modification than in the analog approach.

## **Chapter 3**

**System Design of Controller IC for**

**Cellular Phone Applications**

### 3.1 Overview of Buck Converter Operation

### 3.1.1 Basics of Buck Converter

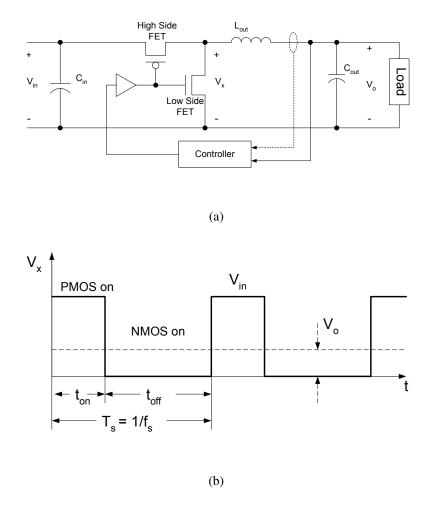

A buck converter is also called a step-down converter, which produces a lower average output voltage  $V_o$  than the DC input voltage  $V_{in}$ . Fig. 3.1(a) shows a synchronous buck converter system. Both the high side and the low side switching devices are implemented with FETs in a synchronous converter. The input voltage from the battery gets chopped by the power switches and the average input voltage is thus reduced. Assuming ideal switches, the chopped voltage  $V_x$  at the switching node is a square wave with duty ratio  $D = t_{on}/T_s$  as shown in Fig. 3.1(b). A second order LC low pass filter is used to pass the DC component of  $V_x$  while attenuating the AC component to an acceptable ripple voltage. Neglecting the loss in the converter, the DC output voltage  $V_o$  is given by [15]

$$V_o = V_{in} \cdot D. \tag{3.1}$$

By varying D,  $V_o$  can be controlled. The corner frequency  $f_c$  of the LC filter is chosen to be much lower than the switching frequency  $f_s$  so that the output voltage ripple is small.

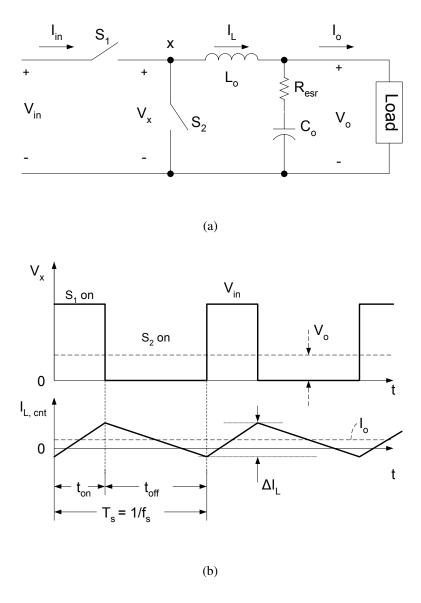

### 3.1.2 Continuous Conduction Mode

If the inductor current remains positive, or is allowed to reverse by the high-side and the low-side switches, the dc-dc converter is said to operate in continuous conduction mode. A converter in continuous conduction mode is shown in Fig. 3.2(a), and switching node voltage  $V_x$ , inductor current  $I_L$  and output current  $I_o$  are shown in Fig. 3.2(b). The inductor

Figure 3.1: (a) Buck converter schematic, (b) switching node voltage waveform  $V_x$  at steady-state.

current ripple  $\Delta I_L$  is give by [15]

$$\Delta I_L = \frac{V_o \cdot t_{off}}{L_o} = \frac{V_o}{L_o} \cdot (1 - D) \cdot T_s, \tag{3.2}$$

where  $T_s$  is the switching period.

In steady-state, the average output voltage is given by (3.1), and the output current  $I_o$  equals the DC component of inductor current  $I_L$ . When  $I_o$  is greater than  $\Delta I_L/2$ , the inductor current remains positive during the entire cycle. When  $I_o$  is less than  $\Delta I_L/2$ , the

Figure 3.2: (a) Synchronous converter, (b) voltage and current waveforms in continuous conduction mode.

inductor current becomes negative momentarily in the switching cycle, which corresponds to the converter discharging the output capacitor  $C_o$  through the inductor. As long as  $I_L$  flows continuously, the converter is considered to be in continuous conduction mode.

There are two ripple components in the output voltage, due to output capacitor  $C_o$  and its equivalent series resistance (ESR)  $R_{ESR}$  respectively. Let  $R_{ESR}$  be zero for now, the output voltage ripple  $\Delta V_o$  can be calculated by estimating the total charge accumulated on  $C_o$  when  $I_L$  is higher than  $I_o$ .

$$\Delta V_o = \frac{\Delta Q}{C_o} = \frac{1}{2} \frac{\Delta I_L}{2} \frac{T_s}{2} \frac{1}{C_o} = \frac{1}{8} \frac{\Delta I_L \cdot T_s}{C_o}.$$

(3.3)

Substituting  $\Delta I_L$  from equation (3.2) yields

$$\Delta V_o = \frac{1}{8} V_o \cdot (1 - D) \frac{T_s^2}{L_o C_o}.$$

(3.4)

Since switching frequency  $f_s=1/T_s$ , and LC filter cut-off frequency  $f_c$  is  $f_c=\frac{1}{2\pi\sqrt{L_oC_o}}$ ,  $\Delta V_o/V_o$  can be expressed as

$$\frac{\Delta V_o}{V_o} = \frac{\pi^2}{2} (1 - D) \frac{f_c^2}{f_s^2}.$$

(3.5)

Equation (3.5) shows that the output voltage ripple can be reduced by selecting the LC cut-off frequency  $f_c$  to be much lower than the switching frequency  $f_s$  of the converter.

With non-zero  $R_{ESR}$ , the output voltage ripple is higher than with zero  $R_{ESR}$ . It can be shown that, assuming the ripple current is piecewise linear, for D < 50%, the voltage

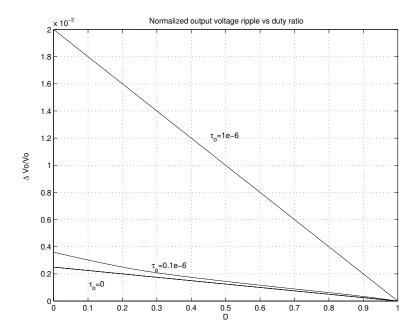

Figure 3.3: Converter output voltage ripple with different output capacitor time constant values.

ripple  $\Delta V_o$  is

$$\Delta V_{o} = \begin{cases} \frac{\Delta I_{L}T}{8C} + \Delta I_{L}R\frac{\tau_{o}}{2T}(\frac{1}{1-D} + \frac{1}{D}) & \text{for } \tau_{o} \leq \frac{1}{2}DT, \\ \frac{\Delta I_{L}}{8C}(1-D)T + \Delta I_{L}R\frac{\tau_{o}}{2(1-D)T} + \frac{\Delta I_{L}}{2}R & \text{for } \frac{1}{2}DT < \tau_{o} \leq \frac{1}{2}(1-D)T, \\ \Delta I_{L}R & \text{for } \tau_{o} > \frac{1}{2}(1-D)T; \end{cases}$$

(3.6)

and for  $D \geq 50\%$

$$\Delta V_{o} = \begin{cases} \frac{\Delta I_{L}T}{8C} + \Delta I_{L}R\frac{\tau_{o}}{2T}(\frac{1}{1-D} + \frac{1}{D}) & \text{for } \tau_{o} \leq \frac{1}{2}(1-D)T, \\ \frac{\Delta I_{L}}{8C}DT + \Delta I_{L}R\frac{\tau_{o}}{2DT} + \frac{\Delta I_{L}}{2}R & \text{for } \frac{1}{2}(1-D)T < \tau_{o} \leq \frac{1}{2}DT, \\ \Delta I_{L}R & \text{for } \tau_{o} > \frac{1}{2}DT, \end{cases}$$

(3.7)

where  $\tau_o$  is the time constant of output capacitor defined as  $\tau_o = RC$ . The derivation

and verification of this equation is in Appendix.A. For a given capacitor technology,  $\tau_o$  is approximately a constant for various capacitance values. For example, the time constant is usually in the range of 0.1 to a few  $\mu s$  for ceramic capacitors, and 1 to 10  $\mu s$  for tantalum capacitors. Fig. 3.3 shows the plots of normalized output voltage ripple as a function of steady-state duty ratio, corresponding to different output capacitor time constant values. It can be noticed that smaller output voltage ripple can be achieved by choosing output capacitors with lower time constant values.

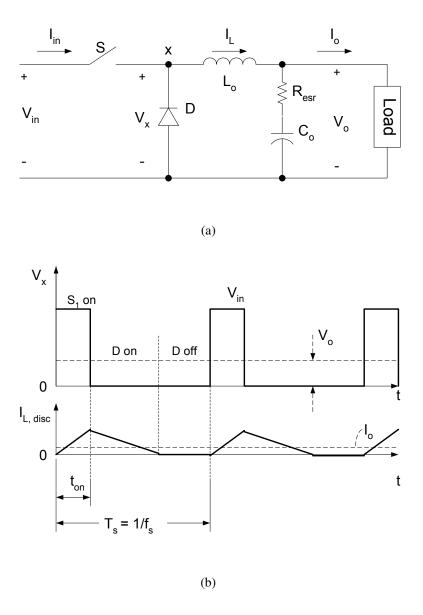

### 3.1.3 Discontinuous Conduction Mode

Replacing the low side switch  $S_2$  in the synchronous converter with a diode D results in a conventional buck converter as shown in Fig. 3.4. When output current  $I_o$  is higher than  $\Delta I_L/2$ , the inductor current flows continuously and the converter still works in continuous conduction mode, with  $V_o$  satisfying (3.1). When  $I_o$  is lower than  $\Delta I_L/2$ , the diode conducts while the inductor current decreases. The inductor discharges stored energy to the output capacitor until the current drops to zero. The diode then blocks the reverse current and the inductor current remains zero until the next switching cycle. This operation mode is called discontinuous conduction mode because the inductor current is identically zero for finite intervals.

In discontinuous conduction mode, the output voltage of the converter  $V_o$  does not

Figure 3.4: (a) Schematic of a conventional buck converter, (b) switching node voltage and inductor current waveforms in discontinuous conduction mode.

satisfies (3.1). Instead, the new expression of D is given by [15]

$$D = \frac{V_o}{V_{in}} \sqrt{\frac{I_o/I_{LB,max}}{1 - V_o/V_{in}}}.$$

(3.8)

where  $I_{LB,max}$  is the maximum value of average inductor current at the edge of continuous conduction mode  $I_{LB}$  if  $V_o$  is constant:

$$I_{LB,max} = \frac{T_s V_o}{2L} \tag{3.9}$$

### 3.2 PWM Mode Power Loss Analysis

Dc-dc converter losses include conduction loss, switching loss, controller quiescent power, inductor core loss, stray inductance loss, etc. Conduction loss and switching loss are usually significant in PWM mode. Assume the input voltage is  $V_{in}$ , the output voltage is  $V_o$ , and the output current is  $I_o$ . Let D be the steady state duty ratio, and  $f_s$  be the switching frequency of the converter, the different loss components are elaborated below.

### 3.2.1 Conduction Loss

The conduction loss is mainly due to the finite on-resistance of the high side and the low side switches, denoted by  $R_{dson,h}$  and  $R_{dson,l}$  respectively, and the series resistance of the output inductor  $R_L$ .

Let  $R_{dson}$  be the equivalent on-resistance of the power switches seen by the inductor current, it can be given by the sum of the on-resistance of the power switches, weighed by

conduction time:

$$R_{dson} = R_{dson,h}D + R_{dson,l}(1-D).$$

(3.10)

In steady state, the average inductor current equals the load current  $I_o$ . Assume the inductor current ripple is small compared to the average inductor current, the conduction loss can then given by

$$P_{hl} = (R_{dson} + R_L)I_o^2. (3.11)$$

To avoid the shoot through current between the high side and the low side switches, deadtime must be inserted in the PWM signals that controls the two switches, to make sure the two switches are not on simultaneously. During the deadtime, both power switches are off, and the continuous flow of inductor current is relying on the body diodes of the switches. Assume the voltage drop across the diode junction is 0.7 V when the diode is on, the conduction loss on the diode, denoted by  $P_D$ , is

$$P_D = \frac{0.7I_o t_{deadtime}}{T_o} \tag{3.12}$$

where  $t_{deadtime}$  is the total deadtime in one switching cycle. If the deadtime is designed properly, the conduction loss from the diode should also be small compared to  $P_{hl}$ .

### 3.2.2 Switching Loss

The power switches conduct momentarily in saturation mode during the turn-on and turn-off transient. The high voltage across the power device and the inductor current that flows through it can cause significant loss. This is often referred to as hard switching. The

switching loss in a dc-dc converter is mainly the loss due to hard switching, and the loss in gate drives.

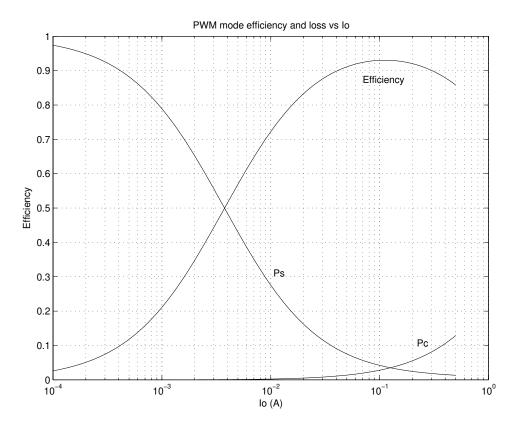

#### **Hard Switching Loss**

The loss due to hard switching is associated with the parasitic capacitor  $C_x$  lumped at the switching node, as shown in Fig. 3.5(a). The capacitor  $C_x$  is composed of the junction capacitance of each power switch, and the parasitic capacitance from the package, the inductor and PCB trace. Idealized transient waveforms of the drain current  $I_d$  and the drain-source voltage  $V_{ds}$  of the high side PMOS is shown in Fig. 3.5(b). The simulated turn-on and turn-off transient waveforms of the same switch is given in Fig. 3.6. For simplicity, in the analysis here, the inductor current ripple is neglected and thus  $I_L = I_o$  in steady state. The finite on-resistance of the power switches are also ignored.

During the deadtime before the PMOS is on, the inductor current shifts to the body diode of low side switch,  $V_{ds}$  of PMOS equals  $V_{in}$ . When  $V_g$  drops to approximately one threshold below the input voltage, the PMOS starts to turn on, the inductor current starts to shift to the high side switch. Drain-source voltage  $V_{ds}$  remains equal to  $V_{in}$  until  $I_d$  is close to  $I_o$ , because of the exponential relation between diode voltage and current. Gate drive current  $I_G$  charges the miller capacitor  $C_m = C_{gd}(1-A)$ , where A is the small signal gain of the PMOS. The large miller capacitor forces gate voltage to plateau at

$$V_g = V_{in} - V_t - \Delta V, \tag{3.13}$$

where  $V_t$  is the PMOS threshold voltage.

Figure 3.5: (a) Schematic of buck converter with parasitic capacitor  $C_x$  at the switching node, (b) hard switching transient waveforms in PMOS.

Figure 3.6: Simulated transient waveforms of PMOS, the top curve being  $I_d$ , middle curve  $-V_g$ , bottom curve  $-V_{ds}$  in each sub-figure (a) turning-on transient, (b) turning-off transient.

The drain current  $I_d$  continues to increase to the peak value  $I_{pk}$ . The current difference  $I_{pk} - I_o$  charges up  $C_x$ , and  $V_{ds}$  of the PMOS decreases until  $V_{ds} = 0$ . The PMOS enters the linear region and the miller transient has passed. The gate voltage continues to ramp up to  $V_{in}$ , the voltage  $V_x$  across the capacitor  $C_x$  settles to  $V_{in}$ , and  $I_d$  falls back to  $I_o$ , at the end of the transient. The turn-off transient is analogous.

The total charge accumulated on  $C_x$  during the turn-on transient can be calculated by integrating the  $I_d$  waveform in the shaded area in Fig. 3.5(b). Since the PMOS is in the saturation region during most of the transient, its gate-drain capacitor  $C_{gd}$  is just the gate-diffusion overlap capacitor, thus  $C_x$  is much greater than  $C_{gd}$ . Let  $Q_x$  be the charge stored on  $C_x$  at the end of turn-on transient. Define  $I_{C_x}$  to be the current exceeding  $I_o$  to charge the switching node, it can then be calculated as

$$I_{C_x} = I_{pk} - I_o = \frac{Q_x}{t_{vf}} = \frac{C_x V_{in}}{t_{vf}},$$

(3.14)

where  $t_{vf}$  is the  $V_{ds}$  falling time, as shown in Fig. 3.5(b). The total energy dissipated in the PMOS during the turn-on transient can be calculated as

$$E_{t,on} = \frac{1}{2} (I_o + I_{C_x}) V_{in} t_{cr} + \frac{1}{2} V_{in} (I_o + I_{C_x}) t_{vf}$$

$$= \frac{1}{2} V_{in} (I_o + I_{C_x}) (t_{cr} + t_{vf}).$$

(3.15)

The energy stored on  $C_x$  is transferred to the output during the NMOS turn-on transient, and shall not be counted as loss. Thus the switching loss at turning-on transient of the PMOS is

$$P_{sw,on} = \frac{E_{t,on}}{T_s} = \frac{V_{in}(I_o + I_{C_x})(t_{cr} + t_{vf})}{2T_s}.$$

(3.16)

Similarly, the loss at the turning-off transient of the PMOS  $P_{sw,off}$  can be calculated as

$$P_{sw,off} = \frac{V_{in}(I_o - I_{C_x})(t_{vr} + t_{cf})}{2T_s}$$

(3.17)

The switching loss in the PMOS  $P_{sw,p}$  can be calculated by summing (3.16) and (3.17). Assume the turn-on and turn-off times are equal, one obtains

$$P_{sw,p} = \frac{V_{in}I_o(t_{vr} + t_{cf})}{T_s}$$

(3.18)

The switching transient time is mainly decided by the speed of the gate driver to charge the miller capacitor. A stronger gate driver results in a faster turn-on and off transient, hence lower switching loss. However, when the turn-off of the high side PMOS is too fast, the low side NMOS might turn on to some extent due to capacitive coupling to the NMOS gate. In many cases it may be necessary to design the high side gate driver weaker in pulling down the PMOS gate voltage for a slower PMOS turn-on transient. A strong pull down transistor in the low side gate driver may also be helpful to alleviate the NMOS gate voltage variation during turn-off transient of the PMOS.

As mentioned earlier, to avoid the momentary shoot-through current when both the PMOS and the NMOS are on, a deadtime is usually inserted between the control signals of the two power switches. If the deadtime is designed properly, the drain-source voltage of the NMOS is zero while the NMOS is turned on, resulting in zero loss. This is often referred to as the soft switching.

#### **Gate Drive Loss**

The power dissipation in the gate drives is mostly dynamic power used to charge and discharge parasitic capacitors of the power switches. Two processes are important in understanding this kind of loss: the charging of gate-source capacitor  $C_{GS}$ , and charging of the miller capacitor  $C_{GD}$ . The charge accumulated on  $C_{gs}$  when the transistors turn on is

$$Q_{GS} = (\Delta V_{GS})C_{GS},\tag{3.19}$$

and the charge delivered to the miller capacitor is

$$Q_m = (\Delta V_{GD})C_{GD},\tag{3.20}$$

where  $\Delta V_{GS}$  and  $\Delta V_{GD}$  are the gate-source and gate-drain voltage change respectively during turning-on transient. Thus,  $\Delta V_{GS} = V_{in}$ , and  $\Delta V_{GD} = 2V_{in}$ . Therefore, the gate drive power loss can be given by

$$P_g = f_s(Q_{GS} + Q_{GD})V_{in} = f_s(C_{GS} + 2C_{GD})V_{in}^2$$

(3.21)

The loss in gate drives is usually smaller than the hard switch loss when the load current is high. However, the hard switch loss has dependency on the load current. The gate drive loss, on the other hand, is independent of load current. Thus, the gate drive loss can become the dominant component in switching loss when the load is light.

# 3.2.3 Stray Inductance Loss

The stray inductance  $L_s$  in the loop formed by input decoupling capacitor and power switches has a power dissipation that equals to [5]

$$P_{Ls} = \frac{1}{2T_s} L_s I_{max}^2, (3.22)$$

where  $I_{max}$  is the maximum inductor current.

The value of  $L_s$  depends on the PCB layout, packaging, etc and can be reduced by minimizing the loop that contains the high current.

## 3.2.4 Controller Quiescent Power

The equivalent bias power the controller of the dc-dc converter dissipates is called controller quiescent power. Typically, the quiescent power of the PWM controller is much lower than the sum of the switching and the conduction losses of the converter in continuous conduction mode.

# 3.2.5 PWM Mode Efficiency

Considering only the conduction loss  $P_c$ , the switching loss  $P_s$ , and the controller quiescent power  $P_q$ , the efficiency  $\eta$  of a dc-dc buck converter in PWM mode can be given by

$$\eta = \frac{P_o}{P_o + P_s + P_c + P_a}. (3.23)$$

Figure 3.7: Efficiency and loss versus  $I_o$ , switching loss  $P_s$  and conduction loss  $P_c$  is each normalized to input power.

An efficiency curve of a dc-dc converter is plotted in Fig. 3.7. The normalized switching and conduction losses,  $P_s/P_{in}$  and  $P_c/P_{in}$  respectively, are also given. The corresponding input voltage is 4.5 V and output voltage is 1.5 V. It shows that the converter efficiency is higher than 80% when the load is higher than 14 mA, and it bends down significantly at light load ( $I_o < 1mA$ ) due to the increasing portion of switching loss in the total input power.

For cellular phone applications, the system works in the standby mode most of its operation time. The load current is very low when the phone is in standby mode. If the voltage regulator continues to operate in PWM mode when the load is light, the efficiency of the

regulator will be poor. To extend the standby time a cellular phone can sustain with each full charge of the battery, the efficiency of the dc-dc converter has to be improved in light load conditions. For this reason, the controller is switched to pulse frequency modulation (PFM) mode control for light load operation.

# 3.3 PFM Mode Power Loss Analysis

The PFM mode runs the buck converter in discontinuous conduction mode. The switching frequency of the converter scales with the load current. At very light load, the switching activity is greatly reduced, resulting in significant switching loss reduction.

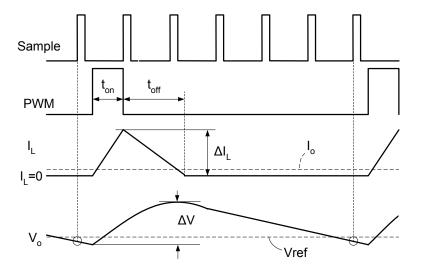

Fixed-on-time control is implemented in the PFM mode in this work. The output voltage is sampled at a fixed frequency, so that when it is detected to be lower than the reference, the PFM controller generates a fixed-on-time pulse to charge the output node. Then the converter is idle until a low  $V_o$  is detected again. The PFM mode waveforms of sampling clock, PWM signal, inductor current and output voltage are shown in Fig. 3.8.

Let  $V_{in}$  and  $V_o$  be the input and output voltage respectively,  $I_o$  be the load current and  $\Delta I_L$  be the peak inductor current. Assume the fixed on-time is  $t_{on}$ . Assume the load current is very low. The total charge Q transferred to the output node in each switching cycle can be estimated by integrating the inductor current in one switching cycle, which results in

$$Q = \frac{\Delta I_L}{2} t_{on} \frac{V_{in}}{V_o}.$$

(3.24)

Neglecting the jitter due to discrete sampling of  $V_o$ , the switching frequency  $f_s$  at load  $I_o$

Figure 3.8: Voltage and current waveforms in buck converter in PFM mode.

can be approximated by

$$f_s \approx \frac{I_o}{Q} = \frac{2I_o}{\Delta I_L} \frac{1}{t_{on} \frac{V_{in}}{V_o}}.$$

(3.25)

Therefore the switching frequency at PFM mode is roughly proportional to the load current.

# 3.3.1 Conduction Loss, Switching Loss, and Stray Inductive Switching Loss in PFM Mode

The time during which the inductor current is non-zero is  $t_{on} + t_{off}$ , which equals to  $t_{on}V_{in}/V_o$ . In steady state, the conduction loss in PFM can be written as

$$P_c = f_s R \int_0^{t_{on} \frac{V_{in}}{V_o}} I_L(t)^2 dt.$$

(3.26)

where R is the equivalent total series resistance. Similarly, switching loss and stray inductance loss in PFM mode is the total energy dissipated each switching cycle times the switch-

ing frequency. Therefore, in PFM mode, conduction loss, gate drive loss, hard switching loss and stray inductance loss are all proportional to the switching frequency and hence load current.

## 3.3.2 PFM Controller Quiescent Power

The PFM controller quiescent power is the equivalent static power of the controller and thus is independent of the load current. When the load is very light, all the other kinds of loss scale with the load current, and controller quiescent power becomes the dominant limiting factor on the efficiency of the PFM mode converter. Therefore, low controller quiescent power is essential to achieve high efficiency at very light load.

# 3.4 DC-DC Converter System Design

# **3.4.1** Digital Controller System Specifications

Some of the main specifications of the buck converter for cellular phone and hand-held ratio applications are listed in Table.3.1.

# 3.4.2 Output Filter Design

The output filter in a buck converter is typically a second order LC filter. As shown by equations (3.5), (3.6) and (3.7), the output voltage ripple could be capacitance dominated, equivalent series resistance (ESR) dominated, or have significant components due to each.

Table 3.1: Dc-dc converter specifications for mobile phone and hand-held ratio applications.

| Symbol           | Parameter                            | Min | Тур  | Max | Units |

|------------------|--------------------------------------|-----|------|-----|-------|

| $I_{o,max}$      | Maximum load current                 |     | 400  |     | mA    |

| $V_{in}$         | Input voltage                        | 2.8 |      | 5.5 | V     |

| $V_o$            | Output voltage                       | 1.0 |      | 1.8 | V     |

| $I_{lim}$        | Switch peak current limit            |     | 1000 |     | mA    |

| $\Delta V_o/V_o$ | PWM mode DC output voltage precision |     | 2%   |     |       |

| $V_{ripp}$       | PWM mode output voltage ripple       |     | 2    |     | mV    |

In the capacitance dominated case, the voltage ripple is quadratically dependent on the ratio of LC filter cutoff frequency and the converter switching frequency. For a specified output voltage ripple and a given switching frequency, the product of the two filter components' values can be determined. And the specific L and C values can be decided by constraints of current ripple, cost and profile requirements of output capacitors. A ceramic capacitor is usually preferred in cellular phone applications to tantalum capacitor or electrolytic capacitor due to its smaller time constant  $\tau_o$ , smaller capacitor physical profile, and higher reliability. As shown previously in Fig. 3.3, a smaller capacitor time constant leads to reduced output voltage ripple. The time constant of ceramic capacitor is about 0.1 to a few  $\mu$ s. The ceramic capacitor used in this work has a  $\tau_o$  value of 1  $\mu$ s, and the resulting output voltage ripple is 2 mV. Thus, the output voltage ripple can be still be reduced by choosing capacitor with smaller time constant.

# 3.4.3 Power Train Design

An optimal power loss can be achieved by making conduction loss and switching loss approximately the same [5]. However, this implies large transistors for both power switches which becomes expensive in terms of die area. In this work, the size of PMOS and NMOS are chosen to achieve a compromise between chip area and power loss. As such, the conduction loss dominates the switching loss at full load.

# **3.4.4 Summary**

To meet the specifications in Table 3.1, some of the important system parameters are summarized in Table 3.2.

Table 3.2: Some system parameters derived for application specification in Table.3.1.

| Symbol       | Parameter                         | Value   | Units            |

|--------------|-----------------------------------|---------|------------------|

| $f_s$        | Switching frequency at PWM mode   | 0.6–1.5 | MHz              |

| L            | Inductor                          | 10      | $\mu \mathrm{H}$ |

| C            | Output capacitor                  | 47      | $\mu { m F}$     |

| $R_{dson,P}$ | On-resistance of power train PMOS | 0.6     | Ω                |

| $R_{dson,N}$ | On-resistance of power train NMOS | 0.6     | Ω                |

# **Chapter 4**

**Architecture of the Dual-Mode Buck**

**Converter IC**

# 4.1 System Architecture

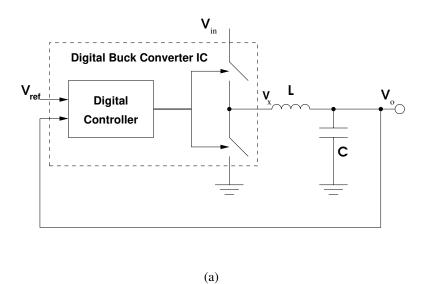

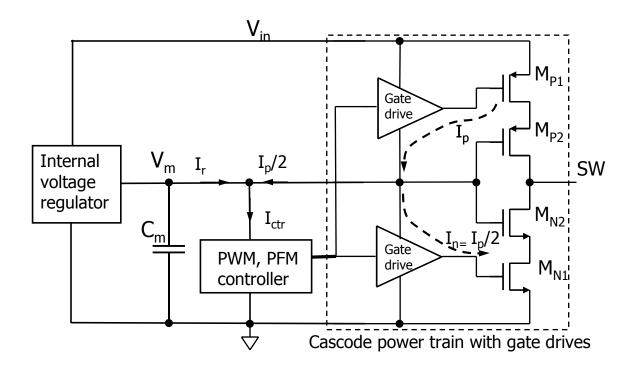

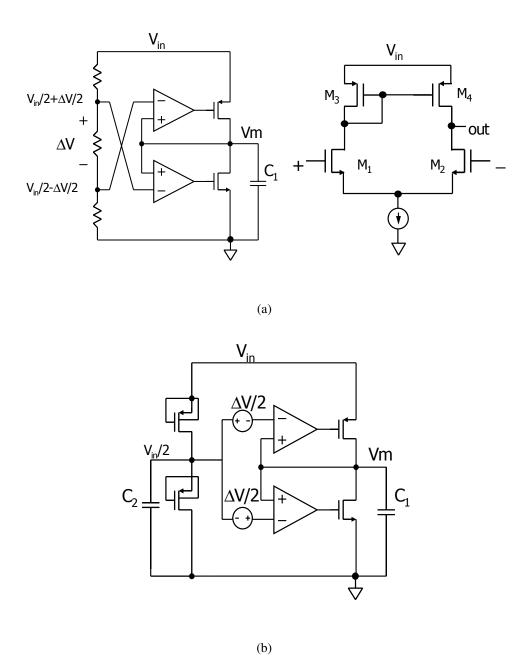

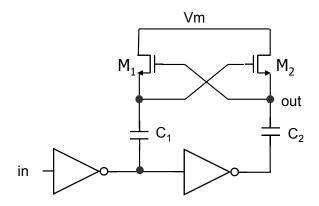

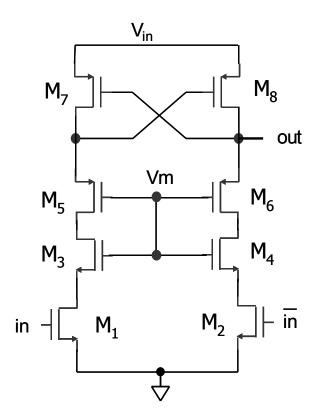

This chapter describes the architecture and voltage compatibility solution for the dual-mode ultra-low-power digitally-controlled buck converter IC for cellular phone applications. Fig. 4.1(a) is a buck converter system composed of the designed IC (in the dashed box) and the external LC filter, and Fig. 4.1(b) shows details of the dual-mode buck converter IC with power train and gate drivers on the same die.

As discussed in the previous chapter, the PWM control achieves good regulation quality and high efficiency at high load. But the efficiency becomes poor when the load goes low. So at light load, it is beneficial to switch to PFM control. The designed IC supports PWM mode for heavy load and PFM mode for light load. The pin MODE in Fig. 4.1(b) is used to switch between the two modes. In PWM mode, the error voltage  $V_e = V_o - V_{ref}$  is quantized by the ADC to provide an error signal in the digital domain  $D_e = (V_o - V_{ref})/V_b$ , where  $V_b$  is a reference voltage and often takes the value of  $V_{in}$  or  $V_o$  depending on control purpose. The digital PID control block generates a duty ratio command D to feed into the digital PWM (DPWM) module which generates the pulses. The PFM mode, as a contrast, runs the converter in discontinuous conduction mode with variable frequency and fixed-on-time. The quiescent power of the PFM controller is the limiting factor for efficiency at ultra-light load. An ultra-low-quiescent-power PFM controller is designed to solve the problem.

For the digital implementation, smaller feature size processes with lower supply voltage are preferred to implement the controller to achieve smaller die area, higher speed and lower power. In cellular phone applications, the power supply of the buck converter system is

PFM mode Comparator **DPWM** PFM logic MUX  $V_{\text{re}\underline{f}}$ De Digital PID Simplified Ring Ring osc. dither control ADČ power train PWM mode System clock MODE **GND**

Figure 4.1: (a) System diagram of a digitally-controlled buck converter, (b) block diagram of digitally controlled buck converter IC for cellular phone applications.

(b)

typically a single cell Li-ion battery, which is commonly used in a discharge range between 4.2 V and 3.6 V. However, when the cellular phone sits in the charger, the supply voltage can go up to 5.5 V. Combine these voltage range and reliability considerations, the input voltage range of the DC-DC converter is usually specified to be from 5.5 to 2.8 V. Thus the input voltage of the converter may be higher than the allowed supply voltage of the process. A solution that resolves the voltage conflict can be of great interest, because it would allow the digital controller of the DC-DC converter with high input voltage to be implemented with low voltage process, making it possible to integrate power management unit with the load circuits on the same die. Significant cost reduction can be achieved consequently. Internal power management is introduced to resolve the conflict of high input voltage and a low voltage process, the details of which are presented in Section 4.4.

# 4.2 PWM Mode

# **4.2.1** Limit Cycling and Quantizer Resolution

Limit cycles exist in many sample-data systems due to signal amplitude quantizers such as ADCs and DACs. In digitally controlled buck converter systems, limit cycles may appear as steady-state oscillation of  $V_o$  and other system variables at a frequency lower than  $f_s$ . Limit cycles might lead to unpredictable voltage variations and thus are undesirable. Since the oscillation amplitude and frequency could be hard to predict, it is difficult to analyze and design for limit cycle operation. Sufficient conditions to eliminate limit cycles are

given in [16], which require the resolution of the DPWM to be greater than the resolution of the ADC.

In this work, due to required DC output voltage precision, the ADC quantization bin size is chosen to be 16 mV, which corresponds to 8.3-bit resolution under 5.5 V input voltage. And the DPWM has a step size of 5.4 mV, or equivalently a 10-bit resolution under 5.5 V input.

#### 4.2.2 ADC and DPWM

The ADC and DPWM are used to provide the analog and digital interface between the digital compensation network and the buck converter. The design of power and area efficient interface elements is the key challenge of making a high performance low power digital controller. The DPWM runs in both PWM and PFM modes, hence a very low power DPWM is desirable for quiescent current consideration in PFM mode. A ring oscillator-multiplexer (Ring-MUX) based DPWM module is presented in Chapter 6, and also reported in [13]. The DPWM not only generates PWM signals, but provides clocks for the compensation network while in PWM mode, and for the sampling comparator while in PFM mode.

A general purpose ADC can be unnecessarily expensive in terms of power consumption and chip area. In PWM mode, an ADC with rail to rail quantization range is not required in the buck converter application since the output voltage  $V_o$  varies only within a small window centered at reference  $V_{ref}$ . A windowed-ADC scheme that gives high resolution only in the small window that contains the maximum possible  $V_o$  range is proposed, and a

novel averaging ADC implementation based on ring oscillators is presented in Chapter 5.

#### **4.2.3** Digital Compensation Network

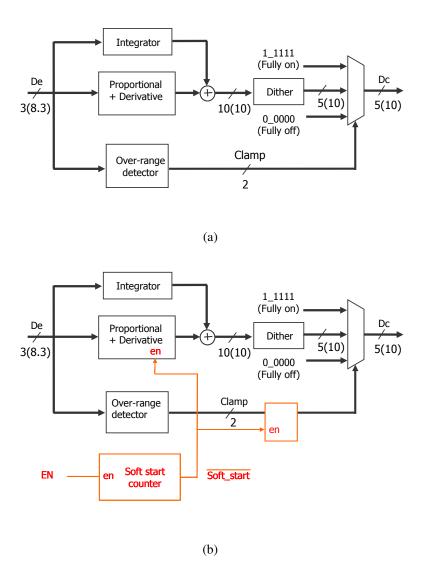

Fig. 4.2(a) shows the digital compensation network in PWM mode. When  $V_o$  is within the specified vicinity of  $V_{ref}$ , in this work a 80 mV window centered at  $V_{ref}$ , a digital PID control law is used to calculate the duty ratio command D for next switching cycle. In the unexpected case when  $V_o$  goes beyond the window range, the over range detector will activate the clamping function which saturates the duty ratio command to fully on or off for a fast response. The PID compensation network continues to calculate for the appropriate duty ratio, and gets its output ready to replace the saturation function. Once  $V_o$  comes back within the specified window, the clamping function is deactivated and the PID network resumes the control of the converter through its output.

To avoid the stress on external components during the converter start-up, soft start is integrated in the digital controller. During start up, the proportional and derivative terms, as well as the over range detection are disabled. A startup counter that is clocked by the internal clock from the DPWM module gives a start up sequence and slews the integrator to the reach the appropriate steady-state value. At the end of soft start process, the proportional, derivative and the over range detector are enabled, and the PWM controller works with PID control with the saturation function previously discussed. The pin EN is used to start the soft start process. The complete digital compensation path with soft-start is shown in Fig. 4.2(b).

Figure 4.2: (a) PID compensation network, (b) compensation network with soft-start function. The number in front of the bracket is the actual number of bits of the signals, and the number in the bracket is the effective bits of resolution.

# 4.2.4 Summary of PWM Mode

Some parameters of the PWM mode controller are summarized in Table 4.1.

Table 4.1: PWM mode parameters.

| Parameter                       | Value | Units |

|---------------------------------|-------|-------|

| ADC quantization step size      | 16    | mV    |

| Windowed ADC quantization range | 80    | mV    |

| DPWM step size                  | 5.4   | mV    |

| Effective ADC resolution        | 8.3   | Bit   |

| Effective DPWM resolution       | 10    | Bit   |

# 4.3 PFM Mode

#### 4.3.1 Ultra-Low-Power PFM Architecture

To improve the converter efficiency at light load, the controller runs in PFM mode when the cellular phone is in standby mode. That is, the buck converter runs in discontinuous conduction mode with a variable frequency and fixed on-time. As shown in Chapter 3, the total loss in PFM mode is composed of losses that are proportional to the load current, and the controller quiescent power which is independent of load current. At ultra light load, the controller quiescent power is the dominant term. In this work, the PFM mode controller includes a clocked comparator, a small logic block, and the DPWM, as shown in

Fig. 4.1(b), to achieve low quiescent power. A very low power internal voltage regulator is also running in PFM mode, which is discussed later.

Idealized operation of the fixed-on-time PFM controller as well as the output voltage and inductor current waveforms were shown in Fig. 3.8 of Chapter 3. When the cell phone is in standby mode and the load  $I_o$  is close to zero,  $I_L - I_o \approx I_L$ . Ignoring the jitter due to discrete sampling, the peak output voltage ripple  $\Delta V_{max}$  at very light load can be calculated, and is given by

$$\Delta V_{max} = \begin{cases} \frac{\Delta I_L}{2C} t_{on} \frac{V_{in}}{V_o} + \frac{\Delta I_L}{2C} \frac{\tau_o^2}{t_{off}} & for \tau_o \leq t_{off}, \\ \frac{\Delta I_L}{2C} t_{on} + \Delta I_L R & for \tau_o > t_{off}, \end{cases}$$

(4.1)

where  $\tau_o$  is the time constant of the output capacitor,  $\Delta I_L$  is the peak inductor current, and  $t_{off}$  is the duration in which the inductor current decreases. Let  $t_{on}$  be the duration of PMOS conduction, or equivalently, the duration in which the inductor current increases. Duration  $t_{off}$  can then be given by

$$t_{off} = t_{on} \frac{V_{in} - V_o}{V_o}. (4.2)$$

Table 4.2 lists the performance specification of the PFM mode.