# A C-Band High Efficiency Second Harmonic Tuned Hybrid Power Amplifier in GaN technology

P. Colantonio<sup>1</sup>, F. Giannini<sup>1</sup>, R. Giofrè<sup>1</sup>, E. Limiti<sup>1</sup>, A. Serino<sup>1</sup> M. Peroni<sup>2</sup>, P. Romanini<sup>2</sup>,

<sup>1</sup>University of Rome "Tor Vergata", Department of Electronic Engineering, via del Politecnico n°1, 00133 Rome, Italy,+390672597346

<sup>2</sup> Selex Sistemi Integrati s.p.a., via Tiburtina Km 12,400, 00131 Rome, Italy

Abstract — In this contribution a C-Band 2<sup>nd</sup> harmonic tuned hybrid power amplifier utilizing a PHEMT GaN device is presented, together with technological aspects, non linear device model and adopted design criteria. The amplifier has been realised in hybrid form, exhibiting a bandwidth larger than 20% around 5.5GHz, with a minimum output power of 33 dBm, and a drain efficiency of 60% at the centre frequency.

## I. Introduction

The realisation of power amplifier (PA) allowing simultaneously highest output power (Pout) level together with highest efficiency is an essential challenge in an huge number of systems involving transmitter units, ranging from mobile communication equipment to base station applications.

It is well known that one of the solution to increase device performances, both in terms of power and efficiency, is to make use of suitable harmonic strategies (e.g. the Class F [1]), fruitfully exploiting the device non linear behaviour to improve its capabilities with respect to a linear approach (e.g. Class A) [2]. In fact, the aim of the harmonic manipulation is to find the optimum device harmonic terminations (usually up to third harmonic component), both at the input and output ports, to improve the fundamental output voltage component according to device physical limitations, thus increasing output power and therefore power gain and efficiency [3].

In particular, the suitable control of the 2<sup>nd</sup> harmonic impedances allows to attain higher performances as compared as to Class F approach, while implying a design complexity increase basically due to the control of input second harmonic device termination [4,5]. Moreover, the use of a 2<sup>nd</sup> harmonic voltage component results in a not symmetrical output voltage waveform, exhibiting a peaking behaviour towards drain-source breakdown limitation, therefore usually restricting, in GaAs technology, the use of such strategy mainly to low voltage applications.

Such limitation is overcame in GaN devices, where the output voltage swing is limited by the device ohmic zone and not by the gate-drain breakdown.

Therefore a 2<sup>nd</sup> harmonic tuned hybrid power amplifier has been designed and the experimental results will be presented in the following.

# II. DEVICE TECHNOLOGY

The selected active device is a GaN HEMT with 1mm gate periphery ( $10x100\mu m$  gate fingers), fabricated by Selex Sistemi Integrati.

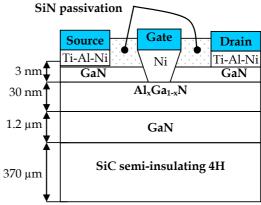

The structure layer is epitaxially grown on semiinsulating 4H SiC. After a proprietary nucleation deposition on SiC substrate of 1.2 $\mu$ m of GaN as buffer layer, in order to reduce reticular mismatching, 30nm of Al<sub>x</sub>Ga<sub>1-x</sub>N (x=0.5) are grown and, to realise the device channel, 3nm of GaN layer are realised on top. The resulting structure of the device is reported in Fig. 1.

Device drain and source ohmic contacts are realised through the layer series of Ti(20nm), Al(100nm), Ni(40nm) and Au(50nm). By using Transmission Line Model (TLM) technique [6], a contact resistance and a sheet resistance of  $R_{\rm C}{=}0.6{\pm}0.1~\Omega/{\rm mm}$  and  $R_{\rm SH}{=}490{\pm}20~\Omega/{\rm sq}$  respectively are measured. Finally, the wafer surface has been passivated by using SiN Plasma Enhanced Chemical Vapour Deposition (PE-CVD), while the active device isolation has been achieved by using fluorine ion implantation. The gate electrode has been defined by lift-off of 20nm Ni/200nm Au Schottky metallisation on the AlGaN surface, deposited after opening a window on the SiN layer by using CF4 plasma reactive ion etching..

Fig. 1: Physical structure of the GaN HEMT device.

The residual current leakage after ion implantation, verified by a test pattern consisting in a  $100\mu m$  wide conductive layers separated by a  $10\mu m$  insulated gap, consists in less than 20nA, with 300Volt bias.

The discrete device fabrication has been completed with Ti/Pt/Au overlay interconnection and Au plated for lines, pads and air bridges. The microphotograph of the GaN HEMT is show in Fig. 2.

Fig. 2: Microphotograph of the GaN HEMT device.

## III. NON LINEAR MODEL

The active device has been modelled using a second generation Angelov model [7]. For this purpose, DC and pulsed I/V measurements and bias dependent S-parameters measurements have been performed. A bias-dependent small-signal equivalent circuit model of the device was preliminarily extracted using the measured S-parameters to obtain the value of the linear elements of the Angelov model and the voltage dependence of its non-linear part [6].

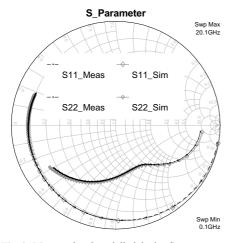

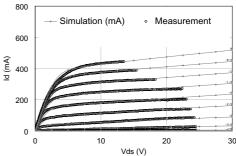

Parameters of both non-linear capacitances and drain current elements involved in the model were determined by fitting the bias dependent capacitances values obtained from the small signal equivalent circuit and the pulsed I-V measurements respectively. Finally, the parameters of the non-linear diodes of the model have been extracted by fitting the DC gate current measurements. Fig. 3 shows the measured an modelled S-parameters for the bias point V<sub>DS</sub>=25V, V<sub>GS</sub>=-3V, while a comparison between measured and simulated I/V device characteristics obtained pulsing from the same bias point is shown in Fig. 4.

Fig. 3: Measured and modelled device S-parameters.

Fig. 4: Measured and modelled pulsed I/V characteristics.

The non linear model has been implemented in a commercial CAD tool (AWR MWOffice in this case).

#### IV. PA DESIGN

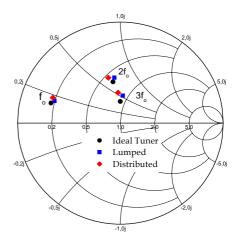

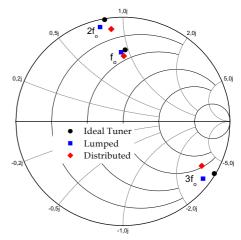

The centre frequency for the PA is  $f_o$ =5.5GHz, while a Class AB bias condition, resulting in a 20% of maximum achievable output current, was selected in order to prevent wrong harmonic current phase generation [3]. Preliminary the optimum input and output optimum load terminations (up to third harmonic frequencies, i.e. 16.5GHz) have been determined, as reported in Fig.5 and Fig.6 respectively (circles).

**Fig.5:** Optimum input harmonic termination synthesised by an ideal tuner, and realised by lumped or distributed networks.

Fig.6: Optimum output harmonic termination synthesised by an ideal tuner, and realised by lumped or distributed networks.

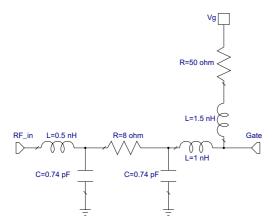

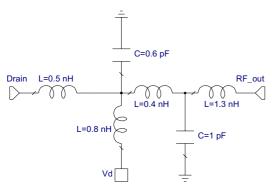

Subsequently, a lumped-element approach has been adopted to implement the optimum load conditions, obtaining the networks reported in Fig.7 and Fig.8 respectively, whose behaviours are reported in Fig.5 and Fig.6 (squares).

Fig.7: Lumped-element implementation of the input network.

Fig.8: Lumped-element implementation of the output network.

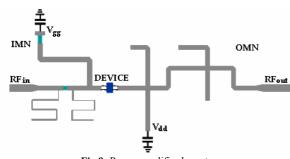

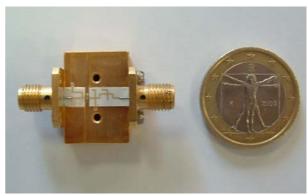

Finally, actual input and output networks have been designed on Alumina substrate ( $\epsilon_r$ =9.8, 381 $\mu$ m thick) with a distributed solution, whose behaviour is plotted in Fig.5 and Fig.6 (diamonds). The resulting layout and the photograph of the realised hybrid PA are reported in Fig.9 and Fig. 10 respectively.

Fig.9: Power amplifier layout.

For the input network, two series-shunt resistors were required to assure respectively in-band and low frequency stability conditions. Then the fundamental large signal conjugate match condition has been assured by a distributed structure, while two open stubs were adopted to properly terminate the second harmonic voltage component generated by the device input nonlinearities.

Fig. 10: Photograph of the power amplifier.

Output matching network is designed to obtain a short circuit condition at  $3f_0$  and purely (optimised) resistive loads at fundamental and  $2f_0$  across the intrinsic drain current source. This has been accomplished via two open stubs, to achieve the theoretical optimum voltage components ratio [8].

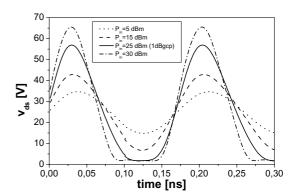

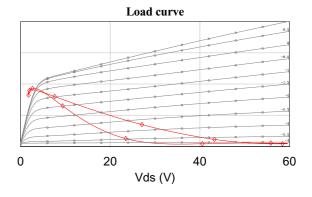

Output voltage waveforms simulated for different input power levels are shown in Fig.11. The voltage waveform @1 dB gain compression (1dBgcp) exhibits the typical "peaking" shape due to a second harmonic component. This behaviour is stressed also in Fig.12, where the intrinsic (i.e. across the current source) load curve at 1dBgcp is reported.

**Fig.11:** Simulated output voltage waveforms for several input power levels.

Fig.12: Simulated intrinsic load curve at 1dBgcp (Pin=25 dBm).

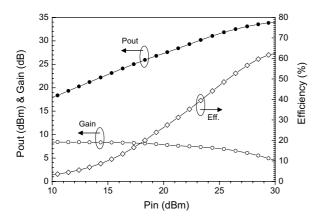

Measured output power and drain efficiency as functions of the input drive at 5.5GHz are shown in Fig.13.

Fig.13: Measured performances at 5.5GHz.

Finally, measured performances of the power amplifier as functions of the frequency from 4.8 to 6.2 GHz for an input power of 28 dBm are reported in Fig.14.

Fig.14: Measured performances for Pin=28 dBm.

## V. CONCLUSION

The design of an hybrid C-Band 2nd harmonic tuned power amplifier based on a GaN device has been discussed. Starting from the device technological realization, its non linear model has been developed and the amplifier design criteria adopted have been briefly presented. Experimental results demonstrate a bandwidth larger than 20% around 5.5GHz, with a minimum output power of 33 dBm and a drain efficiency around 50%.

### VI. ACKNOWLEDGEMENT

Research reported here was performed in the context of the network TARGET— "Top Amplifier Research Groups in a European Team" and supported by the Information Society Technologies Programme of the EU under contract IST-1-507893-NOE, <a href="https://www.target-net.org">www.target-net.org</a>

#### REFERENCES

- [1] F.H.Raab, "Class-F Power Amplifiers with Maximally Flat Waveforms", IEEE Transactions on Microwave Theory and Techniques, Vol. MTT-45, N°11, November 1997, pp.2007-2012.

- [2] S.C.Cripps, RF Power Amplifiers for Wireless Communications, Artech House, 1999.

- [3] P.Colantonio, F.Giannini, E.Limiti, "Nonlinear approaches to the design of microwave power amplifiers", International Journal of RF and Microwave Computer-Aided Engineering, Vol. 14, N 6, Nov. 2004, pp. 493-506.

- [4] P.Colantonio, A.Ferrero, F.Giannini, E.Limiti, V.Teppati, Harmonic Load/Source Pull Strategies For High Efficiency PAs Design, 2003 IEEE MTT-S Symposium Digest, Philadelphia, PA, June 2003, vol.3, pp.1807-1810.

- [5] M. Maeda, H. Masato, H. Takehara, M. Nakamura, S. Morimoto, H. Fujimoto, Y. Ota and O. Ishikawa, "Source Second-Harmonic Control for High Efficiency Power Amplifiers", IEEE Transactions on Microwave Theory and Techniques, Vol. MTT-43, N°12, December 1995, pp.2952-2958.

- [6] G. Dambrine, A Cappy, F. Heliodore, and E. Playez, "A new method for determining the FET small-signal equivalent circuit", IEEE Trans. Microwave Theory Techn., Vol. 36, 1988, pp. 1151-1159

- [7] Iltcho Angelov, Lars Bengtsson, Mikael Garcia, "Extension of the Chalmers non linear HEMT and MESFET model", IEEE Transactions on Microwave Theory and Techniques, Vol. 44, No.10, pp. 1664-1674

- [8] P.Colantonio, F.Giannini, G.Leuzzi, E.Limiti, Multi Harmonic Manipulation for Highly Efficient Microwave Power Amplifiers, International Journal of RF and Microwave Computer-Aided Engineering, Vol.11, N°6, Nov. 2001, pp. 366-384.