# A CMOS 110-dB@40-kS/s Programmable-Gain Chopper-Stabilized Third-Order 2-1 Cascade Sigma-Delta Modulator for Low-Power High-Linearity Automotive Sensor ASICs

José M. de la Rosa, *Member, IEEE*, Sara Escalera, Belén Pérez-Verdú, Fernando Medeiro, *Member, IEEE*, Oscar Guerra, Rocío del Río, *Member, IEEE*, and Angel Rodríguez-Vázquez, *Fellow, IEEE*

Abstract—This paper describes a 0.35-µm CMOS chopper-stabilized switched-capacitor 2-1 cascade  $\Sigma\Delta$  modulator for automotive sensor interfaces. The modulator architecture has been selected from an exhaustive comparison among multiple topologies in terms of resolution, speed and power dissipation. To obtain a better fitting with the characteristics of different sensor outputs, the circuit can be digitally programmed to yield four input-to-output gain values ( $\times 0.5, \times 1, \times 2$ , and  $\times 4$ ) and has been designed to operate within the stringent environmental conditions of automotive electronics (temperature range of -40 °C to 175 °C). In order to relax the amplifier's dynamic requirements for the different modulator input-to-output gains, switchable capacitor arrays are used for all the capacitors in the first integrator. The design of the building blocks is based on a top-down CAD methodology which combines simulation and statistical optimization at different levels of the modulator hierarchy. The circuit is clocked at 5.12 MHz and the overall power consumption is 14.7 mW from a single 3.3-V supply and occupies 5.7 mm<sup>2</sup> silicon area. Experimental results show a maximum SNR of 87.3 dB within a 20-kHz signal bandwidth and 90.7 dB for 10-kHz signals, and an overall DR of 110 and 113.8 dB, respectively. These performance features place the reported circuit at the cutting edge of state-of-the-art high-resolution  $\Sigma\Delta$  modulators.

*Index Terms*—Analog-to-digital conversion, sigma-delta modulation, mixed analog-digital integrated circuits, sampled data circuits.

#### I. INTRODUCTION

**D** URING the last few years there has been a significant increase in the use of electronic sensory systems for the automotive [1]. This is partially fuelled by advances in MEMS technology and the possibility to combine sensors together with DSPs on the same package and even the same chip [2]. Linked to this trend, the necessity arises to design CMOS analog front-ends (AFEs), and specifically analog-to-digital converters (ADCs), capable of coping with the stringent requirements of the automotive industry.

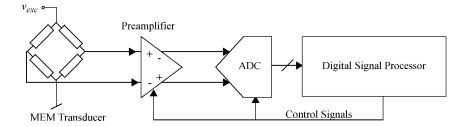

Fig. 1 shows a typical conceptual block diagram for an automotive sensor chip. On the one hand, the converter must be compliant with a very large temperature range, typically

Manuscript received February 15, 2005; revised July 5, 2005. This work was supported by the EU ESPRIT IST Project 2001-34283/TAMES-2 and by the MCyT Projects TEC2004-01752/MIC and TIC2003-09817-C02-01 (VISTA).

The authors are with the Instituto de Microelectrónica de Sevilla, IMSE-CNM (CSIC), 41012-Sevilla, Spain (e-mail: jrosa@imse.cnm.es.

Digital Object Identifier 10.1109/JSSC.2005.857356

$([-40 \circ C, 175 \circ C])$ , and with many other hostile environmental issues [3]–[5]. On the other hand, the AFE must cope with weak signals (ranging from microvolts to hundreds of milivolts) in the presence of large temperature and process dependent offset. The changing amplitude range of the input signal can be handled through programmable gain—similar to what happens in multipurpose sensors [5]. Also, large accuracy and bandwidths up to 10–20 kHz are needed at the ADC to increase the quality of the information delivered to the DSP, and hence the smartness of the system [2].

It is advised that  $\Sigma\Delta$ -based ADCs are used to handle these challenges due to different reasons:

- They are better suited than full Nyquist ADCs to achieve high resolution (16–17 bit) in the band of interest with moderate power consumption [6], [7].

- The action of feedback renders sigma-delta modulators (ΣΔMs) very linear, and high linearity is a must for automotive applications.

- The behavior of some sensing devices fits well to ΣΔ-based ADCs, thus easing partial or total integration of the sensor within the converter [8], [9].

- ΣΔMs can incorporate programmable gain without significant degradation.

However, detailed modeling of circuit nonidealities and involved design plans are needed to take advantage of all these potentials while addressing the stringent environmental and robustness requirements. Actually, several  $\Sigma\Delta$ Ms that digitize 20–25 kHz signals with medium-to-high resolution have been reported [10]–[13]. To the best of our knowledge, the highest resolution (18.7 bits) is featured by the modulator in [11], whereas the lowest power consumption is reported in [12], which targets 14 bits within a 20-kHz signal bandwidth. In all these cases, the modulator input-to-output gain<sup>1</sup> was fixed to unity.

This paper reports a programmable-gain chopper-stabilized third-order cascade (2-1)  $\Sigma \Delta M$  in a 3.3-V 0.35- $\mu m$  CMOS technology. Its design relies upon detailed behavioral modeling and the use of an advanced top-down methodology that combines multilevel behavioral simulation and statistical optimization at different levels of the hierarchy [7]. Experimental results show correct operation in a 20-kHz bandwidth ( $B_w$ )

<sup>&</sup>lt;sup>1</sup>In the following, the term "modulator input-to-output gain" will be referred to as "modulator gain".

Fig. 1. Conceptual block diagram of a "smart" sensor chip.

with 110-dB overall dynamic range (DR), and 113.8-dB DR within  $B_w = 10$  kHz. These figures locate this circuit at the cutting edge of state-of-the-art CMOS  $\Sigma\Delta$ Ms. Also, the herein reported modulator IC is one of the few high-resolution circuits with embedded programmable gain reported to date.

This paper is organized as follows. Section II describes general design considerations. Section III applies those considerations to the proper selection of the modulator architecture and obtains a set of optimized specs for the constituent building blocks. These specs are inputs for the electrical design of the circuit cells, which are covered in Section IV. Finally, Section V gives experimental results and compares the performance of the chip with current state-of-the-art designs.

#### II. BASIC DESIGN CONSIDERATIONS

We choose expandible cascade architectures to implement the modulator [14]. These architectures are advisable as they do not raise stability issues and permit an input voltage amplitude that is close to the theoretical full-scale (FS) input range of the modulator without causing overloading. Actually, the family of expandible cascades exhibits a signal-to-noise ratio (SNR) peak at -5 dBFS regardless of the actual modulator order [14].<sup>2</sup> This helps to handle the changing dynamic range of the sensor signals. Besides, cascade architectures can incorporate a multibit quantizer without resorting to dynamic element matching (DEM) or any other linearization technique [7]. Furthermore, they can be designed by following quite modular, prone- to-optimization plans [14]. Finally, cascade architectures constitute a mature technology demonstrated for a variety of industrial cutting-edge designs [5], [10], [16], [17].

The in-band error power of whatever cascade  $\Sigma\Delta M$  can be expressed as [7]

$$P_{\text{in-band}} \cong P_Q + P_{\text{cn}} + P_{\text{nl}} + P_{\text{st}}$$

(1)

where  $P_Q$  stands for the quantization error,  $P_{cn}$  for the circuit noise error,  $P_{nl}$  for the nonlinearity error, and  $P_{st}$  for the defective settling error.  $\Sigma\Delta Ms$  can be designed such that the quantization error dominates, i.e., such that the following condition is fulfilled:

$$P_{\rm cn} + P_{\rm nl} + P_{\rm st} \ll P_Q$$

$$\cong \frac{1}{12} \left[ \frac{2V_{\rm ref}}{(2^B - 1)} \right]^2 \frac{\pi^{(2L)}}{(2L+1) \cdot M^{(2L+1)}} \quad (2)$$

<sup>2</sup>The use of multibit quantization in every stage of the cascade modulator might result in SNR peaks close to the theoretical FS voltage [15]. However, linearization techniques need to be used in order to reduce the nonlinearity of the internal D/A converters.

where the right term shows the quantization error, neglecting leakage, as a function of the modulator order (L), the oversampling ratio (M), and the number of bits in the internal quantizer (B).  $V_{ref}$  stands for the FS reference voltage of the  $\Sigma\Delta M$ .

In our case, and given the high accuracy target, to make the quantization error dominate would lead to huge power consumption and area occupation. Instead, it is more efficient to make the design such that  $P_Q \cong P_{cn} + P_{nl} + P_{st}$ . Two basic considerations arise related to this criterion: first, to make a comparative balance among the several circuit error contributions; second, to find expression linking the dominant circuit errors to the circuit design parameters. Regarding the balance and owing to the limited bandwidth it can be assumed that  $P_{st} \ll P_{cn}$ . Besides, since the available supply voltage grants large enough room for signal excursion, it can be assumed that  $P_{nl} \ll P_{cn}$ . Under these assumptions, the basic design criterion reduces itself to equalize the quantization error and the circuit noise error, i.e.,  $P_Q \cong P_{cn}$ .

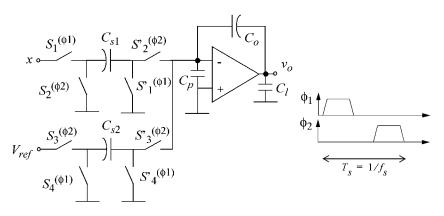

Let us now focus on the expression of the circuit noise error as a function of the circuit design parameters. Consider to that purpose the conceptual schematic of the two-branch switched-capacitor (SC) integrator in Fig. 2, where the input branch and the DAC feedback branch employ different capacitors respectively to implement a modulator gain  $\xi = C_{s1}/C_{s2}$ . The main contributors to the noise error are the operational transconductance amplifier (OTA) thermal and flicker noise, and the switch on-resistance thermal noise. Also, noise coming from the  $V_{ref}$  generation block must be accounted for as a combination of white noise and flicker noise [18].

Flicker noise will be handled at the architectural level by applying chopper techniques [4], [5], so that only white noise remains to dictate electrical design considerations; i.e.,  $P_{\rm cn} \approx P_{\rm wn}$ . Careful analysis including folding mechanisms shows that the input white noise power spectral density (PSD) at the input of each branch of the fully differential circuitry can be approximated at low frequencies by [19]

$$S_{\text{in},C_{s1}}(f) \cong \frac{4kT}{C_{s1}f_S} + \frac{4kT(1+n_t)}{3C_{\text{eq},i}f_S}$$

$$S_{\text{in},C_{s2}}(f) \cong \frac{4kT}{C_{s2}f_S} + \frac{4kT(1+n_t)}{3C_{\text{eq},i}f_S} + \frac{kT}{C_{s2}f_S} \cdot \frac{R_{\text{eq},\text{ref}}}{2R_{\text{on}}}$$

(3)

where k is the Boltzman constant, T is the absolute temperature, and  $R_{on}$  is the switch on-resistance. The first term in each equation above contains the contribution of all the switches in the

Fig. 2. Two-branch SC integrator.

corresponding branch. The second term accounts for the OTA contribution, where

$$C_{\text{eq},i} = C_p + C_{s2}(1+\xi) + C_l \left[ 1 + \frac{C_p + C_{s2}(1+\xi)}{C_o} \right]$$

(4)

is the OTA equivalent load during the integration phase, while  $\phi_2$  is high. When estimating the white noise PSD of the OTA, the contributions of MOS devices other than the input ones are compiled in the factor  $n_t$ , which equals the summation of the respective transconductance ratios. The third term in the expression of  $S_{\text{in},C_{s2}}$  represents the noise coming from  $V_{\text{ref}}$ , where  $R_{\text{eq,ref}}$  is its equivalent noise resistance.

By neglecting contributions other than those of the first integrator in the cascade, the  $\Sigma\Delta M$  output white noise power is obtained as

$$P_{\rm wn} \cong \frac{4kT}{MC_{s2}} (1+\xi) + \frac{4kT(1+n_t)}{3MC_{\rm eq,i}} (1+\xi)^2 + \frac{kT}{MC_{s2}} \frac{R_{\rm eq,ref}}{2R_{\rm on}}.$$

(5)

Quantitative analysis of (5) shows that the white noise power increases with the  $\Sigma\Delta M$  gain,  $\xi$ . In practice, this means that as the gain increases, the capacitances must be increased as well, and thus does the power consumption. This is worsened because as  $\xi$  increases, the OTA equivalent load increases [see (4)] and hence, more power is needed to meet the dynamic requirements.

Seeking minimum power consumption dictates setting  $\xi$  as close as possible to unity. Actually, for  $\xi = 1$ , the two branches in Fig. 2 can be merged into one, thus further reducing  $P_{\rm wn}$  and, consequently,  $C_{\rm eq,i}$ . This is the choice commonly found in literature [5]. However, such a choice implies that in a sensor A/D interface like that shown in Fig. 1, the programmability must be incorporated into the preamplifier, rendering its design more complicated.

In the application under consideration, the automotive sensor interface must accommodate a huge range of signal amplitudes (130 dB below full scale) within a 20-kHz bandwidth. For this purpose, the preamplifier is designed with a fixed gain of ×10, whereas the  $\Sigma\Delta$  modulator can be digitally programmed to yield four gain values—×0.5, ×1, ×2, and ×4. This solution simplifies the architecture and design of the preamplifier, which in this case consists of a resistor-feedback instrumentation topology—*a priori* a less demanding design than using a programmable-gain (×5, ×10, ×20, and ×40) amplifier based

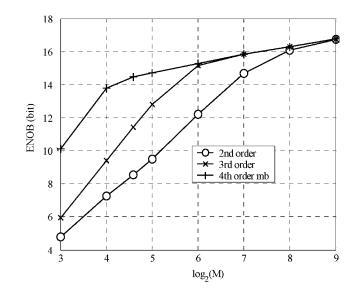

Fig. 3. Effective number of bits (ENOB) versus oversampling ratio for three  $\Sigma \Delta$  Ms: fourth-order 3-bit (L = 4, B = 3), third-order 1-bit (L = 3, B = 1) and second-order 1-bit (L = 2, B = 1).

on switchable elements (capacitors or resistors), given the stringent noise and linearity requirements.

#### **III. ARCHITECTURE SELECTION AND HIGH-LEVEL SIZING**

Architecture selection involves three parameters, namely oversampling ratio (M), loop order (L), and the resolution of the internal quantizer (B). These three parameters univocally define an instance of the general expandible  $2 - 1^{L-2}$  cascade architecture [14].<sup>3</sup>

How are the values of these parameters chosen? A first observation is that, for every value of L and B, as M increases there is a transition from one region where  $P_Q \gg P_{wn}$  into another where  $P_Q \ll P_{wn}$ . It is illustrated in Fig. 3, which shows the effective resolution of three  $\Sigma \Delta Ms$  as a function of M. The same front-end integrator is used for the three cases. For each curve there is a breakpoint where  $P_Q \cong P_{wn}$ . Above this breakpoint, within the region dominated by white noise, doubling M generates a mere 3 dB decrease in the in-band error power. Below this breakpoint the decrease of the error with M depends on the

<sup>&</sup>lt;sup>3</sup>The term  $2 - 1^{T_i-2}$  is used in this paper to denote a *L*th-order cascade modulator formed by a second-order stage followed by L-2 identical first-order stages.

| Σ $\Delta$ M Gain, ξ | Order $(L)^{a}$ | Oversampling Ratio $(M)$ | Estimated Power Consumption (mW) |

|----------------------|-----------------|--------------------------|----------------------------------|

| 0.5                  | 3               | 128                      | 6.77                             |

|                      | 3               | 256                      | 8.12                             |

|                      | 4               | 128                      | 8.27                             |

| 1                    | 3               | 128                      | 8.48                             |

|                      | 3               | 256                      | 9.77                             |

|                      | 4               | 128                      | 10.32                            |

| 2                    | 3               | 128                      | 12.69                            |

|                      | 3               | 256                      | 13.85                            |

|                      | 2               | 512                      | 13.88                            |

| 4                    | 2               | 512                      | 23.24                            |

|                      | 3               | 128                      | 24.21                            |

|                      | 3               | 256                      | 25.02                            |

TABLE I Outcome of the  $\Sigma\Delta M$  Architecture Selection Procedure

a. All  $\Sigma \Delta Ms$  in this table are cascade 2-1<sup>L-2</sup> architectures except for L = 2.

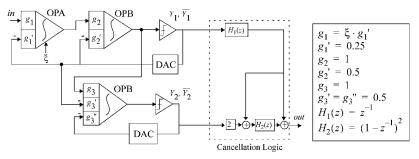

Fig. 4. Block diagram of the programmable-gain 2–1 cascade SC  $\Sigma \Delta M$ .

actual values of L and B. The only way to shift the breakpoint up is by enlarging the sampling capacitor.

This observation provides rationale supporting the choice of  $P_Q \cong P_{wn}$ , namely:

- within the region dominated by quantization noise, the sampling capacitor, and hence the demands on building block dynamics, area and power, are larger than needed;

- within the region dominated by white noise, oversampling becomes less inefficient (only a fraction 1/M of the noise power falls into the signal bandwidth) and either L or B, or both, may allow a reduction without significant impact on resolution.

Actually, most state-of-the-art circuits are designed to operate close to but at the right side of this breakpoint [7].

A second qualitative observation is related to the choice of M. On the one hand, the condition  $P_Q \cong P_{wn}$  defines an univocal relationship between each  $\{L, B\}$  pair and M. On the other hand, since the targeted bandwidth is medium to low, constraints on M are not strong. This means that there are fairly large degrees of freedom to set M, L, and B. As a rule of thumb, since the targeted resolution is only moderately high, the oversampling ratio does not need to be extremely high. This means that the breakpoint in Fig. 3 can be moved to the left, providing room for many possible combinations of B and L.

Actual architecture selection is driven by power minimization, based on the following iterative procedure:

1) For given values of  $L, M, B, V_{ref}$ , and  $\xi$ , calculate  $P_Q$  and select  $C_{s2}$  so that  $P_Q + P_{wn}$  is smaller than the maximum allowed in-band error power.

- 2) Estimate  $C_{eq,i}$  from (4). Then, use a linear settling model with settling constant  $C_{eq,i}/g_m$  to estimate the required OTA transconductance, taking into account that it takes a number  $\ln(2^{ENOB})$  of time constants to settle within effective number of bits (ENOB) resolution.

- 3) Relate the OTA  $g_m$  with its power dissipation, for which the candidate OTA topology must be known *a priori*. A suitable selection is closely linked to the process technology: supply voltage, minimal device length, etc. Potential choices are a folded-cascode OTA up to 3-V supply, and a two-stage amplifier below 2.5 V [20].

- 4) Once the first integrator power dissipation is estimated, that of the remaining integrators (in practice with less demanding specifications) can be estimated as a fraction of it. The overall static power is then obtained by adding up all the contributions.

For realistic estimation, this procedure is fine-tuned by including the impact of other nonideal effects (such as finite and nonlinear OTA DC-gain, slew-rate, errors in the multibit quantizers, etc.), the power dissipated in other blocks, and the dynamic power dissipation [14], [16].

## A. Modulator Architecture

Previous design considerations have been applied for the target specs of 40 kS/s and DR  $\geq 110$  dB. A large number of architectures have been compared in terms of the estimated power consumption and silicon area. The outcome of the comparison, summarized in Table I for  $\Sigma\Delta$ Ms with a 1-bit internal quantizer, led us to choose the third-order 2-1 cascade  $\Sigma\Delta$ M shown in Fig. 4 with  $M \geq 128$ . Note from Table I that the

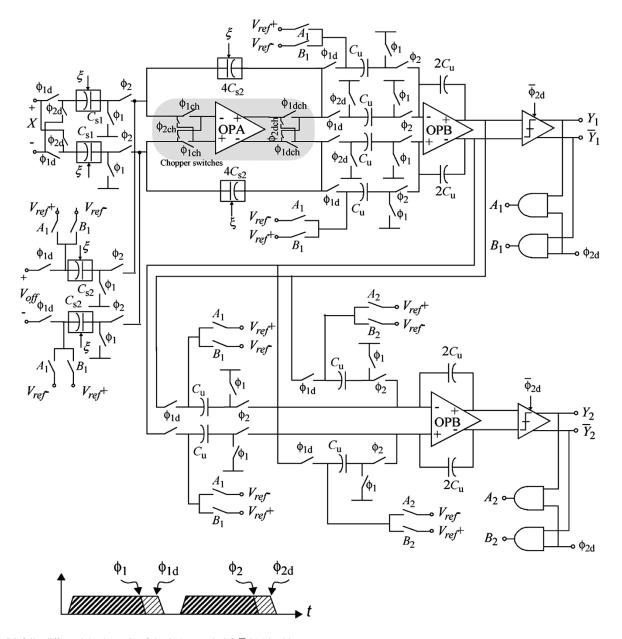

Fig. 5. SC fully differential schematic of the 2–1 cascade SC  $\Sigma\Delta M$  in this paper.

architecture in Fig. 4 obtains the best results, except for  $\xi = 4$ . In this case, the lowest power consumption is obtained by a second-order  $\Sigma \Delta M$  with M = 512, the third-order cascade being the second one in the ranking. However, the second-order architecture does not qualify for some values of  $\xi$ . Also, it requires a four times faster clock than the cascade, thereby increasing the issues related to substrate noise coupling.

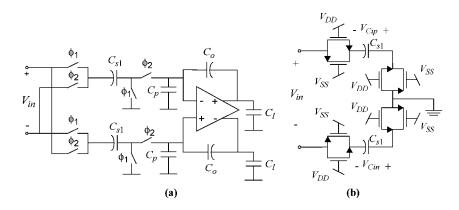

## B. SC Implementation

Fig. 5 shows the fully differential SC schematic of the selected  $\Sigma\Delta M$  architecture. Note that the SC branch connected to the input signal in the first integrator uses double sampling to achieve an extra gain of 2, without increasing circuit noise [21]. The other branch receives the digital-to-analog converter (DAC) outputs. Making use of the spare connection of this branch, an external DC signal ( $V_{\text{off}}$ ) can be applied during  $\phi_1$  to center the sensor signal in the modulator full-scale range. This solution renders unnecessary a third branch for offset compensation; it can therefore be eliminated, and results in no further increase of thermal noise.

The second stage of the modulator incorporates an integrator with only two input branches, although three different weights are implemented:  $g_3, g'_3$ , and  $g''_3$  (see Fig. 4). This can be done because the selection of weights in the designed modulator, considering that  $g_3/g'_3 = g_3/g''_3$ , allows the distribution of weight  $g_3 = 1$  between the two integrator branches, namely  $g'_3 = 0.5$  and  $g''_3 = 0.5$ .

The modulator operation is controlled by two nonoverlapped clock phases, namely sampling phase  $\phi_1$  and integration phase  $\phi_2$ . In order to attenuate the signal-dependent clock feedthrough, delayed versions of the two phases ( $\phi_{1d}$  and  $\phi_{2d}$ ) are also provided. As illustrated in Fig. 5, this delay is incorporated only to the falling edges of the clock phases (i.e., to the turn-off of the switches), while the rising edges are

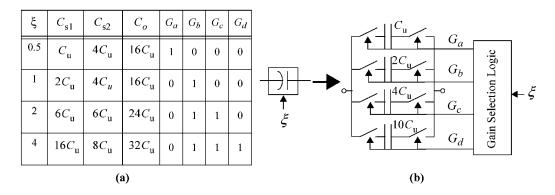

Fig. 6. Programmable capacitors in the first integrator. (a) Capacitor arrays. (b)  $C_{s1}$  implementation.

synchronized in order to increase the effective time-slot for the modulator operations [17]. The comparators are activated at the end of phase  $\phi_2$  (using  $\overline{\phi_{2d}}$  as a strobe signal) to avoid any possible interference due to the transient response of the integrators' outputs at the beginning of the sampling phase. In addition to the master clock phases,  $\phi_1$  and  $\phi_2$ , additional phases are required to control the chopper switches used in the first integrator to attenuate flicker noise. These chopper phases are controlled by a master clock with programmable frequency, as will be described in Section IV.

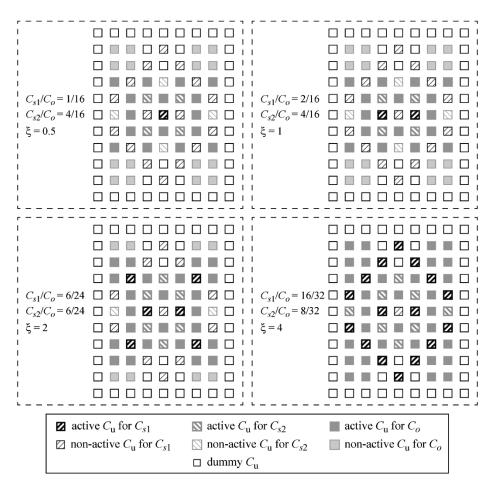

The programmable gain ( $\xi = 0.5, 1, 2$ , and 4) has been mapped onto switchable capacitor arrays, each of them formed by a variable number of unitary capacitors ( $C_u = 1.5 \text{ pF}$ ) as shown in Fig. 6. Such numbers are selected for minimum power dissipation, bearing in mind the circuit noise limitation and the maximum temperature target (175 °C). In order to keep the amplifier dynamic requirements as relaxed as possible, we propose to switch all unitary capacitors instead of just those forming the sampling capacitors. This is based on the following.

- For large gains (ξ > 1) C<sub>s1</sub> is larger than C<sub>s2</sub>. Hence, P<sub>wn</sub> is amplified with respect to the unity-gain case as it multiplied by (1 + C<sub>s1</sub>/C<sub>s2</sub>) [see (5)].

- For low gains ( $\xi < 1$ ) the situation is the contrary. Now  $P_{\rm wn}$  is attenuated with respect to the unity-gain case, which allows us to decrease the capacitance values, mainly  $C_{\rm s2}$ . This strategy also relaxes the required amplifier dynamics because its equivalent load capacitance will also be decreased.

- In order to simultaneously handle the modulator gain<sup>4</sup>  $(2C_{s1}/C_{s2})$  and the first integrator feedback weight  $(C_{s2}/C_o$  always equal to 0.25), the value of all capacitances must be changed by re-arranging the number of unitary capacitors forming them.

## C. High-Level Sizing and Building-Block Specifications

The modulator specifications have been mapped onto building-block specifications using statistical optimization for design parameter selection, and compiled equations (capturing nonideal building-block behavior) for evaluation. This process is fine-tuned by behavioral simulation using an updated version of ASIDES, an advanced behavioral simulator of SC  $\Sigma\Delta$ Ms

<sup>4</sup>An extra signal gain of 2 is considered as a consequence of using double sampling in the first integrator.

[22]. At this step, nonidealities are covered more accurately than when compiled equations are used. Also, worst cases for speed (the largest capacitor values) and for thermal noise (the highest temperature and the lowest capacitor values) are contemplated.

The outcome of this sizing process is summarized in Table II, where OPA denotes the opamp used at the first integrator and OPB refers to the opamps used at the second- and third-integrator (see Fig. 5). The data in Table II show the specifications of the building blocks that define the starting point for the block sizing that will be described in Section IV.

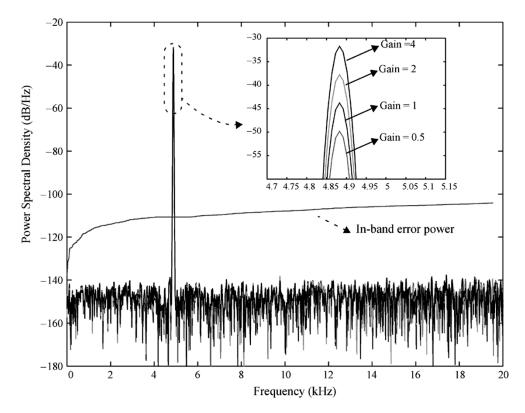

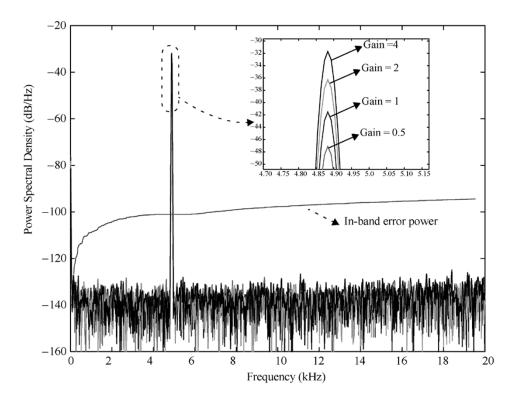

The system-level performance of the modulator has been verified considering the parameters in Table II. Fig. 7 shows the in-band output spectra for the different modulator gains, clocked at  $f_S = 5.12$  MHz and considering a -20-dBV, 5-kHz input sinewave. The in-band error<sup>5</sup> power is also depicted. The figure shows that the total in-band error is, despite the gain, larger than 100 dB below FS ( $V_{ref} = 2$  V), as required for the proposed application. The DR is boosted by the modulator gain, leading to an overall DR referred to FS (DRFS) larger than 118 dB.

## IV. DESIGN OF THE BUILDING BLOCKS

## A. Amplifiers

The key features for the design of the amplifiers are their open-loop DC gain, dynamic requirements and output swing. Regarding the latter, the set of integrator weights used for the  $\Sigma\Delta M$  in Fig. 5 allow us to relax the output swing requirements to being only slightly larger than the voltage reference (2 V in this case), which is feasible when operating with 3.3-V supply in differential mode.

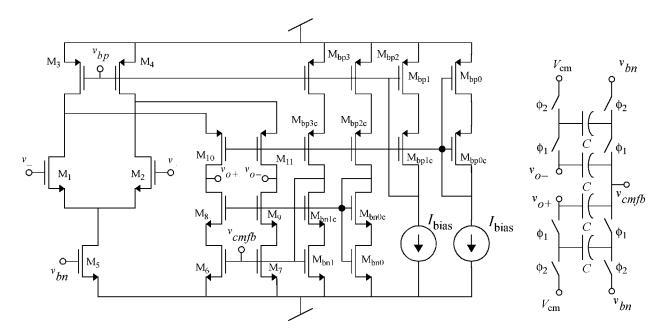

Table II shows that OPA is more demanding than OPB, the reason being that the contribution of the latter to the total in-band error power is attenuated by the gain of the front-end integrator in the signal band. Thus, to reduce power consumption, OPA and OPB are handled as different instances during the design purposes. For this goal, an improved version of the transistor-level sizing tool FRIDGE [22] was used to explore the potentials of a wide catalog of fully differential OTA topologies. A single-stage folded-cascode architecture, shown in Fig. 8, was selected as

<sup>&</sup>lt;sup>5</sup>The in-band error power includes noise and distortion caused by circuit error mechanisms.

| 8           | SPECS: 110-dB@40kS/s@        | ۵۷ <sub>p</sub>   | Value              | Unit |

|-------------|------------------------------|-------------------|--------------------|------|

|             |                              | Gain 0.5          | 24                 | pF   |

|             | Integration consoitor        | Gain 1            | 24                 | pF   |

|             | Integration capacitor        | Gain 2            | 36                 | pF   |

|             |                              | Gain 4            | 48                 | pF   |

| INTEGRATORS | Unitary capacitor            |                   | 1.5                | pF   |

|             | Sigma                        |                   | 0.1                | %    |

|             | Capacitor non-linearity      | 25                | ppm/V <sup>2</sup> |      |

|             | Bottom parasitic capac       | 5                 | %                  |      |

|             | Switch ON-resistance         | <650              | Ω                  |      |

|             | DC agin                      | OPA               | 68                 | dB   |

|             | DC-gain                      | OPB               | 63                 | dB   |

|             | DC-gain non-linearity        |                   | 15%                | V-2  |

| OPAMPS      | ODW                          | OPA (44.2pF load) | 17                 | MHz  |

| OPAMPS      | GBW                          | OPB (8.9pF load)  | 15                 | MHz  |

|             | C1                           | OPA (44.2pF load) | 17                 | V/μs |

|             | Slew-rate                    | OPB (8.9pF load)  | 28                 | V/µs |

|             | Output swing                 |                   | ±2.5               | v    |

| COMPARATORS | (Hysteresis + Offset) (max.) |                   | 30                 | mV   |

| COMPARATORS | Resolution time              | 50                | ns                 |      |

TABLE  $\,$  II High-Level Sizing of the Programmable-Gain 2–1  $\Sigma\Delta M$

Fig. 7. In-band (20 kHz) simulated output spectra of the proposed  $\Sigma\Delta M$  (see Fig. 5) for different modulator gains.

a convenient choice for both amplifiers. N-channel input transistors were employed to take advantage of the twin-well technology feature in removing the body effect of nMOS transistors. The common-mode feedback (CMFB) net has been implemented using a SC circuit, which provides fast linear operation with small power dissipation.

Table III shows the full sizing and biasing of OPA and OPB. Table IV summarizes the obtained electrical performance for both amplifiers using HSPICE, regarding the target values imposed during the optimization procedure with FRIDGE. The table depicts the parameter values corresponding to typical operation conditions (typical process parameters, nominal supply

Fig. 8. Fully differential folded-cascode amplifier used in the  $\Sigma\Delta$  modulator.

| TABLE III                        |

|----------------------------------|

| SIZING AND BIASING OF THE OPAMPS |

|                         | SIZES         |                |

|-------------------------|---------------|----------------|

| Transistor              | OPA (µm/µm)   | OPB (µm/µm)    |

| M <sub>1,2</sub>        | 5x(40/0.5)    | 2x(25/0.5)     |

| M <sub>3,4</sub>        | 8x(65.6/0.5)  | 8x(25.5/0.5)   |

| M5                      | 8x(42.5/0.5)  | 8x(10.7/0.5)   |

| M <sub>6,7</sub>        | 5x(32/0.5)    | 5x(8/05)       |

| M <sub>8,9</sub>        | 8x(31.05/0.6) | 8x(5.65/0.45)  |

| M <sub>10,11</sub>      | 8x(64/0.5)    | 8x(30.20/0.45) |

| M <sub>bp0</sub>        | 8.85/0.5      | 4/0.5          |

| M <sub>bp1,2,3</sub>    | 65.6/0.5      | 25.5/0.5       |

| M <sub>bpc0,1,2,3</sub> | 64/0.5        | 30.20/0.45     |

| M <sub>bn0</sub>        | 4.45/0.5      | 1.9/0.5        |

| M <sub>bnl</sub>        | 42.5/0.5      | 10.7/0.5       |

| M <sub>bnc1,2</sub>     | 31.05/0.6     | 5.65/0.45      |

|                         | BIASING       |                |

| I <sub>bias</sub> (μA)  | 110           | 36.7           |

TABLE

IV

Electrical Performance of the Opamps (HSPICE)

|                         | OPA (4  | 5pF load)  | OPB (9pF load) |            |

|-------------------------|---------|------------|----------------|------------|

| Model                   | Typical | Worst-Case | Typical        | Worst-Case |

| DC gain (dB)            | 74.0    | 71.09      | 68.3           | 68.3       |

| GB (MHz)                | 22.6    | 15.8       | 34.4           | 23.8       |

| Phase Margin (°)        | 86.4    | 85.5       | 83.5           | 81.4       |

| Slew-Rate (V/µs)        | 22.1    | 21.1       | 38.1           | 35.7       |

| Output Swing (V)        | ±2.75   | ±2.50      | ±2.75          | ±2.50      |

| Transconductance (mA/V) | 6.30    | 4.50       | 1.95           | 1.35       |

| Power consumption (mW)  | 7.1     | 7.2        | 2.3            | 2.4        |

voltage, and room temperature) as well as the worst case value for each parameter in a corner analysis—considering fast and slow device models,  $\pm 10\%$  variation in the 3.3-V supply, and temperatures in the range [-40 °C, +175 °C].

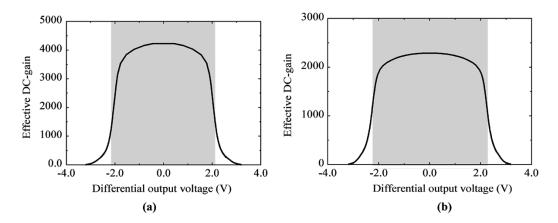

The amplifier nonlinear features (mainly nonlinear DC gain and dynamics) deserve special attention in a high-linear implementation. When the amplifier output swings, the drain-tosource voltage of the output transistors changes, and so does the output impedance. This effect, illustrated in Fig. 9 for the OPA and OPB in the nominal conditions, induces a dependence of the open-loop DC gain on the output voltage; the DC gain reaches its maximum at the central point and decreases as the output approaches the rails. Such a nonlinearity is traditionally modeled by second-order polynomial dependence of the gain on the output voltage [7], but this is only valid for small voltage excursions around the central point. On the contrary, in the proposed 3.3-V implementation, it is expected that small-gain regions of the DC curve (around boundaries of shadowed areas in Fig. 9) are often visited during normal operation of the modulator. In order to accurately account for this nonlinearity during behavioral simulations, we have resorted to a table look-up procedure based on amplifier DC curves obtained by electrical simulation. A similar approach has been employed to validate the actual transient response of the front-end integrator.

## B. Comparators

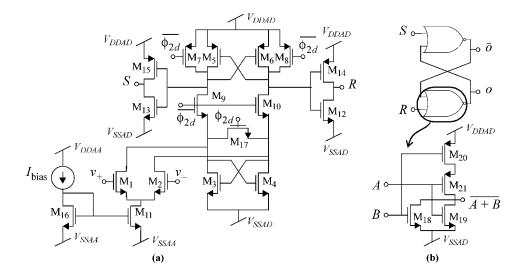

The specifications for the single-bit quantizers (comparators) at the end of the first and second stages of the modulator are given in Table II. In order to cope with the required resolution time (around 50 ns) and hysteresis (lower than 30 mV) a regenerative latch including a pre-amplifying stage was selected [23].

Fig. 10 shows the selected comparator topology. It consists of a nMOS differential input pair  $(M_{1-2})$ , a CMOS regenerative latch circuit, and a RS flip-flop. The latch circuit is composed of a nMOS flip-flop  $(M_{3-4})$  with a pair of nMOS switches  $(M_{9-10})$  for strobing and a nMOS switch  $(M_{17})$  for resetting, and a pMOS flip-flop  $(M_{5-6})$  with a pair of pMOS precharge switches  $(M_{7-8})$ .

The comparator is activated at the end of the integration phase. At the beginning of the next integration phase, the out-

Fig. 9. DC-gain nonlinearity for (a) OPA and (b) OPB.

Fig. 10. Schematic of the comparator. (a) Preamplifier + latch. (b) RS flip-flop.

puts of the latch are forced to the low state and the RS flip-flop maintains the comparator output until the next strobbing of the latch. As shown in Fig. 10, different voltage supplies have been used for the pre-amplifier and for the regenerative latch— $V_{\text{DDAA}}$  and  $V_{\text{DDAD}}$ , respectively. This has been done in order to reduce the comparator sensitivity to injected digital switching noise and supply bounce effects.

The circuit in Fig. 10 has been designed according to the required high-level specifications, while keeping the input capacitance and the power consumption as low as possible. Table V shows the sizes of the transistors and the value of the bias current.

MonteCarlo simulations and corner analysis have been done to extract the comparator performance during sizing. Table VI summarizes its electrical performance, showing the worst cases for hysteresis, offset and resolution time together with the power dissipation. As expected, the resolution is dominated by mismatching, the offset being the dominant limitation factor with a worst case value of 9.92 mV, which is compliant with the specifications in Table II.

## C. Switches

The main design issue related to the switches is the finite switch on-resistance,  $R_{on}$ , which is mainly constricted by dy-

TABLE

V

Sizing and Biasing of the Comparators

Comparators

| MOST                       | W/L (μm/μm) |

|----------------------------|-------------|

| M <sub>1,2</sub>           | 20/0.5      |

| M <sub>3,4</sub>           | 4/2         |

| M <sub>5,6</sub>           | 16/2        |

| M <sub>7-10,12-15,17</sub> | 1.5/0.35    |

| M <sub>11,16</sub>         | 8/1         |

| M <sub>18</sub>            | 6.3/0.35    |

| M <sub>19</sub>            | 4.2/0.35    |

| M <sub>20,21</sub>         | 11.9/0.35   |

| I <sub>bias</sub>          | 55μΑ        |

namic considerations. Incomplete settling caused by transmission gates is traditionally reduced by making  $R_{\rm on}C_{s1}f_S \ll 1$ . In our circuit,  $R_{\rm on}$  values up to 650  $\Omega$  (see Table II) can be tolerated with no degradation of the modulator performance. These values can be obtained using CMOS switches with aspect ratios of 6.5/0.35 for the nMOS transistor and 23.5/0.35 for the pMOS, operating with the nominal 3.3-V supply.

Fig. 11. Analog switches: (a) fully differential SC integrator; (b) circuit under evaluation.

TABLE

VI

Electrical Performance of the Comparators (HSPICE)

| Parameter                    | Typical                     | Worst-case |

|------------------------------|-----------------------------|------------|

| Offset (mV)                  | 0.75                        | 9.92       |

| Hysteresis (mV)              | 0.03                        | 0.12       |

| Resol. time, $T_{RLII}$ (ns) | 4.10                        | 8.60       |

| Resol. time, $T_{RIIL}(ns)$  | 3.90                        | 6.15       |

| Power Consumption (mW)       | Power Consumption (mW) 0.43 |            |

In addition to the  $R_{\rm on}$  value, the dependence of this value with voltage must be carefully addressed. This nonlinearity causes dynamic distortion during the sampling process—the larger the sampling capacitor and the signal frequency, the larger the distortion [24]. In our case, the distortion is particularly noticeable for  $\xi = 4$ , where  $C_{s1} = 24$  pF. To keep it under specs, one first possibility is using smaller  $R_{on}$  values. However, this leads to prohibitive parasitics and power dissipation. Another possibility is including clock-bootstrapping [25]. However, this increases complexity and leads to a less robust design. Instead, we have studied in depth the sampling process of the first SC integrator [see Fig. 11(a)], seeking optimization. Electrical simulations of the circuit in Fig. 11(b) have been done using corner analysis for a 0 dBV at 20 kHz sine-wave input. The differential voltage stored in capacitors  $C_{s1}$  was collected at a rate of 5.12 MHz, and a Kaiser-windowed fast Fourier transform (FFT) was processed.

Table VII summarizes the total harmonic distortion (THD) values obtained during corner analysis. Note that the worst case THD generated by the analog switches is -100 dB, which agrees with required specifications. Thus, the sizing used for the CMOS switches in the front-end integrator—with aspect ratios of 29.1/0.35 for the nMOS transistor and 105.9/0.35 for the pMOS—ensures a distortion low enough for the present application, and suggests that clock boosting or similar techniques are not required in the technology used.

#### D. Capacitor Arrays

Capacitors have been implemented using MIM structures. With this structure, the 1.5-pF unitary capacitor used to implement the integrator weights is approximately

TABLE

VII

THD CAUSED BY ANALOG SWITCHES FOR A 1 Vpd at 20 kHz INPUT TONE

| Model   | Temperature (°C) | THD (dB) |

|---------|------------------|----------|

|         | -40              | -100     |

| Slow    | 25               | -101     |

|         | 175              | -102     |

|         | -40              | -104     |

| Typical | 25               | -105     |

|         | 175              | -107     |

|         | -40              | -109     |

| Fast    | 25               | -110     |

|         | 175              | -112     |

31.6  $\mu$ m × 31.6  $\mu$ m in size. The estimated mismatch for this capacitor is  $\sigma(\Delta C/C) = 0.1\%$ . As mismatch error is one of the most important limiting factors in cascade architectures, common centroid structures have been used in the layout. For the first integrator, all the capacitors ( $C_{s1}, C_{s2}$ , and  $C_0$  in Fig. 6) are made up of unitary capacitors that are connected or disconnected from an array structure depending on the value of the modulator gain. The arrangement of unitary instances in this programmable common-centroid structure is symbolically shown in Fig. 12. On the other hand, the matching of weights  $g'_2, g'_3$ , and  $g''_3$  is just based on closely placed unitary capacitors.

#### E. Clock-Phase Generators

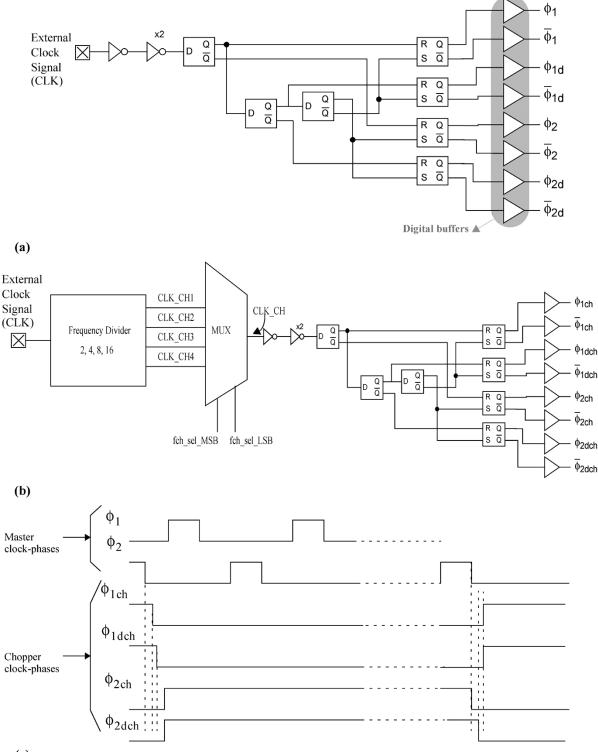

Two clock-phase generator circuits have been incorporated to the prototype: one of them generates the master clock phases and the other one provides the chopper phases required by the first integrator (see Fig. 5).

Fig. 13 shows the schematics of the two clock-phase generators. Both of them generate two nonoverlapped clock phases  $(\phi_1, \phi_2, \phi_{1ch}, \phi_{2ch})$  from an external clock signal CLK. In order to avoid signal-dependent clock feedthrough, delayed versions of the two phases  $(\phi_{1d}, \phi_{2d}, \phi_{1dch}, \phi_{2dch})$  are also generated [26]. The complementary versions of these phases are also generated  $(\bar{\phi}_j)$  in order to control the CMOS switches, and all phases are properly buffered at the generators output. A buffer tree is used for that purpose, given the assorted capacitive loads that the different clock phases have to drive. In order to relax the requirements on the integrators' transient response, especially for the case  $\xi = 4$ , the external clock signal has a duty cycle of 77.5%–22.5% (integration-sampling phases). With the clock

Fig. 12. Conceptual layout of programmable capacitor array of the front-end integrator.

scheme used, conceptually shown in Fig. 13(c), the nonoverlapping time and the delay time are approximately 0.2 ns, while the effective time-slot for integrators operations is 151.37 ns for  $\phi_1, \phi_{1d}, \overline{\phi}_1, \overline{\phi}_{1d}$ , and 43.54 ns for  $\phi_2, \phi_{2d}, \overline{\phi}_2, \overline{\phi}_{2d}$ .

## V. EXPERIMENTAL RESULTS

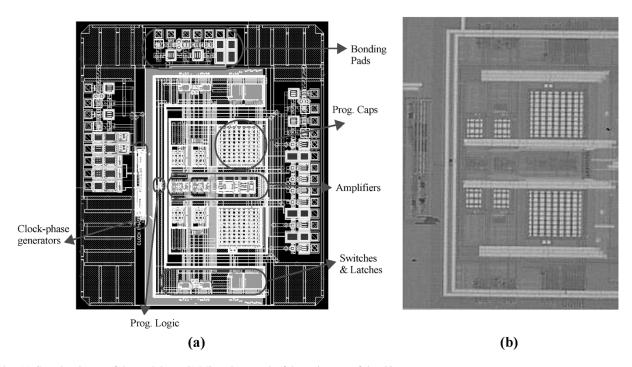

The modulator has been designed and fabricated in a singlepoly, five-metal,  $0.35-\mu$ m CMOS technology. Fig. 14 shows the complete layout [Fig. 14(a)] and a microphotograph of the main parts of the chip [Fig. 14(b)]. The layout has been carefully designed to maximize the modulator performance according to the following considerations:

- The distance between the most sensitive analog blocks (front-end) and the digital section is the longest possible in order to attenuate the impact of the switching activity.

- Separated analog, mixed, and digital supplies have been used. Analog power supplies have been employed for the current biasing of the analog blocks in the  $\Sigma\Delta$  modulator (mainly the amplifiers and the pre-amplifiers stages of the comparators), as well as the voltage biasing of the substrate and wells in the analog section of the chip. Mixed supplies have been dedicated to the integrator switches, the dynamic CMFB nets for the amplifiers and the comparators regenerative latches. Digital power supplies have been used for the biasing of the clock-phase generators and for the two

buffers driving the output of the modulator stages out of the chip.

- Guard-rings that surround the analog, mixed, and digital sections of the chip, have been included in order to maintain a low impedance return path and avoid the spreading of digital switching noise to the sensitive parts of the modulator.

- The layout has been kept symmetrical and centroid layout techniques with unitary transistors have been employed for matched transistors in the operational amplifiers, and in the preamplifying stages and regenerative latches of the comparators.

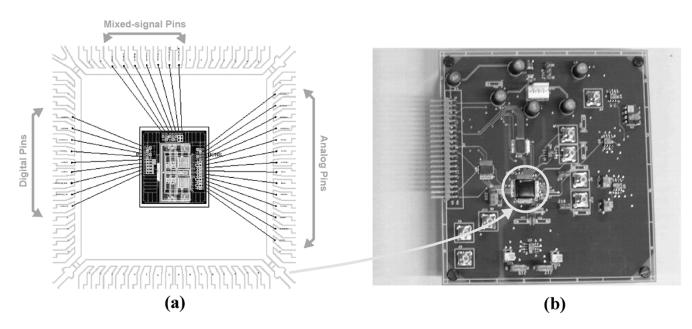

The complete modulator occupies an area of  $5.7 \text{ mm}^2$  (pads included) and dissipates 14.7 mW from a single 3.3-V supply. The chip is encapsulated in 64-pin plastic quad flat package as illustrated in Fig. 15(a). Double-bonding techniques and multiple pins are used for the power supplies in order to reduce supply bounce.

The circuit has been tested using a printed circuit board (PCB), shown in Fig. 15(b), that includes intensive filtering and decoupling strategies, as well as proper impedance termination to avoid signal reflections. The performance of the modulator was evaluated using a high-resolution (-100-dB THD) sinusoidal source to generate the input signal and a digital data acquisition unit to generate the clock signal and to acquire the bit streams of the first and second stages of the  $\Sigma\Delta M$ . The same unit controlled the

(c)

Fig. 13. Clock-phase generators: (a) master clock; (b) chopper clock; (c) clock-phase scheme.

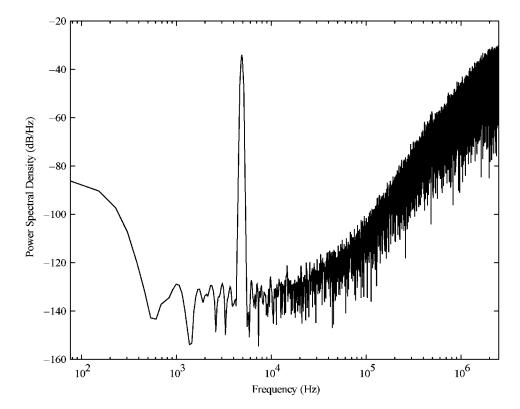

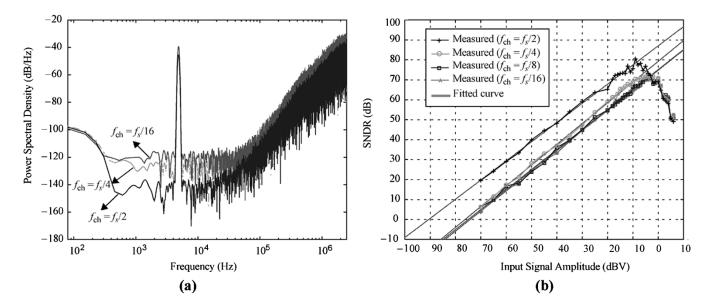

supply and reference voltages. After the acquisition, which is automatically performed by controlling the test set-up through proprietary C routines, data were transferred to a workstation to perform the digital post-processing using MATLAB. The digital filtering was performed with a *Sinc* filter, implemented by software. Fig. 16 shows a measured 65 536-point Kaiser-windowed FFT of the modulator output, clocked at 5 MHz and considering a -7-dBV, 5-kHz input sinewave, a modulator gain of  $\xi = 1$ , and a chopper frequency equal to  $f_{\rm ch} = f_s/2$ . The effect of varying the chopper frequency is illustrated in Fig. 17(a), which shows several output spectra corresponding

Fig. 14. (a) Complete layout of the modulator. (b) Microphotograph of the main parts of the chip.

Fig. 15. (a) Bonding diagram of the  $\Sigma \Delta M$  chip and (b) PCB.

to  $f_{\rm ch} = f_s/16, f_s/4, f_s/2$ . Note that the lower  $f_{\rm ch}$ , the more flicker noise appears in the baseband, thus degrading the modulator performance. This is better illustrated in Fig. 17(b), where the signal-to-(noise + distortion) ratio (SNDR) versus the input signal amplitude is represented for  $\xi = 1$  and different cases of  $f_{\rm ch}$ . It can be noted that the best performance is achieved for  $f_{\rm ch} = f_s/2$ . For that reason, all measurements are henceforth given for this value of  $f_{\rm ch}$ .

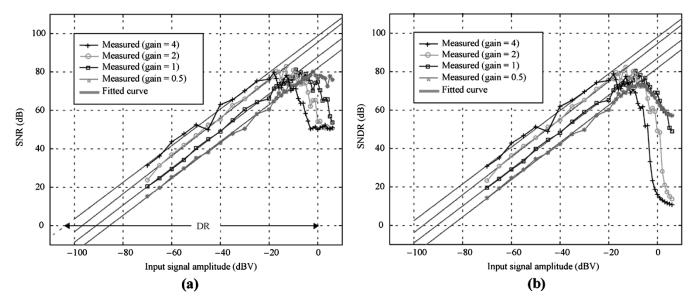

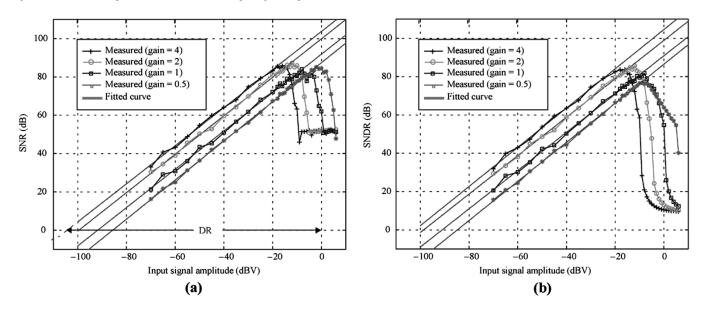

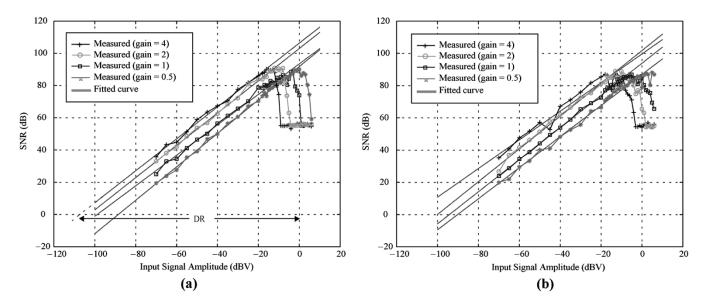

Fig. 18 shows several in-band (20-kHz) output spectra corresponding to the four different cases of the modulator gain ( $\xi = 0.5, 1, 2, 4$ ) when a -20 dBV at 5 kHz input signal is applied. The measured in-band spectra are in good agreement with those obtained by behavioral simulation (see Fig. 7). Indeed, the measured in-band noise power is about -96 dB for each case of the modulator gain, corresponding to 16.2 bits with respect to the full-scale reference voltage. This resolution can be notably improved by the effect of the modulator gain. This is illustrated in Fig. 19 where the measured SNR and SNDR are represented against the input amplitude. The input-referred DR is approximately 104 dBV, i.e., 110 dB below the full-scale reference voltage ( $V_{\rm ref} = 2$  V).

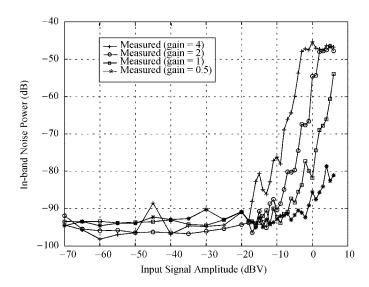

Note from Fig. 19 that in most cases of the modulator gain, the SNR/SNDR-peak is reached at approximately -10-dBFS signal amplitudes. Indeed, the in-band error power increases at those amplitudes as illustrated in Fig. 20. Behavioral simulations reveal that this nonlinear phenomenon is due to an incorrect oper-

Fig. 16. Measured modulator output spectrum for a -7 dBV at 5-kHz input signal,  $\xi = 1$  and  $f_{ch} = f_s/2$ .

Fig. 17. Effect of chopper frequency on measured results: (a) Output spectra and (b) SNDR versus input signal amplitude for different cases of the chopper frequency  $(f_{ch})$ .

ation of the chopper circuitry, which seems to be caused by the dielectric relaxation of the MIM capacitors in the first integrator [27]. This effect, often not properly characterized in most technology processes, may lead to an underestimation of the in-band noise power during the design phase, especially in high-resolution ADCs. Nevertheless, when the reference voltage is reduced from 2 V (nominal) to 1 V, the SNR peak improves in approximately 5 dB for all cases of the modulator gain, as illustrated in Fig. 21.

The noise-shaping is slightly degraded near the edge of the signal bandwidth, as illustrated in Figs. 16 and 18. Therefore, the performance near FS might be improved if a smaller signal bandwidth is taken. This is shown in Fig. 22 by plotting the SNR versus the input signal amplitude for different cases of the modulator gain and the reference voltage. Note that, in addition to the obvious resolution improvement due to doubling the oversampling ratio, the modulator behavior near FS is better than in Fig. 19.

Fig. 18. Measured modulator in-band (20-kHz) spectra corresponding to the different gain cases.

Fig. 19. (a) SNR and (b) SNDR as a function of the input amplitude for the different cases of modulator gain.

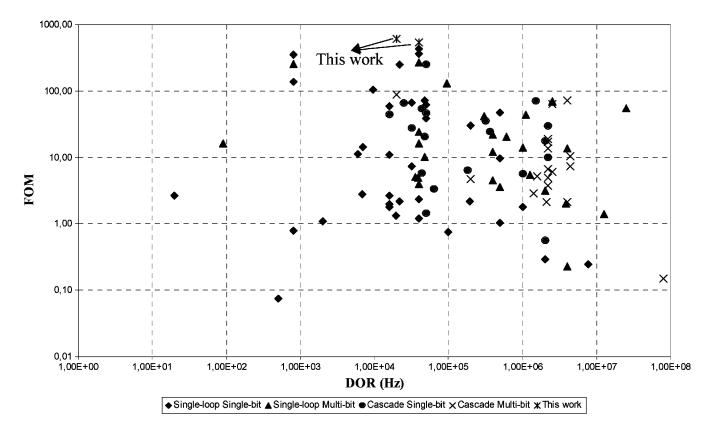

Table VIII summarizes the measured modulator performance by displaying its most significant figures. As a matter of conclusion, these features are compared in Fig. 23 with current state-of-the-art  $\Sigma\Delta$ Ms by using the following figure of merit (FOM) [10]:

$$FOM = 2 \cdot 10^5 \cdot k \cdot T \cdot \frac{3 \cdot 2^{2 \cdot \text{DRFS(bit)}} \cdot \text{DOR(Hz)}}{\text{Power(W)}} \quad (6)$$

to quantify the quality of  $\Sigma\Delta Ms$ , where  $DOR = 2 \cdot B_w$  stands for the digital output rate. Note from (6) that the better the  $\Sigma\Delta M$ , the larger the value of FOM. Table IX<sup>6</sup> compares the performance of those  $\Sigma\Delta Ms$  in Fig. 23 that achieve FOM > 200. Note that, thanks to the combined use of modulator-gain programmability and high resolution,<sup>7</sup> the circuit in this paper achieves the largest FOM reported to date.

$^{6}$ All  $\Sigma \Delta Ms$  in Table IX use switched-capacitor techniques and achieve medium-high resolution within signal bandwidths below 25 kHz. Recently, continuous-time techniques are demonstrating to be very promising to achieve those resolutions in the MHz bandwidth [31].

<sup>7</sup>It is important to note that the dynamic range of the  $\Sigma \Delta M$  in this paper is enhanced by the action of the modulator gain programmability. This is one of the key features of the proposed modulator and it is very important for sensor applications in which there is a changing signal range. Note that if the unity-gain case is considered, the FOM decreases, being 25.4 for 20 kHz.

Fig. 20. In-band noise power as a function of the input signal amplitude.

Fig. 21. (a) SNR and (b) SNDR as a function of the input amplitude for  $V_{\rm ref}$  = 1 V.

Fig. 22. SNR versus input amplitude for 10-kHz bandwidth: (a)  $V_{ref} = 1$  V; (b)  $V_{ref} = 2$  V.

Fig. 23. Comparison with state-of-the-art  $\Sigma \Delta Ms$ .

|                          | $V_{ref}(\mathbf{V})$  | $B_{w}$ (kHz) | ۳C  | SNR/SNDR-peak <sup>a</sup> (dB) | DR (dBV)/ DRFS (dB) |

|--------------------------|------------------------|---------------|-----|---------------------------------|---------------------|

|                          |                        | 20            | 0.5 | 80.2/73.5                       | 85.1/91.6           |

|                          |                        |               | 1   | 81.3/80.4                       | 91.1/97.1           |

|                          |                        |               | 2   | 82.9/82.5                       | 96.9/102.9          |

|                          | 2                      |               | 4   | 78.8/70.8                       | 104.1/ <b>110.1</b> |

|                          |                        | 10            | 0.5 | 88.0                            | 90.3/96.3           |

|                          |                        |               | 1   | 86.8                            | 94.3/100.3          |

|                          |                        |               | 2   | 89.0                            | 100.1/106.1         |

| Resolution/<br>Bandwidth |                        |               | 4   | 87.3                            | 107.8/113.8         |

| Danuwidun                | 1                      | 20            | 0.5 | 85.2/76.8                       | 85.7                |

|                          |                        |               | 1   | 84.0/81.8                       | 91.9                |

|                          |                        |               | 2   | 87.3/85.7                       | 100.1               |

|                          |                        |               | 4   | 85.8/83.7                       | 104.1               |

|                          |                        | 10            | 0.5 | 88.5                            | 90.1                |

|                          |                        |               | 1   | 88.8                            | 100.0               |

|                          |                        |               | 2   | 90.7                            | 103.0               |

|                          |                        |               | 4   | 90.1                            | 108.0               |

| Technology               | 0.35µm 1P-5M CMOS      |               |     |                                 |                     |

| Architecture             | Cascade 2-1 single-bit |               |     |                                 |                     |

| Sampling Frequency       | 5.12MHz                |               |     |                                 |                     |

| Active Area              | 5.7mm <sup>2</sup>     |               |     |                                 |                     |

| Supply Voltage           | 3.3V                   |               |     |                                 |                     |

| Power Consumption        | 14.7mW                 |               |     |                                 |                     |

TABLE VIII SUMMARY OF MEASURED PERFORMANCE

a. In the case of  $B_w = 10$  kHz, measurements are given for a input signal frequency of 5-kHz and hence, only SNR is computed.

| Author, year      | DRFS (bits) | DOR (kS/s) | Power Consumption (mW) | FOM   |

|-------------------|-------------|------------|------------------------|-------|

| Rabii, 1997 [10]  | 16.1        | 50         | 2.5                    | 246.3 |

| Snoeij, 2001 [28] | 16.7        | 22         | 2.5                    | 248.9 |

| Nys, 1997 [29]    | 19.0        | 0.8        | 2.18                   | 252.4 |

| Yang, 2003 [11]   | 18.7        | 40         | 68                     | 266.3 |

| Kerth, 1994 [30]  | 21.0        | 0.8        | 25                     | 351.3 |

| Yao, 2004 [12]    | 14.4        | 40         | 0.13                   | 358.9 |

| Coban, 1999 [13]  | 16.0        | 40         | 1                      | 428.8 |

| This work         | 18.1        | 40         | 14.7                   | 536.1 |

|                   | 18.7        | 20         | 14.7                   | 615.9 |

TABLE IX Performance Comparison ( $\Sigma \Delta Ms$  With FOM > 200)

#### VI. CONCLUSION

A 0.35- $\mu$ m CMOS programmable-gain cascade 2-1  $\Sigma \Delta M$ to be included in an automotive sensor interface has been described. The main design considerations have been discussed and applied to select the most appropriate modulator architecture in terms of resolution, speed, and power consumption. The design of the prototype is based on a top-down CAD methodology that combines simulation and statistical optimization at different levels of the modulator hierarchy. Experimental results show that the dynamic range can be highly enhanced by the action of gain programmability. This combined effect places the presented chip at the cutting edge of state-of- the-art  $\Sigma \Delta Ms$ for similar applications, achieving the largest figure of merit reported up to now.

#### ACKNOWLEDGMENT

The authors would like to thank E. Laes, L. Vandervoorde, and R. Vanhooren of AMI Semiconductors for their constructive comments on the 0.35- $\mu$ m technology process.

#### REFERENCES

- [1] W. J. Fleming, "Overview of automotive sensors," *IEEE Sensors J.*, pp. 296–308, Dec. 2001.

- [2] D. S. Eddy and D. R. Sparks, "Application of MEMS technology in automotive sensors and actuators," *Proc. IEEE*, pp. 1747–1755, Aug. 1998.

- [3] J. E. Johnston, "A 24-bit delta-sigma ADC with an ultra-low noise chopper-stabilized programmable gain instrumentation amplifier," in *Proc. Conf. Advances A/D and D/A Conversion Techniques and Their Applications*, 1999, pp. 27–28.

- [4] P. Malcovati and F. Maloberti, "An integrated microsystem for 3-D magnetic field measurements," *IEEE Trans. Instrum. Meas.*, vol. 49, no. 2, pp. 341–345, Apr. 2000.

- [5] C. B. Wang, "A 20-bit 25-kHz delta-sigma A/D converter utilizing a frequency-shaped chopper stabilization scheme," *IEEE J. Solid-State Circuits*, vol. 36, no. 3, pp. 566–569, Mar. 2001.

- [6] S. R. Norsworthy, R. Schreier, and G. Temes, *Delta-Sigma Data Converters—Theory, Design and Simulation*. New York: IEEE Press, 1997.

- [7] F. Medeiro, B. Pérez-Verdú, and A. Rodríguez-Vázquez, *Top-Down Design of High-Performance Sigma-Delta Modulators*. Norwood, MA: Kluwer, 1999.

- [8] K. A. A. Makinwa and J. H. Huijsing, "A smart CMOS wind sensor," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, 2002, pp. 432–479.

- [9] H. Kulah, N. Yazdi, and K. Najafi, "A CMOS switched-capacitor interface circuit for an integrated accelerometer," *Proc. IEEE Midwest Symp. Circuits and Systems*, pp. 244–247, Aug. 2002.

- [10] S. Rabii and B. A. Wooley, "A 1.8-V digital-audio sigma-delta modulator in 0.8-μm CMOS," *IEEE J. Solid-State Circuits*, vol. 32, no. 6, pp. 783–796, Jun. 1997.

- [11] Y. Yang, A. Chokhawala, M. Alexander, J. Melanon, and D. Hester, "A 114-dB 68-mW chopper-stabilized stereo multibit audio ADC in 5.62 mm<sup>2</sup>," *IEEE J. Solid-State Circuits*, vol. 38, no. 12, pp. 2061–2068, Dec. 2003.

- [12] L. Yao, M. S. J. Steyaert, and W. Sansen, "A 1-V 140-µW 88-dB audio sigma-delta modulator in 90-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 39, no. 11, pp. 1809–1818, Nov. 2004.

- [13] A. L. Coban and P. E. Allen, "A 1.5 V 1.0 mW audio delta sigma modulator with 98 dB dynamic range," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, 1999, pp. 50–51.

- [14] F. Medeiro, R. del Río, J. M. de la Rosa, B. Pérez-Verdú, and A. Rodríguez-Vázquez, "High-Order Cascade Multi-Bit ΣΔ Modulators," in *CMOS Telecom Data Converters*, A. Rodríguez-Vázquez, F. Medeiro, and E. Janssens, Eds. Boston, MA: Kluwer Academic, 2003, ch. 9.

- [15] I. Fujimori, L. Longo, A. Hairapetian, K. Seiyama, S. Kosic, J. Cao, and S. L. Chan, "A 90-dB SNR 2.5-MHz output-rate ADC using cascaded multibit delta-sigma modulation at 8 × oversampling ratio," *IEEE J. Solid-State Circuits*, vol. 35, no. 12, pp. 1820–1828, Dec. 2000.

- [16] R. del Río, J. M. de la Rosa, B. Pérez-Verdú, M. Delgado-Restituto, R. Domínguez-Castro, F. Medeiro, and A. Rodríguez-Vázquez, "Highly linear 2.5-V CMOS ΣΔ modulator for ADSL+," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 51, no. 1, pp. 47–62, Jan. 2004.

- [17] A. M. Marques, V. Peluso, M. S. J. Steyaert, and W. Sansen, "A 15-b resolution 2-MHz nyquist rate ΔΣ ADC in a 1-μm CMOS technology," *IEEE J. Solid-State Circuits*, vol. 33, no. 7, pp. 1065–1075, Jul. 1998.

- [18] G. Yin, "High-performance analog-to-digital converters using cascaded  $\Sigma\Delta$  modulators," Ph.D. dissertation, Katholieke Universiteit Leuven, Belgium, 1994.

- [19] F. V. Fernández, R. del Río, R. Castro-López, O. Guerra, F. Medeiro, and B. Pérez-Verdú, "Design Methodologies for Sigma-Delta Converters," in *CMOS Telecom Data Converters*, A. Rodríguez-Vázquez, F. Medeiro, and E. Janssens, Eds. Boston, MA: Kluwer Academic, 2003, ch. 15.

- [20] B. Razavi, Design of Analog CMOS Integrated Circuits. New York: McGraw-Hill, 2000.

- [21] C. C. Enz and G. C. Temes, "Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization," *Proc. IEEE*, vol. 84, no. 11, pp. 1584–1614, Nov. 1996.

- [22] F. Medeiro, B. Pérez-Verdú, A. Rodríguez-Vázquez, and J. L. Huertas, "A vertically integrated tool for automated design of ΣΔ modulators," *IEEE J. Solid-State Circuits*, vol. 30, no. 7, pp. 762–772, Jul. 1995.

- [23] G. M. Yin, F. Op't Eynde, and W. Sansen, "A high-speed CMOS comparator with 8-b resolution," *IEEE J. Solid-State Circuits*, vol. 27, no. 2, pp. 208–211, Feb. 1992.

- [24] W. Yu, S. Sen, and B. H. Leung, "Distortion analysis of MOS track-and-hold sampling mixers using time-varying volterra series," *IEEE Trans. Circuits Syst. II*, vol. 46, no. 2, pp. 101–113, Feb. 1999.

[25] J.-T. Wu and K.-L. Chang, "MOS charge pumps for low-voltage oper-

- [25] J.-T. Wu and K.-L. Chang, "MOS charge pumps for low-voltage operation," *IEEE J. Solid-State Circuits*, vol. 33, no. 4, pp. 592–597, Apr. 1998.

- [26] K. Lee and R. G. Meyer, "Low distortion switched-capacitor filter design techniques," *IEEE J. Solid-State Circuits*, vol. SC-20, no. 12, pp. 1103–1113, Dec. 1985.

- [27] J. W. Fattaruso, M. De Wit, G. Warwar, K. S. Tan, and R. K. Hester, "The effect of dielectric relaxation on charge-redistribution A/D converters," *IEEE J. Solid-State Circuits*, vol. 25, no. 12, pp. 1550–1561, Dec. 1990.

- [28] M. F. Snoeij, O. Bajdechi, and J. H. Huijsing, "A fourth-order switched-capacitor sigma-delta A/D converter using a high-ripple chebyshev loop filter," in *Proc. IEEE Int. Symp. Circuits and Systems*, 2001, pp. 615–618.

- [29] O. Nys and R. K. Henderson, "A 19-bit low-power multibit sigma-delta ADC based on data weighted averaging," *IEEE J. Solid-State Circuits*, vol. 32, no. 7, pp. 933–942, Jul. 1997.

- [30] D. A. Kerth, D. B. Kasha, T. G. Mellissinos, D. S. Piasecki, and E. J. Swanson, "A 120-dB linear switched-capacitor delta-sigma modulator," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, 1994, pp. 196–197.

- [31] S. Yan and E. Sánchez-Sincenio, "A continuous-time ∑∆ modulator with 88-dB dynamic range and 1.1-MHz signal bandwidth," *IEEE J. Solid-State Circuits*, vol. 39, no. 1, pp. 75–86, Jan. 2004.

José M. de la Rosa (S'96–M'01) received the Licenciado en Física Electrónica (Electronics Physics) degree in 1993 and the Doctor en Ciencias Físicas (Ph.D.) degree in 2000 from the University of Seville, Spain.

Since 1994, he has been with the Institute of Microelectronics of Seville (IMSE-CNM, CSIC) of the Spanish Microelectronics Center. He is also with the Department of Electronics and Electromagnetism, School of Engineering, University of Seville, where he is an Associate Professor. His main research

interests are in the field of mixed-signal integrated circuits, especially pipeline and sigma-delta analog-to-digital converters, including analysis, behavioral modeling and design automation of such circuits. He has participated in several National and European R&D projects and has co-authored more than 80 international scientific publications, including journal and conference papers, book chapters and the book *Systematic Design of CMOS Switched-Current Bandpass Sigma-Delta Modulators for Digital Communication Chips* (Springer, 2002).

**Sara Escalera** received the B.S. degree in electronic physics and the M.S. degree in microelectronics from the University of Sevilla, Spain, in 2001 and 2004, respectively. She is currently working toward her Ph.D. degree at the Instituto de Microelectrónica de Sevilla (IMSE-CNM) in the field of sigma-delta analog-to-digital converters testing.

Her main areas of interest are test and design of mixed-signal circuits, especially of high-accuracy SC sigma-delta converters.

**Fernando Medeiro** (M'99) was born in Higuera de Vargas, Badajoz, Spain. He received the Licenciado en Física Electrónica degree in 1990 and the Doctor en Física (Ph.D.) degree with honors in 1997, both from the University of Seville, Spain, in 1990 and 1997, respectively.

Since 1991, he has been working at the Microelectronics Institute of Seville (IMSE, C.S.I.C.). He is also with the Department of Electronics and Electromagnetism at the Escuela Superior de Ingenieros of the University of Seville, where he is an Associate

Professor. His research interest are in the field of sigma-delta converters, including modeling, behavioral simulation and design automation. In this topic, he has participated as a Lecturer in several international courses and has co-authored the book *Top-Down Design of High-Performance Sigma-Delta Modulators* (Springer, 1998).

**Oscar Guerra** received the physics degree in electronics and the Ph.D. degree in the field of analog design automation, from the University of Seville, Spain, in 1995 and 2002, respectively.

Since 1997, he has been with the Instituto Nacional de Microelectrónica, Centro Nacional de Microelectrónica (IMSE-CNM), and since 2000, he has also been an Assistant Professor at the University of Seville. His research interests are in the fields of modeling techniques for analog integrated circuit design, with special enphasis on symbolic analysis techniques and design and design-for-testability of

high-resolution sigma-delta converters. His work has been developed in the context of eight research projects, ranging from the developement of CAD tools to analog circuit design and built-in self-test techniques. He has been an author or co-author of more than 40 papers in international journals and international proceedings, as well as one chapter in the book *CMOS Telecom Data Converters* (Kluwer, 2003).

**Rocío del Río** (M'04) received the Licenciado en Fisíca Electrónica and the Ph.D. degree from the University of Seville, Spain, in 1996 and 2004, respectively.

She joined the Department of Electronics and Electromagnetism at the University of Seville in 1995, where she is currently an Assistant Professor. Since 1995, she has also been with the Institute of Microelectronics of Seville (IMSE-CNM, CSIC). Her main research interests are in ADCs, especially sigma-delta converters, including modeling, behav-

ioral simulation, and design automation.

Angel Rodríguez-Vázquez (M'80–F'96) was born in Seville, Spain. He is a Professor of Electronics at the Department of Electronics and Electromagnetism, University of Seville. He is also a member of the research staff of the Institute of Microelectronics of Seville-Centro Nacional de Microelectrónica (IMSE-CNM), where he is heading a research group on Analog and Mixed-Signal VLSI. His research interests are in the design of analog interfaces for mixed-signal VLSI circuits, CMOS imagers and vision chips, neuro-fuzzy controllers, symbolic

analysis of analog integrated circuits and optimization of analog integrated circuits.

Dr. Rodríguez-Vázquez served as an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I, FUNDAMENTAL THEORY AND APPLICATIONS (TCAS-I) from 1993 to 1995, as Guest Editor of the IEEE TCAS-I special issue on Low-Voltage and Low-Power Analog and Mixed-Signal Circuits and Systems (1995), as Guest Editor of the IEEE TCAS-II special issue on "Advances in Nonlinear Electronic Circuits" (1999), and as chair of the IEEE CAS Analog Signal Processing Committee (1996). He was co-recipient of the 1995 Guillemin–Cauer award of the IEEE Circuits and Systems Society, and the best paper award of the 1995 European Conference on Circuit Theory and Design. In 1992, he received the Young Scientist Award of the Seville Academy of Science. In 1996, he was elected to the degree of Fellow of the IEEE for "contributions to the design and applications of analog/digital nonlinear ICs".

Belén Pérez-Verdú has been an Associate Professor at the University of Seville, Spain, since 1987. She is also with the Institute de Microelectronics of Seville (IMSE-CNM). Her research activities are in the field of mixed-signal integrated circuit design, in particular, sigma-delta modulators, computer-aided design and modeling of analog integrated circuits. She has published two books and more than 70 papers including journal and conference papers. She has participated in several European ESPRIT projects and Spanish CICYT projects.