Open access • Journal Article • DOI:10.1109/TCSII.2010.2092823

# A CMOS 8-Bit 1.6-GS/s DAC With Digital Random Return-to-Zero — Source link 🗹

Wei-Hsin Tseng, Jieh-Tsorng Wu, Yung-Cheng Chu

Institutions: National Chiao Tung University

Published on: 01 Jan 2011 - IEEE Transactions on Circuits and Systems li-express Briefs (Institute of Electrical and Electronics Engineers Inc.)

Topics: CMOS and Dynamic range

Related papers:

- A 10-bit 1-GSample/s Nyquist current-steering CMOS D/A converter

- The Analysis and Improvement of a Current-Steering DAC's Dynamic SFDR—II: The Output-Dependent Delay Differences

- A 130 nm CMOS 6-bit Full Nyquist 3 GS/s DAC

- A 12 bit 2.9 GS/s DAC With IM3 \$  $\leq$  -\$ 60 dBc Beyond 1 GHz in 65 nm CMOS

- A Compact Dynamic-Performance-Improved Current-Steering DAC With Random Rotation-Based Binary-Weighted Selection

# A CMOS 8-Bit 1.6-GS/s DAC With Digital Random Return-to-Zero

Wei-Hsin Tseng, Jieh-Tsorng Wu, Senior Member, IEEE, and Yung-Cheng Chu

*Abstract*—A digital random return-to-zero technique is presented to improve the dynamic performance of current-steering digital-to-analog converters (DACs). To demonstrate the proposed technique, a CMOS 8-bit 1.6-GS/s DAC was fabricated in a 90-nm CMOS technology. The DAC achieves a spurious-free dynamic range better than 60 dB for a sine-wave input up to 460 MHz and better than 55 dB up to 800 MHz. The DAC consumes 90 mW of power.

*Index Terms*—Current steering, digital-to-analog converter (DAC), digital random return-to-zero (DRRZ), return-to-zero (RZ).

#### I. INTRODUCTION

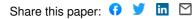

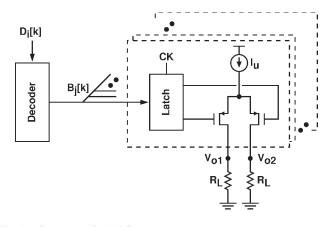

THE current-steering digital-to-analog converters (DACs) can achieve a high sampling rate and, thus, are commonly used in generating high-frequency signals [1]-[5]. Fig. 1 shows a generic current-steering DAC. It consists of M equally weighted current cells. Each current cell contains a current source of  $I_u$  output current, a p-channel MOSFET pair functioning as a current switch, and a digital latch controlled by the clock CK. The complementary outputs of the latch control the current switch, directing the  $I_u$  current to either the  $R_L$ load at  $V_{o1}$  or the one at  $V_{o2}$ . A decoder converts the DAC digital input  $D_i[k]$  into M thermometer-code signals  $B_j[k]$ , where  $1 \le j \le M$ , such that  $D_i[k] = \sum_{j=1}^M B_j[k]$ . The  $B_j[k]$ signal has a binary value of either +1 or -1. Fig. 2 illustrates the DAC differential nonreturn-to-zero (NRZ) output waveform  $V_o = V_{o1} - V_{o2}$ .  $V_o$  has a voltage range between  $+MI_uR_L$  and  $-MI_uR_L$  and a step size of  $2I_uR_L$ .

DAC static linearity, which is specified as differential nonlinearity (DNL) and integral nonlinearity (INL), is mainly determined by the matching of  $I_u$  among different current cells and the output resistances of the  $I_u$  current sources. There are techniques to improve static linearity, which will not be covered in this brief. However, even with ideal  $I_u$  current sources, dynamic nonlinearity still occurs. It is manifested as spuriousfree dynamic range (SFDR) degradation shown in the  $V_o$  output

Manuscript received June 28, 2010; revised September 1, 2010; accepted October 22, 2010. Date of publication December 20, 2010; date of current version January 19, 2011. This work was supported by the National Science Council of Taiwan under Grant NSC-98-2221-E-009-131-MY2. This paper was recommended by Associate Editor N. Neihart.

W.-H. Tseng and J.-T. Wu are with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: jtwu@mail.nctu.edu.tw).

Y.-C. Chu is with Faraday Technology Corporation, Hsinchu 300, Taiwan. Color versions of one or more of the figures in this paper are available online

at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSII.2010.2092823

Fig. 1. Current-steering DAC.

Fig. 2. NRZ output waveform of a current-steering DAC.

spectrum when the  $D_i[k]$  input is a single-tone sine wave. The SFDR decreases rapidly with increasing input frequency. The sources of dynamic nonlinearity are numerous and complex, including code-dependent switching transients [6], [7] and the capacitive output impedance of the current cells [5], [12], [13].

The return-to-zero (RZ) technique has been proposed to improve the DAC dynamic performance [6], [8], [9]. The technique adds an output buffer to isolate the output loads from the current switches and executes current-switching operation during the zero phase. The DAC dynamic performance can also be improved by modifying the current-switching operation to make the switching transients uncorrelated with the input sequence [2], [10], [11].

In this brief, we propose a digital random RZ (DRRZ) technique to mitigate the effect of switching transients on the DAC dynamic performance. An 8-bit 1.6-GS/s current-steering DAC chip was designed to demonstrate the proposed technique. The rest of this brief is organized as follows. Section II introduces the DRRZ technique. Section III describes the circuit implementation of the DAC chip. Section IV shows the experimental results. Section V draws conclusions.

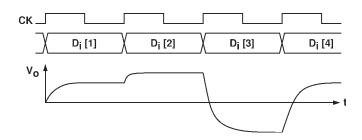

Fig. 3. Waveforms of an RZ DAC.

# II. DRRZ

Consider the *j*th current cell of the DAC shown in Fig. 1. Its current switch is driven by  $B_j[k] \in \{-1, +1\}$ . When CK changes from low to high, the current switch may remain unchanged or undergo a (-1)-to-(+1) or a (+1)-to-(-1) switching. When the current switch makes a switching, the DAC output  $V_o$  experiences a transient disturbance called switching transient. The (-1)-to-(+1) and (+1)-to-(-1) switching transients have opposite polarities. For the NRZ DAC, the switching of the current cells is determined by the input  $D_i[k]$ . Thus, the switching transients are input dependent and will result in DAC dynamic distortion.

Analog RZ (ARZ) has been used to hide the switching transients from the output [6], [8], [9]. The CK and  $V_o$  waveforms of Fig. 3 show the ARZ operation. When CK is high, the DAC is in the data phase. It decodes the digital input  $D_i[k]$ , sets up its internal current switches, and generates the analog output  $V_o$ corresponding to  $D_i[k]$ . When CK is low, the DAC is in the zero phase. The DAC output  $V_o$  is forced to zero by analog switches added at output nodes  $V_{o1}$  and  $V_{o2}$ . The current switches in the DAC are switched to reflect the next input  $D_i[k+1]$  during the zero phase. Thus, the switching transients do not appear in  $V_o$  to contribute dynamic distortion. The analog switches at the output nodes must be large enough to eliminate switching transients.

We can generate the RZ  $V_o$  waveform without using the analog switches at the output nodes. As shown in Fig. 3, when CK is low, the DAC is in the zero phase Z[k], in which the DAC arranges its internal current switches in such a way that the output  $V_o = 0$ . In the Z[k] state, the switch controls  $B_i[k]$  are reset to predefined values such that  $\sum_{j=1}^{M} B_j[k] = 0$ , assuming that M is an even number. However, in this digital RZ (DRZ) setup, switching transients appear in  $V_o$ . Consider the *j*th current cell. The sequence of its switching control  $B_i$  is shown in Fig. 4. When CK is high,  $B_j = B_j[k]$  is determined by the input  $D_i[k]$ . When CK is low,  $B_j = R_j[k]$  is a fixed value of either +1 or -1. In Fig. 4,  $B_j[1] = +1$  and  $B_j[2] = +1$ have the same value. If  $R_j[1] = +1$ , there will be no switching during the Z[1] period. If  $R_i[1] = -1$ , there will be (+1)-to-(-1) and (-1)-to-(+1) transients on both edges of the Z[1]period. Fig. 4 also shows that  $B_i[2] = +1$  and  $B_i[2] = -1$ have different values. If  $R_i[2] = +1$ , a (+1)-to-(-1) transient occurs at the right edge of the Z[2] period. If  $R_j[2] = -1$ , a (+1)-to-(-1) transient occurs at the left edge of the Z[2]period. In summary, DRZ assigns a constant to  $R_j[k]$ , i.e.,  $R_j[k] = +1$  for all k or  $R_j[k] = -1$  for all k. The current switch transitions are determined by the  $B_i[k]$  sequence alone.

| ск                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \[ D_i [1] \]         Z[1] \]         D_i [2] \]         Z[2] \]         D_i [3] \]         Z[3] \]         D_i [4] \]         Z[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bj[1] Rj[1] Bj[2] Rj[2] Bj[3] Rj[3] Bj[4] Rj[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $B_{j} \underbrace{\chi +1}_{+1/-1} \underbrace{+1/-1}_{+1} \underbrace{+1/-1}_{+1/-1} \underbrace{\chi -1}_{+1/-1} \underbrace{\chi +1/-1}_{+1/-1} \underbrace{\chi -1}_{+1/-1} \underbrace{\chi +1/-1}_{+1/-1} $ |

Fig. 4. Switching behavior of a current cell in a DRZ DAC or a DRRZ DAC.

Their strong correlation with the input  $D_i[k]$  yields distortion in  $V_o$ . DRZ, in fact, introduces more input-dependent switching transients than NRZ.

We propose the DRRZ technique to randomize the switching transients appearing in DRZ. In this scheme, the switch controls  $B_i[k]$  in the Z[k] phase are dictated by a pseudorandom number generator (PRNG), such that  $\sum_{j=1}^{M} B_j[k] = 0$ . Consider the *j*th current cell and the operation sequence shown in Fig. 4. When CK is high,  $B_i = B_i[k]$  is determined by the input  $D_i[k]$ . When CK is low,  $B_j = R_j[k]$  becomes a binary random variable, which has a value of either +1 or -1. In Fig. 4,  $B_j[1] = +1$ and  $B_i[2] = +1$  have the same value. Switch transitions occur only if  $R_i[1] = -1$ . Fig. 4 also shows that  $B_i[2] = +1$  and  $B_j[2] = -1$  have different values. A switch transition occurs at the right edge of the Z[2] period if  $R_i[2] = +1$ . On the other hand, a switch transition occurs at the left edge of the Z[2]period if  $R_i[2] = -1$ . In summary, DRRZ makes  $R_i[k]$  a random sequence, which randomizes the current switch transitions. When the switching transients are not correlated with the input  $D_i[k]$ , they appear as noises in  $V_o$  and will not cause distortion.

#### **III. CIRCUIT DESCRIPTIONS**

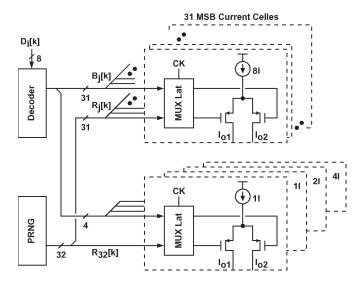

Fig. 5 shows the block diagram of the 8-bit DAC. It is segmented into a 5-bit equally weighted most significant bit (MSB) DAC (M-DAC) and a 3-bit binary-weighted least significant bit (LSB) DAC (L-DAC). The M-DAC comprises 31 identical current cells. Each current cell can output a current of 8I, where I is the DAC unit current. The L-DAC comprises four current cells, which output currents of 11, 11, 21, and 41, respectively. There are two 1I current cells in the L-DAC so that a differential output of zero can be realized. The nodes  $I_{o1}$  and  $I_{o2}$  of all current cells are tied together to form two differential DAC output terminals. The two output terminals are connected to two  $R_L$  resistors to generate the differential  $V_o$ , as illustrated in Fig. 1. When CK is high, the decoder controls both the M-DAC and the L-DAC. The current of the extra 1I current cell in the L-DAC is always directed to the  $I_{o1}$  node. The DAC output is expressed as  $V_o[k] = (D_i[k] - 127) \times 2IR_L$ , where  $D_i[k]$  is an integer from 0 to 255. In our design,  $I = 80 \ \mu A$  and  $R_L = 25 \ \Omega$  yield  $V_o$  with a differential signal range of 1  $V_{pp}$ .

As shown in Fig. 5, each current cell contains a multiplexing (MUX) latch. When CK is high, the latch selects the  $B_j[k]$  control from the  $D_i[k]$  decoder for a normal DAC output. When CK is low, the latch selects the  $R_j[k]$  control from a PRNG. The PRNG is a 16-bit linear feedback shift register. Its 16 outputs and their complements form the 32  $R_j[k]$  zero-phase controls. This arrangement ensures that  $\sum_{j=1}^{32} R_j[k] = 0$ . During the

Fig. 5. DAC block.

Fig. 7. Microphotograph of the DRRZ DAC.

Fig. 8. Measured DNL and INL.

Fig. 6. Current cell schematic.

zero phase, the entire L-DAC is treated as a single MSB current cell controlled by a single  $R_{32}[k]$  signal.

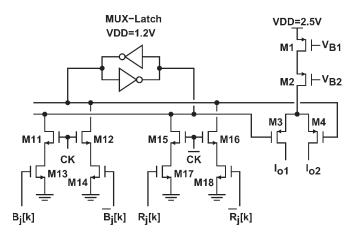

Fig. 6 shows the circuit schematic of a current cell. MOSFETs M1 and M2 form a cascode current source. M3 and M4 together function as a current switch. The current source is operated under a 2.5-V supply. M1–M4 are MOSFETs with thick gate oxide. MOSFETs M11–M18 and the two inverters form a level-sensitive MUX latch. When CK is high, the  $B_j[k]$ signal is loaded into the latch. When CK is low, the  $R_j[k]$  signal is loaded into the latch. The MUX latch is operated under a 1.2-V supply.

### **IV. EXPERIMENTAL RESULTS**

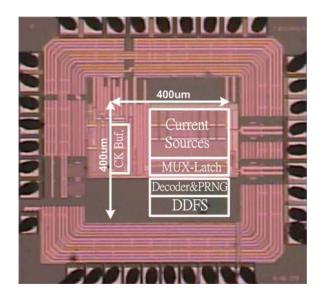

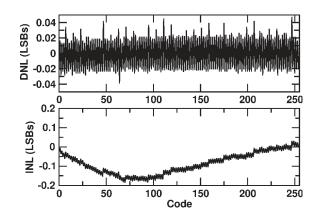

The DAC was fabricated in a standard 90-nm CMOS technology. Fig. 7 shows the chip photograph. The DAC core area is  $400 \times 400 \ \mu m^2$ . The chip also includes a direct digital frequency synthesizer (DDFS) to generate digital inputs for DAC testing. Fig. 8 shows the measured DNL and INL of the DAC. The DNL is +0.04/-0.03 LSB, and the INL is +0/-0.2 LSB.

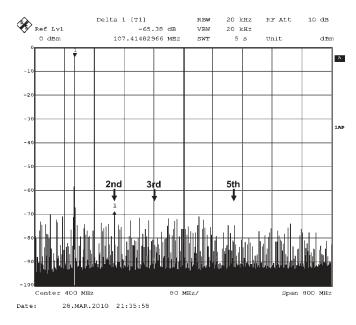

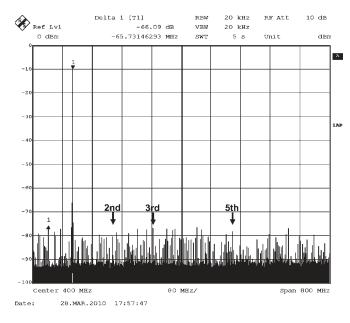

Figs. 9 and 10 show the output spectra of the DAC operating at a 1.6-GS/s sampling rate, and the input frequency is 107 MHz. In Fig. 9, the DRRZ function is turned off, and the DAC output waveform is similar to NRZ  $V_o$  waveform shown in Fig. 2. In Fig. 10, the DRRZ function is turned on, and the DAC output waveform is similar to the RZ  $V_o$  waveform shown in Fig. 3. There are no significant harmonic tones in both figures. The measured SFDR is 65.4 dB for the NRZ DAC and 66 dB for the DRRZ DAC. When the input frequency of the DAC is low, the total number of current switches forced to switch is low in each clock cycle. The overall switching transients have little effect on the harmonic distortion of the DAC. Thus, the DRRZ function shows little improvement in the SFDR.

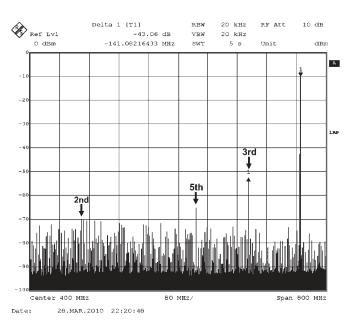

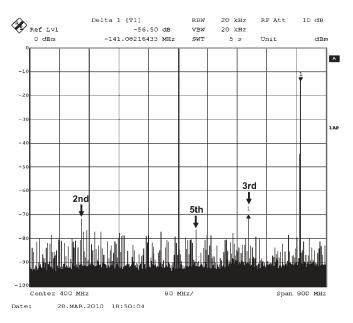

Figs. 11 and 12 are the DAC output spectra under similar conditions, except that the input frequency is raised to 731 MHz. When the input frequency of the DAC is high, the total number of current switches forced to switch is high in each clock cycle. The effect of switching transients becomes large and is revealed as the harmonic tones in Fig. 11. The SFDR is 43 dB and is dominated by the third harmonic. The harmonic tones are suppressed by the DRRZ operation, as illustrated in Fig. 12. The SFDR is improved to 56.5 dB.

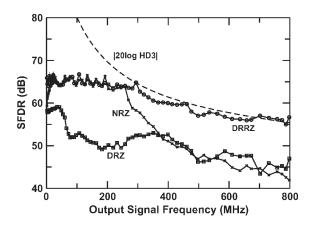

Fig. 13 shows the measured SFDR of the DAC operated at a 1.6-GS/s sampling rate and with different input frequencies. The DAC has three different configurations, which are NRZ, DRZ, and DRRZ. For the NRZ DAC, the measured SFDR is

Fig. 9. Output spectrum of the DAC with NRZ. Sampling rate is 1.6 GS/s, and input frequency is 107 MHz.

Fig. 10. Output spectrum of the DAC with DRRZ. The sampling rate is 1.6 GS/s, and the input frequency is 107 MHz.

degraded from 65 to 42 dB as the input frequency increases toward 800 MHz. Employing the DRRZ operation, the DAC can maintain an SFDR larger than 60 dB up to 460 MHz and an SFDR larger than 55 dB up to 800 MHz. Fig. 13 also shows the measured SFDR of the DRZ DAC. The DRZ setup cannot improve the SFDR at all. At low frequencies, the DRZ DAC exhibits an SFDR even worse than the NRZ DAC. This is because, at low frequencies, DRZ introduces more switching transients than NRZ.

Fig. 13 also shows a theoretical third-order harmonic distortion (HD3) calculation by considering only the output impedance of current cells [5], [12], [13]. It is expressed as

$$\text{HD3} = \left[\frac{M}{4} \cdot \frac{R_{L,d}}{|Z_o|}\right]^2 \tag{1}$$

Fig. 11. Output spectrum of the DAC with NRZ. The sampling rate is 1.6 GS/s, and the input frequency is 731 MHz.

Fig. 12. Output spectrum of the DAC with DRRZ. The sampling rate is 1.6 GS/s, and the input frequency is 731 MHz.

where  $R_{L,d} = 50 \ \Omega$  is the differential resistance of the DAC output loads, M = 32 is the total number of M-DAC current cells, and  $Z_o$  is the output impedance of an M-DAC current cell. The L-DAC is treated as a single M-DAC current cell. Referring to Fig. 6,  $Z_o$  is the output impedance looking into the  $I_{o1}$  terminal when M3 is turned on and M4 is off.  $Z_o$  in our design can be modeled as a resistor  $R_o = 1.9 \ M\Omega$  in parallel with a capacitor  $C_o = 10.8 \ \text{fF}$ . Fig. 13 indicates that the HD3 of (1) is the major distortion source for the DRRZ DAC with input frequencies higher than 300 MHz. This type of distortion cannot be removed by DRRZ.

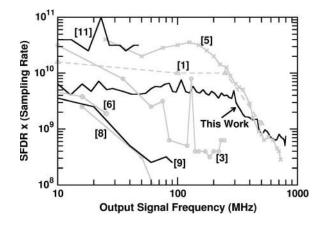

The DAC specifications are summarized in Table I. Fig. 14 compares the dynamic performance of this DAC against other published DAC works. In order to compare DACs of different

Fig. 13. Measured SFDR at different signal frequencies.

TABLE I DAC Performance Summary

| Technology                        | CMOS 90 nm           |

|-----------------------------------|----------------------|

| Resolution                        | 8 Bits               |

| Sampling Rate $f_s$               | 1.6 GS/s             |

| DNL                               | +0.04 / -0.03 LSB    |

| INL                               | +0.0 / -0.2 LSB      |

| SFDR @ $f_{in} = 100 \text{ MHz}$ | 64.5 dB              |

| SFDR @ $f_{in} = 700$ MHz         | 57.0 dB              |

| Load Current                      | 20 mA                |

| Output Swing                      | 1 V <sub>pp</sub>    |

| Supply Voltage (Analog/Digital)   | 2.5 V / 1.2 V        |

| Power Consumption                 | 90 mW                |

| Core Area                         | 0.16 mm <sup>2</sup> |

Fig. 14. Dynamic performance comparison of published DACs.

sampling rates, the dynamic performance is defined as SFDR  $\times f_s$ , where SFDR is expressed in power ratio, and  $f_s$  is the sampling rate (in hertz). Note that the reported DAC is only an 8-bit design, but its dynamic performance is competitive at high signal frequencies.

#### V. CONCLUSION

A CMOS 8-bit 1.6-GS/s current-steering DAC has been presented to demonstrate the proposed DRRZ technique. The technique requires only a small overhead in digital circuits. The improvement in the SFDR of the DAC is 14 dB when the input frequency is 800 MHz.

## ACKNOWLEDGMENT

The authors would like to thank H.-H. Chen, C.-W. Chang, C.-T. Wu, and K.-H. Wu of Faraday Technology Corporation for engineering support.

#### REFERENCES

- A. V. den Bosch, M. A. F. Borremans, M. S. J. Steyaert, and W. Sansen, "A 10-bit 1-GSample/s Nyquist current-steering CMOS D/A converter," *IEEE J. Solid-State Circuits*, vol. 36, no. 3, pp. 315–324, Mar. 2001.

- [2] B. Schafferer and R. Adams, "A 3 V CMOS 400 mW 14 b 1.4 GS/s DAC for multi-carrier applications," in *Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2004, pp. 360–532.

- [3] K. Doris, J. Briaire, D. Leenaerts, M. Vertregt, and A. van Roermund, "A 12 b 500 MS/s DAC with >70 dB SFDR up to 120 MHz in 0.18 mum CMOS," in Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, Feb. 2005, pp. 116–588.

- [4] X. Wu, P. Palmers, and M. S. J. Steyaert, "A 130 nm CMOS 6-bit full Nyquist 3 GS/s DAC," *IEEE J. Solid-State Circuits*, vol. 43, no. 11, pp. 2396–2403, Nov. 2008.

- [5] C.-H. Lin, F. M. L. van der Goes, J. R. Westra, J. Mulder, Y. Lin, E. Arslan, E. Ayranci, X. Liu, and K. Bult, "A 12 bit 2.9 GS/s DAC with IM3 < -60 dBc beyond 1 GHz in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 44, no. 12, pp. 3285–3293, Dec. 2009.

- [6] A. R. Bugeja, B.-S. Song, P. L. Rakers, and S. F. Gillig, "A 14-b, 100-MS/s CMOS DAC designed for spectral performance," *IEEE J. Solid-State Circuits*, vol. 34, no. 12, pp. 1719–1732, Dec. 1999.

- [7] T. Chen and G. G. E. Gielen, "The analysis and improvement of a currentsteering DACs dynamic SFDR–I: The cell-dependent delay differences," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 53, no. 1, pp. 3–15, Jan. 2006.

- [8] A. R. Bugeja and B.-S. Song, "A self-trimming 14-b 100-MS/s CMOS DAC," *IEEE J. Solid-State Circuits*, vol. 35, no. 12, pp. 1841–1852, Dec. 2000.

- [9] Q. Huang, P. A. Francese, C. Martelli, and J. Nielsen, "A 200 MS/s 14 b 97 mW DAC in 0.18 mum CMOS," in Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, Feb. 2004, pp. 364–532.

- [10] S. Park, G. Kim, S.-C. Park, and W. Kim, "A digital-to-analog converter based on differential-quad switching," *IEEE J. Solid-State Circuits*, vol. 37, no. 10, pp. 1335–1338, Oct. 2002.

- [11] K. L. Chan, J. Zhu, and I. Galton, "Dynamic element matching to prevent nonlinear distortion from pulse-shape mismatches in high-resolution DACs," *IEEE J. Solid-State Circuits*, vol. 43, no. 9, pp. 2607–2078, Sep. 2008.

- [12] A. V. den Bosch, M. Steyaert, and W. Sansen, "SFDR-bandwidth limitations for high-speed high-resolution current-steering CMOS D/A converters," in *Proc. IEEE ICECS*, Sep. 1999, pp. 1193–1196.

[13] S. Luschas and H.-S. Lee, "Output impedance requirements for

- [13] S. Luschas and H.-S. Lee, "Output impedance requirements for DACs," in *Proc. IEEE Int. Symp. Circuits Syst. Dig. Tech. Papers*, May 2003, pp. I-861–I-864.