# A CMOS Current-Mode Magnetic Hall Sensor With Integrated Front-End

Hadi Heidari, Student Member, IEEE, Edoardo Bonizzoni, Member, IEEE, Umberto Gatti, Member, IEEE, and Franco Maloberti, Fellow, IEEE

Abstract—A Hall magnetic sensor working in the current domain and its electronic interface are presented. The paper describes the physical sensor design and implementation in a standard CMOS technology, the transistor level design of its high sensitive front-end together with the sensor experimental characterization. The current-mode Hall sensor and the analog readout circuit have been fabricated using a 0.18- $\mu$ m CMOS technology. The sensor uses the current spinning technique to compensate for the offset and provides a differential current as an output signal. The measured sensor power consumption and residual offset are 120  $\mu$ W and 50  $\mu$ T, respectively.

Index Terms—CMOS Hall sensors, current spinning, magnetic sensor.

## I. INTRODUCTION

N RECENT years, Hall sensors became widely used because of their compatibility with modern semiconductor technologies. In particular, there are on the market applications for proximity switching, positioning, speed detection, and current sensing that use integrated Hall sensors fabricated in low-cost complementary metal-oxide-semiconductor (CMOS) technologies.

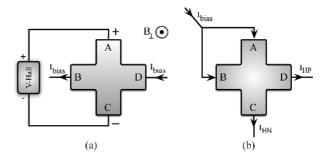

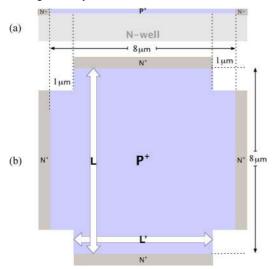

Since the Hall sensors convert a magnetic field into an electrical signal, either voltage or current, we distinguish between operation in voltage or current mode. For both modes, the biasing is a constant voltage or a constant current. In the voltage mode, the magnetic field (orthogonal to the Hall plate) is converted into an output voltage, as shown in Fig. 1(a). The layout permits current spinning, a technique used to compensate for the offset. The output voltage is typically in the order of micro- to millivolt and, therefore, it must be amplified before being transmitted to the outside world. A chain of amplifiers, often directly integrated on the same silicon chip, amplifies the signal by factors that can go up to 1000. Important features for qualifying Hall sensors are signal-to-noise ratio (SNR), residual offset, and sensitivity and offset temperature dependent drifts. Several techniques have been developed for improving these characteristics, [1]-[6]. In particular, works reported in [3] and in [4] present Hall sensor microsystems operating in the voltage mode

Manuscript received October 24, 2014; revised January 12, 2015; accepted February 21, 2015. Date of current version April 28, 2015. This paper was recommended by Associate Editor G. Setti.

The authors are with the Department of Electrical, Computer and Biomedical Engineering of the University of Pavia, 27100 Pavia, Italy (e-mail: hadi.hei-dari@unipv.it; edoardo.bonizzoni@unipv.it; u.gatti@redcatdevices.it; franco.maloberti@unipv.it).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2015.2415173

Fig. 1. (a) Hall plate operating in the voltage mode. (b) Proposed Hall plate working in the current mode.

achieving a temperature sensitivity lower than 100 ppm/ $^{\circ}$ C. The result is made possible by continuous time measurement and calibration of the device sensitivity. The same techniques are effective to compensate for drifts due to mechanical stresses and ageing. The work described in [6] focuses on the reduction of input referred noise and power consumption. The Hall microsystem uses current spinning and a delta-sigma modulator employing a switched biasing amplifier. The measured input referred noise is reduced down to 25  $\mu T/\sqrt{Hz}$ , a remarkable value, but the power consumption is 4.5 mW.

The current mode is an alternative to the widely used voltage mode. The output is a current and the configuration is like the one of Fig. 1(b). Even in this case, the shape of the sensor allows current spinning. The bias current,  $I_{bias}$ , enters into two consecutive arms (A and B in the figure); for zero magnetic field, it is split in two equal parts, assuming that the voltages of terminals C and D are equal. A magnetic field orthogonal to the Hall plate unbalances the sensor giving rise to different output currents,  $I_{HP}$  and  $I_{HN}$ , equal to  $I_{bias}/2 \pm I_{Hall}/2$ . The difference of these two currents can be represented by an equivalent current source of a Hall current,  $I_{Hall}$ , which is proportional to the applied magnetic field.

The effectiveness of Hall devices is measured by the sensitivity. It corresponds to the output quantity for unity supply quantity and magnetic field. Table I gives the sensitivity definitions for the two types of Hall devices.

This paper describes the design of a current mode Hall microsystem and its electronic interface. The prototype has been fabricated in a standard 0.18- $\mu$ m CMOS technology. The system consists of two Hall plates driven in the current mode able to provide a differential output current proportional to the applied magnetic field. The offset caused by possible mismatch in Hall plates dimensions is canceled out by means of current spinning. A fully differential chopper stabilized current integrator cascaded to the sensor determines the output voltage. Experimental results are reported.

$TABLE \ I \\ SENSITIVITY \ OF \ HALL \ DEVICES \ IN \ VOLTAGE \ AND \ CURRENT \ MODE$

| Mode                        | Sensitivity                                                     | Unit              |  |

|-----------------------------|-----------------------------------------------------------------|-------------------|--|

| Current biased voltage mode | $S_{V_I} = \left  \frac{V_{Hall}}{I_{bias} \times B} \right $   | [V/AT]            |  |

| Voltage biased voltage mode | $S_{V_{V}} = \left  \frac{V_{Hall}}{V_{bias} \times B} \right $ | $[V/VT] = T^{-1}$ |  |

| Current Mode                | $S_I = \left  \frac{I_{Hall}}{I_{bias} \times B} \right $       | $[A/AT] = T^{-1}$ |  |

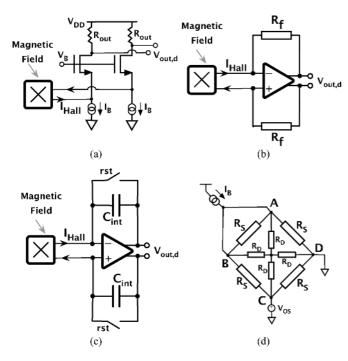

Fig. 2. Three I/V configurations: (a) common-gate detection, (b) resistive detection, and (c) integrator capacitive detection. (d) 8-resistors Hall plate equivalent model.

The paper is organized as follows. Section II provides the sensor and the readout circuit implementation details while Section III discusses the simulation results achieved in COMSOL Multiphysics environment of the designed Hall plate. Section IV presents the experimental verification of both the sensor and the entire microsystem while Section V draws the conclusions.

#### II. SYSTEM DESIGN

A current-mode Hall device typically generates small output currents, in the nano- to microampere range for very small bias currents. Fig. 2 shows three possible non-sampled techniques for the I/V conversion: the common-gate detection, the resistive detection, and the integrating detection, [7]. For the solution of Fig. 2(a), the Hall currents,  $\pm I_{Hall}$ , flow into the sources of a common-gate stage (N-channel input). The input resistances and the thermal noise currents depend on the transconductance of the input transistors. Therefore, in order to have a good SNR, a relatively large bias current,  $I_B$ , is required. The resistive detection of Fig. 2(b) uses a resistance,  $R_f$ , to convert the sensor current into voltage. In this case, the resistance  $R_f$  itself is the main noise source. This limits the

Fig. 3. Block diagram of the proposed magnetic current-mode Hall sensor microsystem.

maximum transresistance gain of the sensor interface. The third method, shown in Fig. 2(c), integrates the currents  $\pm I_{Hall}$  over the capacitor  $C_{int}$  for a given period of time after a reset. The method grants better noise performances, [7], [8], and provides a transresistance gain proportional to the integration time.

The first scheme is pseudo-differential, the other fully differential. For all of them, the equivalent offset of the measure circuit causes an offset in the differential current. If significant, it is necessary to compensate for the limit. In order to quantify the consequence of the offset, we can use the equivalent circuit of the sensor depicted in Fig. 2(d), [9]. Simple calculations show that an offset  $V_{os}$  unbalancing nodes C and D causes a current difference,  $\Delta I$ , equal to

$$\Delta I = V_{os} \frac{R_S + 3R_D}{R_S R_D} \tag{1}$$

It is proportional to the offset voltage and is independent on the bias current. A fitting of the designed Hall sensor with the electrical model of Fig. 2(d) provides  $R_S=18~\mathrm{k}\Omega$  and  $R_D=8~\mathrm{k}\Omega$ . With these values, an offset of 4 mV causes a current imbalance  $\Delta I=1.67~\mu\mathrm{A}$ . If the current sensitivity is 3%/T, it is required to use  $I_B=55.67~\mathrm{mA}$  for generating equal signal current with a 1-mT magnetic field.

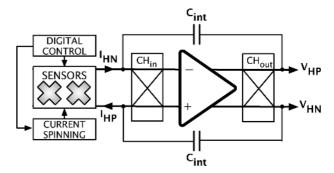

This project avoids the limit by using a chopper stabilized op-amp [10]. Fig. 3 shows the block diagram of the architecture. It uses two current-driven Hall plates to form a twin horizontal Hall sensor. They provide two differential output currents,  $I_{HN}$  and  $I_{HP}$ , which are integrated for a given time-slot. The digital unit controls the circuit and generates the phases necessary for chopper and current spinning operations.

# A. Horizontal Current Mode Twin Hall Sensor

For an optimal design of the Hall structures, it is necessary to account for noise, offset, and sensitivity. This has been done using the software COMSOL Multiphysics. Reference [9] shows that the cross-shaped layout is a good choice for a minimum noise, residual offset and good sensitivity. In addition, the symmetry of the cross-shaped layout enables current spinning [11].

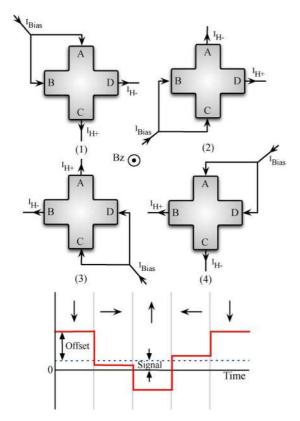

Fig. 4 shows the four configurations for each 90° rotation. The graph at the bottom of the figure conceptually shows the output offset during the four states. Every fourth phase, the average of the offset is zero.

Since simulations show that the optimal sensitivity is for relatively low doping, an N-well layer makes the Hall plate. A shallow highly doped P<sup>+</sup> top layer that covers the surface of the active area significantly reduces the 1/f noise. The four contact

Fig. 4. Current spinning technique and output offset of a single cross-shaped Hall plate during the four possible states.

Fig. 5. Model geometry of a cross-shaped Hall plate in a CMOS technology: (a) cross view and (b) top view.

regions in the N-well diffusion are N<sup>+</sup>. Fig. 5 shows the geometry of the Hall plate; Fig. 5(a) shows the cross section while Fig. 5(b) shows the top view. The device is  $8~\mu m \times 8~\mu m$  and the four contacts are 0.5- $\mu m$  wide.

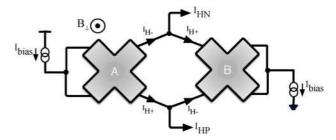

Since the output currents are the signal plus half of the bias current,  $I_{bias}/2$ , it is necessary to subtract this term from the two outputs. This is done by using a twin cross-shaped Hall sensor, as shown in Fig. 6. The bias current,  $I_{bias}$ , is injected into two shorted terminals of the cross shaped plate A and the same amount of current is drained from two shorted terminals of the Hall plate B. With no magnetic field, the sensor structure is balanced, thus making null the output currents,  $I_{HN}$  and  $I_{HP}$ .

Fig. 6. Twin current mode Hall sensor structure.

Fig. 7. Schematic diagram of the twin sensor with biasing and common mode feedback circuits.

When an external magnetic field orthogonal to the sensor plane,  $B_{\perp}$ , is applied, the sensor is unbalanced and, as mentioned, the output currents become

$$I_{H+} = \frac{I_{bias}}{2} + \frac{I_{Hall}}{2} \tag{2}$$

$$I_{H-} = \frac{I_{bias}}{2} - \frac{I_{Hall}}{2} \tag{3}$$

where the currents,  $I_{Hall}$ , proportional to the current mode sensitivity, depend on the sensor geometry, physical parameters, and temperature.

As evident from Fig. 6, the differential output current is twice the Hall current. The solution is also suitable for the current spinning technique.

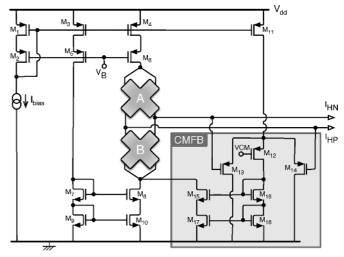

#### B. Twin Sensor Current Bias

The schematic of Fig. 6 uses two nominally equal current generators. A possible mismatch between them causes an unwanted common mode current at the outputs. The limit is avoided by the feedback control shown in Fig. 7. The high compliance cascode P-channel current mirror replicates and injects the bias current,  $I_{bias}$ , into the Hall sensor A. The N-channel cascode current mirror sinks a current lower than the nominal value, thus leaving room for the common mode control. The missing current is determined by the common mode feedback (CMFB) made by the P-channel differential pair  $M_{13}-M_{14}$ , sensitive to the common mode voltage of the output terminals.

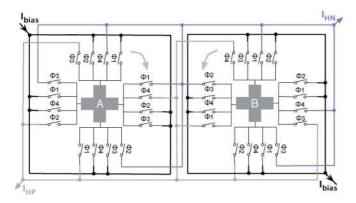

#### C. Current Spinning

The current spinning technique, [12], periodically interchanges output and supply terminals of Hall plates so that the bias current enters in each pair of terminals whereas a

Fig. 8. Hall plates with switches configuration for current spinning.

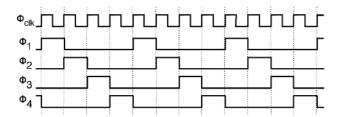

Fig. 9. Phases timing diagram for current spinning operation.

corresponding offset appears at the output. For the twin structure, the sensor A rotates clockwise while the sensor B rotates anti-clockwise, as shown in Fig. 8. At the end of a full spinning cycle, the average of the offset becomes zero. The spinning can be realized with a clockwise or an anti-clockwise rotation. Since there is the possibility of second order asymmetry, the direction of the spinning rotation is programmable by changing the clock phase generator. Fig. 8 shows the two sensors and related switches. Phases  $\Phi_1$ ,  $\Phi_2$ ,  $\Phi_3$ , and  $\Phi_4$  (given in Fig. 9) drive them so that during each phase two sensor terminals are connected to the bias generators and the other two to the outputs. The switches are complementary CMOS pairs.

## D. Readout Circuit

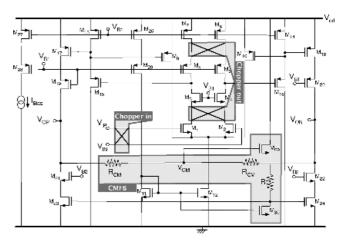

The block diagram of Fig. 3 includes an op-amp. Its integration of the signal current over the capacitances  $C_{int}$  gives rise to complementary voltage ramps at the output. However, its finite gain,  $A_0$ , affects the accuracy of the measure because of the voltage at the input terminals  $(-V_{out}/A_0)$  which unbalances the magnetic sensors. If the maximum swing of the complementary ramps is  $\pm 0.4$  V, a DC gain higher than 100 dB unbalances the input by  $\mp 4~\mu V$ . This high gain is obtained with the fully differential scheme of Fig. 10. It is a two stages amplifier. Each stage is a cascode. The coupling between the two stages uses source followers to accommodate the voltage room necessary for the current chopping of the first stage. The common mode feedback uses a resistors averaging network. The value of  $R_{CM}$ is large (1 M $\Omega$ ) and does not affect the gain of the second stage. The simulated DC gain is 109 dB and the GBW is 11 MHz. The chopping frequency used in the chopper is such that an integer number of spinning periods is performed within each chopping phase. Therefore, the offset affects an integer number of spinning cycles with positive sign and the same number of spinning periods with the negative sign. Moreover, the integration of the signal lasts for an integer number of chopping periods.

Fig. 10. Schematic diagram of the two stage fully differential amplifier.

Fig. 11. Simplified block diagram of the proposed microsystem with output SC filter and control signals of a complete read-out operation.

# E. Digital Control Unit, Output SC Filter, and Read-Out Operation

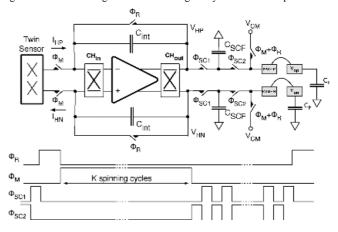

A digital control unit generates all the signals necessary for current spinning, reset, integration cycles, chopper and output switched-capacitor filter (Fig. 11). It uses an external master clock of  $f_{clk}=1~\mathrm{MHz}$ .

The read-out operation starts with a reset (phase  $\Phi_R$  shown in Fig. 11) of the integrating capacitors,  $C_{int}$ . The measure (phase  $\Phi_M$ ) lasts for an integer number, K, of current spinning cycles, digitally controlled. The amplifier differential output voltage becomes

$$V_{out,\pm} = \pm \frac{|I_{HP}|8K}{C_{int}f_{clk}} \tag{4}$$

At the end of the integration period, the twin sensor output currents  $I_{HP}$  and  $I_{HN}$  are disconnected from the readout circuit and the output voltages  $V_{HP}$  and  $V_{HN}$  are available for further processing or for output sampling.

A typical processing chain moves the signal generated by the front end into the digital domain by means of a suitable A/D converter. This design does not include the conversion on chip and provides at the output the analog differential signal. In order to avoid output buffers, two switched-capacitor RC networks drive the output pins as shown in Fig. 11. During the integration phase  $(\Phi_M)$ , the op-amp is load-free and the output pins are pre-charged to the common mode voltage,  $V_{CM}$ . At the end of the integration phase, the small switched capacitors  $C_{SCF}$

| Symbol                             | Value    | Parameter             |

|------------------------------------|----------|-----------------------|

| n [cm <sup>-3</sup> ]              | 7.38e16  | Carrier Concentration |

| μ [cm <sup>2</sup> /Vsec]          | 1058     | Mobility              |

| sigma0 [S/m]                       | $qn\mu$  | Silicon Conductivity  |

| r <sub>H</sub> [m <sup>3</sup> /C] | -1/(qn)  | Hall Coefficient      |

| $B_z$ [mT]                         | 0 ~ 20   | Magnetic Field        |

| V <sub>0</sub> [V]                 | 0.02     | Applied Voltage       |

| t_si [m]                           | 0.5e - 6 | Silicon Thickness     |

| Ι <sub>0</sub> [μΑ]                | 12       | Input Current         |

#### TABLE II MODEL PARAMETERS

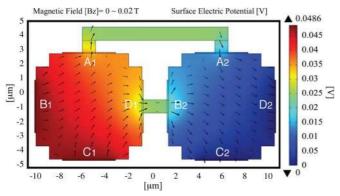

Fig. 12. COMSOL Multiphysics simulation results of a single current mode cross-shaped Hall sensor.

exponentially charge the output pins under the control of signals  $\Phi_{SC1}$  and  $\Phi_{SC2}$  (easily achievable by masking the master clock with the signal  $\Phi_M$ ).

#### III. SIMULATION RESULTS

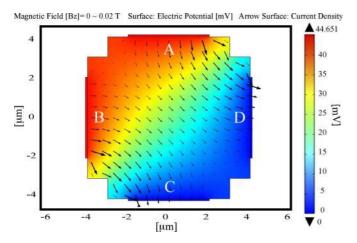

The study, design and performance optimization of the single Hall plate and the twin sensor have been carried out with the software COMSOL Multiphysics. It is used to estimate the currents distribution in the Hall devices with and without magnetic field and to account for possible geometrical mismatches. Table II summarizes the parameters used in the simulations. They correspond to the available technology.

#### A. Single Horizontal Cross-Shaped Hall Plate

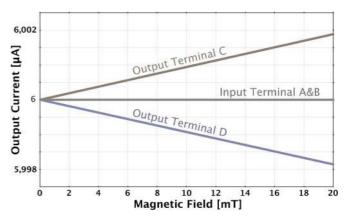

Fig. 12 shows the geometry of a single Hall plate with width and length of 8  $\mu$ m. The figure also shows the surface electrical distribution when a magnetic field of 20 mT is applied and the arising current density distribution (indicated by the arrows). The simulation uses the nominal bias current of 12  $\mu$ A injected in terminals A and B. The voltage drop across the device is 44.6 mV. The surface electric potential distribution seems symmetrical, but the small asymmetry caused by the magnetic field determines a difference in the output currents, as Fig. 13 shows. A swing of the magnetic field from 0 to 20 mT gives rise to a linear response with maximum differential output current of 3.4 nA. The resulting sensitivity is 1.42%/T. The value can be increased by using a well with lower doping and lower thickness.

Fig. 13. Simulated input and output currents of the current-mode Hall plate without any mismatch.

Fig. 14. Simulated average output currents  $(I_{H+} \text{ and } I_{H-})$  of current mode Hall sensor plate with mismatch and current spinning.

Fig. 15. Simulated sensitivity as a function of the Hall plate width.

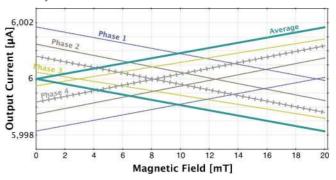

Fig. 14 shows the sensor responses in the four spinning connections with the arm B 0.01- $\mu m$  longer than the others. The current mismatch with zero magnetic field is, in the worst case, equivalent to the full scale signal. However, the spinning makes the average equal to zero, as indicated by Fig. 14.

The Hall current and, hence, the sensitivity depends on the geometry of the device and on physical parameters. It is given by

$$S_I = G \frac{r_H}{qnt} \tag{5}$$

where G is the geometry parameter,  $r_H$  the Hall factor, t the thickness of the sensor, and n the carrier concentration, [1].

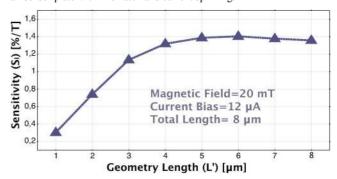

COMSOL Multiphysics simulations determine the optimal dimensions of the cross-shaped sensor. This study uses a total length of 8  $\mu m$  and the inner square varying from 1 to 8  $\mu m$ . Fig. 15 shows the results for a constant bias current of 12  $\mu A$  and 20-mT magnetic field. The sensitivity goes from a minimum of 0.37%  $T^{-1}$  to an optimum value (1.42%  $T^{-1}$ ) for  $L'=6~\mu m$ .

Fig. 16. Simulated sensitivity as a function of the temperature.

Fig. 17. COMSOL Multiphysics simulation results of a twin current mode cross-shaped Hall sensor.

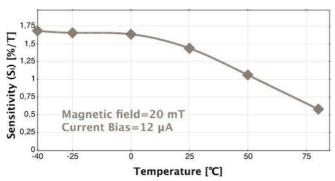

The sensitivity depends on temperature because the Hall factor  $r_H$  depends on temperature. This because of the variation of carriers concentration, n, and carriers mobility,  $\mu$ , [13]. COMSOL Multiphysics simulations verify the expected behavior, as Fig. 16 shows. The figure considers the relatively low temperature range, from  $-40~^{\circ}\mathrm{C}$  to  $+85~^{\circ}\mathrm{C}$ . Even for this simulation the bias current is 12  $\mu\mathrm{A}$  and the applied magnetic field is 20 mT. Since the sensitivity significantly changes above the room temperature, as it happens for all the Hall sensors, suitable correcting methods will be necessary.

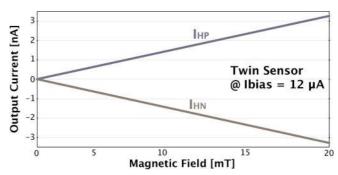

# B. Twin Horizontal Cross-Shaped Hall Plate

Fig. 17 shows the model geometry of the simulated twin Hall sensor. The figure shows the simulated surface electrical distribution and the current distribution when a perpendicular magnetic field of 20 mT is applied. The plot is for a bias current of 12  $\mu$ A injected in terminals  $B_1$  and  $C_1$  of the first plate and drained from terminals  $C_2$  and  $D_2$  of the second plate. In the same conditions, Fig. 18 plots the two output currents,  $I_{HP}$  and  $I_{HN}$ , as a function of the magnetic field applied in the range from 0 to 20 mT. The result confirms the expectations.

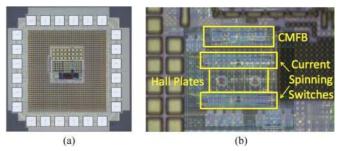

#### IV. MEASUREMENT RESULTS

The proposed sensor microsystem has been fabricated in a standard 0.18- $\mu$ m TSMC CMOS process with 6 metal and 2 poly layers. The chip microphotograph including the 24 pins is shown in Fig. 19(a). The chip area is 1.08  $\times$  1.08 mm². Fig. 19(b) shows a detail of the microphotograph with back-annotated layout of the sensor plates and relevant switches: they occupy an active area of  $80 \times 50 \ \mu \text{m}^2$ . The readout circuit area is  $300 \times 200 \ \mu \text{m}^2$ . The supply voltage of the entire chip is

Fig. 18. Simulated output currents ( $I_{HP}$  and  $I_{HN}$ ) of the twin Hall sensor as a function of the magnetic field.

Fig. 19. Hall sensor microphotograph: (a) whole chip including pads and (b) detail of the sensor plates area (with back-annotated layout).

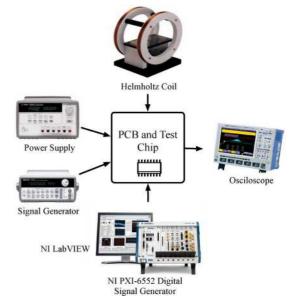

Fig. 20. Used measurement setup.

1.8 V and the master clock is at 1 MHz. The test chip permits to measure the sensor performance with [14] and without [11] the readout circuit.

Fig. 20 shows the measurement setup. A digital signal generator/analyzer (NI PXI-6552) provides the master clock. Two Helmholtz coils connected in series produce a nearly uniform magnetic field in middle of the two coils, [15]. The applied magnetic field ranges from 0 to 10 mT.

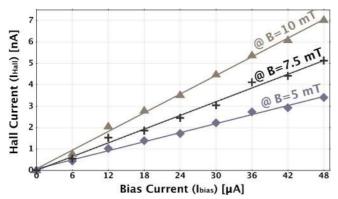

Fig. 21 plots the measured differential sensor output current,  $I_{Hall}$ , before the sensor interface as a function of the bias current for three different magnetic fields, 5 mT, 7.5 mT, and 10 mT.  $I_{bias}$  ranges from 0 to 48  $\mu$ A. The figure shows that within the measure accuracy the sensor is linear with respect to the applied magnetic field.

Fig. 21. Measured sensor output current before interface as a function of the biasing current at different magnetic fields.

Fig. 22. Measured sensor sensitivity without interface as a function of the biasing current at different magnetic fields.

Fig. 23. Distribution of the sensitivity after 70 repeated measurements for a bias current of 30  $\mu$ A and a magnetic field of 5 mT.

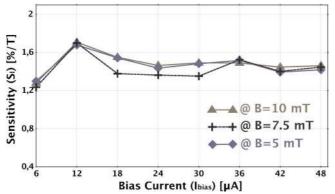

Fig. 22 gives the sensitivity (measured before the sensor interface),  $S_I$ , as a function of the sensor bias current (ranging from 6 to 48  $\mu$ A) for the above external magnetic fields.

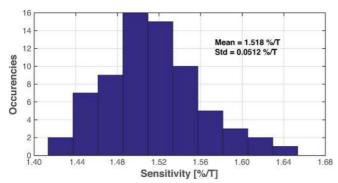

Fig. 23 plots the distribution of the sensitivity (measured before the sensor interface),  $S_I$ , obtained after 70 measurements repeated on the same sample in the same conditions (sensor bias current and magnetic field equal to 30  $\mu$ A and 5 mT, respectively). The achieved average value is  $1.518\%T^{-1}$  while the standard deviation is  $0.0512\%T^{-1}$ , equivalent to 11 bit.

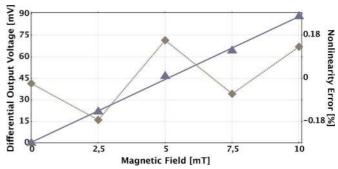

Fig. 24 shows the differential output voltage of the whole microsystem (twin sensor with readout circuit) as a function of the applied magnetic field. It ranges from 0 to 10 mT. The bias current is 36  $\mu$ A. The sensors offset is less than 50  $\mu$ T and the differential signal has a slope of about 8 mV/mT. The nonlinearity error, as Fig. 24 shows, is always lower than  $\pm 0.2\%_{FS}(\pm 20~\mu\text{T})$ . The used integrating capacitor is 4 pF and the integration is for 64 clock periods, with a conversion rate of 15.625 kS/s.

Fig. 24. Measured sensor differential output voltages as function of the magnetic field and its nonlinearity error.

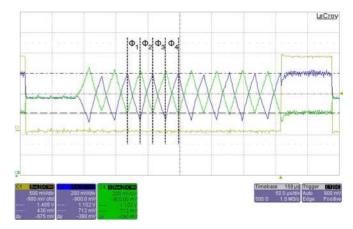

Fig. 25. Output voltages transient response measured with active probes.

TABLE III

PERFORMANCE SUMMARY AND COMPARISON TABLE OF THIS WORK WITH

RECENTLY PUBLISHED CMOS HALL SENSORS

|                     | [4]                   | [16]    | This Work            |

|---------------------|-----------------------|---------|----------------------|

| Year of Publication | 2013                  | 2014    | 2015                 |

| CMOS Technology     | 0.35 μm               | 0.18 µm | 0.18 μ <b>m</b>      |

| Hall Plate Shape    | Square                | Cross   | Cross                |

| Plates Number       | 4                     | 4       | 2                    |

| Mode of Operation   | Voltage               | Voltage | Current              |

| Spinning Frequency  | 20 kHz                | 1 kHz   | 250 kHz              |

| Supply Voltage      | 3.3 V                 | 5 V     | 1.8 V                |

| Max Sensitivity     | 50 mA/T               | 50 mV/T | 1660 V/A/mT          |

| Residual Offset     | 40 μT                 | 25 μΤ   | < 50 μT              |

| Sensor Bias Current | 1 mA                  | 350 μΑ  | 12 μΑ                |

| Power Consumption   | 6.6 mW                | N/A     | 120 μW               |

| Non-linearity       | < 0.08%               | N/A     | < 0.2%               |

| Chip Area           | 11.55 mm <sup>2</sup> | N/A     | 1.16 mm <sup>2</sup> |

| Active Area         | N/A                   | N/A     | 0.06 mm <sup>2</sup> |

|                     |                       |         |                      |

Fig. 25 shows the integrator output voltages measured with low capacitive active probes. The master clock frequency has been reduced to 50 kHz to emphasize the integration of the offset each spinning period. It results spur signals as large as few hundreds of millivolt cancelled out at the end of the spinning cycle. For a bias current equal to 48  $\mu A$  and an applied magnetic field of 7.5 mT, the final differential output voltage is the expected 390 mV.

Table III summarizes the microsystem performance for a bias current of 12  $\mu$ A and provides a comparison of this work with other two recently published CMOS Hall sensors. The overall

measured power consumption is about 120  $\mu$ W. The readout section consumes 54  $\mu$ W. The sensor and the relevant switches for current spinning measured power consumption is 65  $\mu$ W.

#### V. CONCLUSION

This paper described a magnetic current-mode Hall microsystem. Two Hall plates operating in the current mode and able to provide differential currents at the output nodes have been fabricated in a standard 0.18- $\mu$ m CMOS process. The use of a low-noise chopper stabilized operational amplifier enables the integration of the signal current and ensures good voltage sensitivity. The measurement cycle starts with a reset phase followed by the integration of a multiple of full current spinning cycles. Measurement results show that the Hall sensor can achieve a sensitivity after the sensor interface better than 1660 V/A/mT when the magnetic field is in the range from 0 to 7 mT  $(I_{bias} = 36 \mu A, 512 T_{CK})$ . The use of the crossed-shaped Hall plates and a current-mode approach enables current spinning technique for offset cancellation. The overall measured offset, power consumption and the achieved voltage sensor sensitivity after the sensor interface are remarkable.

#### REFERENCES

- R. S. Popovic, Hall Effect Devices, 2nd ed. Boca Raton, FL, USA: CRC, 2010.

- [2] C. Schott and S. Huber, Modern CMOS Hall Sensors With Integrated Magnetic Concentrators. Berlin/Heidelberg, Germany: Springer, 2008, pp. 3–21.

- [3] M. Pastre, M. Kayal, and H. Blanchardl, "A hall sensor analog front end for current measurement with continuous gain calibration," *IEEE Sensors J.*, vol. 7, no. 5, pp. 860–867, May 2007.

- [4] A. Ajbl, M. Pastre, and M. Kayal, "A fully integrated hall sensor microsystem for contactless current measurement," *IEEE Sensors J.*, vol. 13, no. 6, pp. 2271–2278, 2013.

- [5] G. Boero, D. Memierre, P. A. Besse, and R. S. Popovic, "Micro-hall devices: Performance, technologies and applications," *Sensors Actua*tors A, no. 106, pp. 314–320, 2003.

- [6] Y.-J. Min, C.-K. Kwon, H.-K. Kim, C. Kim, and S.-W. Kim, "A CMOS magnetic hall sensor using a switched biasing amplifier," *IEEE Sensors J.*, vol. 12, no. 5, pp. 1195–1196, May 2012.

- [7] T. A. Roessig, R. T. Howe, A. P. Pisano, and J. H. Smith, "Surface-micromachined 1 MHz oscillator with low-noise pierce configuration," in *Proc. IEEE Solid-State Sensor Actuator Workshop*, 1998.

- [8] J. Verd, G. Abadal, J. Teva, A. Uranga, N. Barniol, J. Esteve, M. Duch, and F. Perez-Murano, "High-sensitivity capacitive readout system for resonant submicrometer-scale cantilevers based sensors," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2005, vol. 5, pp. 4209–4212.

- [9] H. Heidari, U. Gatti, E. Bonizzoni, and F. Maloberti, "Low-noise low-offset current-mode hall sensors," in *Proc. IEEE Conf. Ph.D. Res. Microelectron. Electron. (PRIME)*, Jun. 2013, pp. 325–328.

- [10] M. Belloni, E. Bonizzoni, A. Fornasari, and F. Maloberti, "A micropower chopper-CDS operational amplifier," *IEEE J. Solid-State Circuits*, vol. 45, no. 12, pp. 2521–2529, Dec. 2010.

- [11] H. Heidari, E. Bonizzoni, U. Gatti, and F. Maloberti, "A current-mode CMOS integrated microsystem for current spinning magnetic hall sensors," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2014, pp. 678–681.

- [12] A. Bilotti, G. Monreal, and R. Vig, "Monolithic magnetic hall sensor using dynamic quadrature offset cancellation," *IEEE J. Solid-State Cir*cuits, vol. 32, no. 6, pp. 829–836, Jun. 1997.

- [13] M.-A. Paun, J. M. Sallese, and M. Kayal, "Temperature influence investigation on hall effect sensors performance using a lumped circuit model," *Proc. IEEE Sensors*, pp. 382–385, 2012.

- [14] H. Heidari, E. Bonizzoni, U. Gatti, and F. Maloberti, "A 0.18- μm CMOS current-mode hall magnetic sensor with very low bias current and high sensitive front-end," *Proc. IEEE Sensors*, pp. 1467–1470, Nov. 2014

- [15] E. L. Bronaugh, "Helmholtz coils for EMI immunity testing: Stretching the uniform field area," in *Proc. IEEE Int. Conf. Electromagn. Compat.*, Aug. 1990, pp. 169–172.

[16] J. Jiang, W. J. Kindt, and K. A. A. Makinwa, "A continuous-time ripple reduction technique for spinning-current hall sensors," *IEEE J. Solid-State Circuits*, vol. 49, no. 7, pp. 1525–1534, Jul. 2014.

Hadi Heidari (M'15) is working at the Integrated Microsystem (IMS) group of the University of Pavia, Italy, as a Ph.D. student under supervision of Prof. Franco Maloberti since November 2011. During a first project of his Ph.D., he worked on integrated CMOS horizontal Hall sensor microsystems. In a second chip, he designed a multi-sensors prototype of four different vertical Hall sensors. A third chip was on the design of a magnetic sensor with interface for NMR system integration. To realize this project, he cooperated with the State Key Laboratory of

Analog and Mixed-Signal VLSI at the University of Macau. His current research interests include analog/mixed-signal circuit design, CMOS sensors, interface circuits for microsensors, magnetic sensors, and FEM simulations. He is a reviewer of the IEEE SENSORS JOURNAL. He received honorary mention paper award at the IEEE ISCAS 2014 and gold leaf award at IEEE PRIME 2014 conferences.

Edoardo Bonizzoni (M'06) was born in Pavia, Italy, in 1977. He received the Laurea degree (summa cum laude) in electronic engineering from the University of Pavia in 2002. From the same university, he received the Ph.D. degree in electronic, computer, and electrical engineering in 2006. In 2002 he joined the Integrated Microsystems Laboratory of the University of Pavia as a Ph.D. candidate. During his Ph.D., he worked on development, design, and testing of non-volatile memories with particular regard to phase-change memories. From 2006 his

research interests are mainly focused on the design and testing of DC-DC and A/D converters. In this period he worked on single-inductor multiple-output DC-DC buck regulator solutions and on both Nyquist-rate and oversampled A/D converters. Recently, his research focuses on the design of high precision amplifiers and ultra-low voltage voltage reference circuits as well. Presently, he is an Assistant Professor at the Department of Electrical, Computer, and Biomedical Engineering of the University of Pavia. Dr. Bonizzoni coauthored more than 70 papers and he is corecipient of the IEEE International Symposium on Circuits and Systems (ISCAS) 2014 honorary mention paper award of the Sensory Systems Track, of the IEEE/IEEJ Analog VLSI Workshop (AVLSIWS) 2010 best paper award, of the IEEE European Solid-State Circuits Conference (ESSCIRC) 2007 best paper award and of the IEEE/IEEJ Analog VLSI Workshop (AVLSIWS) 2007 best paper award. Since 2011, he is an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—PART II: EXPRESS BRIEFS. Dr. Bonizzoni has been nominated Best TCAS-II Associate Editor for the 2012-2013 term. Since 2013 he is a TPC member of the IEEE Conference on Ph.D. Research in Microelectronics and Electronics (PRIME).

**Umberto Gatti** (M'91) received the Laurea degree (*summa cum laude*) in electronic engineering and the Ph.D. degree in electronics and information engineering from the University of Pavia, Italy, in 1987 and 1992, respectively. From 1993 to 1999, he worked in the Central R&D Lab of Italtel, Italy, and then in the R&D Lab of Siemens, Italy, as Senior ASIC Engineer. Besides developing analog and mixed analog-digital CMOS/BiCMOS ICs for telecom (data converters, base-band wireless transceivers, burst mode PON interfaces), he was the coordinator of funded projects

under the frameworks of FP and Eureka, focused on high-speed Nyquist-rate and sigma-delta converters. In 2007 he joined Nokia Siemens Networks, Italy, where he was a Sr. Power Supply Architect for telecom equipment (both at rack and boards level). Currently he is with Redcat Devices, Italy, as Senior Microelectronic Engineer and also holds cooperation with the University of Pavia in the Hall sensors field. His current research interests are in the area of CMOS mixed-signal ICs, in particular in rad-hard digital libraries and SRAMs, data converters, and testing techniques under irradiations. He holds 2 international patents and is coauthor of more than 50 papers.

Franco Maloberti (F'96) received the Laurea degree in physics (summa cum laude) from the University of Parma, Parma, Italy, in 1968, and the Doctorate Honoris Causa in electronics from the Instituto Nacional de Astrofisica, Optica y Electronica (Inaoe), Puebla, Mexico, in 1996. He was a Visiting Professor at The Swiss Federal Institute of Technology (ETH-PEL), Zurich, Switzerland and at the EPFL, Lausanne, Switzerland. He was the TI/J. Kilby Chair Professor at Texas A&M University, and the Distinguished Microelectronic Chair Professor at the University of

Texas at Dallas. Presently he is Professor of Microelectronics and Head of the Micro Integrated Systems Group, University of Pavia, Italy. His professional expertise is in the design, analysis, and characterization of integrated circuits and analog digital applications, mainly in the areas of switched-capacitor circuits, data converters, interfaces for telecommunication and sensor systems, and CAD for analog and mixed A/D design. He has written more than 450 published papers

on journals or conference proceedings, four books, and holds 30 patents. Dr. Maloberti was the recipient of the XII Pedriali Prize for his technical and scientific contributions to national industrial production, in 1992. He was corecipient of the 1996 Institute of Electrical Engineers Fleming Premium, the best Paper award, ESSCIRC-2007, and the best paper award, IEEJ Analog Workshop—2007 and 2010. He was the President of the IEEE Sensor Council from 2002 to 2003 and Vice-President, Region 8, of the IEEE CAS Society from 1995 to 1997 and an Associate Editor of IEEE TCAS-II. He served as VP-Publications of the IEEE CAS Society 2007-2008. He was distinguished lecturer of the IEEE Solid State Circuits Society 2009–2010 and distinguished lecturer of the Circuits and Systems Society 2012-2013. He received the 1999 IEEE CAS Society Meritorious Service Award, the 2000 CAS Society Golden Jubilee Medal, and the 2000 IEEE Millennium Medal. He received the IEEE CAS Society 2013 Mac Van Valkenburg Award. He is an IEEE Fellow. In 2009 he received the title of Honorary Professor of the University of Macau and he is currently the chairman of the Academic Committee of the Microelectronics Key-Lab of Macau. He is President Elect of the IEEE Circuits and Systems Society.