# A CMOS Image Sensor With In-Pixel Buried-Channel Source Follower and Optimized Row Selector

Yue Chen, *Student Member, IEEE*, Xinyang Wang, *Member, IEEE*, Adri J. Mierop, and Albert J. P. Theuwissen, *Fellow, IEEE*

Abstract—This paper presents a CMOS imager sensor with pinned-photodiode 4T active pixels which use in-pixel buried-channel source followers (SFs) and optimized row selectors. The test sensor has been fabricated in a 0.18- $\mu$ m CMOS process. The sensor characterization was carried out successfully, and the results show that, compared with a regular imager with the standard nMOS transistor surface-mode SF, the new pixel structure reduces dark random noise by 50% and improves the output swing by almost 100% without any conflicts to the signal readout operation of the pixels. Furthermore, the new pixel structure is able to drastically minimize in-pixel random-telegraph-signal noise.

*Index Terms*—Buried-channel source follower (BSF), CMOS image sensor (CIS), optimized row selector, random-telegraph-signal (RTS) noise, 4T-active-pixel sensor.

#### I. INTRODUCTION

**T** ECENTLY, a lot of efforts have been made on reducing the random noise in CMOS imagers, which is mainly composed of the 1/f and the so-called random-telegraph-signal (RTS) noises [1]. Research has revealed that the dominated random noise sources in CMOS image sensors (CISs) are due to the lattice defects at the Si-SiO<sub>2</sub> interface of the in-pixel source follower (SF) transistor [2], [3]. However, the exact mechanism of the RTS and the 1/f noises is still not completely clear [4], and the use of correlated double sampling (CDS) cannot fully eliminate 1/f and RTS noises [5], [6]. Therefore, reducing these noises becomes very difficult. Moreover, as CMOS processes scale down, the gate area of the transistors becomes so small that it easily happens to have only one active interface trap underneath the transistor's gate, which will induce the RTS noise. Because of this single-electron trapping and detrapping during the transistor operation, the RTS appears

Manuscript received January 6, 2009; revised June 15, 2009. First published September 18, 2009; current version published October 21, 2009. The review of this paper was arranged by Editor J. Hynecek.

- Y. Chen is with the Electronic Instrumentation Laboratory, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: yue.chen@tudelft.nl).

- X. Wang was with the Electronic Instrumentation Laboratory, Delft University of Technology, 2628 CD Delft, The Netherlands. He is now with CMOSIS NV, 2000 Antwerpen, Belgium.

- A. J. Mierop is with DALSA Semiconductors, 5656 AE Eindhoven, The Netherlands.

- A. J. P. Theuwissen is with Harvest Imaging, 3960 Bree, Belgium, and also with the Electronic Instrumentation Laboratory, Delft University of Technology, 2628 CD Delft, The Netherlands.

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2009.2030600

in pixels which have only one active interface defect and dominates the pixel temporal noise, and RTS noise limits the imaging quality under low-light conditions [6], [7]. Therefore, as long as a perfect clean gate interface cannot be guaranteed, the 1/f or RTS noise will stay dominant in the random noise in pixels.

It has been proved that it is difficult to reduce these noises using circuit techniques [8]. Therefore, the effective techniques are mainly the improvements of the processing technology. On the other hand, reducing the gate-oxide thickness should improve the gate control over the channel region, and the converse is also true. However, because the image-sensor process flow has constraints on reducing the gate-oxide thickness, e.g., increase of dark current due to gate-induced drain leakage, RTS cannot be reduced beyond a certain point for a given trap density. One common method is to adjust the annealing process in order to optimize the gate-oxide properties [1], [9]. However, such an approach is very process dependent and needs precise control on annealing temperatures and time. Furthermore, from the noise point of view, simply reducing the amount of Si-SiO<sub>2</sub> interface traps through annealing optimization may not help too much since a single interface defect can already introduce RTS noise as high as millivolts [10]. Consequently, the reduction of the interface-defect-induced noise by improving the annealing process will become less significant.

In order to deal with the imperfection Si-SiO2 interfaceintroduced random noise, an alternative approach can be used, i.e., taking the conducting carriers away from the Si-SiO2 interface by creating a buried-channel nMOS transistor (nMOST) in a modern CMOS imager process. In this paper, an in-pixel SF based on a buried-channel nMOST is introduced. The buried channel requires only one extra implantation, which pushes the highest potential in the channel away from the Si-SiO<sub>2</sub> interface. Thus, the possibility of carriers being trapped by lattice defects can be minimized, and the 1/f and RTS noises can be reduced. As a result, the random noise level of the imager can be significantly reduced. Furthermore, because the buried-channel transistor has a negative threshold voltage, the output swing of the pixels can be drastically improved by the buried-channel SF (BSF) transistor together with an optimized row selector. This means that "digital" transistors with reduced power-supply voltages can be used in the pixel without limiting the pixel's output swing, saturation level, and dynamic range.

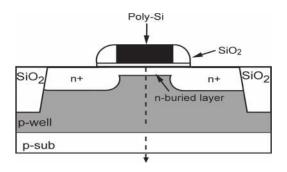

Fig. 1. Cross section of a buried-channel nMOST.

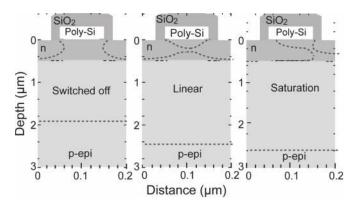

Fig. 2. Expected operation modes of a buried-channel nMOST.

#### II. WORKING PRINCIPLE OF BURIED-CHANNEL nMOST

In principle, the buried-channel transistors stand for transistors of which the majority of their conducting carriers flow far beneath the gate Si-SiO<sub>2</sub> interface during operation. In a modern CMOS process that uses a single-gate poly process, the p-type MOS transistors are naturally buried-channel devices because of the compensation threshold voltage  $(V_t)$  adjust implantation process during fabrication. Therefore, the expected structure of a buried-channel nMOST is very straightforward, i.e., a total region reversing of a pMOS transistor, as shown in Fig. 1. The desired operation modes for such a device are shown in Fig. 2. It was simulated from an "ideal" CMOS process, which means that all parameters and process flows can be adjusted freely. The dashed lines stand for the boundaries of the depletion regions. As shown in Fig. 2, during switch OFF, the gate interface region is fully depleted, and no current flows from the drain to the source. While during the linear operation, the two depletion regions are separated from each other, which allows current to flow. In the saturation region, the channel is pinched off near the drain side.

Because of the buried-channel doping, the  $V_t$  of this nMOST is shifted toward a negative value. This will help to increase the pixel output swing, which will be discussed in detail with measurement results later.

# III. DEVICE SIMULATIONS

The device simulations were done with MEDICI, and the device structure, material, and doping information was generated by the process simulator TSUPREM. The original simulation files were supplied by TSMC, which described the standard

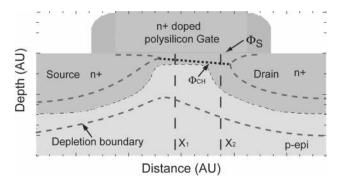

Fig. 3. Cross section of simulated BSF under SF operation bias condition.

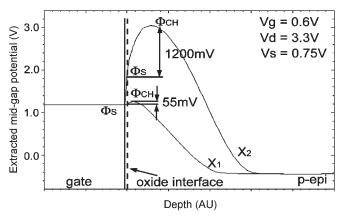

Fig. 4. Middle-gap potential curve extracted along the different locations of the gate length.

fabrication steps of an in-pixel SF transistor in a 0.18- $\mu$ m CMOS process.

#### A. Potential Distance Simulations

According to [11], to avoid the interaction between the carriers and the gate Si-SiO<sub>2</sub> interface traps, the "potential distance" between the channel and gate Si-SiO2 interface needs to be greater than kT/q (-25.8 mV at room temperature), which is also expected in the buried-channel nMOS SF. The simulated device cross section with the SF bias conditions is shown in Fig. 3. The boundary of the depletion region is shown as well as the location of  $\Phi_{\rm CH}$  which means the potential distance between the highest channel potential along the gate length. In this case, the implantation was simulated with phosphorus doping, with a total dose of  $6.5 \times 10^{12}$  atoms/cm<sup>2</sup>, and implantation energy of 70 keV, bias current density of 12  $\mu$ A/ $\mu$ m. It is important to note that the  $\Phi_{CH}$  dashed line along the gate is a slanting line instead of a horizontal one. It can be seen that the difference of  $\Phi_{\rm CH}$  at the various locations along the channel is rather significant, which means that the trap-related noise-reduction efficiency will highly depend on the trap location along the gate length. From the middle gap potential curves extracted along  $X_1$  and  $X_2$ , shown in Fig. 4, it can be seen that, although both the potential distances between the channel potential  $\Phi_{\mathrm{CH}}$  and the gate interface potential  $\Phi_S$  at  $X_1$  and  $X_2$  are greater than kT/q (25.8 mV), the channel may turn back to surface mode near the source.

| Implantation<br>Energy(keV)<br>/Dose(atom/cm <sup>2</sup> ) | Channel depth(nm)<br>(Vgate = 2.6 V) | Channel depth(nm)<br>(Vgate = 1.6 V) | Channel depth(nm)<br>(Vgate = 0.6 V) |

|-------------------------------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|

| 70/7.5 x 10 <sup>12</sup> (P)                               | 20                                   | 30                                   | 40                                   |

| 80/7.5 x 10 <sup>12</sup> (P)                               | 20                                   | 30                                   | 40                                   |

| 90/8.5 x 10 <sup>12</sup> (P)                               | 25                                   | 40                                   | 55                                   |

TABLE I SIMULATED CHANNEL DEPTH OF DIFFERENT DOPINGS

#### B. Channel-Depth Simulations

Aside from the potential distance, the channel depth, i.e., the actual physical distance between the channel (the maximum potential) and the gate Si-SiO $_2$  interface, was also investigated by simulations. The channel depths of four different doping solutions as a function of the gate bias are shown in Table I. The implantation was still simulated with phosphorus doping, and the source/drain regions are both with a standard shallow  $\rm n^+$  implant. As shown, the maximum channel buried depth is determined by the doping energy and dose. Comparing with the channel depth of a buried-channel CCD [11], i.e.,  $\sim 0.8~\mu \rm m$ , the channel depth is, in fact, shallow, such that, in saturation condition, it is possible that the device turns into partly surface mode. This condition is believed mainly due to the extremely thin gate oxide in modern CMOS technology, which is actually a fundamental technology limitation.

Although the channel depth cannot be optimized the same as the condition in a buried-channel CCD, the simulation results of the potential distance can already provide very important evidence that buried-channel devices can be made by means of the current CMOS process technology and that the buried condition can be achieved as well. The "buried" concept and feasibility of creating such devices in a modern CMOS process are also proved by means of the simulations. Test structures were then developed based on the TSMC  $0.18-\mu m$  CMOS process with different buried-channel implant-energy and dose combinations.

# C. Test Transistor Characterization

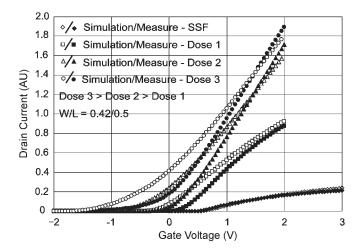

The comparison of the simulated and measured gate characteristics of the surface- and buried-channel transistors is shown in Fig. 5. These buried-channel devices were made through different total doses but with the same implantation energy. The transistor size is the same.

It can be seen that, as expected, increasing the implantation dose will shift the transistor threshold voltage toward a more negative value. The simulated and measured I-V curves of the standard surface-channel device match very well. Increasing the implantation dose will lower the  $V_t$  of the transistors. The  $V_t$  extracted from the measurement is slightly higher than the simulated one. Such difference becomes larger with higher implantation dose.

As shown in Fig. 5, under the same gate bias condition, the slope of the I-V curve, i.e., the transconductance  $(g_m)$ , increases with increasing the implantation dose. For the SF application in CMOS imagers, the transistors operate under very small biasing current in order to maintain a weak inversion operation; therefore, it is important to compare the  $g_m$ 's at the

Fig. 5. Simulated and measured gate characteristic of transistors with different implantations.

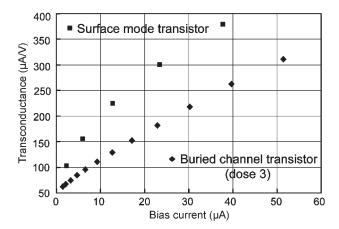

Fig. 6. Measured  $g_m$  of the surface and buried-channel transistor.

expected operation points. In Fig. 6, the measured  $g_m$  of the surface- and buried-channel transistors is shown as a function of the bias current. The experiment was done with a fixed source voltage in order to include the body effect. The gate voltage is swept to acquire all the dc points. As shown, with the same bias current, the  $g_m$  of the buried-channel device is almost half of that of the surface-mode device, which is due to the fact that the channel is buried into bulk silicon, and, thus, less gate-modulation efficiency; such effect is similar to increasing the gate-oxide thickness. The decreased  $g_m$  may cause a longer settling time, but this difference of buried- and surface-mode devices is rather unimportant. In imaging applications, the signal on the SF gate normally varies between reset and video signals, and the settling time of the column is mainly dominated by the slew rate (charge/discharge of the column capacitor).

The buried-channel implantation, in fact, also changes the gate capacitance of SF; thus, a change of  $g_m$  is observed. BSF pixels should have a higher capacitance of floating diffusion (FD) node. However, the capacitance of the FD node measured consists of FD active capacitance, SF capacitance (only 1/3), TG overlap capacitance, and other parasitic capacitances; thus, an increase due to buried-channel implantation is not so obvious.

Fig. 7. Chip micrograph of the prototype imager.

Based on the simulation results and test transistor characterization, it is shown that the buried-channel conditions, i.e., maximum channel potential and buried depth, and the threshold voltage of transistors are strongly dependent on implantation energy and dose. Increasing the implantation energy will slightly increase the channel depth, however, with the risk of a large leakage current. Therefore, the implantation dose and energy need to be adjusted carefully to obtain an optimized channel depth and threshold voltage. On the other hand, in order to inspect how much CMOS imagers may benefit from BSFs in terms of read-out noise, a large number of buried-channel nMOSTs need to be measured to acquire enough statistical data. Thus, the benefits from BSFs in terms of read-out noise can only be proved by measuring the actual sensors.

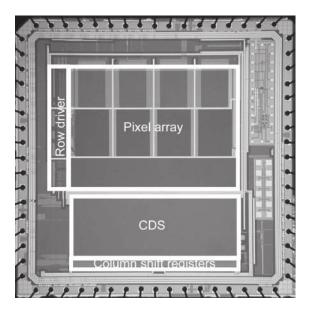

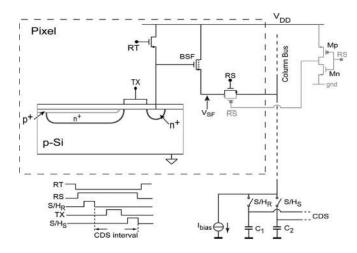

## IV. SENSOR DESIGN

A prototype sensor with BSFs was first fabricated in a 0.18- $\mu$ m 1P3M CMOS process by TSMC. The chip micrograph with several fundamental functional blocks of the prototype chip is shown in Fig. 7. The pixel array is 240 rows  $\times$ 300 columns with three different pixel pitches, i.e., 6, 7.4, and 10  $\mu$ m. All pixels are pinned-photodiode 4T designs with both BSF and surface-channel SF (SSF) pixels on the same sensor. In the pixel design, the gate signal of all transistors, i.e., the reset transistor (RT), the charge transfer transistor, and the row select transistor, can be supplied individually. The fill factors for 6- and 7.4- $\mu$ m pixels are quite low in order to give flexibility to the SF sizing. The row and the column addressing circuitry are realized through a shift register structure. The CDS at each column is used to cancel out the offset, the reset (kTC) noise, and the 1/f noise. The pixel output can be amplified ten times by the CDS amplifier to lift the signal and the noise floor already from chip level in order to achieve good accuracy of the noise measurement. The front-end read timing is supplied by an external FPGA. The sensor clock frequency is 10 MHz, which is a unit clock signal (clk) applied through the FPGA.

The sensor signal will be read out during each line time, which is 3000 clk cycles for this case. During these 3000 clk cycles, one line of pixels is being read out to the column bus, CDS will be performed, and video signals will be read out by an output amplifier one by one from that line of pixels. Integration time is set by n times of line time, and n can be adjusted through I2C interface on an FPGA coding program. The sensor has a rolling shutter operation. The SF settling time is  $0.5~\mu s$ , which is five clk cycles. For the noise measurement, the CDS time interval is  $1.5~\mu s$ , and the charge transfer period is  $1~\mu s$ . The outputs of the imager are analog signals, being converted into digital by an off-chip image processor with a 12-b ADC. The exact analog signal processing chain of a CMOS imager was well explained in [12].

The characterization results of the prototype sensor were already presented and well analyzed in [10] and [13]. The noise improvement achieved by using BSFs inside the pixels was rather significant. However, as explained in [10], a fundamental tradeoff between the maximum pixel output and the image lag did exist in the prototype BSF pixels.

As mentioned in Section II, the maximum pixel output swing can be significantly improved because of the negative  $V_t$  of the BSF transistor. However, such improvement is limited by the row select switch, which is normally realized by a standard nMOST. The maximum voltage which can pass through the row select switch is then determined by the gate voltage and threshold voltage of this row select transistor. Therefore, the FD node reset voltage is expected to be reasonably low in order to ensure that the video signal can be properly read out by the row select switch. Meanwhile, a small FD voltage is also preferred in relation to the random noise [13]. However, reducing the FD reset voltage brings a potential risk of incomplete charge transfer from the photodiode to the FD region, thus introducing image lag. Therefore, this tradeoff between the noise reduction and improvement of the output swing (the possibility of introducing image lag) is limiting the feasibility and performance of the BSF pixels. A solution to this issue is proposed and applied to the following design, i.e., a new test sensor with in-pixel BSFs and optimized row select switches.

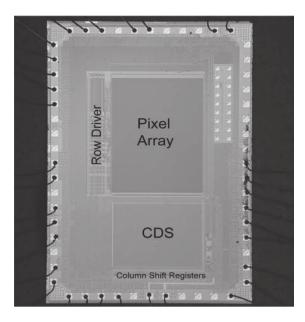

The new test sensor was fabricated in a 0.18- $\mu$ m 1P4MCMOS process by TSMC. The chip micrograph with several fundamental functional blocks of the prototype chip is shown in Fig. 8. The pixel array is 200 rows  $\times$  150 columns with 10- $\mu$ m pixel pitches. All pixels are pinned-photodiode 4T designs with BSF, in which five columns of pixels are with both BSF and an optimized row selector. The schematic of the pixel is shown in Fig. 9, in which a transmission gate is implemented as the row selector. All the other readout structures and techniques were being used as the prototype sensor. The system clock frequency is still 10 MHz. The front-end read timing is supplied by an external FPGA. For the noise measurement, the CDS time interval and the charge transfer period are also the same with the prototype sensor, i.e., 1.5 and 1  $\mu$ s, respectively. The outputs of the imager are analog signals, being converted into digital signals by an off-chip image processor with a 12-b ADC.

Both prototype and new test imager were successfully fabricated and tested. The measurement results are presented and discussed in the following section.

Fig. 8. Chip micrograph of the new test imager.

Fig. 9. Pixel schematic and front-end readout timing.

# V. MEASUREMENT RESULTS

#### A. Pixel Output Swing

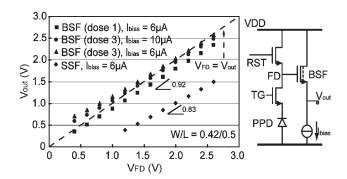

The pixel output swing was measured from the 6- $\mu$ m pitch pixels in the prototype sensor. The measurement results are shown in Fig. 10. During the measurement, the RT gate is tied to the highest voltage of the pixel, i.e., performing hard reset, and the transfer gate (TX) is grounded. Therefore, the FD voltage equals the RT power supply. The column bias current remains constant for all pixels.

As shown, the output swing of the BSF pixels is about 2 V, nearly double that of the SSF pixels. If the bias current is reduced while the implantation dose remains the same, the pixel output further approaches or even exceeds the line of  $V_{\rm FD}=V_{\rm out}$ , which indicates that the channel is buried deeper into the silicon. If the bias current remains constant, increasing the implantation dose also pushes the channel deeper. Therefore, in principle, the pixel readout noise level, if dominated by the interface trap related noise, will be smaller in case of a smaller bias current or higher implantation dose of the BSF.

Fig. 10. Pixel output swing measurement with different implantation doping and bias currents.

Furthermore, it can be seen that, regardless of the bias current and implantation dose, all output swing curves tend toward  $V_{\rm out} > V_{\rm FD}$  at a lower FD voltage, i.e., the SF operates further into the buried mode. Therefore, the pixel readout noise is expected to be reduced as well. The measured voltage gain of the SF is improved from 0.83 of the surface-mode devices to about 0.92–0.95 of a buried-channel transistor. To make a conclusion, both the pixel output swing and the SF voltage gain are improved by using the BSFs inside the pixel.

#### B. Dark Random Noise

The pixel random noise can be measured by calculating the standard deviation of each pixel output among multiframes. However, in order to distinguish that the random noise is from the APS pixel or from the analog processing, one common approach is to ground the row select transistor during operation; thus, the pixel output node can be considered as floating, and the measured random noise is the noise of the analog chain. Therefore, if any changes of the in-pixel transistor or photodiode operation status during the imager operation, e.g., the integration times, the bias current of the SF, and the reduction of the CDS period, introduce significant effect on the random noise, it can be confirmed that the measured noise is indeed from the pixel-level noise sources instead of the analog chain. In order to exclude the contribution of the photon shot noise from the total noise floor, all the noise measurements were carried out in complete darkness.

The dark random noise of BSF and SSF pixels was measured with both the prototype and new test sensor. Both the BSFs and SSFs were biased with 6- $\mu$ A current. The FD reset voltage of the SSF pixels was 3.3 V, while in order to ensure that the row select transistor works properly, the measurement was done with a low FD reset voltage on the BSF pixels in the prototype sensor, i.e., 1.8 V. However, with the optimized row selector, the dark random noise can be measured with a much higher FD reset voltage on the BSF pixels in the new test sensor, i.e., 3.3 V.

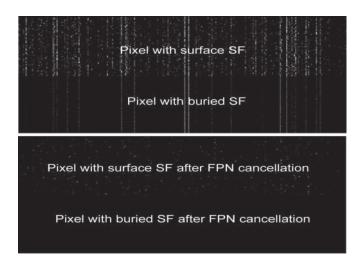

The measurement results from the prototype sensor were presented in [13]. A test image captured in the dark is shown in Fig. 11. The test image was measured in the dark with an analog sensor gain of ten, at 30 ft/s and 33.3-ms integration time and with a 12-b board-level ADC. The CDS interval is 1.5  $\mu$ s, and the charge transfer period is 1  $\mu$ s. The upper part of the figure

Fig. 11. Test image in the dark,  $10 \times$  sensor gain [13].

Fig. 12. Histograms of the dark random noise for BSF and SSF pixels in the new test sensor.

shows the raw data, while the lower part shows the data after a digital column-fixed-pattern noise cancellation. About 0.5% of the pixels in the SSF array were observed to be RTS pixels, compared to none in the BSF array.

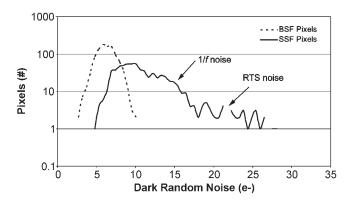

The results from the new BSF pixels with optimized row selector are shown in Fig. 12. The transistor dimension for both BSFs and SSFs are the same in prototype and new test sensors, i.e.,  $W/L=0.42/0.5~\mu m$ . The measurements were processed with an analog sensor gain of 10, at 17 ft/s and with a 12-b board-level ADC. The CDS interval is 1.5  $\mu$ s with the TX transistor grounded. The FD reset voltage of both the new BSF pixels with optimized row selector and the SSF pixels is 3.3 V. For the new BSF pixels with optimized row selector (10- $\mu$ m pixel pitch), the fill factor is 33%, and the conversion gain is 41  $\mu$ V/e<sup>-</sup>.

The random noise of each pixel is obtained by calculating the standard deviation over 20 frames' outputs. The asymmetric distribution of the pixels around the peak of the SSF pixel curve indicates the dominance of the 1/f and RTS noises of the SSF [2]. Comparing with previous results [13], the same random noise improvement is still shown in the pixels with BSFs and optimized row selectors. The average dark random noise of the BSF pixels is about 5 e $^-$ , reduced around 50% comparing with the SSF pixels, and the noise histogram of the BSF pixels closely approximates a true Gaussian distrib-

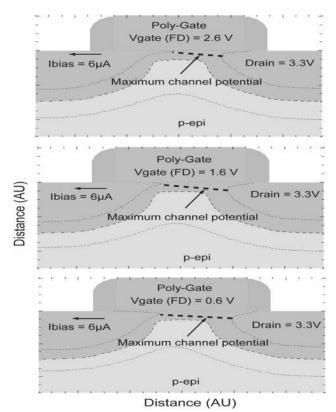

Fig. 13. Simulation of the depletion region and the channel location of a BSF with different gate bias.

ution with significantly reduced noise spread. Moreover, no hot pixel (high 1/f noise) or blinking pixel (RTS pixel) has been found in the 200 row  $\times$  150 column BSF pixel array of the new test sensor.

As shown in Fig. 13, the simulation results of the depletion region and the channel location change of a BSF pixel with varying FD voltages are presented. It can be seen that the FD reset voltage (gate bias) has strong influence on the potential distance and depletion region at the Si-SiO<sub>2</sub> interface. Reducing the gate bias helps to push the channel deeper; this extends the depletion region at the interface further toward the source side. This condition means that the total channel length will have more area working as a buried-channel mode rather than surface mode; in other words, it can be understood such that the total buried-channel length is increased by reducing the gate bias.

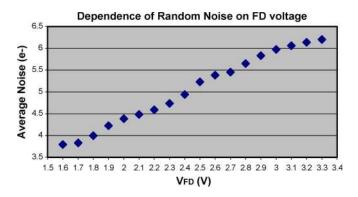

From the new test sensor, the measurement result of the average dark random noise as a function of different FD voltages is shown in Fig. 14. Apparently, the relationship between pixel random noise and SF channel depth is confirmed by the results. The channel is buried deeper by lower FD voltages; therefore, the measured random noise is smaller for lower FD voltages. However, a low FD voltage may introduce image lag because of the incomplete charge transfer.

# VI. CONCLUSION

A CIS with an in-pixel BSF and an optimized row selector has been presented. Compared with a conventional surfacemode SF design, the BSF can gain the following: 1) a reduction

Fig. 14. Dark random noise measurement with different FD voltages.

of more than 50% in dark random noise and improvement of noise spread; 2) a significant reduction of the RTS noise component; 3) a nearly 100% improvement in pixel output swing; and 4) an increase in the voltage gain of the in-pixel SF. Comparing with our previous work [13], the new designed BSF with an optimized row selector still shows the same attractive dark random noise performance and, moreover, is able to get rid of the tradeoff between the noise reduction and the improvement of the pixel output swing.

#### ACKNOWLEDGMENT

The authors would like to thank M. Sonder, P. Donegan, F. Feng, and E. Fox of DALSA Corporation for their contribution to the prototype sensor, B. Mheen for his contribution to the new test sensor, M. F. Snoeij for his contribution to the image test board, P. R. Rao for his contribution to the device simulation, and particularly, F. K. Chen, S. G. Wu, V. Hsu, and M. Li of TSMC for their support in modifying the process flow.

## REFERENCES

- [1] M. Cohen, F. Roy, D. Herault, Y. Cazaux, A. Gandolfi, J. P. Reynard, C. Cowache, E. Bruno, T. Girault, J. Vaillant, F. Barbier, Y. Sanchez, N. Hotellier, O. LeBorgne, C. Augier, A. Inard, T. Jagueneau, C. Zinck, J. Michailos, and E. Mazaleyrat, "Fully optimized Cu based process with dedicated cavity etch for 1.75 μm and 1.45 μm pixel pitch CMOS image sensors," in *IEDM Tech. Dig.*, Dec. 2006, pp. 127–130.

- [2] B. Pain, T. Cunningham, B. Hancock, C. Wrigley, and C. Sun, "Excess noise and dark current mechanisms in CMOS imagers," in Proc. IEEE Workshop CCDs, Adv. Image Sens., Karuizawa, Japan, Jun. 2005, pp. 145–148.

- [3] J. Y. Kim, S. I. Hwang, J. J. Lee, J. H. Ko, Y. Kim, J. C. Ahn, T. Asaba, and Y. H. Lee, "Characterization and improvement of random noise in 1/3.2" UXGA CMOS image sensor with 2.8 μm pixel using 0.13 μm-technology," in *Proc. IEEE Workshop CCDs*, *Adv. Image Sens.*, Karuizawa, Japan, Jun. 2005, pp. 149–152.

- [4] A. Lahav, D. Veinger, and A. Fenigstein, "Optimization of random telegraph noise non uniformity in a CMOS pixel with a pinnedphotodiode," in *Proc. Int. Image Sens. Workshop*, Ogunquit, ME, Jun. 2007, pp. 230–234.

- [5] K. Findlater, R. Henderson, D. Baxter, J. E. D. Hurwitz, L. Grant, Y. Cazaux, F. Roy, D. Herault, and Y. Marcellier, "SXGA pinned photodiode CMOS image sensor in 0.35 μm technology," in *Proc. ISSCC Dig. Tech. Papers*, 2003, pp. 218–219.

- [6] X. Wang, P. R. Rao, A. Mierop, and A. J. P. Theuwissen, "Random telegraph signal in CMOS image sensor pixels," in *IEDM Tech. Dig.*, Dec. 2006, pp. 115–118.

- [7] C. Leyris, F. Martinez, M. Valenza, A. Hoffmann, J. C. Vildeuil, and F. Roy, "Impact of random telegraph signal in CMOS image sensors for low-light levels," in *Proc. 32nd IEEE ESSCIRC*, Montreux, Switzerland, Sep. 2006, pp. 276–379.

- [8] M. F. Snoeij, A. P. van der Wel, A. J. P. Theuwissen, and J. H. Huijsing, "The effect of switched biasing on 1/f noise in CMOS imager front-ends," in *Proc. IEEE Workshop CCDs*, *Adv. Image Sens.*, Karuizawa, Japan, Jun. 2005, pp. 68–71.

- [9] C. Leyris, A. Hoffmann, M. Valenza, J. C. Vildeuil, and F. Roy, "Evolution of R.T.S source activities in saturation range in N-MOSFETs for different oxidation temperatures," in *Proc. 18th ICNF*, Aug. 2005, pp. 213–216.

- [10] X. Wang, "Noise in sub-micron CMOS image sensors," Ph.D. dissertation, Delft Univ. Technol., Delft, The Netherlands, 2008.

- [11] A. J. P. Theuwissen, Solid-State Imaging With Charge-Coupled Devices. Dordrecht, The Netherlands: Kluwer, 1995, pp. 40–42.

- [12] E. R. Fossum, "CMOS image sensors: Electronic camera-on-a-chip," IEEE Trans. Electron Devices, vol. 44, no. 10, pp. 1689–1698, Oct. 1997.

- [13] X. Wang, M. F. Snoeij, P. R. Rao, A. Mierop, and A. J. P. Theuwissen, "A CMOS image sensor with a buried-channel source follower," in *Proc. ISSCC Dig. Tech. Papers*, San Francisco, CA, Feb. 2008, pp. 62–63.

Yue Chen (S'08) received the B.Sc. degree in microelectronics from the Department of Physics, Nanjing University (NJU), Nanjing, China, in 2004 and, with Philips Semiconductor (currently named NXP) and Top Talent Scholarships sponsoring, the M.Sc.E.E. degree from the Department of Microelectronics, Faculty of EEMCS, Delft University of Technology (TU Delft), Delft, The Netherlands, in 2007, where he is currently working toward the Ph.D. degree in the Electronic Instrumentation Laboratory with Prof. A. J. P. Theuwissen on the subject of CMOS

image sensor research and development.

From June 2004 to 2005, he continued to work in the Jiangsu Province Key Laboratory of Advanced Photonic and Electronic Materials, NJU, as a Research Assistant, mainly in the research of diluted magnetic semiconductor materials. From June to August 2005, he took an Internship with the Institute of Microelectronics, NJU, for Verilog HDL digital circuit and system design.

Xinyang Wang (S'05–M'08) received the B.Sc. degree in electrical engineering from Zhejiang University, Hangzhou, China, in 2002, the M.Sc. degree in microelectronics system design from the University of Southampton, Southampton, U.K., in 2003, and the Ph.D. degree in electrical engineering from the Electronic Instrumentation Laboratory, Delft University of Technology (TU Delft), Delft, The Netherlands, in 2008, where he focused on pixel-level noise of CMOS image sensors with deep submicrometer CMOS process under the guidance of

Prof. A. J. P. Theuwissen.

In May 2008, he started to work as a Pixel Designer for custom CMOS image sensors with Cypress Semiconductor, Mechelen, Belgium. Since November 2008, he has been with CMOSIS NV, Antwerpen, Belgium, as an Image Sensor Specialist.

**Adri J. Mierop** received the B.Sc. and M.Sc. degrees in electrical engineering from Delft University of Technology (TU Delft), Delft, The Netherlands, in 1979 and 1986, respectively.

From 1987 to 1996, he worked on application, specification, and evaluation of CCD sensors in professional studio cameras with Broadcast Television Systems, Breda, The Netherlands. In 1997, he joined Philips Semiconductors, Eindhoven, The Netherlands, and, later, DALSA Semiconductors, Eindhoven, where he worked on the specification and

design of CMOS image sensors. For two days a week, he works with the group of Prof. A. J. P. Theuwissen with the Electronic Instrumentation Laboratory, TU Delft, on the subject of CMOS image sensors.

**Albert J. P. Theuwissen** (F'02) was born in Maaseik, Belgium, on December 20, 1954. He received the M.S. and Ph.D. degrees in electrical engineering from the Catholic University of Leuven, Leuven, Belgium, in 1977 and 1983, where his thesis work was based on the development of supporting hardware around a linear CCD image sensor and his dissertation was on the implementation of transparent conductive layers as gate material in the CCD technology.

From 1977 to 1983, he was with the ESAT Laboratory, Catholic University of Leuven, where his work focused on semiconductor technology for linear CCD image sensors. In 1983, he was a Member of the Scientific Staff with the Micro-Circuits Division, Philips Research Laboratories, Eindhoven, The Netherlands. Since that time, he has been involved in research of solid-state image sensing, which resulted in the project leadership of SDTV and HDTV imagers. In 1991, he became the Department Head of the Imaging Devices Division, including CCD as well as CMOS solid-state imaging activities. In March 2001, he was appointed as a Part-Time Professor with the Delft University of Technology, Delft, The Netherlands, where he teaches courses in solid-state imaging and coaches Ph.D. students in their research on CMOS image sensors. In April 2002, he was with DALSA Corporation as the company's Chief Technology Officer. In September 2004, he retired as CTO and became the Chief Scientist with DALSA Semiconductors. After he left DALSA in September 2007, he started his own company "Harvest Imaging," Bree, Belgium, focusing on consulting, training, teaching, and coaching in the field of solid-state imaging technology (www.harvestimaging.com). He cofounded (together with his peers E. Fossum and N. Teranishi) ImageSensors, Inc. (a Californian nonprofit public benefit company) to address the needs of the image sensor community (www.imagesensors.org). He is the author or coauthor of over 120 technical papers in the solid-state imaging field and issued several patents. In 1995, he authored the textbook *Solid-State Imaging With Charge-Coupled Devices*. This work is still considered as one of the main textbooks in the field of solid-state imaging. He is a member of the editorial board of the magazine *Photonics Spectra*.

Dr. Theuwissen is a member of SPIE. In 1988, 1989, 1995, and 1996, he was a member of the International Electron Devices Meeting paper selection committee. He was a Coeditor of the IEEE TRANSACTIONS ON ELECTRON DEVICES Special Issues on Solid-State Image Sensors for May 1991, October 1997, and January 2003, and of the IEEE MICRO Special Issue on Digital Imaging for November/December 1998. In 1998, he became an IEEE Distinguished Lecturer. He was the General Chairman of the IEEE International Workshop on Charge-Coupled Devices and Advanced Image Sensors in 1997 and 2003, and he will serve again as the Chairman of the International Image Sensor Workshop to be organized in 2009. He is a member of the Steering Committee of the aforementioned workshop and the Founder of the Walter Kosonocky Award, which highlights the best paper in the field of solid-state image sensors. For several years, he was a member of the technical committee of the European Solid-State Device Research Conference and of the European Solid-State Circuits Conference. Since 1999, he has been a member of the technical committee of the International Solid-State Circuits Conference, for which he was the Secretary, Vice-Chair, and Chair in the European ISSCC Committee. He is also a member of the overall ISSCC Executive Committee. He will be the Vice-Chair and Chair of the International Technical Program Committee for ISSCC 2009 and 2010, respectively. Recently, he was the recipient of the Fuji Gold Medal for his contributions to research, development, and education in the field of image capturing.