# A Comprehensive Analysis and Modeling of the Self-Powered Synchronous Switching Harvesting Circuit With Electronic Breakers

Weiqun Liu, Adrien Badel, Fabien Formosa, Qiao Zhu, Caiyou Zhao,

Guang-Di Hu

# ▶ To cite this version:

Weiqun Liu, Adrien Badel, Fabien Formosa, Qiao Zhu, Caiyou Zhao, et al.. A Comprehensive Analysis and Modeling of the Self-Powered Synchronous Switching Harvesting Circuit With Electronic Breakers. IEEE Transactions on Industrial Electronics, Institute of Electrical and Electronics Engineers, 2018, 65 (5), pp.3899 - 3909. 10.1109/tie.2017.2762640. hal-01901519

# HAL Id: hal-01901519 https://hal.archives-ouvertes.fr/hal-01901519

Submitted on 23 Oct 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A Comprehensive Analysis and Modeling of the Self-powered Synchronous Switching Harvesting Circuit with Electronic Breakers

Weiqun Liu, Adrien Badel, Fabien Formosa, Qiao Zhu, Caiyou Zhao and Guangdi Hu

Abstract-Self-powered realization for synchronous switching circuits is a hot spot for piezoelectric vibration energy harvesting. As a well-known approach, the electronic breaker is widely used for its simplicity and reliability. It plays an important role on the performance of the piezoelectric generator by affecting the available open-circuit voltage and the switching phase lag. In this paper, a comprehensive model is developed for improved performance analysis with missed factors included in comparison with previous investigations. The combined influence of the envelope resistor and the capacitor on both the phase lag and the open-circuit voltage is newly considered while the additional phase lag effect induced by charging the switch parasitic capacitance with the envelope capacitance is supplemented. Experiments and simulations validate the proposed model with better accuracy and the results show that these supplemented factors are important to the generator performance, especially for the micro-power energy harvesting with small piezoelectric capacitance or displacement magnitude. Moreover, more detailed design guidelines are deduced from the proposed model.

*Index Terms*— Piezoelectric Energy harvesting, Self-powered synchronous switching circuit; Electronic breaker.

## I. INTRODUCTION

T HE rapid development of micro power circuits promotes new possibilities of scavenging energy from environment

Manuscript received May 23, 2017; revised Sep. 10, 2017; accepted Oct. 3, 2017. Corresponding author: Weiqun Liu.

This work was supported in part by the National Natural Science Foundation of China under Grant 51505395, China Postdoctoral Science Foundation under Grant 2017T100709 and 2016M600747 and the Fundamental Research Funds for the Central Universities under Grant 2682017CX26 and 2682017CY05.

Weiqun Liu, Qiao Zhu and Guangdi Hu are with the School of Mechanical School, Southwest Jiaotong University, Chengdu, 610031, China. (e-mail: <u>weiqunliu@home.swjtu.edu.cn</u>, <u>zhuqiao@home.swjtu.edu.cn</u> and <u>ghu@home.swjtu.edu.cn</u>). Caiyou Zhao is with the School of Civil Engineering, Southwest Jiaotong University, Chengdu, 610031, China. (e-mail: <u>zcy848279@163.com</u>)

Adrien Badel and Fabien Formosa are with the laboratory SYMME, Université Savoie Mont Blanc, Annecy le Vieux, 74944, France. (e-mail: <u>adrien.badel@univ-smb.fr</u> and <u>fabien.formosa@univ-smb.fr</u>)

vibrations, leading to the advancement of wireless sensor network (WSN) of battery free [1]. Piezoelectric generator is one of the promising techniques that can scavenge energy from ambient vibrations. Beside the improvement on the mechanical structure to increase power density [2] or operation bandwidth [3-4], the study of electronic interface circuits is another important subject. For the purpose of regulating the alternative current (AC) to direct current (DC) from harvested electricity, the standard circuit composed of a rectifier and a capacitor was firstly proposed [5]. However, the energy return phenomenon that part of the energy without being extracted goes back to the mechanical system [6] makes its performance not good in low electromechanical coupling cases [7]. To increase the harvested power, many synchronous switching harvesting techniques were developed, for instance, synchronized switching harvesting on an inductor (SSHI) [8-10] and synchronous electric charge extraction (SECE) [11]. The advantages of performance enhancement in low electromechanical coupling cases and low load dependence were observed for these circuits. Further improvements on SSHI such as double synchronized switch harvesting (DSSH) [12], SSHI with magnetic rectifier (SSHI-MR) [13] etc. or on SECE such as optimized SECE (OSECE) [14], tunable SECE [15] etc. were proposed with different features as well.

For these synchronous switching circuits, the self-powered realization remains a hot topic. A variety of approaches have been studied, including electronic breakers [16-18], mechanical switches [19-21], velocity control [22] or integrated circuits [23-25] etc. Among them, the electronic breaker composed of an envelope and a comparator receives great interests due to its simplicity and reliability. It is firstly proposed for SSHI [16] and subsequently extended for other synchronous switching circuits [18]. In the self-powered switching circuits with electronic breakers, the switches, which are in fact powered by the piezoelectric source, automatically take actions to invert the piezoelectric voltage based on the information from the peak detectors that the maxima or minima are attained. Therefore, the harvested power is strongly related to the available open-circuit voltage magnitude and the phase lag between the switching actions and the corresponding piezoelectric extrema in the self-powered circuits [17].

Lallart and Guyomar conducted a primary analysis by including the voltage drop on the diode and the transistor [16]. Nevertheless, other components in the circuit were not accounted and the phase lag was assumed to be constant. Liang and Liao presented an improved analysis which contained the influence of the envelope capacitor and the leakage resistance of the piezoelectric element [17]. The phase lag induced by the diode and the transistor in the electronic breaker was analyzed as well. The design and optimization of the self-powered synchronous switching harvesting circuits relies on the accurate model. However, the envelope resistor and capacitor's influence is not well analyzed in existed models. In particular, the switch's parasitic capacitance and turn-on threshold are not considered either. In this paper, a comprehensive modeling and analysis taking these two factors into consideration are proposed. Investigations show that, the envelope resistor and capacitance affects the switching phase delay and the generator's open-circuit voltage while considerable additional phase lag is introduced for charging the switch's parasitic capacitance to turn on the switch. The harvested power is then greatly affected, especially for a piezoelectric generator with a small intrinsic capacitance which is usual for micro-power energy harvesting, i.e., MEMS generators. With the proposed model, better understanding and more precise suggestions on the design of the synchronous harvesting circuit can be found and more accurate performance evaluation can be performed. For instance, the performance degeneration observed with large envelope resistors or small envelope capacitances (see Fig. 9 in [17]) can be well understood, whereas it was not explained by the previous models [16-18].

This paper is organized as follows. Section 2 presents the introduction on the principle and operation of the OSECE and its self-powered realization with the electronic breaker. The Self-powered OSECE (SP-OSECE) circuit is selected here due to the easy feasibility of the self-powered circuit and low load dependence [14]. It thus facilitates the discussion by choosing a constant load without affecting the generality. Section 3 introduces the detailed investigations about the self-powered circuit based on electronic breakers. An improved model is then proposed to study the performance by a thorough analysis on the phase lag and the open circuit voltage as a function of the aforementioned parameters. Then it is validated by experiment and simulation with further discussions presented in section 4. Based on the proposed model, further discussions on the circuit design are performed with guidelines concluded in section 5.

#### II. PRINCIPLE AND CIRCUIT

### A. OSECE circuit

For a sinusoidal excitation  $u=u_M sin\omega t$ , the short-circuit current from the piezoelectric generator is

$$i_{ea} = \alpha \dot{u} = \alpha u_{M} \omega \cos \omega t \tag{1}$$

according to the piezoelectric constitution equation. Here,  $\alpha$  is the force-factor of the piezoelectric generator and u is the displacement. As a result, the piezoelectric element can be modeled as a current source in parallel with an intrinsic capacitance  $C_0$  and a leak resistor  $R_0$ . For the ideal case of no dielectric loss ( $R_0=\infty$ ), the open circuit piezoelectric voltage of the piezoelectric element is expressed as

$$V_p = \frac{1}{C_0} \int i_{eq} dt = \frac{\alpha u}{C_0}$$

(2)

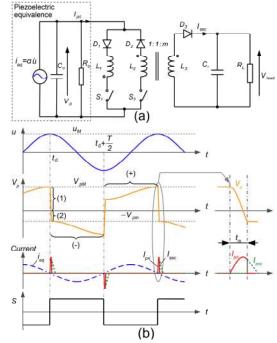

Fig. 1 presents the OSECE approach and the corresponding typical waveforms. In this approach, a fly-back transformer

composed of three windings  $L_1$ ,  $L_2$  and  $L_3$  is used with a 1:1:m turn ratio. Two switches  $S_1$  and  $S_2$  are in series with  $L_1$  and  $L_2$ respectively at the primary side while  $L_3$  is connected to the energy storage element  $C_r$  and the load  $R_L$  at the secondary side.

Fig. 1. (a) OSECE approach; (b) Typical waveforms.

The operation principle, detailed in [14], is briefly explained as follows. The switch signal S is applied to two switches at the same time while  $S_1$  and  $S_2$  are closed for positive and negative driving signal respectively. At the beginning, with  $S_1$  opened and  $S_2$  closed, the piezoelectric element is in the open-circuit status due to the diode  $D_2$ . The piezoelectric voltage  $V_p$ increases with the displacement from  $-u_M$  to  $u_M$ .  $S_1$  is then closed and  $S_2$  is opened, leading a transient LC oscillation which is further divided into two processes (1) and (2) in Fig. 1. At the end of the process (1) (a quarter of LC oscillation period), most of the electric energy is stored in the transformer without going to the load because the voltage on  $L_3$  is negative and the secondary side is blocked by  $D_3$ . At this moment, the current  $I_{pri}$  is maximum while  $V_p$  equals zero. After that, the circuit enters process (2).  $C_0$  is charged by  $L_1$  along the reversed direction. As soon as  $V_p = -V_{pm} = (V_{load} + V_D)/m$ , the secondary side is conducted and the remaining energy on the transformer is transferred to the load in the form of current  $I_{sec}$ . Next, the circuit enters the half period denoted (-) in which  $V_p$  decreases with the displacement towards the negative peak with similar operations.

For each switching, the energy transferred to load is:

Λ

$$E = C_0 (V_{pM}^2 - V_{pm}^2) \eta /2$$

(3)

in which the efficiency  $\eta$  is determined by the load and the quality factor related to the dissipative components including the transformer, the switches, the diodes etc. [18] and we have

$$V_{pM} = V_{pm} + \frac{1}{C_0} \int_{-u_M}^{u_M} \alpha \dot{u} du = \frac{V_{load} + V_D}{m} + \frac{2\alpha u_M}{C_0}$$

(4)

Then the transferred power is

$$P_{h} = \omega \Delta E / \pi = \eta f \alpha u_{M} (V_{load} / m + \alpha u_{M} / C_{0})$$

(5)

where  $f=\omega/(2\pi)$ . Since the voltage is inversed at each displacement peak as shown in Fig. 1 (b), the piezoelectric voltage has the same sign as  $i_{eq}$ . Therefore, the output power converted from the vibration by the piezoelectric generator is always positive. It hints that the produced electric energy is completely extracted and not back to the mechanical dynamic system. The inverted voltage after switching is used as a bias for subsequent conversion from mechanical to electrical energy in the generator so that the performance in low coupling cases can be improved.

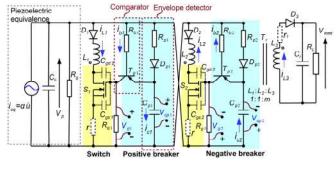

Fig. 2. SP-OSECE approach.

#### B. Self-powered realization with electronic breakers

In order to implement the OSECE approach for the fully self-powered purpose, the electronic breaker firstly proposed for SSHI in [16] to produce the switching signal is applied to the OSECE circuit as well. The corresponding circuit realization is shown in Fig. 2. Two identical electronic breakers which contain an envelope detector  $(R_{pi}, D_{pi}, C_{pi})$  and a comparator  $T_{pi}$  are used for the positive and negative maxima respectively. The MOSFETs highlighted in the yellow box are used as the switches with the parasitic capacitors  $(C_{gsi}, C_{gdi})$ plotted in dashed lines. Considering that the diode's parasitic capacitance is in the pF order and the voltage across the diode is small, it is neglected in the circuit. Different from the usual series resistor to suppress the possible MOSFET gate ringing, two parallel gate resistors  $R_{gi}$  are used in consideration of discharging the gate charge in order to turn off the MOSFET before the turning on of the other switch. Therefore, the simultaneously conducting of the two switches can be avoided so as to ensure the proper operation of the circuit. Moreover, the neutralized charge can be decreased correspondingly, which is favorable to the performance. Notably, a frictional series resistor r is added at the primary side to account for the parasitic loss of the switches (conducting resistor  $R_{ds-on}$ ), the diodes (voltage drop  $V_D$ ) and the transformer (coil resistance and magnetic loss). Meanwhile,  $r_1$  is added for the loss at the secondary side from the transformer and the diode. The modeling of the transformer is difficult due to the strong nonlinearity. However, in our case, the transformer is assumed to work in the non-saturation region only, thus a simple model can be used with magnetic losses included by r and  $r_1$  as well [26] while the parasitic capacitance is neglected due to the low frequency application. It is reminded that r and  $r_1$  are used only

for modeling the losses of circuit, not real components.

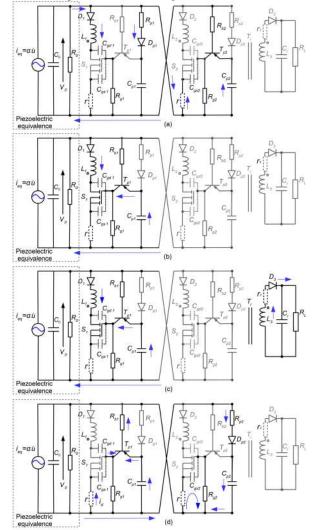

According to the working principle introduced before,  $S_1$  and  $S_2$  need to be closed and opened alternatively at the proper displacement extrema. Since the piezoelectric is in open-circuit status except during the inversion process, the breaker detects the voltage peak instead of the displacement extrema by comparing the piezoelectric voltage with the preserved peak in the envelope detector. Due to the similarity, only a half vibration period is considered here while similar results are expected for the other half period. For elaborating on the working process of the self-powered circuit, we can further divide the half vibration period into four phases as shown in Fig. 3. For each phase, the current conducting branches are underlined in black with the current direction indicated by the arrows, while the others are plotted in grey. With the variable symbols defined in Fig. 2, the simulated waveforms by LTSpice© are also presented in Fig. 4 and Fig. 5. As a reference, Fig. 4 (b) plots the experimental and simulated waveforms together, which show good consistence.

Fig. 3. Four phases of SP-OSECE approach in a half vibration period: (a) Natural charging; (b) Voltage inversion; (c) Energy transfer; (d) Charge neutralization.

Phase 1: Natural charging. The current from  $i_{eq}$  charges  $C_0$

towards the maximum  $V_{pM}$  as shown in Fig. 3 (a). The envelope capacitor  $C_{p1}$  is also charged through  $R_{p1}$  and  $D_1$  while  $C_{p2}$  and  $C_{gs2}$  are charged through  $T_{P2}$  and the base resistor  $R_{b2}$ . Due to the existence of  $R_{p1}$  and  $D_1$ , the peak value of  $V_{cp1}$  appears later and smaller than  $V_{pM}$  with a difference of  $\Delta V_1$  shown in Fig. 4. Afterwards, the peak value of  $V_{cp1}$  is preserved on  $C_{p1}$  while  $V_p$ and  $V_{cp2}$  start to decline until  $V_{pM}$ - $\Delta V_1$ - $V_{BE}$  and phase 2 begins. In this phase, the MOSFET parasitic capacitors ( $C_{gs1}$ ,  $C_{gd1}$ ) and the gate resistor  $R_{gi}$  also bypass a little part of the current  $i_{eq}$ .

Fig. 4. (a) Simulated waveforms of the SP-OSECE circuit; (b) Comparison of experimental and simulated waveforms Solid lines: experimental; Dashed lines: simulated.

Fig. 5. Zoomed waveforms around the inversion instant.

Phase 2: Voltage inversion. As  $V_p$  declines to  $V_{pM}-\Delta V_1-V_{BE}$ ( $V_{BE}$  denotes the transistor base-emitter threshold voltage), the transistor  $T_{p1}$  starts to conduct and  $C_{gs1}$  is charged by  $C_{p1}$ . A voltage drop  $\Delta V_2$  on  $C_{p1}$  is found in Fig. 4, which hints the charge transfer from  $C_{p1}$  to  $C_{gs1}$ , also indicated by the collector current  $i_{c1}$  of  $T_{p1}$  in Fig. 5. As the gate voltage  $V_{g1}$  reaches the MOSFET threshold  $V_{th}$ , the switch  $S_1$  turns on and  $C_0$  starts a quick discharge from the voltage  $V_{pM}-\Delta V_1-\Delta V_2-V_{BE}$  through the inductive path  $L_1$  as indicated by the current  $i_{L1}$  in Fig. 5. Notably, the MOSFET switch undergoes a transition from the linear region (large  $R_{ds-on}$ ) to the saturation region (small  $R_{ds-on}$ ), which brings losses in this phase. However, the transition is short since the charging speed gets faster after the voltage inversion begins due to the rapidly increased voltage difference between  $V_{cp1}$  ( $T_{p1}$ 's emitter) and  $V_p$  ( $T_{p1}$ 's base). Considering the difficulty to detail the variation of  $R_{ds-on}$ , the loss is roughly covered by the friction resistance r.

Phase 3: Energy transfer. When the piezoelectric voltage is reversely charged to  $-(V_{load}+V_D)/m$  by  $i_{L1}$ , the voltage on  $L_3$  is larger than  $V_{load}+V_D$  so that it begins to charge  $C_r$  with  $i_{L3}$  as shown in Fig. 4 and Fig. 5. Owing to the large value of  $C_r$ ,  $V_{load}$ is almost unvaried so that most of the energy in the transformer goes to the load. To be noted,  $i_{L1}$  does not immediately decreases to zero due to the non-ideal transformer and the series resistance r in the circuit. As a result, the piezoelectric voltage continues to decrease until  $-V_b$  as seen in Fig. 4, slighly lower than the ideal case  $-(V_{load}+V_D)/m$  in Fig. 1. When  $i_{L1}$  decrease to zero,  $S_1$  turns off and the inductive circuit is blocked by  $D_1$ .

Phase 4: Charge neutralization. After  $V_p$  reaches the local negative extreme  $-V_b$ , some charges are still preserved on  $C_{p1}$ ,  $C_{p2}$  and  $C_{gs1}$  with positive voltage  $V_{cp1}$ ,  $V_{cp2}$  and  $V_{g1}$  as shown in Fig. 4 and Fig. 5. Consequently, two current paths to balance the voltage between  $C_{p1}$ ,  $C_{p2}$ ,  $C_{gs1}$  and  $C_0$  are established: (1)  $C_{p1}(C_{gs1}) \rightarrow T_{p1}$ 's emitter (collector)  $\rightarrow T_{p1}$ 's base  $\rightarrow R_{b1} \rightarrow C_0$ and (2)  $C_{p2} \rightarrow C_0 \rightarrow R_{p2} \rightarrow D_2$ . The waveform of  $i_{c1}$  (current from  $C_{p1}$ ,  $i_{c2}$  (current from  $C_{p2}$ ) and  $i_{b1}$  (base current of  $T_{P1}$ ) are plotted in Fig. 5.  $i_{b1}$  has a larger value than  $i_{c1}$  due to the current from  $C_{gs1}$  flowing through the collector. By observing Fig. 4 and Fig. 5, it can be found that the RC time constant for  $C_{gs1}$ ,  $C_{p1}$  and  $R_{b1}$  is small so that  $V_{cp1}$  gets close to  $V_p$  shortly while the RC time constant for  $R_{p2}$  and  $C_{p2}$  is relatively larger so that more time is spent for  $V_{cp2}$  to get close to  $V_p$ . The charge neutralization leads to the piezoelectric voltage retreat towards zero until a new local extreme  $-V_{pm}$  as seen in Fig. 5. It is worthy of note that the use of a series resistance  $R_{p2}$  makes  $V_{cp2}$ changes more slowly than  $V_p$  so that the circuit will not trigger the voltage inversion immediately at the negative side. In particular, it helps to reduce the misjudgments about the maximum or minimum that could be caused by the piezoelectric voltage noise induced by high-frequency environmental vibration or switching operation. Moreover, the reversely charged  $C_{gs2}$  in the natural charging phase starts to discharge through  $R_{g2}$  until zero so that it is easy to be charged by  $C_{p2}$  to the turn-on threshold of  $S_2$  with less charge needed.

By carefully observing the circuit and the waveforms in Figs. 3-5, some important facts can be found:

(1) The envelope detectors  $(R_{pi}, D_{pi}, C_{pi})$  which are connected in parallel to the piezoelectric element work as a load beside the leak resistance  $R_0$  and affects the original system bypassing the current out from the source  $i_{eq}$ , leading to the magnitude decrease of the voltage in the natural charging phase. The charge neutralization phase after the inversion consumes a part of the charges on the piezoelectric element. It will then also decrease the available piezoelectric voltage peak  $V_{pM}$ .

(2) Due to the voltage drop on  $R_{pi}$  and  $D_{pi}$ , the detected peaks on  $C_{pi}$  are lower than the real peaks  $V_{pM}$  with the difference of  $\Delta V_1$ . In addition, there exists a phase lag between the detected peaks to the real peaks. (3) In order to turn on the switches, the piezoelectric voltage  $|V_p|$  is required to be lower than the preserved peak on  $C_{pi}$  in order to make  $T_{pi}$  conduct, thus  $C_{pi}$  can charge  $C_{gsi}$ , making  $|V_{gi}|$  larger than the threshold  $V_{th}$  required to switch on the MOSFET. A significantly phase lag is introduced by this process as seen in Fig. 4. As a result, the voltage inversion happens much later than the ideal case corresponding to the peak piezoelectric voltage. Moreover, it is worthy of note that a minimum requirement on  $V_{cpi}$ 's magnitude  $(=V_{pM}-\Delta V_1)$  exists so that  $V_{gi}$  are greater than  $V_{th}$  after the final balance between  $C_{pi}$  and  $C_{gsi}$ . The corresponding open-circuit piezoelectric voltage magnitude  $V_{pM}$  to trigger the switching action and let SP-OSECE work properly is called the starting voltage.

With the displacement magnitude  $u_M$  given,  $i_{eq}$  is fixed. The SP-OSECE circuit's harvested power is mainly related to the open-circuit voltage, the switching phase lag and the circuit quality factor for the selected  $R_L$ . Considering that the quality factor is mainly determined by the selected components, few efforts can be done except using highly-efficient components to enhance the quality factor as much as possible.

Therefore, the open-circuit voltage and the phase lag induced by the SP-OSECE circuit impose more critical influence on the harvested power. The studies, in which the influence of the envelop resistance  $R_{pi}$  is assumed to be negligible, have been performed for SP-SSHI by Liang et al. [17] and for SP-OSCECE by Wu et al. [18] based on the first fact. However, to reject the noises from environmental vibrations or switching operations,  $R_{pi}$  is usually selected to be relatively large. More important, the studies [17-18] on the phase lag only considered the voltage drop of the diode and the transistor while the influence of the envelop RC circuit and the charging process of  $C_{gsi}$  is probably more relevant as implied by the waveforms in Fig. 4 and Fig 5. Therefore, a thorough analysis taking all the facts into consideration is expected and performed in this study.

#### III. ANALYSIS

# A. Open-circuit Voltage

Without any circuit, the open-circuit voltage magnitude of the piezoelectric equivalence can be written as:

$$V_{oc,org} = \frac{\alpha u_M \omega R_0}{\sqrt{1 + \omega^2 R_0^2 C_0^2}} \text{ and } \varphi_{org} = \tan^{-1} \frac{1}{\omega R_0 C_0}$$

(6)

The leak resistance  $R_0$  leads to a magnitude decrease compared with eq. (2) and a phase difference between  $V_p$  and u. As the SP-OSECE circuit is applied, the induced open-circuit voltage variation can be analyzed by observing the natural charging phase in Fig. 3 (a). By neglecting the voltage drop on diodes, transistors and inductors and removing the non-conducting branches, the SP-OSECE circuit can be viewed as a parallel connected *RC* network including  $R_{p1}$ ,  $C_{p1}$ ,  $C_{gd1}$ ,  $C_{gs1}$ ,  $C_{gs2}$ ,  $C_{p2}$ ,  $R_{b2}$ ,  $R_{g1}$  and  $R_{g2}$ . Considering the large value of  $R_{gi}$  and the small values of  $C_{gd1}$  and  $C_{gs1}$ , the RC network can be further simplified by excluding these components. It yields:

$$i_{eq} = C_0 \frac{dV_p}{dt} + \frac{V_p}{R_0} + C_{p1} \frac{dV_{cp1}}{dt} + (C_{p2} + C_{gs2}) \frac{dV_{cp2}}{dt}$$

(7)

$$C_{p1} \frac{dV_{cp1}}{dt} = \frac{V_p - V_{cp1}}{R_{p1}}$$

(8)

$$(C_{p2} + C_{gs2}) \frac{dV_{cp2}}{dt} = \frac{V_p - V_{cp2}}{R_b}$$

(9)

(10)

Here, the voltage  $V_{g2}$  is thought to be the same as  $V_{cp2}$  by neglecting the voltage drop on  $T_{p1}$ . Then the open-circuit voltage can be obtained by considering the first natural charging phase at the instant where the SP-OSECE circuit is connected to the piezoelectric element with zero initial conditions for  $V_p$ ,  $V_{cp1}$  and  $V_{cp2}$ . Applying the Laplace transform leads to the open-circuit voltage  $V_{oc}$  and the phase difference  $\varphi$  between  $V_p$  and u as

where

$$\begin{split} V_{\text{Re}} &= \omega C_0 + \frac{\omega (C_{gs} + C_p)}{1 + \omega^2 (C_{gs} + C_p)^2 R_b^2} + \frac{\omega C_p}{\omega^2 C_p^2 R_p^2 + 1} \\ V_{\text{Im}} &= \frac{1}{R_0} + \frac{\omega^2 (C_{gs} + C_p)^2 R_b}{1 + \omega^2 (C_{gs} + C_p)^2 R_b^2} + \frac{\omega^2 C_p^2 R_p}{\omega^2 C_p^2 R_p^2 + 1} \end{split}$$

$V_{oc} = \frac{\alpha u_M \omega}{\sqrt{V_{\text{Re}}^2 + V_{\text{Im}}^2}}$  and  $\varphi = \tan^{-1} |\frac{V_{\text{Im}}}{V_{\text{Re}}}|$

Here, we use the circuit symmetry:  $C_{p1}=C_{p2}=C_p$ ,  $R_{p1}=R_{p2}=R_p$ ,  $R_{b1}=R_{b2}=R_b$  and  $C_{gs1}=C_{gs2}=C_{gs}$ . In comparison with eq. (6), the open-circuit voltage with SP-OSECE gets smaller and the induced phase difference  $\varphi$  is larger as well. In particular, with  $\omega(C_{gs}+C_p)R_b <<1$  and  $\omega C_pR_p <<1$ , we have:

$$V_{oc} \approx \frac{\alpha u_M \omega R_0}{\sqrt{1 + \omega^2 R_0^2 (C_0 + 2C_p + C_{gs})^2}}$$

(11)

It can be inferred that the SP-OSECE presents an equivalent effect of increasing  $C_0$  thus decreasing the electromechanical coefficient. With  $\alpha$  and  $u_M$  unvaried,  $V_{oc}$  decreases. Especially, the decreasing effect is more obvious in the case of small  $C_0$  if  $C_p$  is comparable. Notably,  $C_{gs}$  is taken into consideration in comparison with previous studies [17-18]. With  $R_{pi}$  and  $C_{pi}$ , the difference between  $V_{pM}$  and  $V_{cpi}$  is

$$\Delta V_1 = V_{oc} - \frac{V_{oc} - V_D}{\sqrt{1 + \omega^2 R_p^2 C_p^2}}$$

(12)

As it has been previously pointed out, for the purpose of switching on the MOSFET, the charge transferred from  $C_{pi}$  is required to charge  $C_{gsi}$  from zero to  $V_{th}$ . Then we must have:

$$C_{p}(V_{oc} - \Delta V_{1}) = \frac{C_{p}(\bar{V_{oc}} - V_{D})}{\sqrt{1 + \omega^{2}R_{p}^{2}C_{p}^{2}}} > C_{gs}V_{th} + C_{p}(V_{th} + V_{CE}) + \frac{V_{th}}{4R_{g}f}$$

(13)

in which  $V_{CE}$  is the emitter-collector voltage of  $T_{pi}$ . It can be noted that  $V_{CE}$  will be relatively large for small  $C_p$  with weak current corresponding to  $T_{pi}$ 's amplification region and close to the saturation voltage  $V_{CE\_sat}$  for larger  $C_p$  with relatively large current. The left side in eq. (13) stands for the charge stored on  $C_{pi}$  at the peak amplitude and the right side represents the minimum charge for turning on the MOSFET. The term  $V_{th}/(4R_gf)$  is the estimation of the leakage charge through  $R_{gi}$ assuming the critical condition that  $V_{gsi}$  is linearly increasing to  $V_{th}$  for a whole quarter of the vibration period T/4. It gives the SP-OSECE's starting condition:

$$V_{oc} > \sqrt{1 + \omega^2 R_p^2 C_p^2} \left( \frac{4f R_g (C_{gs} + C_p) + 1}{4f R_g C_p} V_{th} + V_{CE\_sat} \right) + V_D = V_{start}$$

(14)

In combination with eq. (11), it is found that  $C_p$  and  $C_{gs}$  will simultaneously affect both sides of eq. (14), the open circuit

voltage and the starting threshold  $V_{start}$ . Moreover, substituting eq. (10) into eq. (14) with the given MOSFETs and transistors, a minimum of displacement amplitude is obtained as the critical starting displacement  $u_{MC}$ , which is a function of  $C_p$ .

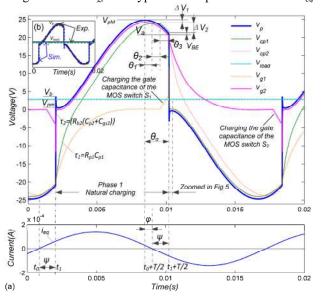

#### B. Phase lag analysis

Beside the open-circuit voltage, the phase lag induced by electronic breakers in the synchronous switching extracting circuits imposes critical influence on the performance of the generator. The phase lag refers to the delay of the switching action relative to the ideal position of the  $V_p$  extreme, which is unavoidable owing to the electronic breaker's principle. When analyzing the phase lag, previous researches [17-18] mainly focused on the voltage drop across the diode and the transistor  $V_D + V_{BE}$  corresponding to the conduction of the comparator transistor  $T_{pi}$ . In fact, the phase lag is induced by several different aspects. An improved analysis has been performed in this paper and the detailed information is seen in Fig. 4. The total phase lag  $\theta_a$  can be further divided into  $\theta_1$ ,  $\theta_2$  and  $\theta_3$ .  $\theta_1$ stands for the phase lag due to the envelope RC circuit  $(R_{pi}, C_{pi})$ and  $\theta_2$  represents the phase lag induced by the well-known voltage drop  $V_D + V_{BE}$ . Furthermore,  $\theta_1$  and  $\theta_2$  can be viewed together as the phase lag induced by the necessary voltage drop  $\Delta V_1 + V_{BE}$  to turn on  $T_{pi}$ . After the conduction of  $T_{pi}$ , the switch  $S_i$ is not turned on until  $V_{gi}$  is greater than  $V_{th}$ . The charging of  $C_{gsi}$ brings the envelope voltage  $V_{cpi}$  down simultaneously and induces the additional phase lag of  $\theta_3$  as seen in Fig. 4. This voltage drop is estimated as:

$$\Delta V_2 \approx C_{gs} V_{th} / C_p + V_{th} \theta_3 / (\omega R_g)$$

<sup>(15)</sup>

The second term stands for the leakage current on  $R_{gi}$  assuming that  $V_{gsi}$  is linearly increasing to  $V_{ih}$ . The total phase lag is

$$\theta_{a} = \cos^{-1}(1 - \frac{\Delta V_{1} + V_{BE}}{V_{oc}}) + \theta_{3} = \cos^{-1}(1 - \frac{\Delta V_{1} + V_{BE} + \Delta V_{2}}{V_{oc}})$$

(16)

Combining eq. (15) and eq. (16),  $\Delta V_2$  and  $\theta_a$  can be solved. It is interesting to find that large  $C_p$  will reduce  $\Delta V_2$  and diminish the phase lag induced by the  $C_{gs}$  charging, but it will lower  $V_{oc}$ and increase the phase lag at the meantime. Reversely, small  $C_p$ increases the phase lag by higher  $\Delta V_2$  but reduces the phase lag by obtaining larger  $V_{oc}$ . It implies a complex relationship between  $\theta_a$  and  $C_p$  and an optimal  $C_p$  can be found for obtaining a minimum phase lag using eq. (15) and eq. (16).

Using eq. (10) and eq. (16), the phase difference  $V_p$  and u is  $\psi = \theta_a \cdot \varphi$  (17)

## C. Efficiency

The energy transfer efficiency  $\eta$  is influenced by many various loss factors from the switches, diodes and the transformers etc. According to the operation principle,  $\eta$  is mainly related to the voltage inversion phase and the energy transfer phase, and it can be written as  $\eta = \eta_1 \eta_2$ .  $\eta_1$  is the efficiency of the voltage inversion process related to frictional resistance *r* from the diode, the transformer and the switches and  $\eta_2$  is efficiency of the transformer's secondary side with  $r_1$ for the transformer and the diode. According to analysis in [14], we have

$$V_b = V_a \cos \lambda e^{-\frac{\lambda}{2Q}} \approx \frac{V_{load} + V_D}{m}$$

(18)

for the voltage inversion process. Here,  $Q = (L_1/C_0)^{-1/2} r^{-1}$  is the

LC circuit quality factor to be determined with experimental identifications for  $L_1$ ,  $C_0$  and r while  $\lambda$  is the phase angle of the LC oscillation at the end of the voltage inversion. The corresponding current of the secondary side at this instant  $t_s$  is:

$$i_{L3(t_s)} = \frac{V_a \sin \lambda e^{-\frac{\pi}{2Q}}}{m} \sqrt{\frac{C_0}{L_1}}$$

(19)

Then the efficiency  $\eta_2$  can be written as:

$$\eta_2 = \frac{\int_{t_s}^{t_s + \tau} i_{L3} V_{load} dt}{\int_{t_s}^{t_s + \tau} i_{L3} (V_{load} + V_D) + i_{L3}^2 r_1 dt}$$

(20)

Here,  $\tau$  is the energy transfer duration. When  $i_{L3}$  can be assumed linearly decreasing to zero as implied in Fig. 5, namely,  $i_{L3} \approx i_{L3}(t_s)(t-t_s)/\tau$  for  $t_s \le t \le t_s + \tau$ , the efficiency can be simplified using eq. (18) and eq. (19):

$$\eta_2 \approx \frac{V_{load}}{V_{load} + V_D + \frac{2}{3}i_{L3(t_s)}r_1} \approx \frac{\kappa m^2 \cos \lambda}{m^2 \cos \lambda + \frac{2}{3} \sin \lambda \sqrt{\frac{C_0}{L_1}}}$$

(21)

in which  $\kappa = V_{load}/(V_{load}+V_D)$ . Considering the energy balance and using the efficiency definition, we have

$$\frac{1}{2}C_0(V_a^2 - V_b^2)\eta_1 = \frac{1}{2}L_3i_{L_3(t_s)}^2 = \frac{1}{2}mL_1i_{L_3(t_s)}^2 \qquad (22)$$

$$\frac{1}{2}\eta_2 L_3 i_{L_3(t_s)}^2 = \frac{V_{load}^2}{R_L} \approx \frac{(\kappa m V_b)^2}{R_L}$$

(23)

Given a  $\kappa$  (eg.,  $\kappa \approx 1$  for  $V_{load} \gg V_D$ ), we can calculate  $\lambda$ ,  $\eta_1$  and  $\eta_2$  using the equations (18), (22) and (23). Considering that  $\kappa$  is dependent on  $V_{load}$ , a trial value of  $\kappa$  can be firstly assumed for the calculation of  $\eta$  and  $V_{load}$ , then  $\kappa$  is updated with the calculated  $V_{load}$  and the recalculation of  $\eta$  and  $V_{load}$  is performed. The iteration stops with the satisfied accuracy reached. It is reminded that r and  $r_1$  varies with the working conditions in a certain range. However, for convenience, the estimated constant r and  $r_1$  values are often used as an approximation in most cases.

#### D. Power performance

The power performance of the SP-OSECE circuit is determined by the transferred energy at each switching event, which directly relies on the voltage before and after the inversion, namely,  $V_a$  and  $V_b$  in Fig. 4. In the corresponding half vibration period from  $t_1$  to  $t_1+T/2$ ,  $V_p$ ,  $V_{cp1}$  and  $V_{cp2}$  still satisfy eqs. (7) - (9) with the following initial status:

$V_p(t_1)=V_b$ ;  $V_{cp1}(t_1)\approx -V_a$ ;  $V_{cp2}(t_1)=V_{g2}(t_1)\approx -(V_{pM}-\Delta V_1)C_p/(C_p+C_{gs})$ which can be deduced from Figs. 4-5. Here, the voltage drop on  $D_1$  and  $R_{p1}$  is neglected for  $V_{cp1}$  while  $V_{cp2}(t_1)$  and  $V_{g2}(t_1)$  are obtained after charge balance with  $T_{p2}$ 's  $V_{CE}$  and the leaking effect of  $R_{g2}$  neglected. Moreover,  $V_b$  can be approximated as  $V_{load}/_m$  since the difference induced by the non-ideal transformer and diodes is small. As a result, the piezoelectric voltage  $V_p$  can be solved directly using eqs. (7) – (9) and the phase relationship is  $\omega t_1=\psi$  for  $i_{eq}$ . However, the analytical solution is complex and some simplifications are preferred.

It is observed that the charge neutralization caused by the non-zero initial status is composed of two transient processes of RC discharging corresponding to  $C_{p1}$  and  $C_{p2}+C_{gs}$ , leading to a

retreat towards zero for  $V_p$  as shown in Fig. 4. Generally, we have  $\tau_2 < \tau_1 < T/2$  and the charge neutralization ends in a short time. Then the retreated extreme  $V_{pm}$  is estimated as

$$V_{pm} \approx \frac{C_0 V_b - C_p (V_a + V_{pM} - \Delta V_1)}{C_0 + 2C_p + C_{gs}}$$

(24)

using the balance relationship for the total charge on these capacitors. After the charge neutralization,  $V_p$  can be assumed to follow the variations of  $V_{oc}$  from  $V_{pm}$  and we have

$$V_{p} \approx V_{pm} + V_{oc}(\cos\theta_{a} - \cos(\omega t + \varphi)) \quad (\psi \le \omega t \le \pi + \psi)$$

(25)

Using  $V_{b} \approx (V_{b,cd} + V_{D})/m$  it yields

$$V_{pM} = \frac{C_0 (V_{load} + V_D) / m - C_p (V_a - \Delta V_1) + (C_0 + 2C_p + C_{gs}) V_{oc} (1 + \cos\theta_a)}{C_0 + 3C_p + C_s} (26)$$

$$V_a = V_{pm} + 2V_{oc} \cos \theta_a \approx V_{pM} - \Delta V_1 - \Delta V_2 \qquad (27)$$

with  $V_{oc}$  given by eq. (10). We then have

$$V_{pm} = \frac{\alpha u_M \cos \varphi (1 + \cos \theta_a) + C_0 (V_{load} + V_D) / m + 2C_p \Delta V_1 + C_{gs} V_{th}}{C_0 + 4C_p + C_{gs}}$$

$$V_a = \frac{2\alpha u_M \cos\varphi \cos\theta_a + C_0 (V_{load} + V_D) / m - C_{gs} V_{th}}{C_0 + 4C_p + C_{gs}}$$

(28)

(29)

using eq. (11) and eq. (12). Therefore, according to eq. (5), the harvested power on the load can be written as

$P_{SP\_OSECE} \approx \eta f C_0 (V_a^2 - (V_{load} + V_D)^2 / m^2) \approx \eta f C_0 (V_a^2 - V_{load}^2 / m^2)$  (30) by neglecting  $V_D$  for the purpose of simplifying the calculation of  $V_a$  subsequently. It is logical that  $V_D << V_{load}$  and  $(V_{load}+V_D) << V_a$  are satisfied in the usual case. The ignoring of  $V_D$  will not affect the modeling accuracy. Considering  $P_{SP OSECE} = V_{load}^2 / R_L$  for energy balance, it yields

$$V_{a} \approx \frac{2(C_{0} + 2C_{P} + C_{gs})V_{oc}\cos\theta_{a} - C_{gs}V_{th}}{C_{0} + 4C_{P} + C_{gs} - C_{0}\sqrt{\frac{\eta f C_{0}R_{L}}{\eta f C_{0}R_{L} + m^{2}}}$$

(31)

$$P_{SP OSECE} = \eta f C_0 m^2 V_a^2 / (\eta f C_0 R_L + m^2)$$

(32)

Obviously, with the efficiency  $\eta$ , the load  $R_L$  and the piezoelectric capacitance  $C_0$  fixed, the harvested power is only related to  $V_a$ . Comparing the  $V_a$  expression of eq. (31) with  $V_{pM}$ of eq. (5) corresponding to the ideal piezoelectric voltage before the inversion, it is found that  $C_p$  and  $C_{gs}$  increases the equivalent capacitance of the piezoelectric element as implied by the denominators in these two equations. Especially,  $C_n$ plays a more important role with a multiplied factor of 4, which differs from previous results with a factor of 2 [18]. This is because the analysis here includes the influence of the charge neutralization of  $C_p$  and  $C_{gs}$ , which leads to the foreseeable decrease of the available value of  $V_a$ . More important, the effectively produced charge in the half vibration period decreases from  $\alpha u_M$  to  $\alpha u_M \cos \varphi \cos \theta_a$  due to the phase difference between the switching action and the displacement peak (corresponding to  $i_{ea}=0$ ). The factor  $\cos\varphi$  represents the phase difference between u and  $V_p$  due to  $R_0$  and the RC network of the SP-OSECE circuit while  $\cos \theta_a$  stands for the phase lag induced by  $\theta_1$  the RC phase delay  $(R_{pi}, C_{pi}), \theta_2$  the voltage drop on diodes and transistors, and  $\theta_3$  the switch turning on process. Moreover, the charge  $C_{gs}V_{th}$  required to switch on the MOSFET also has to be subtracted. As a result, the accumulated charge corresponding to the numerator in eq. (31) is much lower than the ideal case in eq. (5), leading to a smaller  $V_a$  as well.

From the analysis above, it is shown that  $R_{pi}$ ,  $C_{pi}$ ,  $R_{gi}$ ,  $V_{th}$  and  $C_{gsi}$  impose important effects on  $V_a$  and the harvested power. Notably,  $C_{gs}$  is always unfavorable to the performance by decreasing  $V_{oc}$  and increasing the phase lag  $\theta_a$  with  $V_{th}$  together, thus the MOSFET switches with small  $C_{gs}$  and  $V_{th}$  are preferred. Meanwhile, the leaking current on  $R_{gi}$  prolongs the turning-on time of the switches and increases  $\theta_a$  as well so that it should be large enough. Yet, it should however satisfy  $R_gC_{gs} < T/2$  so as to turn off the switch before the next inversion by discharging  $C_{gs}$  in half a period. Due to the more relevant effects, further investigations are focused on  $R_{pi}$ ,  $C_{pi}$ ,  $C_{gsi}$  and  $V_{th}$ .

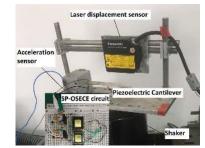

Fig. 6 Experimental set-up.

| Table I. Components and Parameters |             |                 |            |

|------------------------------------|-------------|-----------------|------------|

| Definition                         | Value       | Definition      | Value      |

| MOSFET $(S_i)$                     | IRFP240     | $R_{gi}$        | 1 MΩ       |

| Transistor $(T_{pi})$              | 2N5401      | $C_{gs}$        | 1.25 nF    |

| $Diodes(D_i, D_{pi})$              | BYV28-100   | $R_L$           | 100 kΩ     |

| Transformer $T_1$                  | WE750811290 | $V_{th}$        | 3.7 V      |

| $C_0$                              | 13.75nF     | $V_D$           | 0.5 V      |

| $R_0$                              | 5ΜΩ         | $V_{CE\_sat}$   | 0.3 V      |

| α                                  | 0.0003 N/V  | $r_1$           | $26\Omega$ |

| $R_{bi}$                           | 3.3 kΩ      | m               | 1          |

| f                                  | 61 Hz       | $V_{BE}$        | 0.2 V      |

| r                                  | 96Ω         | $L_1, L_2, L_3$ | 0.46 mH    |

#### IV. RESULTS

In order to validate the developed model, experimental tests are performed on a piezoelectric generator with the SP-OSECE circuit as shown in Fig. 6. The generator fixed on the shaker (2075E-HT, The Modal Shop<sup>©</sup>)) is composed of a steel cantilever (20mm×100mm×0.6mm) and a piezo ceramic patch (20mm×30mm×0.4mm). A signal generator (DG1032, Rigol©) drives the shaker through a power amplifier with a sinusoidal excitation of 61Hz around the generator's resonant frequency. A laser sensor (HL-C203BE, SUNX<sup>©</sup>) is used to measure the displacement whose amplitude is kept constant (tuning the driving signal amplitude). The used components and their characteristics are listed in Table I from experimental identifications or factory datasheet. Since the SP-OSECE circuit has low load dependence [15],  $R_L$  is fixed as 100k. Due to the difficulty of directly measuring r and  $r_1$ , it is estimated by best fitting the results with the model. The maximum efficiency  $\eta$  is measured to be 25.3% which is around the estimated efficiency 23.1% from the model, not so high for the elaborated circuit case in the tests. It is due to the high dissipation of the transformer, the diodes and the transistors in the low load

voltage cases. Meanwhile, the simulation is also performed with the LT-Spice<sup>©</sup> software with the Spice models obtained by the vendor for the semiconductor components. All the passive components are assumed to be ideal except a series resistance of  $r_1$  assumed for each transformer winding to represent the transformer's losses.

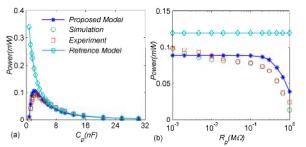

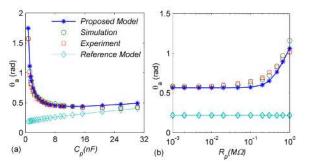

Multiple experiments and simulations have been carried out varying  $C_p$  from 0.75 nF to 30.2nF and  $R_p$  from 1 k $\Omega$  to 1 M $\Omega$  while  $u_M$  is kept constant at 1.25mm. Fig. 7 presents the harvested power. As seen in Fig. 7 (a), the power first increases then decreases when  $C_p$  is increasing. This trend is consistent with the fact that low  $C_p$  introduces a significant phase lag for charging  $C_{gs}$  as shown in Fig. 8 (a) while high  $C_p$  reduces the available  $V_{oc}$  and  $V_a$ . Thus, an optimal  $C_p$  exists for the SP-OSECE circuit performance. Regarding the influence of  $R_p$ , the performance decreases as  $R_p$  increases as indicated in Fig. 7 (b). It is attributed to the increasing phase delay of the envelope's RC circuit ( $R_{pi}$  and  $C_{pi}$ ) which is seen in Fig. 8 (b). Therefore,  $R_p$  always imposes adverse effects on the circuit performance and should be kept as small as possible while preserving the SP-OSECE robustness against noise. Good agreements are found between the analytical results from the proposed model and both experimental and simulated results, as shown in in Fig. 7 and Fig. 8. As a reference, the results using the model which does not consider the phase delay effects of the envelope's RC circuit and the charging of  $C_{gs}$  [17-18] are also plotted. The reference model can obviously not predict the performance of the circuit for small  $C_p$  and large  $R_p$  for which a significant deviation from experimental results is exhibited. Using the reference model, the phase delay estimation remains smaller than experiment as seen in Fig. 8, especially for small  $C_p$  and large  $R_p$ . Consequently, the power is always over optimistic in these cases as seen in Fig. 7.

Fig. 7 (a) Power versus different  $C_p$  with  $R_p$ =4.7 k; (b) Power versus different  $R_p$  with  $C_p$ =3.4 nF.

Fig. 8 Phase delay  $\theta_a$  versus different (a)  $C_p$  with  $R_p$ =4.7 k $\Omega$  and (b)  $R_p$  with  $C_p$ =3.4 nF.

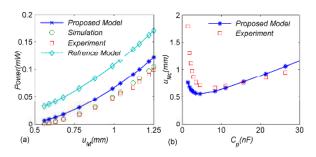

Fig. 9 (a) Power versus displacement magnitude  $u_M$ ; (a) Critical starting displacement  $u_{Mc}$  versus  $C_p$ .

Additional investigations have been done to validate the proposed model for different displacement magnitude  $u_M$  as shown in Fig. 9 (a) with  $C_p=3.4$ nF and  $R_p=4.7$ k $\Omega$ . Once again, good accordance is found between the proposed model and experiment while the reference model gives overestimated results. Slight difference is observed between the proposed model and experiment for small  $u_M$  of 0.6mm where the power is zero in experiment and simulation but nonzero according to the model. The reason is that the critical start displacement  $u_{Mc}$ corresponding to the start voltage  $V_{start}$  predicted by the model is higher than the measured one for small  $C_p$  as shown in Fig. 9 (b). It is induced by using  $V_{CE\_sat}$  instead of  $V_{CE}$  in eq. (14) when calculating  $V_{start}$  and  $u_{Mc}$ . For small  $C_p$  corresponding to  $T_{pi}$ 's amplification region ( $V_{CE} >> V_{CE \ sat}$ ), the calculated  $V_{start}$  will be smaller than the real one. For relatively large  $C_p$  corresponding to  $T_{pi}$ 's saturation region, the proposed model gives results close to experiment in Fig. 9(b).

# V. DISCUSSION

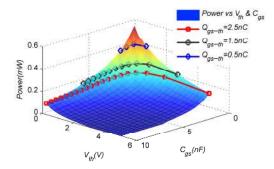

With the well validated model, further discussions can be performed to give better understanding on the design of SP-OSECE, especially about the critical MOSFET switch. Fig. 10 shows the SP-OSECE circuit's power with the MOSFET switches of varied  $V_{th}$  and  $C_{gs}$ . For each case, the optimal  $C_p$  is used to ensure the best performance while other parameters are listed in Table I. It shows that better results are obtained for the cases with smaller product values of  $Q_{gs-th} = V_{th}C_{gs}$  which means less phase delay and smaller optimal  $C_p$ , thus higher power. Furthermore, given a constant  $Q_{gs-th}$ , a trade-off between  $V_{th}$  and  $C_{gs}$  is found that the optimal performance is found for moderate  $C_{gs}$  and  $V_{th}$  as shown by the three marked lines corresponding to the  $Q_{gs-th}$  values of 0.5nC, 1.5nC, and 2.5nC respectively in Fig. 10. If the values of  $C_{gs}$  or  $V_{th}$  are over bias to one side, the power declines. It can be understood through eq. (15) and eq. (16) that the increase of either  $V_{th}$  or  $C_{gs}$  will enlarge the phase lag while  $V_{th}$  shows more influence. However,  $C_{gs}$  affects not only the phase lag but also  $V_a$  and  $V_{oc}$  directly. Consequently, over bias values of either  $V_{th}$  or  $C_{gs}$  decreases the power, and the circuit's best performance is obtained for a compromise configuration. Moreover, higher  $V_{th}$  imposes more obvious impact on the increase of the start voltage than  $C_{gs}$  does according to eq. (14).

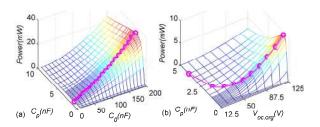

In order to detail  $C_p$ 's influence on the circuit performance, the harvested power by varying  $C_p$  and  $C_0$  respectively and keeping the original open circuit voltage  $V_{oc,org} = \alpha u_M / C_0$  (eq. (6)) constant is plotted in Fig. 11 (a) using the proposed model with the optimal  $C_p$  for each  $C_0$  highlighted with pink lines and circles. It is seen that the performance is strongly related to  $C_p$  for small  $C_0$ . As  $C_0$  increases, the performance does not change too much for a relatively large  $C_p$  range since  $C_p$  is much smaller than  $C_0$ . Moreover, the optimal  $C_p$  increases with  $C_0$  towards a constant as indicated by the pink line with circles. The explanation is that the phase lag from  $\theta_1$  the envelope's RC circuit and  $\theta_3$  the charging of  $C_{gs}$  becomes negligible while  $C_p$  affects the performance mainly by decreasing  $V_{oc}$ . Fig. 11 (b) shows the power for different  $C_p$  and  $V_{oc,org}$  with  $C_0$  constant. As  $V_{oc,org}$  increases, the optimal  $C_p$  decreases towards a constant as well. The results in Fig. 11 (a) and (b) hints that,  $C_p$  imposes critical effects on the SP-OSECE circuit by decreasing  $V_{oc}$  for high  $V_{oc,org}$  and  $C_0$  cases, and by introducing additional phase lag  $\theta_1$  and  $\theta_3$  for low  $V_{oc,org}$  and  $C_0$  cases.

Fig. 10 Power performance versus the MOSFET switches of varied  $V_{th}$  and  $C_{gs}$ .

Fig. 11 (a) Power versus  $C_0$  and  $C_p$  with  $V_{oc,org}$  constant as 37.5V; (b)  $V_{load}$  versus  $u_M$  and  $C_p$  with  $C_0$  constant as 13.75nF.

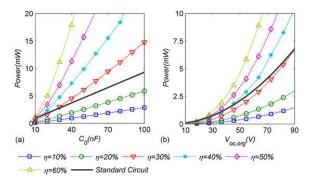

Fig. 12 Optimal power performance comparison between the SP-OSECE circuit and the standard circuit: (a) constant  $V_{oc,org}$  = 37.5V; (b) constant  $C_0$  = 13.75nF.

Comparative studies between the classic standard circuit and the SP-OSECE circuit are performed as well. Fig. 12 shows the optimal performance of the standard circuit and the SP-OSECE circuit for the constant  $V_{oc,org}$  case (Fig. 12 (a)) and for the constant  $C_0$  case (Fig. 12 (b)) respectively with both circuits well load-matched. The SP-OSECE circuit performance is plotted for six efficiency grades from 10% to 60%. It is seen that the efficiency  $\eta$  is necessary to be larger than a certain threshold so that the SP-OSECE circuit could outperform the standard circuit. As  $C_0$  or  $V_{oc,org}$  increases, this efficiency threshold decreases and the SP-OSECE circuit is inclined to achieve better performance easily. It reveals two facts: (1) when it is difficult to achieve the efficiency higher than the threshold, especially for the small  $C_0$  and  $V_{oc,org}$  cases, it might be better to use the standard circuit directly; (2) when the proper design for high efficiency by selecting the high quality components, such as the switches with small R<sub>ds-on</sub> and the transformer with low losses etc., the SP-OSECE circuit can obtain much better performance than the standard circuit, especially for large  $C_0$  or  $V_{or,org}$  cases.

Through the discussions above, it is found that the proposed model can be used as an effective tool for the SP-OSECE design. Some important design rules can be then concluded as follows: (1) adopting the MOSFET switch with small  $Q_{gs-th}$  and  $R_{ds-on}$  as possible while the trade-off between  $V_{th}$  and  $C_{gs}$  is to be considered with the start voltage covered as well; (2) selecting  $C_p$  around its optimal value; (3) enhancing efficiency by using proper components, such as high-quality transformer, low-loss diodes and so on. Besides, according to the former analysis, two addition points can be found: (1) using as small  $R_p$  as possible without risking misjudgment on the extreme; (2) using as large  $R_g$  as possible while ensuring the discharging requirement of  $C_{gs}$ ; Moreover, the criterion of using the SP-OSECE circuit or the standard circuit has to be judged by comparing the optimal power utilizing the proposed model.

#### VI. CONCLUSION

A comprehensive model has been developed in this paper by including the influence of the electronic breaker and the gate-source capacitance. The phase lag which plays an important role in the circuit performance has been thoroughly analyzed with these factors included. Experimental and simulated studies show that more accurate results can be obtained with this model in comparison with previous studied models. It is especially relevant for micro-power level energy harvesting of the µW order with small piezoelectric capacitance and displacement magnitude, since the phase lag introduced by the envelope detector of the electronic breaker in the form of RC phase delay and the necessary charging time for the gate-source capacitance become significant in this case. In particular, an optimal envelope capacitance exists for the determined piezoelectric capacitance and displacement magnitude. More precise guidelines on the design of the SP-OSECE circuit have been discussed and summarized while the comparison between the standard circuit and the SP-OSECE circuit has been done. It shows that, the SP-OSECE circuit outperforms the standard circuit only if the efficiency is higher than a certain threshold. This threshold decreases as the piezoelectric capacitance  $C_0$  and the original open-circuit voltage  $V_{oc,org}$  increases. Finally, it can be pointed out that, despite that the SP-OSECE circuit is used in this paper, the

analysis and the model are also applicable to other self-powered synchronous switching energy harvesting circuit using the electronic breaker approach.

#### REFERENCES

- Y. Zhang et al., "A batteryless 19 W MICS/ISM-band energy harvesting body sensor node soc for EXG applications," *IEEE J. Solid-State Circuits*, vol. 48, no. 1, pp. 199–213, 2013.

- [2] W. Li, S. He, and S. Yu, "Improving power density of a cantilever piezo- electric power harvester through a curved L-shaped proof mass," *IEEE Trans. Ind. Electron.*, vol. 57, no. 3, pp. 868–876, Mar. 2010.

- [3] W. Liu, C. Liu, B. Ren et al., "Bandwidth increasing mechanism by introducing a curve fixture to the cantilever generator," *Appl. Phys. Lett.*, vol. 109, pp. 43905, 2016.

- [4] L. Xiong, L. Tang, and B. R. Mace, "Internal resonance with commensurability induced by an auxiliary oscillator for broadband energy harvesting," *Appl. Phys. Lett.*, vol. 108, no. 20, p. 203901, 2016.

- [5] G. K. Ottman, H. F. Hofmann, A. C. Bhatt, and G. A. Lesieutre, "Adaptive piezoelectric energy harvesting circuit for wireless remote power supply," *IEEE Trans. Power Electron.*, vol. 17, no. 5, pp. 669–676, Sep. 2002.

- [6] J. R. Liang and W. H. Liao, "Piezoelectric energy harvesting and dissipation on structural damping," *J. Intell. Mater. Syst. Struct.*, vol. 20, no. 5, pp. 515–527, Mar. 2009.

- [7] E. Lefeuvre, A. Badel, C. Richard et al., "A comparison between several vibration-powered piezoelectric generators for standalone systems," *Sensors Actuators A Phys.*, vol. 126, no. 2, pp. 405–416, Feb. 2006.

- [8] D. Guyomar, A. Badel et al., "Toward Energy Harvesting Using Active Materials and Conversion Improvement by Nonlinear Processing," *IEEE Trans. Ultrason. Ferroelectr. Freq. Control*, vol. 52, no. 4, pp. 584–595, 2005.

- [9] I. C. Lien, Y. C. Shu, W. J. Wu, S. M. Shiu, and H. C. Lin, "Revisit of series-SSHI with comparisons to other interfacing circuits in piezoelectric energy harvesting," *Smart Mater. Struct.*, vol. 19, no. 12, p. 125009, Dec. 2010.

- [10] A. Badel, A. Benayad, E. Lefeuvre et al., "Single crystals and nonlinear process for outstanding vibration-powered electrical generators," *IEEE Trans. Ultrason. Ferroelectr. Freq. Control*, vol. 53, no. 4, pp. 673–683, 2006.

- [11] E. Lefeuvre, A. Badel, C. Richard and D. Guyomar, "Piezoelectric Energy Harvesting Device Optimization by Synchronous Electric Charge Extraction," *J. Intell. Mater. Syst. Struct.*, vol. 16, no. 10, pp. 865–876, Oct. 2005.

- [12] M. Lallart, L. Garbuio, L. Petit, C. Richard, and D. Guyomar, "Double synchronized switch harvesting (DSSH): A new energy harvesting scheme for efficient energy extraction," *IEEE Trans. Ultrason. Ferroelectr. Freq. Control*, vol. 55, no. 10, pp. 2119–2130, 2008.

- [13] L. Garbuio, M. Lallart, D. Guyomar et al., "Mechanical Energy Harvester With Ultralow Threshold Rectification Based on SSHI Nonlinear Technique," *IEEE Trans. Ind. Electron.*, vol. 56, no. 4, pp. 1048–1056, Apr. 2009.

- [14] Y. Wu, A. Badel, F. Formosa, W. Liu, and A. E. Agbossou, "Piezoelectric vibration energy harvesting by

optimized synchronous electric charge extraction," J. Intell. Mater. Syst. Struct., vol. 24, no. 12, pp. 1445–1458, 2012.

- [15] E. Lefeuvre, A. Badel, A. Brenes et al., "Analysis of piezoelectric energy harvesting system with tunable SECE interface," *Smart Mater. Struct.*, vol. 26, no. 3, 2017.

- [16] M. Lallart and D. Guyomar, "An optimized self-powered switching circuit for non-linear energy harvesting with low voltage output," *Smart Mater. Struct.*, vol. 17, no. 3, p. 35030, 2008.

- [17] J. Liang and W. Liao, "Improved design and analysis of self-powered synchronized switch interface circuit for piezoelectric energy harvesting systems," *IEEE Trans. Ind. Electron.*, vol. 59, no. 4, pp. 1950–1960, 2012.

- [18] Y. Wu, A. Badel, F. Formosa et al., "Self-powered optimized synchronous electric charge extraction circuit for piezoelectric energy harvesting," *J. Intell. Mater. Syst. Struct.*, vol. 25, no. 17, pp. 2165–2176, 2014.

- [19] Y. P. Wu, A. Badel, F. Formosa et al., "Nonlinear vibration energy harvesting device integrating mechanical stoppers used as synchronous mechanical switches," J. Intell. Mater. Syst. Struct., vol. 25, no. 14, pp. 1658, 2014.

- [20] W. Liu, F. Formosa, A. Badel et al., "Self-powered nonlinear harvesting circuit with a mechanical switch structure for a bistable generator with stoppers," *Sensors Actuators A Phys.*, vol. 216, pp. 106–115, Sep. 2014.

- [21] H. Liu, J. Liang, and C. Ge, "A mechatronic power boosting design for piezoelectric generators," *Appl. Phys. Lett.*, vol. 107, no. 14, p. 141902, 2015.

- [22] Y.-Y. Chen, D. Vasic, F. Costa, W.-J. Wu, and C.-K. Lee, "A self-powered switching circuit for piezoelectric energy harvesting with velocity control," *Eur. Phys. J. Appl. Phys.*, vol. 57, no. 3, p. 30903, Feb. 2012.

- [23] S. Lu and F. Boussaid, "A Highly Efficient P-SSHI Rectifier for Piezoelectric Energy Harvesting," *IEEE Trans. Power Electron.*, vol. 30, no. 10, pp. 5364, 2015.

- [24] S. Boisseau, P. Gasnier, M. Gallardo, and G. Despesse, "Self-starting power management circuits for piezoelectric and electret-based electrostatic mechanical energy harvesters," *J. Phys. Conf. Ser.*, vol. 476, p. 12080, 2013.

- [25] N. Kong and D. S. Ha, "Low-power design of a self-powered piezoelectric energy harvesting system with maximum power point tracking," *IEEE Trans. Power Electron.*, vol. 27, no. 5, pp. 2298–2308, 2012.

- [26] J. A. Martinez and B. A. Mork, "Transformer Modeling for Low- and Mid-Frequency Transients — A Review," *IEEE Trans. Power Deliv.*, vol. 20, no. 2, pp. 1625–1632, 2005.