Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000,

Digital Object Identifier 10.1109/ACCESS.2017.Doi Number

# A Comprehensive Review on Space Vector Modulation Techniques for Neutral Point Clamped Multi-Level Inverters

# VINOTH JAYAKUMAR<sup>1</sup>, BHARATIRAJA CHOKKALINGAM<sup>1</sup> (Senior Member, IEEE), JL MUNDA<sup>2</sup>

<sup>1</sup>Department of Electrical and Electronics Engineering, SRM Institute of Science and Technology, Chennai 603203 India

Corresponding author: Bharatiraja Chokkalingam (e-mail: bharatiraja@gmail.com).

**ABSTRACT** The Neutral Point Clamped (NPC) Multi-Level Inverters (MLI) have been ruling the power electronics industries for the past two decades. The Multi-Carrier Pulse Width Modulation (MCPWM) is common PWM techniques which are widely used in NPC-MLI applications. However, MCPWM is not having a good impact on the balancing of DC-link voltages, Common Mode Voltage (CMV) and limiting the Total Harmonics Distortion (THD). The Selective Harmonic Elimination (SHE) technique is introduced for reducing the THD, however all the switching angles should be maintained less than  $\pi/2$  to keep the eliminated harmonics at constant level which narrows down the modulation index range. Hence, in recent days Space Vector Modulation (SVM) technique is widely used in NPC-MLI, which gives better DC-link voltage balancing, self-neutral point balancing, near-zero CMV reduction, better-quality harmonics profile and switching loss minimization. Hence, it is a preferred solution for the majority of electrical conversion applications such as electric traction, high power industrial drives, renewable power generation, and gridconnected inverters, etc. The paper gives a comprehensive review of the SVM for NPC-MLI. First, this paper deliberates the state of art for two-level SVM and extends it to three-level (3L) SVM. Also compares the 3L SVM performance with other MCPWM techniques. Followed by the various modified MLI SVM techniques in terms of their implementations, DC-link capacitor balancing, and reduction of CMV. Further, the review of MLI SVM is widened to open-end winding Inverters and multiphase MLIs. The final part of this paper discussed the future trends and research directions on MLI SVM techniques and its applications.

**INDEX TERMS** Space Vector Modulation, Multi carrier Pulse Width Modulation, 3-Phase Neutral Point Clamped Inverters, 5-Phase Neutral Point Clamped Inverters, DC-link voltage balancing, Total Harmonics Distortion, Common Mode Voltage, Open-End Winding Inverter.

|                                      | PSC PWM                                                                                                                                                                                                                                                                                                                                                    | Phase Shifting Carrier PWM                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multi-Level Inverter                 | IC PWM                                                                                                                                                                                                                                                                                                                                                     | Interleaved Carrier PWM                                                                                                                                                                                                                                                                                                                                                                                                     |

| Voltage Source Inverter              | VFC PWM                                                                                                                                                                                                                                                                                                                                                    | Variable Frequency Carrier PWM                                                                                                                                                                                                                                                                                                                                                                                              |

| Total Harmonic Distortion            | VSVM                                                                                                                                                                                                                                                                                                                                                       | Virtual Space Vector Modulation                                                                                                                                                                                                                                                                                                                                                                                             |

| Pulse Width Modulation               | NTV                                                                                                                                                                                                                                                                                                                                                        | Nearest Three Vector                                                                                                                                                                                                                                                                                                                                                                                                        |

| Multi carrier Pulse Width Modulation | STV                                                                                                                                                                                                                                                                                                                                                        | Selected Three Vector                                                                                                                                                                                                                                                                                                                                                                                                       |

| Neutral Point Clamped                | OFV                                                                                                                                                                                                                                                                                                                                                        | Optimized Five Vectors                                                                                                                                                                                                                                                                                                                                                                                                      |

| Common Mode Voltage                  | 2L                                                                                                                                                                                                                                                                                                                                                         | 2 Level                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Cascaded H-Bridge                    | 3L                                                                                                                                                                                                                                                                                                                                                         | 3 Level                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Flying Capacitor                     | NPF                                                                                                                                                                                                                                                                                                                                                        | Neutral Point Fluctuation                                                                                                                                                                                                                                                                                                                                                                                                   |

| Selective Harmonic Elimination PWM   | DC                                                                                                                                                                                                                                                                                                                                                         | Direct Current                                                                                                                                                                                                                                                                                                                                                                                                              |

| Space Vector Modulation              | 3D                                                                                                                                                                                                                                                                                                                                                         | 3 Dimensional                                                                                                                                                                                                                                                                                                                                                                                                               |

| Space Vector Diagram                 | OVM                                                                                                                                                                                                                                                                                                                                                        | Over Modulation                                                                                                                                                                                                                                                                                                                                                                                                             |

| Phase Disposition PWM                | $M^2ZV$                                                                                                                                                                                                                                                                                                                                                    | One Zero Vector and Two Medium                                                                                                                                                                                                                                                                                                                                                                                              |

| Phase Opposition and Disposition PWM |                                                                                                                                                                                                                                                                                                                                                            | Switching Vectors                                                                                                                                                                                                                                                                                                                                                                                                           |

| Alternate POD PWM                    | $M^3V$                                                                                                                                                                                                                                                                                                                                                     | Three Medium Switching Vectors                                                                                                                                                                                                                                                                                                                                                                                              |

|                                      | Multi-Level Inverter Voltage Source Inverter Total Harmonic Distortion Pulse Width Modulation Multi carrier Pulse Width Modulation Neutral Point Clamped Common Mode Voltage Cascaded H-Bridge Flying Capacitor Selective Harmonic Elimination PWM Space Vector Modulation Space Vector Diagram Phase Disposition PWM Phase Opposition and Disposition PWM | Multi-Level Inverter Voltage Source Inverter Voltage Source Inverter Voltage Source Inverter VFC PWM Total Harmonic Distortion VSVM Pulse Width Modulation NTV Multi carrier Pulse Width Modulation Neutral Point Clamped Common Mode Voltage Cascaded H-Bridge Flying Capacitor Selective Harmonic Elimination PWM Space Vector Modulation Space Vector Diagram Phase Disposition PWM Phase Opposition and Disposition PWM |

<sup>&</sup>lt;sup>2</sup>Department of Electrical Engineering, Tshwane University of Technology, Pretoria 0001, South Africa

FPGA Field Programmable Gate Array

PE Partial Elimination FE Full Elimination

EMI Electromagnetic Interference

OFV Optimized Five Vectors

OEW Open-End Winding

FLI Five leg Inverter

NSI Nine Switch Inverter

FOC Field Oriented Control

DTC Direct Torque Control

# I. INTRODUCTION

The two-level (2L) VSI has been ruling the industrial world before the development of MLI. The 2L VSI is widely used in transportation and industrial automation [1], [2]. The output voltage of the 2L VSI will be of two levels such as  $+V_{dc}$  and  $-V_{dc}$ . The PWM generation plays an important role in controlling the connected load. The generation of PWM for two-level (2L) VSI is discussed. The limitation of using 2L inverter is that it is not possible to operate high power and high frequency applications. To overcome this issue the three-level (3L) inverter is developed in 1981 by A.Nabae, et.al., The output voltage of the 3L inverter will be in three level like  $+V_{dc}/2$ , 0 and  $-V_{dc}/2$ . Since the development of 3L inverter, the controlling of motor drive in high voltage applications is preferred using MLIs [3]-[6].

The MLIs are most commonly categorized into NPC inverter [7]-[10], cascaded H-bridge inverter [11]-[14] and flying capacitor inverter [15]-[18]. Among these three types, NPC which is also called as diode clamped multilevel inverter attracts the industries as they have lower Electromagnetic Interference (EMI) and the efficiency is considerably high. The controlling of drives is done by PWM strategies which are basically classified as Multicarrier PWM (MC PWM) [19]-[21], Selective Harmonic Elimination (SHE) PWM [22]-[24] and Space Vector Modulation (SVM) [25]-[28]. The PWM signal generated using multiple carrier signals by shifting the level and phase angle of carrier signals is named as Multi carrier PWM signals. The Phase Disposition (PO) [29], Phase Opposition and Disposition (POD) and Alternative Phase Opposition and Disposition (APOD) [30] techniques are grouped as level shifted PWM. In Phase Shifting Carrier (PSC) PWM [31], the power loss is evenly distributed when compared to level shifted PWM. The Interleaved Carrier (IC) PWM [32] and Variable Frequency Carrier (VFC) PWM [33] are also the types of MCPWM techniques. These MCPWM techniques are not able to reduce the harmonics in output which induces the researcher to move on to SHE PWM technique. The SHE PWM is used to eliminate the harmonics selectively [22]. The harmonics which are needed to be removed is included in the carrier signal which helps to eliminate the corresponding harmonic elements from PWM pulse. Though SHE PWM eliminates the

harmonics, it has few drawbacks like slower reaction during transient conditions, switching angle needs to be maintained below  $\pi/2$ , pre-defined calculations are required etc., [216-219]. To overcome all these issues, the SVM technique [34] is introduced which also provides the balancing of DC-link voltages and reduction of common mode voltages along with harmonic reduction [35]-[38]. The output voltage and harmonic elimination of SVM is better over the sine PWM techniques [220-221]. The reduction of CMV can be done easily in SVM by neglecting the switching states that generates high CMV. As the pulses in SVM technique is digital, the DC-link utilization can be done easily in SVM.

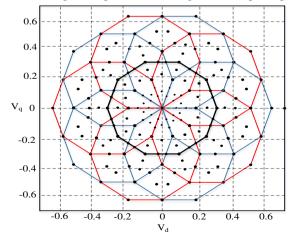

Though SVM has few advantages, the medium vectors present in space vector are responsible for the fluctuation in DC-link voltages. This problem can be reduced by removing the medium vectors and it is named as Virtual Space Vector Modulation (VSVM) [39]-[41]. Due to the absence of medium vectors in VSVM, the fluctuation in the neutral point is tends to be reduced which provides the better output. Another challenge in the NPC MLI is faced when the unbalanced dc source (PV input) is used [42]-[44]. The location of vectors in SVM of unbalanced dc source will be displaced from its original position due to the variation of dc sources. The performance of multi-level inverter when unbalanced dc source is supplied to the inverter is discussed. The minimum time period is involved along with original time period to overcome the unbalancing issues caused by asymmetrical dc sources. The operation of the MLI at over modulation region is discussed and its performance is compared with the normal modulation region. [45]- [46].

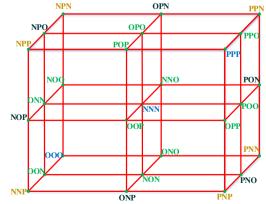

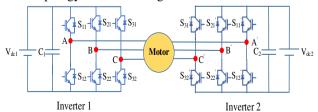

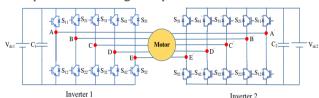

Then the research is moved towards 3D SVM technique which provides the faster and accurate response than 2D SVM. The 3D SVM techniques for three-leg and four-leg inverter are studied [47]. The CMV and dc-link balancing is minimized because of non-availability of redundant vectors (vectors at same point is said as redundant vectors). The other advantages of 3D SVM is low switching loss and conduction loss. The research is very less in 3D SVM due to its complex structure and calculation. Though many PWM and SVM techniques are available for the 3-phase inverters to reduce the DC-link voltage, switching loss, CMV etc., The development of Open-End Winding (OEW) inverter gives the solution for the above-mentioned limitations. OEW inverter is introduced to overcome all these issues without any changes in the modulation techniques [48], [49]. The OEW inverter has two inverters with separate windings connected to a common load. No additional modification needed for this topology to reduce the CMV as the inverters are connected to separate DC voltages and switching loss is less because the supply voltage is half when compared to the conventional NPC MLI. The SVM of the 2L and 3L OEW inverter is discussed.

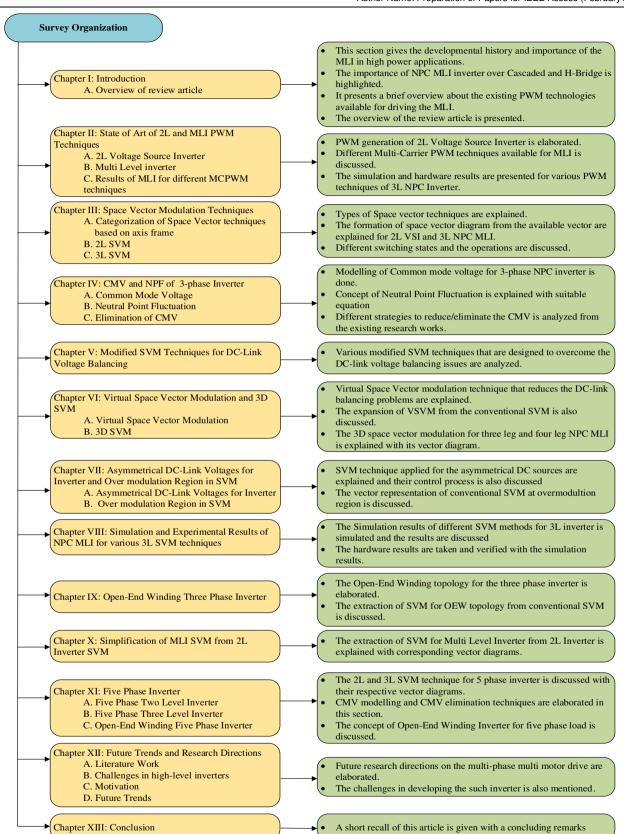

FIGURE 1. Organization of the review article

IEEE Access

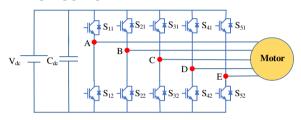

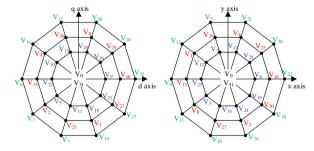

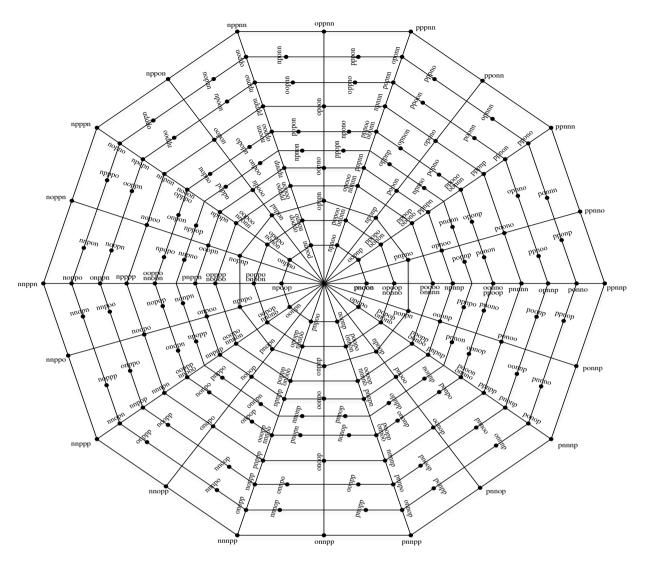

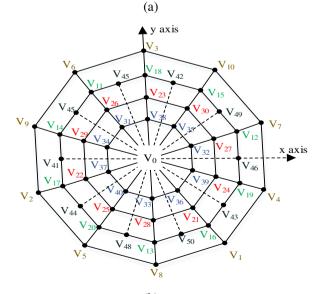

In recent years, the researchers are slowly concentrating on 5-phase inverters which decrease the switching loss and CMV when compared to the 3-phase inverters [50]. Also, it provides the optimum DC-link voltage for inverter. The multi-phase system reduces the per-phase power stress as power gets divided by five [51]. The MCPWM techniques of 5-phase inverter will be similar to 3- phase inverter [52]-[54]. The SVM for 5-phase 2L NPC inverter [55] is

discussed followed by 3L SVM technique where Optimized Five Vector (OFV) method is used for the selection of vectors [56], [57]. The OFV is carefully chosen so that the desired voltage is generated at main subspace ( $\alpha$ - $\beta$  subspace) and the average voltage at auxiliary subspace (x-y subspace) is made zero.

The OFV consists of reduced switching vectors (113 vectors) of the 5-phase SVM which is further reduced to 51 vectors that has zero CMV which eliminates the CMV completely. The OEW topology for 5-phase inverter is also discussed. The review on different PWM techniques is made to realize that a SVM technique provides better performances than the MCPWM techniques.

### A. Overview of review article:

The overview of the presented review article is illustrated in flowchart Fig. 1. This article is organized as described in the flowchart. The aim of this article is to find the suitable PWM generation technique for the NPC MLI which overcomes the issues of CMV, DC-Link balancing, etc. This review article discusses about the following for 3-phase and 5-phase loads.

- This paper gives the basic knowledge about different PWM techniques available for 2L VSI and NPC MLI.

- The mathematical analysis of CMV and NPF is carried out.

- Various modified SVM techniques to reduce CMV and DC-link capacitor voltage are discussed.

- OEW inverter topology are discussed.

- SVM techniques for asymmetrical DC source MLI, SVM at Over-modulation region, VSVM and 3D SVM techniques are also explained for 3-phase loads.

The section II in this paper discusses about the PWM techniques involved in 3-phase inverter. The Space Vector Modulation technique for 2L and 3L three-phase Inverter has been discussed in the section III. The CMV and NPF for 3-phase inverter has been explained in section IV. The modified SVM techniques are compared and discussed in section V. The section VI explains about Virtual Space Vector Modulation and 3D SVM techniques. The SVM techniques for asymmetrical DC-link voltages and SVM in over-modulation region has been explained in section VII. The simulation results are validated with experiments results of 3-phase NPC MLI for different 3L SVM techniques in section VIII. The OEW topology of 3-phase inverter is discussed in section IX. Simplification of MLI from 2L Inverters is discussed in section X. The section XI discussed about SVM of 5-phase 2L and 3L inverters along with OEW topology. The future trends and research directions are discussed in section XII. The inference obtained from this review article is summarized in section XIII as conclusion.

### II. STATE OF ART OF 2L AND MLI PWM TECHNIQUES

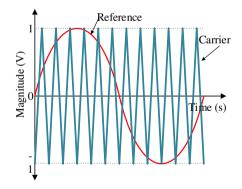

The power electronics switches are controlled by switching on and off. This switching process is done by PWM techniques. The triangular carrier signal is compared with sinusoidal reference signal for generation of pulse which controls the switching process of power electronic switches and it is named as carrier based PWM techniques. The number of carrier signals used in PWM technique is based on the number of levels required. Number of carrier signals = N-1, where N is number of levels. The various PWM techniques for 2L and 3L inverter are discussed in this section.

# B. 2 Level Inverter:

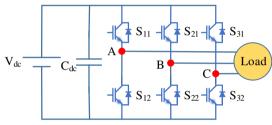

The circuit for 2L VSI is shown in Fig. 2. The inverter has 6 switches with 2 switches in each leg. The upper switch and lower switch in each leg are complementary to each other.

FIGURE 2. Schematic representation of 2-L VSI

The number of carrier signal required for the 2L VSI is 1 (N-1). The switching table for 2L VSI considering phase A is given in Table 1. The arrangement of reference and carrier signal for 2L VSI is shown in Fig. 3. Whenever the carrier signal is higher than reference signal, the pulse is generated and given to switches. The output voltage of this

arrangement has two level such as + $V_{dc}$  and - $V_{dc}$ . FIGURE 3. Pulse Generation for 2L inverter

Table 1. Switching Table for 2L inverter

| States | S <sub>11</sub> | S <sub>12</sub> | Output Voltage   |

|--------|-----------------|-----------------|------------------|

| p      | 1               | 0               | $V_{dc}$         |

| n      | 0               | 1               | -V <sub>dc</sub> |

# C. Multi-Level Inverter:

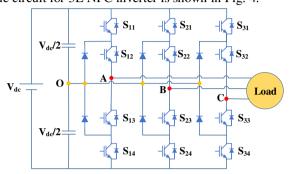

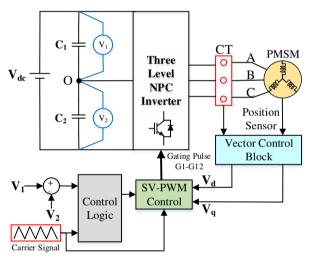

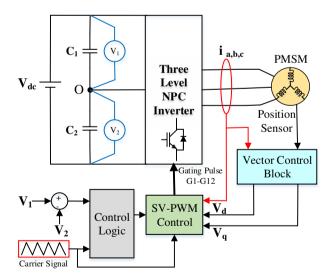

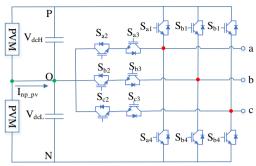

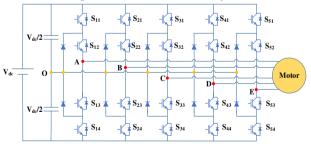

Multi-Level Inverter Topologies are widely used in High Voltage AC Drives. On comparing to 2L VSI, MLIs has many advantages such as reduction in voltage stress across switching devices, lower dv/dt, lesser switching loss at high switching frequency, lesser harmonic contents and lower CMV. Due to these advantages, the MLI is widely preferred in high power and high frequency applications. The circuit for 3L NPC inverter is shown in Fig. 4.

FIGURE 4. Three level Neutral Point Clamped Inverter

The number of active switches in 3L inverter is more when compare to 2L VSI. The 3L inverter has 12 switches and 6 diodes. Each leg consists of 4 switches with 2 switches in upper leg and 2 switches in lower leg. Also 2 diodes are used in each leg, with one junction is connected to neutral point of DC-link capacitor and the other junction is connected in between two switches in the upper and lower leg correspondingly. The pulse for multi-level inverter is generated by various PWM techniques. The Multicarrier PWM technique is classified as Phase Disposition (PO) PWM, Phase Opposition Disposition (POD) PWM, Alternate Phase Opposition Disposition (APOD) PWM, Phase Shifting Carrier (PSC) PWM, Interleaved Carrier (IC) PWM and Variable Frequency Carrier (VFC) PWM. The arrangements of carrier and reference signal for 3L PWM is shown in Fig. 4. The carrier signals required for 3L inverter is 2 (N-1) [212],[213].

Table 2. Switching States of Phase A

| States       | S <sub>11</sub> | S <sub>12</sub> | S <sub>13</sub> | S <sub>14</sub> | Pole voltage |

|--------------|-----------------|-----------------|-----------------|-----------------|--------------|

| p (Positive) | 0               | 0               | 1               | 1               | $V_{dc/2}$   |

| o (Zero)     | 0               | 1               | 1               | 0               | 0            |

| n (Negative) | 1               | 1               | 0               | 0               | $-V_{dc/2}$  |

| Invalid      | 1               | 0               | 0               | 1               | -            |

The switching states and phase voltage of A phase is shown in Table 2. In switching states, 1 is denoted when the switch is in ON condition and 0 is denoted when the switch is in OFF condition. The pole voltage of each state will be obtained as  $V_{dc}/2$ , 0 or  $-V_{dc}/2$ . If  $S_{11}$  and  $S_{14}$  switches are turned on, then such state is not valid for the NPC inverter. The remaining 3 states will be denoted as p, o and n respectively.

In PD PWM technique [58], the carrier signals are placed at different position in above and below of the zero

reference as shown in Fig.5 (a). While in POD PWM technique [59], the carrier signals are not only placed in different positions but also the phase angles are shifted by  $180^{\circ}$  for the signals placed below zero reference when compared to the signals placed above zero reference as shown in Fig.5 (b).

FIGURE 5. Arrangements of Reference and Carrier signal waveforms of

phase A for 3-level NPC inverter for (a) PD, (b) POD, (c) APOD, (d) IC, (e) PSC, (f) VFC PWM techniques

In APOD PWM technique [60], the alternative carrier signals are shifted by 180° to each other as given in Fig..5 (c). The carrier signals will not overlap each and also the amplitude and frequency remain same in above three methods [213]. In IC PWM technique [61], the amplitude and frequency will be same for all carrier signals but one carrier signal will overlap with the other carrier signal in some parts as shown in Fig.5 (d). In PSC PWM technique [62], all the carrier signals will be at same amplitude level and frequency will also be same, but each carrier signal will be shifted by certain degrees based on the number of levels is shown in Fig.5 (e). The phase angle of carrier signals shifted is calculated as 180°/N. The frequency of all carrier signal will not be same for VFC PWM technique [63] as shown in Fig.5 (f).

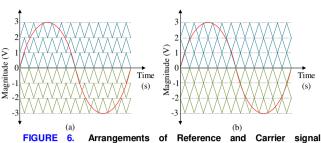

In case of 3L inverter both POD and APOD technique will be similar to each other. However, in higher level inverter they both will be different as shown below. The seven level PWM generation using POD and APOD technique is shown in Fig. 6. The following section discusses about the Space Vector Modulation Techniques [212].

FIGURE 6. Arrangements of Reference and Carrier signal waveforms of phase A for 7 level NPC inverter for (a) POD, (b) APOD PWM techniques

# D. Results of MLI for different MCPWM techniques:

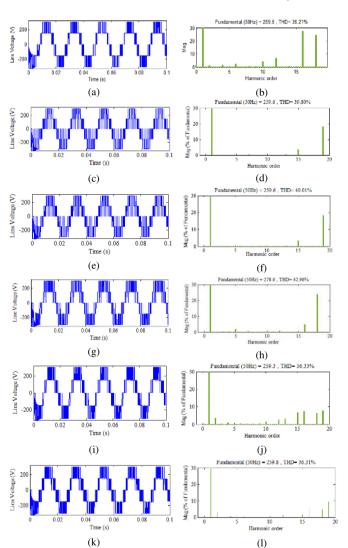

FIGURE 7. Line-to-Line Voltage of (a) PO, (c) POD, (e) APOD, (g) IC, (i) PSC and (k) VFC PWM. Voltage THD of (b) PO, (d) POD, (f) APOD, (h) IC, (j) PSC and (l) VFC PWM

The input dc voltage is considered as 300V to perform the simulation with 10kHz switching frequency. The line voltage waveforms and THD chart upto 20 harmonics are captured for PO, POD, APOD, IC, PSC and VFC PWM techniques and shown in Fig. 7 (a-l).

The MATLAB simulation is carried out for various PWM techniques of 3L inverter at different modulation indices and the results are noted in Table 3. From the obtained results, it is observed that IC PWM technique provides high line voltage but the THD% is very poor when compared to other PWM techniques. While, the PO PWM technique has considerable lesser THD% among MC PWM techniques and the line voltage is almost similar to line voltage obtained from other PWM techniques.

Table 3. Line Voltage and THD for various PWM Techniques

| M       | PD     |       | P     | POD   |       | APOD  |  |

|---------|--------|-------|-------|-------|-------|-------|--|

| $M_{i}$ | V      | THD%  | V     | THD%  | V     | THD%  |  |

| 1       | 259.5  | 35.21 | 259.6 | 39.80 | 259.6 | 40.01 |  |

| 0.9     | 233.6  | 33.82 | 233.4 | 37.67 | 233.8 | 38.01 |  |

| 0.8     | 207.68 | 31.78 | 207.5 | 36.58 | 207.8 | 36.88 |  |

| 0.7     | 181.72 | 34.67 | 181.5 | 38.31 | 181.8 | 35.85 |  |

| 0.6     | 155.76 | 39.56 | 155.6 | 42.14 | 155.8 | 40.31 |  |

| Mi      | IC     |       | PSC   |       | VFC   |       |  |

| IVI     | V      | THD%  | V     | THD%  | V     | THD%  |  |

| 1       | 278.6  | 42.96 | 259.3 | 36.33 | 259.8 | 36.31 |  |

| 0.9     | 250.7  | 41.13 | 233.6 | 34.76 | 236.2 | 35.06 |  |

| 0.8     | 222.8  | 39.58 | 207.6 | 32.91 | 210.6 | 33.81 |  |

| 0.7     | 195.1  | 40.15 | 181.7 | 35.81 | 187.8 | 34.95 |  |

| 0.6     | 167.1  | 41.26 | 155.7 | 37.26 | 162.3 | 36.03 |  |

The output harmonics in MC PWM techniques are high. To reduce the harmonics, SVM technique is introduced. Also, DC-link voltage balancing can be done in SVM which is difficult in MCPWM technique. The voltage stress at switches can be reduced while using SVM technique. The next section deals with SVM technique for 2L and 3L inverter.

# **III. SPACE VECTOR MODULATION:**

The SVM technique is a digital modulating technique which generates PWM based on the vector representation. These digital signals are given directly to switches which are controlled as per vector representation. The vectors are placed in hexagonal structure for representing magnitudes and phases of each vector. The SVM which is represented in  $\alpha\text{-}\beta$  frame is the conventional technique. The SVM can also be represented in g-h coordinate system and K-L coordinate system.

# A. Space Vector Techniques Based on Axis Frame:

# 1) CONVENTIONAL (α-β frame) SVPWM TECHNIQUE

In [64], various space vector PWM techniques are discussed. The SVM shown in Fig. 6 is conventional ( $\alpha$ - $\beta$  frame) SVM technique. The axis of  $\alpha$  is along  $0^0$  and  $\beta$  is along  $90^0$ . The reference voltage is given in below equation:

$$V_{ref} = \frac{2}{3} [V_a + \alpha V_b + \alpha^2 V_c] \tag{1}$$

where  $\alpha = e^{j2\pi/3}$

Table 4. Relation between abc frame with different coordinate systems

|                          | α-β frame                                                                                                                                                                                                                             | g-h Coordinate system                                                                                                                                                                                                     | K-L Coordinate system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Vector<br>Representation | $\beta$ $t_b$ $t_b$ $t_b$ $t_b$ $t_b$ $t_c$ $t_b$ $t_c$ $t_b$                                                                                                                                                                         | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                     | $\begin{array}{c c} & & & & \\ & & & \\ \hline \\ l_{K+1} & & & \\ \hline \\ l_{K} & & \\ \hline \\ l_{K} & & \\ \hline \\ & & \\ \hline \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ & & \\ \\ &$ |  |

| Relation with abc frame  | $\begin{bmatrix} V_{r\alpha} \\ V_{r\beta} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix}$ | $\begin{bmatrix} V_{rg} \\ V_{rh} \end{bmatrix} = \begin{bmatrix} 1 & -1 & 0 \\ 0 & 1 & -1 \end{bmatrix} \begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix}$                                                                 | $\begin{bmatrix} V_{rL} \\ V_{rK} \end{bmatrix} = \begin{bmatrix} 1 & 0 & -1 \\ 0 & 1 & -1 \end{bmatrix} \begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Volt Sec<br>Balance      | $V_{ref}T_s = V_8t_a + V_1t_b + V_7t_c$ $T_s = t_a + t_b + t_c$                                                                                                                                                                       | $egin{align*} V_{rg}T_{s} &= V_{ag}t_{g,h} + V_{bg}t_{g+1,h} \\ &+ V_{cg}t_{g,h+1} \\ V_{rh}T_{s} &= V_{ah}t_{g,h} + V_{bh}t_{g+1,h} \\ &+ V_{ch}t_{g,h+1} \\ T_{s} &= t_{g,h} + t_{g+1,h} + t_{g,h+1} \\ \end{gathered}$ | $\begin{aligned} V_{rL}T_{s} &= V_{aL}t_{L,K} + V_{cL}t_{L,K+1} + V_{dL}t_{L+1,K+1} \\ V_{rK}T_{s} &= V_{aK}t_{L,K} + V_{cK}t_{L,K+1} + V_{dK}t_{L+1,K+1} \\ T_{s} &= t_{L,K} + t_{L,K+1} + t_{L+1,K+1} \end{aligned}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

# 2) SVPWM BASED ON g-h COORDINATE SYSTEM

In g-h coordinate system, the g axis is placed along  $0^0$  which overlaps  $\alpha$  axis and h axis is shifted by  $60^0$  from g axis.

# 3) SVPWM BASED ON K-L COORDINATE SYSTEM

The K-L coordinate system is also referred as  $120^{0}$  coordinate system. In this system, the L axis is overlapped with  $\alpha$  axis at  $0^{0}$  and the K axis is shifted by  $120^{0}$  from L axis in clockwise direction. The volt-sec balance and the relation between abc frame and the corresponding frames are shown in Table 4.

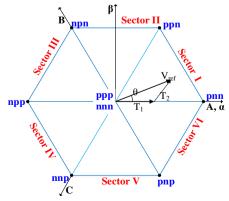

# B. 2 Level SVM:

The 2L SVM for 3-phase inverter has 8 switching states ( $x^n = 2^3 = 8$ ) and it contains 6 active vectors and 2 zero vectors [65]-[71]. In the switching sequence, "n" is denoted when the lower switch is active whose corresponding voltage is -V<sub>dc</sub> and "p" is denoted when the upper switch is active whose corresponding voltage is +V<sub>dc</sub>. The space vector diagram for 2L inverter is shown in Fig. 8.

FIGURE 8. Space Vector Diagram of 2-Level Inverter

FIGURE 9. Effects of Switching States of 2L Inverter

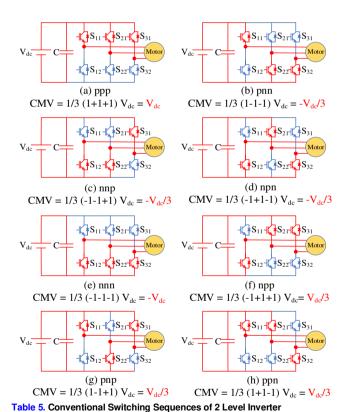

The conventional SVM switching sequence for different sectors of 2L inverter is given in Table 5. The effects of

Switching Sequence

ppp-ppn-pnn-nnn-pnn-ppp

ppp-ppn-npn-nnn-npn-ppn-ppp

ppp-npp-npn-nnn-npn-npp-ppp

ppp-npp-nnp-nnn-nnp-ppp

ppp-pnp-nnp-nnn-nnp-npn-ppp

ppp-pnp-pnn-nnn-pnn-pnp-ppp

2 VOLUME XX, 2017

Sector 1

Sector 2

Sector 3

Sector 4

Sector 5

Sector 6

various switching States with their CMV for 2L VSI is shown in Fig. 9.

If the reference vector is placed in sector I, V<sub>1</sub> and V<sub>2</sub> are the two nearest voltage vectors to reference vector and  $V_Z$  is the zero-voltage vector.  $T_1$ ,  $T_2$  and  $T_Z$  are the corresponding time duration for reference vectors. The Volt-Second equation is given as

$$V_{ref}T_s = V_1T_1 + V_2T_2 + V_zT_z$$

(2)

where  $T_s = T_1 + T_2 + T_z$ From the vector diagram, the following equations are derived.

$$T_1 + T_2 \cos 60^0 = m T_s \cos \alpha \tag{3}$$

$$T_2 \sin 60^0 = m T_s \sin \alpha \tag{4}$$

$T_1 + T_2 \cos \theta \theta = m T_s \sin \alpha$   $T_2 \sin 60^0 = m T_s \sin \alpha$ Where  $m = \frac{V_{ref}}{V_{dc}}$

On solving the above equations, the time period can be calculated.

red.

$$T_{1} = (m. T_{s}) \frac{\sin(60^{0} - \theta)}{\sin(60^{0})}$$

(5)

$$T_{2} = (m. T_{s}) \frac{\sin(\theta)}{\sin(60^{0})}$$

(6)

$$T_{Z} = T_{s} - T_{1} - T_{2}$$

(7)

$$T_2 = (m. T_s) \frac{\sin(\theta)}{\sin(600)}$$

(6)

$$T_Z = T_s - T_1 - T_2 (7)$$

Though 2L SVM is easy to apply, there are many disadvantages. The 2L inverters can be used only for low power and low frequency applications. For the application of high power and high frequency, the 3L inverter is introduced.

The SVM and switching sequence of 3L NPC MLI is discussed in following sub-section.

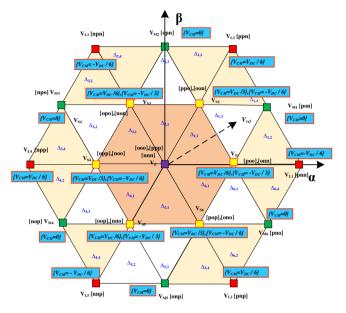

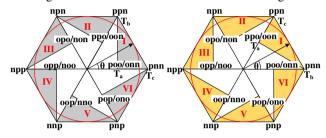

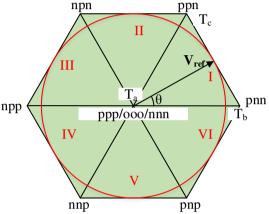

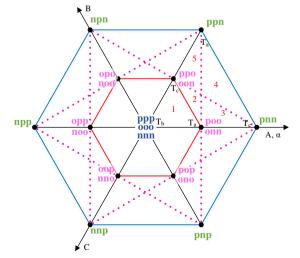

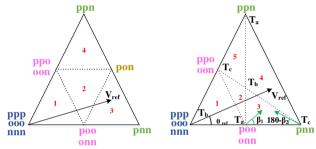

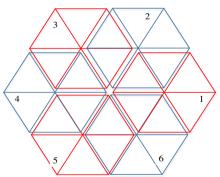

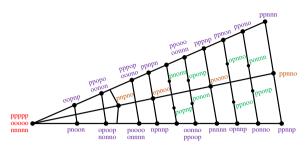

# 3 Level SVM:

FIGURE 10. Space Vector Modulation of 3L Inverter

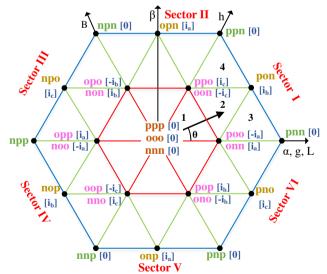

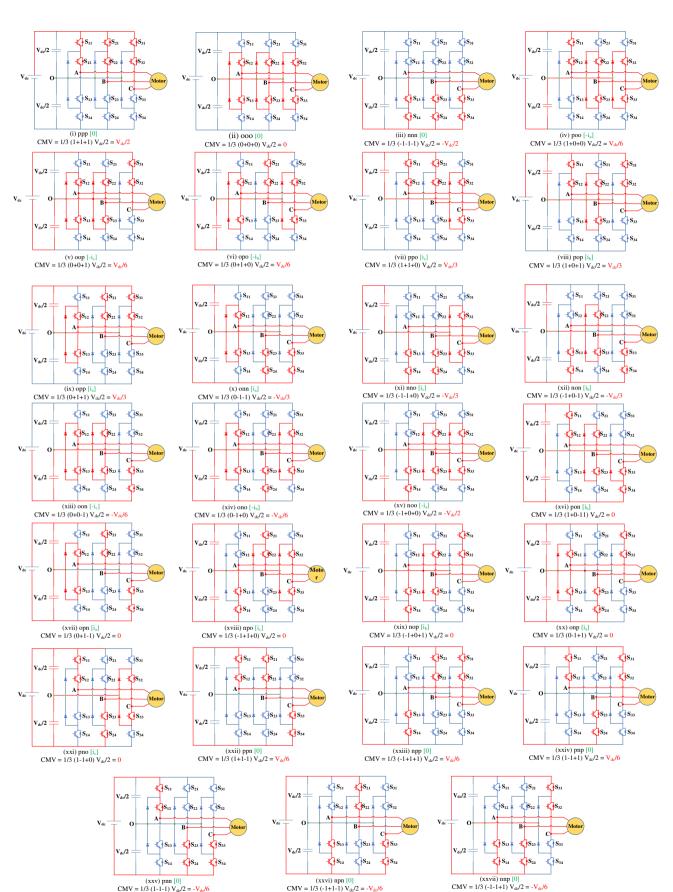

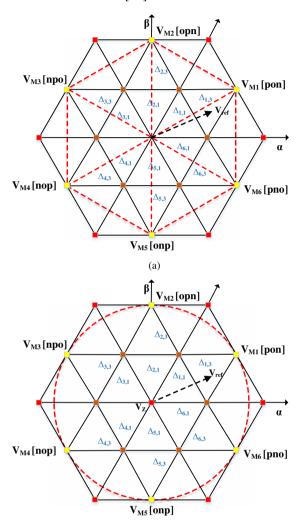

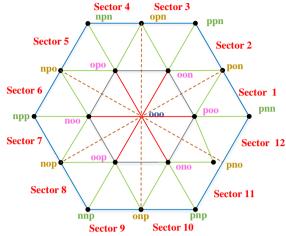

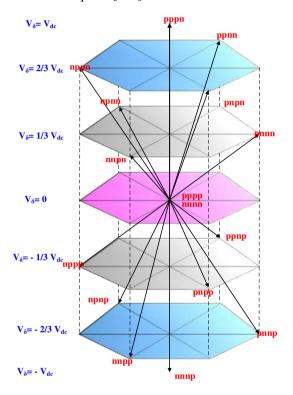

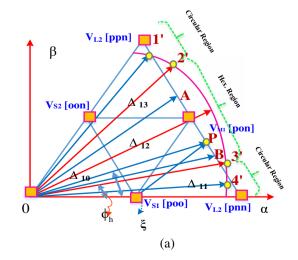

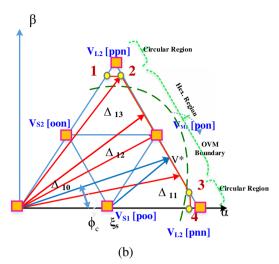

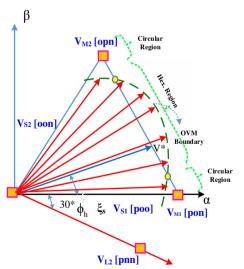

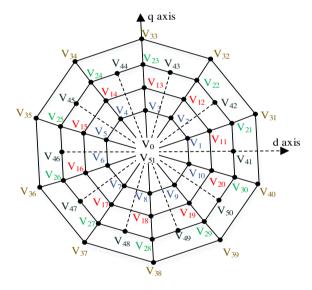

The 3L inverter has 27 switching states with 3 Zero vectors, 12 Small vectors, 6 Medium vector and 6 Large vectors. Among those 27 switching states ( $x^n = 3^3 = 27$ ), 8 states are redundancy states and the remaining 19 vector states are placed in space vector diagram in Fig. 10. The SVM is divided into 6 sectors and each sector is divided

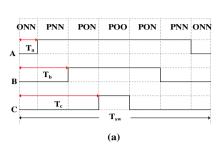

into 4 sub-sectors. The neutral point current of each vector is denoted in the SVM diagram [72]-[78]. The effects of various switching states for the 3L inverter are shown in Fig. 11. The conventional SVM switching sequence for six sectors of the 3L NPC MLI is given in the Table 6.

Table 6. Conventional switching sequence of the three-level inverter SVM

| Sector | Sub-sector | Switching sequence                                      |

|--------|------------|---------------------------------------------------------|

|        | 1          | nnn-onn-oon-ooo-poo-ppo-ppo-poo-ooo-                    |

|        | 1          | oon-onn-nnn                                             |

| 1      | 2          | onn-oon-pon-poo-poo-pon-oon-onn                         |

|        | 3          | onn-pnn-pon-poo-pon-pnn-onn                             |

|        | 4          | ppo-ppn-pon-oon-pon-ppn-ppo                             |

|        | 1          | ppp-ppo-opo-ooo-oon-non-nnn-non-oon-ooo-opo-ppp         |

| 2      | 2          | non-oon-opn-opo-ppo-opo-opn-oon-non                     |

|        | 3          | oon-opn-ppn-ppo-ppn-opn-oon                             |

|        | 4          | non-npn-opn-opo-opn-npn-non                             |

|        | 1          | ppp-opp-opo-ooo-noo-non-nnn-non-noo-ooo-<br>opo-opp-ppp |

| 3      | 2          | opp-opo-npo-noo-non-noo-npo-opo-opp                     |

|        | 3          | non-npn-npo-opo-npo-npn-non                             |

|        | 4          | oop-nop-nnp-nno-nnp-oop                                 |

|        | 1          | ppp-opp-oop-ooo-noo-nno-nnn-nno-noo-ooo-                |

|        | 1          | oop-opp-ppp                                             |

| 4      | 2          | nno-noo-nop-oop-oop-nop-noo-nno                         |

|        | 3          | opp-npp-nop-noo-nop-npp-opp                             |

|        | 4          | oop-nop-nnp-nno-nnp-nop-oop                             |

|        | 1          | ppp-pop-oop-ooo-ono-nno-nnn-nno-ono-ooo-                |

|        | 1          | oop-pop-ppp                                             |

| 5      | 2          | pop-oop-onp-ono-nno-ono-onp-oop-pop                     |

|        | 3          | oop-onp-nnp-nno-nnp-oop                                 |

|        | 4          | pop-pnp-onp-ono-onp-pnp-pop                             |

|        | 1          | ppp-pop-poo-ooo-ono-onn-nnn-onn-ono-ooo-                |

|        | 1          | poo-pop-ppp                                             |

| 6      | 2          | pop-poo-pno-ono-onn-ono-pno-poo-pop                     |

|        | 3          | pop-pnp-pno-ono-pno-pnp-pop                             |

|        | 4          | poo-pno-pnn-onn-pnn-pno-poo                             |

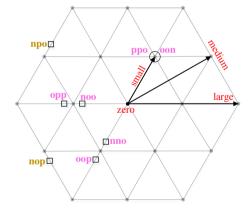

In conventional SVM method, the reference vector is identified based on the three vectors which are placed nearest to the reference vectors. Hence it is also known as Nearest Three Vector (NTV) method.

# IV. CMV AND NPF OF 3 PHASE INVERTER:

# Common Mode Voltage

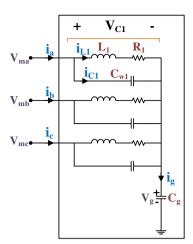

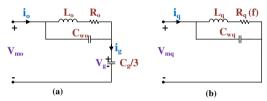

The common mode voltage for the inverter is calculated from  $V_{CMV} = (V_{ao} + V_{bo} + V_{co})/3$ . The High frequency model of a 3-phase inverter motor drive is shown in Fig. 12. The common mode current for 3-phase inverters will be flowing through the stray capacitance Cg and it is calculated by

$$i_g = i_a + i_b + i_c = 3i_o = C_g \frac{dv_g}{dt}$$

(8)

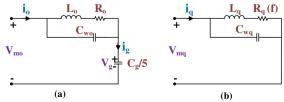

The common mode model for 3-phase load is shown in Fig. 13. (a), where lo, Ro and Cwo are the zero-sequence component of L, R and C respectively. The differential mode model for three phase load is shown in Fig. 13. (b), where the l<sub>q</sub>, R<sub>q</sub> and C<sub>wq</sub> are the q-axis component of L, R and C respectively, while the d-axis model will be same as the q-axis model [79], [80].

FIGURE 11. Effects of Switching States of 3 Level SVM

FIGURE 12. High Frequency model of CMV for 3 phase

FIGURE 13. (a) Common Mode model of a 3-phase load, (b) Differential Mode model of a 3-phase load

The admittance transfer function for common mode model  $(Y_0)$  and differential mode model  $(Y_q = Y_d)$  is given as

$$Y_{o} = \frac{i_{o}}{v_{o}} = \frac{sC_{g}L_{o}C_{wo}\left[s^{2} + s\frac{R_{o}}{L_{o}} + \frac{1}{L_{o}C_{wo}}\right]}{L_{o}(C_{g} + 3C_{wo})\left[s^{2} + s\frac{R_{o}}{L_{o}} + \frac{3}{L_{o}(C_{g} + 3C_{wo})}\right]}$$

(9)

$$Y_{d} = Y_{q} = \frac{i_{q}}{v_{q}} = \frac{C_{wq}\left[s^{2} + s\frac{R_{q}(f)}{L_{q}} + \frac{1}{L_{q}C_{wq}}\right]}{L_{q}\left[s + \frac{R_{q}(f)}{L_{q}}\right]}$$

(10)

$$Y_d = Y_q = \frac{i_q}{v_q} = \frac{C_{wq} \left[ s^2 + s \frac{R_q(f)}{L_q} + \frac{1}{L_q C_{wq}} \right]}{L_q \left[ s + \frac{R_q(f)}{L_q} \right]}$$

(10)

The CMV of 2L inverter is  $\pm V_{dc}/3$  and  $\pm V_{dc}$ , while the CMV for 3L inverter is as follows:  $\pm V_{dc}/6$ ,  $\pm V_{dc}/3$ ,  $\pm V_{dc}/2$ and 0. It is observed that the CMV for 3L inverter  $(\pm V_{dc}/6)$ is less when compared to CMV of 2L inverter (±V<sub>dc</sub>). The CMV for each vector along with their output voltage levels of 2L and 3L inverters are listed in Table 7 and Table 8 respectively.

Table 7. Switching States and CMV of 2L Inverter

| Switching States | CMV Calculation                 | CMV                |

|------------------|---------------------------------|--------------------|

| nnn (Zero)       | $(-V_{dc}-V_{dc}-V_{dc})/3$     | -V <sub>dc</sub>   |

| pnn              | $(V_{dc} - V_{dc} - V_{dc})/3$  | -V /3              |

| ppn              | $(V_{dc} + V_{dc} - V_{dc})/3$  | V <sub>dc</sub> /3 |

| npn              | $(-V_{dc}+V_{dc}-V_{dc})/3$     | -V /3              |

| npp              | $(-V_{dc} + V_{dc} + V_{dc})/3$ | V /3               |

| nnp              | $(-V_{dc}-V_{dc}+V_{dc})/3$     | -V /3              |

| pnp              | $(V_{dc} - V_{dc} + V_{dc})/3$  | V <sub>dc</sub> /3 |

| 111 (Zero)       | $(V_{dc} + V_{dc} + V_{dc})/3$  | V <sub>dc</sub>    |

Table 8. Output voltage and CMV of the each switching states in 3L inverter

| Vectors | Switching States CMV     |                              | Voltage level     |  |

|---------|--------------------------|------------------------------|-------------------|--|

| Zero    | 000                      | 0                            |                   |  |

| Vectors | ppp                      | $V_{dc}/2$                   | 0                 |  |

|         | nnn                      | $\frac{V_{dc}/2}{-V_{dc}/2}$ |                   |  |

|         | poo, oop, opo            | $V_{dc}/6$                   |                   |  |

| Small   | ppo, pop, opp $V_{dc}/3$ |                              | 1/ /2             |  |

| Vectors | onn, nno, non            | $-V_{dc}/3$                  | $V_{dc}/3$        |  |

|         | oon, ono, noo            | $-V_{dc}/6$                  |                   |  |

| Medium  | pon, opn, npo,           | 0                            | $V_{dc}/\sqrt{3}$ |  |

| Vectors | nop, onp, pno            | Ö                            | dc/ V3            |  |

| Large   | ppn, npp, pnp            | $V_{dc}/6$                   | 217 /2            |  |

| Vectors | pnn, npn, nnp            | $-V_{dc}/6$                  | $\frac{2V}{dc}/3$ |  |

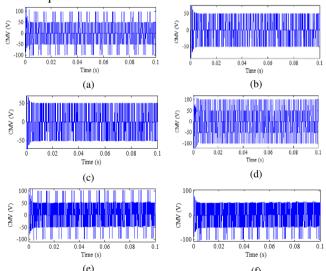

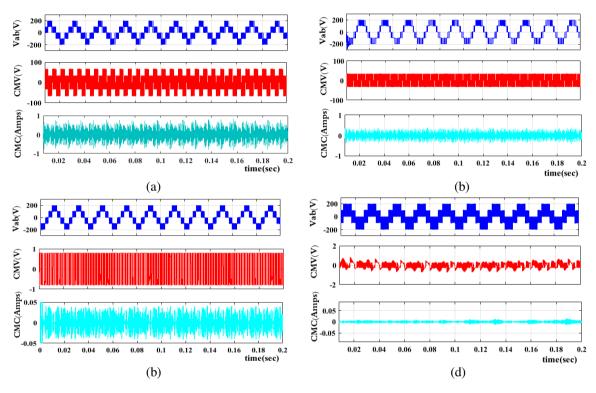

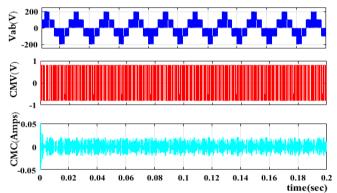

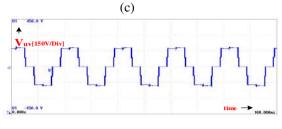

The simulation results of CMV for 3L NPC MLI of various MC PWM is shown in Fig. 14 (a-f). The results are obtained for PO, POD, APOD, IC, PSC and VFC PWM techniques.

FIGURE 14. CMV of (a) PO, (b) POD, (c) APOD, (d) IC, (e) PSC and (f) VFC

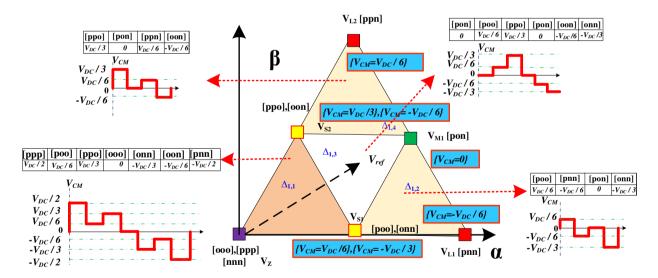

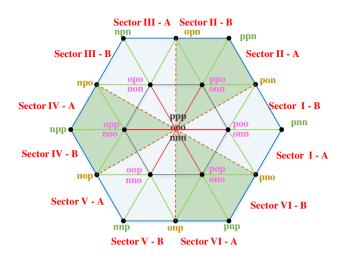

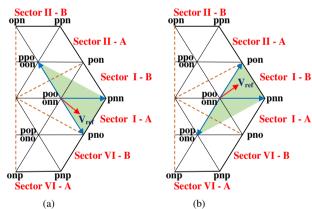

The SVM diagram is redrawn with the values of CMV for each vector in Fig.15. It can be noticed that the CMV of medium vectors are zero which plays a major role in the reduction on CMV in the NPC MLI.

The effects of CMV in the sector I of the 3L SVM is shown in Fig. 16. The changes in CMV from one switching state to other switching state is also represented for each switching sequences of sector I.

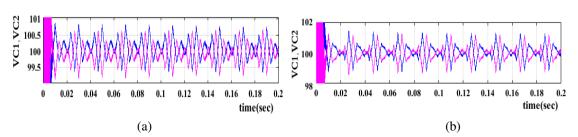

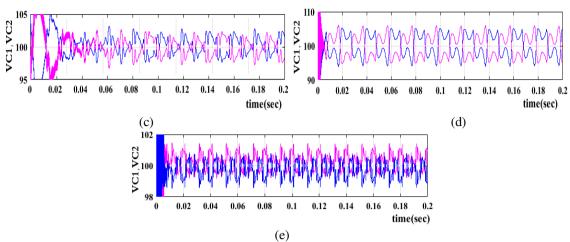

# B. Neutral Point Fluctuation:

The multi-level inverter has (n-1) DC-link capacitors which should have equal voltages (V<sub>dc</sub>/n-1). Due to third harmonic injection, unequal commutation semiconductors devices, etc. the DC-link voltages will not be same.

This variation in DC-link voltage is known as Neutral Point Fluctuation [81] and it is calculated as

$$NPF = \frac{\frac{V_{dc}}{n-1} - V_{c2}}{\frac{V_{dc}}{nc}} * 100 \tag{11}$$

FIGURE 15. 3L SVM diagram with CMV calculation

The CMV and NPF has been noted in simulation by applying different PWM techniques in 3L NPC MLI which in given in the Table 9. The allowable value for Neutral Point Fluctuation is 1% as per IEEE standard [213]

Table 9. Common Mode Voltage and Neutral Point Fluctuation for various PWM Techniques

| 1 Will Toolingdoo |     |     |      |     |     |     |     |

|-------------------|-----|-----|------|-----|-----|-----|-----|

| PWM<br>Techniques | PD  | POD | APOD | IC  | PSC | VFC | SVM |

| NPF %             | 0.6 | 0.6 | 1.2  | 0.8 | 0.6 | 0.5 | 0.4 |

| CMV               | 50  | 100 | 50   | 50  | 50  | 50  | 100 |

The Time duration of reference voltage from the nearest three vector for each sub-sector of the 3L inverter SVM is given in the Table 10.

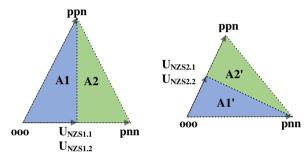

# C. Elimination of CMV:

The common mode voltage is eliminated by selecting the suitable vectors that produces zero CMV. The zero vectors like PPP and NNN can be neglected as it produces the CMV of  $V_{dc}/2$  and  $-V_{dc}/2$  respectively [82]-[84]. If the small vector is neglected, then the CMV will be reduced from  $V_{dc}/3$  to  $V_{dc}/6$ . The large vector which is responsible for the production of CMV of  $V_{dc}/6$  is removed and the resultant output will be free from CMV.

The different CMV reduction processes are discussed by various authors is given in Table 11. These effects have been researched by various authors as cited below.

FIGURE 16. Sector I representation of 3L SVM with the effect of CMV

Table 10. Time duration of reference voltage from nearest three vector

| Table 10. Time duratio | n of reference voltage from nearest three v                | ector                                                       |                                                             |

|------------------------|------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|

| Sub-Sector             | T <sub>1</sub>                                             | T <sub>2</sub>                                              | <b>T</b> <sub>3</sub>                                       |

| 1                      | $T_s\left(2-m\sin\left(\frac{\pi}{3}-\theta\right)\right)$ | $T_s\left(1-2m\sin\left(\frac{\pi}{3}+\theta\right)\right)$ | $T_s\left(2m\sin(\theta)\right)$                            |

| 2                      | $T_s\left(1-2m\sin(\theta)\right)$                         | $T_s\left(2m\sin\left(\frac{\pi}{3}+\theta\right)-1\right)$ | $T_s\left(1-2m\sin\left(\frac{\pi}{3}-\theta\right)\right)$ |

| 3                      | $T_s\left(2-m\sin\left(\frac{\pi}{3}+\theta\right)\right)$ | $T_s\left(2m\sin(\theta)\right)$                            | $T_s\left(2m\sin\left(\frac{\pi}{3}-\theta\right)-1\right)$ |

| 4                      | $T_s\left(2m\sin(\theta)-1\right)$                         | $T_s\left(2m\sin\left(\frac{\pi}{3}-\theta\right)\right)$   | $T_s\left(2-2m\sin\left(\frac{\pi}{3}+\theta\right)\right)$ |

Table 11. Effect of CMV based on vector representation

| Table I       | 1. Effect of CMV based on vector representation                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|---------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ref           | CMV Reduction process                                                                        | Effect of CMV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| [85]          | Large Vector and<br>Medium Vector                                                            | The switching states which have CMV of $\pm V_{\text{de}}/2$ and $\pm V_{\text{de}}/3$ are not considered. Instead, their redundant states which has lower CMV alone is taken which results in the reduction of CMV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| [86],<br>[94] | 1 Zero vector<br>(000) and 6<br>medium vectors                                               | The "ooo" vector and medium vectors are only used and the remaining vectors are not included in SVM. As these vectors will generate only 0 CMV, the CMV is eliminated with this process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| [87],<br>[91] | V <sub>7</sub> and V <sub>0</sub> is eliminated and the remaining vectors are rotated by 30° | If the switching is from even to odd state or vice-versa and switching from even to $V_7$ or odd to $V_0$ then $1/3V_{dc}$ CMV is obtained, whereas switching from even to $V_0$ or odd to $V_7$ then $2/3V_{dc}$ CMV is obtained. While switching from even to even or odd to odd has no variation in common mode voltage. The vectors $V_7$ and $V_0$ is eliminated so as to reduce the CMV, but the reference voltage is restricted to $0.5V_{DC}/2$ . If the reference voltage and phase currents are distorted. Therefore, remaining vectors are rotated by $30^0$ and resultant vectors are used. This results in increasing the maximum peak voltage reference to $0.58V_{DC}/2$ . |  |  |

| [88]          | Zero Redundant<br>State PWM                                                                  | In PODPWM technique two carriers (A1 and A2) are used to generate the pulse, while in Zero redundant state PWM technique four carriers (A1, A2, A1* and A2*) are used. The A1* and A2* are the phase shifted by 1800 from A1 and A2. Due to this, the redundant states are eliminated which results in the reduction of CMV to $\pm V_{\rm dc}/6$ .                                                                                                                                                                                                                                                                                                                                       |  |  |

| [89],<br>[90] | Redundant<br>vectors are<br>removed                                                          | The redundant vectors in zero and small vectors are removed. Theses vectors produce $\pm V_{dc}/2$ and $\pm V_{dc}/3$ at zero and medium vectors respectively. On removing thes vectors, the CMV is reduced.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| [92],<br>[93] | Active Zero State<br>PWM                                                                     | The zero state is avoided in this process. The adjacent vectors $(V_1 \text{ and } V_2)$ of reference vector are accompanied by active zero pairs $(V_3 \text{ and } V_6)$ . Since the zero state is avoided, CMV is reduced to $\pm V_{dc}/6$ .                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| [94]          | Three nearest medium vectors (M³V)                                                           | In this method only 6 medium vectors are considered and the remaining vector are eliminated. As CMV of medium vector is zero, the resultant CMV of the inverter is also zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

Many researches have been made for the reduction of CMV in NPC MLI inverter as discussed in [95]-[98]. The power loss and switching loss analysis of MLI is done in [99]-[103]. The comparative study between different PWM techniques is made in [104]-[106].

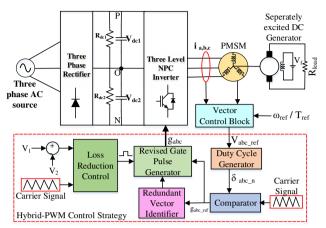

# V. MODIFIED SVM TECHNIQUES:

In 3L inverter, the major issue is balancing of DC-link capacitance voltages. To eliminate this capacitance balancing issues, there are 3 main methods are available [107].

- Using two separate isolated DC-Voltage sources with the help of two independent rectifiers.

- Using back-to-back topology

- Using the carrier or space vector modulation techniques without external hardware

In Table 6, it is noticed that the number of switching sequence is not equal for all the sub-sectors which results in the different switching frequency. Due to the variation in switching frequency, the switching losses is increased. Many researchers have proposed some modified SVM Techniques that balances the DC-link capacitance voltages and reducing the losses. [108]- [110]. The Table 12 gives the effect of DC-link capacitance under modified SVM techniques as per citations given.

| Table 12. V | Various Modified SVM Techniques for Balancing the DC-Link ce                                                                                |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Citation    | Effect of DC-link capacitor balancing                                                                                                       |

| [111],      | The medium vectors with higher modulation index are                                                                                         |

| [112]       | restricted. The modulation indices for 4 regions are given                                                                                  |

|             | below.                                                                                                                                      |

|             | $mg+mh \le 0.5$ for region I                                                                                                                |

|             | mg+mh > 0.5 && mg < 0.5 && mh < 0.5 for region II                                                                                           |

|             | $mg > 0.5 \&\& mh > 0.5 \&\& mg \ge mh$ for region III                                                                                      |

|             | mg > 0.5 && mh > 0.5 && mg < mh for region IV                                                                                               |

| [113]       | Based on phase currents:                                                                                                                    |

|             | a. Large and Zero vectors does not have the                                                                                                 |

|             | phase current that results in proper balancing                                                                                              |

|             | of capacitor voltages                                                                                                                       |

|             | b. Medium vectors that have non-zero phase                                                                                                  |

|             | creates the imbalance in capacitor voltages                                                                                                 |

|             | 2. Based on Modulation Index:                                                                                                               |

|             | a. When modulation index is $0 \le m < 0.5$ , only the                                                                                      |

|             | small vector are active vectors. As a result, the                                                                                           |

|             | DC-link capacitor is in balanced condition.                                                                                                 |

|             | <ul> <li>b. When modulation index is 0.5≤m&lt;0.8, both<br/>medium and small vectors are active vectors.</li> </ul>                         |

|             | Due to the presence of medium vectors, the                                                                                                  |

|             | capacitor balancing will be poor.                                                                                                           |

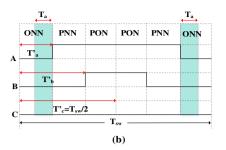

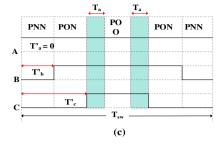

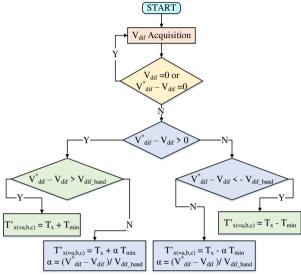

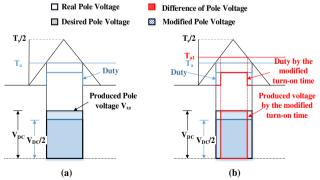

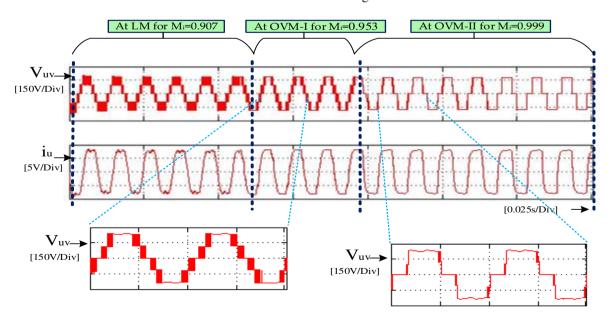

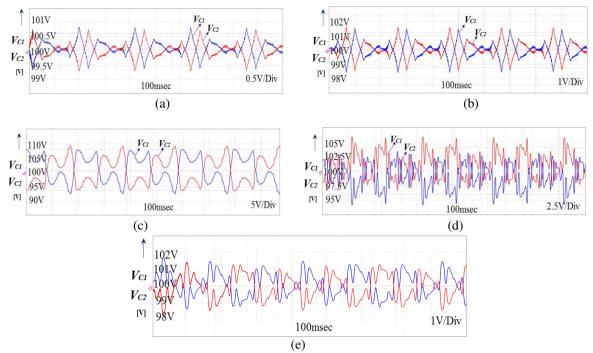

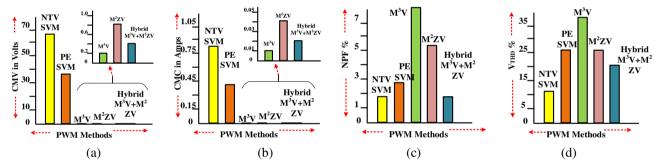

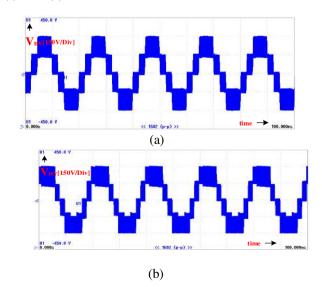

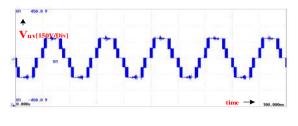

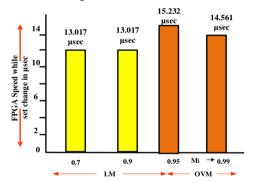

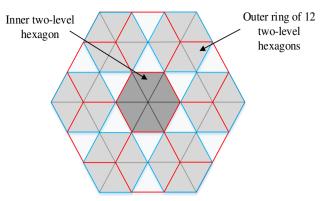

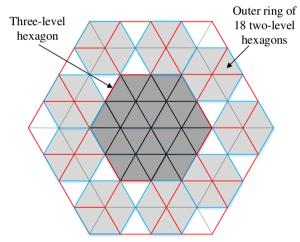

|             | c. When modulation index is 0.8≤m<0.907, the                                                                                                |