# A continuous-time delta-sigma ADC with integrated digital background calibration

Siyu Tan<sup>1</sup><sup>(b)</sup> · Yun Miao<sup>1</sup> · Mattias Palm<sup>2</sup> · Joachim Neves Rodrigues<sup>1</sup> · Pietro Andreani<sup>1</sup>

Received: 29 January 2016/Revised: 3 July 2016/Accepted: 12 July 2016/Published online: 29 July 2016 © The Author(s) 2016. This article is published with open access at Springerlink.com

Abstract This work presents a digital calibration technique in continuous-time (CT) delta-sigma ( $\Delta\Sigma$ ) analog to digital converter. The converter is clocked at 144 MHz with a low oversampling ratio (OSR) of only 8. Dynamic element matching is not efficient to linearize the digital to analog converter (DAC) when the OSR is very low. Therefore, non-idealities in the outermost multi-bit feedback DAC are measured and then removed in the background by a digital circuit. A third-order, four-bit feedback, single-loop CT  $\Delta\Sigma$  converter with digital background calibration circuit has been designed, simulated and implemented in 65 nm CMOS process. The maximum simulated signal-to-noise and distortion ratio is 67.1 dB within 9 MHz bandwidth.

**Keywords** Delta-sigma modulator · Continuous-time · Digital calibration · Background calibration

# **1** Introduction

Delta-Sigma ADCs have increased in popularity in recent years. These converters typically use higher order structures with multi-bit quantizers. Higher SNDR is achieved, while maintaining a lower clock speed. Therefore, multi-bit feedback DACs are required. The linearity of the multi-bit DACs are crucial to reach a high performance for the converter. Especially the linearity of the outermost DAC lies in the feedback loop impairs the SNDR the most.

Siyu Tan siyu.tan@eit.lth.se Mismatches in this DAC is directly fed into the system in parallel with the input signal.

A possible technique to mitigate the non-linearity is using DEM. However, the effectiveness is limited in a system with very low OSR. In this work, a digital calibration circuit is implemented to compensate for mismatches in the outermost DAC. These mismatches are estimated using digital cross-correlation between the digital output and an externally injected pseudo random test signal. It then been subtracted from the converter's output in the digital domain to regain the target SNDR. In [1], the digital block is implemented in an external FPGA to calibrate the modulator. However the effectiveness of the background calibration is limited, due to the imperfect test signal cancelation. This work has a synthesised and placeand-routed digital algorithm, integrated with the modulator on a single chip.

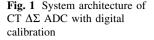

Figure 1 shows the system architecture of the proposed converter. The analog part design will be briefly described in Sect. 2. The shadowed digital part is generated using digital design flow. It provides the calibration function to the outermost feedback DAC ( $DAC_1$  in Fig. 1) and the detail of this part will be discussed in Sect. 3.

# 2 Analog modulator architecture

## 2.1 CT loop filter

The initial phase in  $\Delta\Sigma$  ADC design is choosing a proper loop filter. The design specification is to achieve more than 60 dB SNDR in 9 MHz bandwidth. CT loop filters have speed advantages over their discrete-time (DT) counterparts, enabling a higher clock rate or a lower power consumption [3]. A noise transfer function (NTF) should be

<sup>&</sup>lt;sup>1</sup> Lund University, Box 118, 221 00 Lund, Sweden

<sup>&</sup>lt;sup>2</sup> Ericsson Research, Lund, Sweden

chosen to determine the noise shaping of the spectrum. The NTF was synthesised and simulated using the Delta-Sigma toolbox [3] presented in [4], which resulted in a 3rd order, 4-bit feedback modulator with an OSR of 8. The NTF is shown in (1).

$$NTF = \frac{(z-1)(z^2 - 1.908z + 1)}{(z - 0.1808)(z^2 - 0.02173z + 0.08153)}$$

(1)

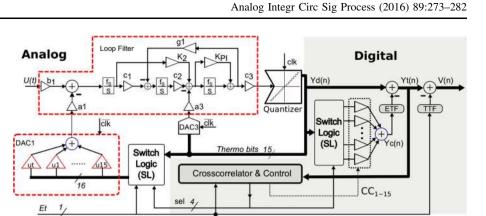

This NTF is then mapped to a cascaded integrators with distributed feedback (CIFB) architecture in DT, as the architecture shown in Fig. 2(a). Three feedback paths exist in the modulator loop. The equivalent CT architecture is converted from the DT model. The corresponding CT loop filter coefficients are calculated using the impulse invariant transformation [5]. The principle is that the CT and DT impulse responses are identical at the sampling instant. Table 1 illustrates the impulse response of 1st, 2nd and 3rd order DT integration. To simplify the calculation, resonator ( $g_1$  in Fig. 2) is temporarily removed.

Fig. 2  $\Delta\Sigma$  modulator architecture. **a** 3rd order DT CIFB architecture; **b** Optimized 3rd order CT CIFB/FF architecture

**Table 1**1st, 2nd and 3rd orderDT integrator transfer functionsand the impulse responses

| Z-domain                    | Impulse response                             |  |  |

|-----------------------------|----------------------------------------------|--|--|

| $a_{3,DT}(\frac{1}{z-1})$   | <i>a</i> <sub>3,DT</sub>                     |  |  |

| $a_{2,DT}(\frac{1}{z-1})^2$ | $a_{2,DT}(n-1)$                              |  |  |

| $a_{1,DT}(\frac{1}{z-1})^3$ | $a_{1,DT}(\frac{n^2}{2} - \frac{3}{2}n + 1)$ |  |  |

Non return-to-zero (NRZ) feedback pulses is generated using the DACs. The impulse response of the CT integration with direct path excess loop delay (ELD) compensation is listed in Table 2. The parameters  $\alpha$  and  $\beta$  represent the start and stop time of the feedback pulse respectively, which are normalized to the clock period  $T_s$ . For example, if there is no ELD,  $\alpha = 0$  and  $\beta = 1$ ; If there exists half clock cycle ELD, then  $\alpha = 0.5$  and  $\beta = 1.5$ . For the first sample (n = 1), however, an additional parameter  $\gamma_i = min(\beta_i, 1)$  is necessary to guarantee a correct impulse response calculation.

In the design optimization, the second feedback path, which should be placed in the middle, is omitted. Instead, a direct feed-forward path from the first integrator's output to the summation point before the third integrator ( $K_2$  path in Fig. 2(b)) is added [6]. In consequence, this operation yields a lower signal swing at the output of the first integrator, due to the lack of subtraction with the feedback signal.

#### 2.2 Excess loop delay

Due to the non-zero response time of transistors in the quantizer, the ELD between the quantizer clock and the DAC feedback current would affect the equivalence between CT modulator loop filter and its DT counterpart. ELD degrades the performance of the modulator and can even lead to an unstable modulator [7]. Therefore, in this design, a fixed half clock cycle delay between the quantizer and the feedback DACs is allocated. To realise the original

Table 2The transfer functionsof rectangular pulse DACfeedback through direct path,and through 1st, 2nd and 3rdorder CT integrators in Laplacedomain, and the impulseresponses

| S-domain                                                                             | Impulse response $(n = 1)$                                                                                     | Impulse response $(n \ge 2)$                                                         |  |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| $\frac{a_{4,CT}}{s}(e^{-s\alpha_4T}-e^{-s\beta_4T})$                                 | <i>a</i> <sub>4,<i>CT</i></sub>                                                                                | 0                                                                                    |  |

| $\frac{a_{3,CT}}{s}(e^{-s\alpha_3T}-e^{-s\beta_3T})\frac{1}{s}$                      | $a_{3,CT}(\gamma_3-\alpha_3)$                                                                                  | $a_{3,CT}(\beta_3-\alpha_3)$                                                         |  |

| $\frac{a_{2,CT}}{s} \left( e^{-s\alpha_2 T} - e^{-s\beta_2 T} \right) \frac{1}{s^2}$ | $a_{2,CT}[(\gamma_2-lpha_2)n+rac{lpha_2^2-\gamma_2^2}{2}]$                                                    | $a_{2,CT}[(eta_2-lpha_2)n+rac{lpha_2^2-eta_2^2}{2}]$                                |  |

| $\frac{a_{1,CT}}{s} \left( e^{-s\alpha_1 T} - e^{-s\beta_1 T} \right) \frac{1}{s^3}$ | $\frac{a_{1,CT}}{2}[(\gamma_1 - \alpha_1)n^2 + (\alpha_1^2 - \gamma_1^2)n + \frac{\beta_1^3 - \alpha_1^3}{3}]$ | $rac{a_{1,CT}}{2}[(eta_1-lpha_1)n^2+(lpha_1^2-eta_1^2)n+rac{eta_1^3-lpha_1^3}{3}]$ |  |

NTF, the basic idea is to insert a fast feedback loop around the quantizer [8]. However, such implementation requires one additional high-speed DAC, which consumes extra chip area and power. On the contrary, a feed-forward proportional path (PI path) bypassing the third integrator ( $K_{PI}$  path in Fig. 2(b)) is implemented, as proposed in [9]. The feedback signal propagate through  $DAC_3$  and the PI path to act as a direct feedback around the quantizer. It shows identical simulation result in both approaches. Only additional resistors are required instead of a DAC, which benefits both in area and power consumption. The optimized CT CIFB/FF architecture with ELD compensation is plotted in Fig. 2(b).

## 2.3 Switch logic

The switch logic block (SL), routes an external single-bit test signal to a selected unit cell in the DAC, and controls the calibration in digital domain. This enables the converter to sequentially determine the gain of each unit cell. One SL block is placed between the quantizer and the outermost DAC. A similar one is implemented in the digital domain to match the calibration coefficients with the corresponding bit lines. The 4-bit selection signal, released by a digital control unit, controls both SL blocks. It guarantees synchronised signal routing and correct mismatch correction.

## **3** Digital calibration

Error shaping and error correction are the two major techniques for linearizing  $\Delta\Sigma$  modulator. Error shaping technique, also known as DEM, works very reliable, but the performance is limited in low OSR designs [10]. Error correction techniques can be implemented in either the analog or the digital domain. When errors are compensated in the digital domain, the mismatch error to be corrected should be determined in advance. The method of determining individual unit element mismatch in this work is employing the correction techniques with an approach similar to that presented in [1]. The functionality is as follows.

## 3.1 Algorithm

As shown in Fig. 1,  $DAC_1$  is extended by one additional unit element *ut*. This extension allows the insertion of a single-bit test signal  $E_t$  into the modulator through one selected DAC unit element routed by SL block, without interfering with the loop behaviour. The inserted additional unit element becomes a part of the system and is used on the fly for background calibration. However, one drawback is that the input dynamic range is slightly reduced by 0.5 dB, because the test bit is processed in parallel with the input.

The feedback DACs can be expressed as a combination of unit gain elements. Each unit element amplifies the corresponding bit line. Therefore, the gain mismatches of these unit elements must be estimated. A single bit pseudo random test signal  $E_t$  is injected into the modulator along with the actual input U(t).  $E_t$  is limited to low frequencies (deep in-band) of the modulator bandwidth, where the signal transfer function (STF) is flat. After it is inserted through a selected unit element, it appears at the output of the  $\Delta\Sigma$  modulator. The test signal is uncorrelated with the input signal. Therefore, a characteristic value of individual gain of the unit element under test is calculated through the cross-correlation between test signal  $E_t$  and the digital output signal.

#### 3.1.1 Calibration factors

The calibration relies on cross-correlation as presented in [11]. The cross-correlation between  $E_t$  and  $Y_t$  (see Fig. 1) is:

$$CCF_i = \sum_{n=1}^{L} E_t(n)Y_t(n) \approx k_i s_{E_i}^2, \quad i = t, 1, 2, \dots, 15$$

(2)

where  $CCF_i$  is the cross-correlation factor for  $DAC_1$  unit element *i*,  $k_i$  is the individual gain of the unit element under test, and  $s_{E_i}^2$  is the variance of the inserted test signal. In the design,  $L = 2^{18}$  samples are grouped as one *set* for computing the cross-correlation for one unit element. 16 sets are regarded as one *frame*. Test signal patterns are identical for every set in one frame. Therefore, in (2), the  $CCF_i$  is directly proportional to the gain  $(k_i)$  of each DAC unit element. The  $CCF_t$  is chosen as a reference, and (3) relates  $CCF_i$  to  $CCF_t$  to reveal the mismatch which is also the calibration coefficient  $CC_i$  for DAC unit element *i*:

$$CC_i = k \left( \frac{CCF_i}{CCF_t} - 1 \right) + CC'_i, \quad i = 1, 2, ..., 15$$

(3)

where  $CC'_i$  is the calibration coefficient calculated from previous iteration, and k is the ideal unit gain factor. The  $CC_i$  are stored in the registers.

## 3.1.2 Digital calibration

In Fig. 1, each  $CC_i$  is multiplied with a corresponding bit in  $Y_d$ , which is routed by the SL block. The calibrate value  $Y_c$  is then the summation of these multiplications:

$$Y_c = \sum_{i=1}^{15} Y_d[i] \times CC_i \tag{4}$$

where  $Y_d[i]$  represents the *i*th bit in 15-bit thermometer coded  $Y_d$ . The calibrated value  $Y_c$  is a 17-bit binary signal, where the first 5 bits represent the signed integer, while the following 12 bits contain the fraction of calibration.

After the calculation,  $Y_c$  passes through an error transfer function (ETF), which contains unit delays. It is because the in-band mismatches are injected into the system in parallel with input U and are shaped by a flat STF. The test input can be regarded as an additional deep in-band input, so the same principle applies to the test transfer function (TTF) as well.

The digital output is the subtraction from the quantizer output with calibration and test signal:

$$V(n) = Y_d(n) - Y_c(n) \times ETF - E_t \times TTF$$

(5)

As the calibration runs in background, each iteration increases the accuracy of  $CC_i$  and V continuously approaches the mismatch-free result.

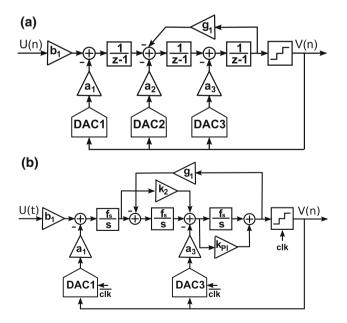

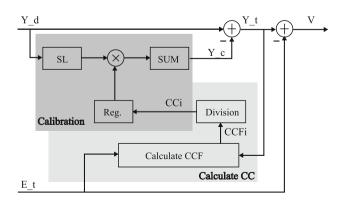

Fig. 3 Digital part block diagram

#### **3.2 Implementation**

Figure 3 is the block diagram of the digital calibration system implementation. The major task is to implement two equations, cross-correlation (2) and calibration coefficient calculation (3).

The implementation of cross correlation is done in two steps: the multiplication and the accumulation. In the multiplication, the multiplicand  $E_t(n)$  is either '0' or '1'. Therefore, the multiplication is done simply by changing the sign of  $Y_t(n)$  accordingly using a multiplexer. The accumulation is performed sequentially as:

$$CCF_{i}(n) = \begin{cases} CCF_{i}(n-1) + Y_{t}(n), E_{t}(n) = 1\\ CCF_{i}(n-1) - Y_{t}(n), E_{t}(n) = 0 \end{cases}$$

(6)

where  $CCF_i(n-1)$  and  $CCF_i(n)$  represent the previous and current accumulation value respectively.

To implement (3), a division block is necessary. The division module is built based on Newton-Raphson algorithm [12, 13], which is briefly described here. Newton-Raphson division is a division method using functional iteration. The division can be written as the product of the dividend and the reciprocal of the divisor. In the algorithm, a priming function is chosen, which has a root at the reciprocal. By efficiently computing the reciprocal of the divisor, the quotient Q can be computed as in (7).

$$Q = \frac{N}{D} = N \times \frac{1}{D} \tag{7}$$

Consider the priming function:

$$f(X) = \frac{1}{X} - D \tag{8}$$

where the root of f(X) is the divisor reciprocal  $\frac{1}{D}$ . The Newton-Raphson equation is given by:

$$X_{i+1} = X_i - \frac{f(X_i)}{f'(X_i)}$$

(9)

f(X) is continuously differentiable around the root, and the derivative at that root is not zero. Newton-Raphson equation converges quadratically. Applying (8) to (9), this iteration can be used to find an approximation to the reciprocal:

$$X_{i+1} = X_i + \frac{\frac{1}{X_i} - D}{\frac{1}{X_i^2}} = X_i \times (2 - D \times X_i)$$

(10)

The error in the reciprocal decreases quadratically after each iteration.

In (3), the reference value  $CCF_t$  for calculating  $CC_i$ , is a cross-correlation result of the first set sample with the test pattern. It is a constant denominator D in (7). Therefore, division is only calculated once per frame of data.

#### **4** Circuit level implementation

#### 4.1 Amplifiers

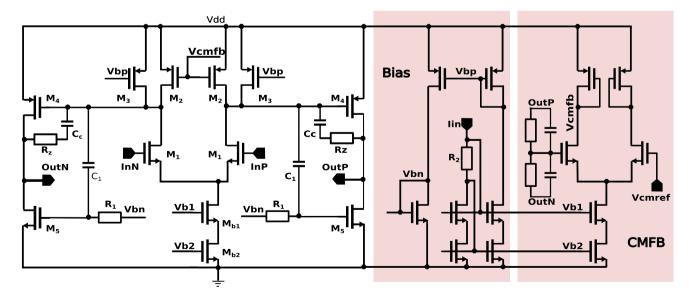

Various amplifier architectures have been studied and evaluated. The first integrator in the loop filter handles the input and feedback signal, and the non-linearity in this stage directly degrade the system's SNDR, which requires high linearity. The last integrator must drive large input capacitors in the multi-bit quantizer, which demands a high driving capability amplifier in the integrator. To meet these requirements, all three amplifiers in the integrators share the same two-stage, Miller-compensated, class-AB output architecture [14], while the bias current is unique for each amplifier to balance the speed, area and power consumption. The schematic is shown in Fig. 4. Tail current sources are cascoded to provide a stable bias current. Common mode feedback (CMFB) circuit senses the common mode voltage of the outputs and controls a part of the input differential stage's active load. This reduces the CMFB gain, which makes the CMFB easier to stabilize [15].

In the simulation, the gain bandwidth product (GBW) of the three amplifiers are individually swept to study the impact on SNDR. The first amplifier has the highest linearity requirements. The last amplifier should be fast because it handles the PI path. The second integrator has a lower GBW requirement. It does not have to drive a low impedance load and any nonlinearity is suppressed by the loop filter. The optimized GBW of the three amplifiers are 600, 350 and 600 MHz, respectively.

#### 4.2 Flash quantizer

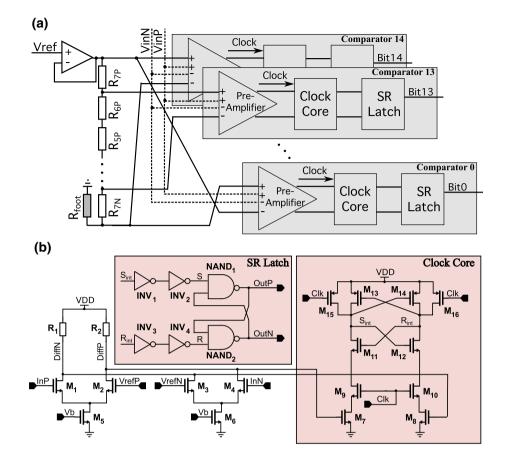

The four-bit mid-rise flash quantizer consists of 15 comparators, and the block diagram is shown in Fig. 5(a). A resistor ladder provides reference levels to the comparators, and an external control voltage  $V_{ref}$  controls the reference range. Each comparator is formed by a pre-amplifier, a clocked core and a SR latch, as seen in Fig. 5(b) [16]. The pre-amplifier senses the input and the reference voltage. When clock is low,  $M_{15}$  and  $M_{16}$  drive  $R_{int}$  and  $S_{int}$  nodes to VDD. At the clock rising edge, either  $M_7$  or  $M_8$  is conducting depending on the voltage of node *DiffP* and *DiffN*. Therefore, the decision is made at this instant and the cross-couple pair  $M_{11}-M_{14}$  keep forcing  $S_{int}$  and  $R_{int}$  to be '1' or '0'. The SR latch then latches this value for one clock cycle.

## 4.3 DAC

In the CIFB architecture, the outer-most feedback DAC is a critical component, since its linearity dominates the modulator's performance. The widely used high-speed DAC type is the current-steering DAC, which contains unit elements consisting of MOS transistors operating as current sources.

In this work, a resistive current-mode DAC is chosen. Resistors in the unit elements generate a current, corresponding to the digital value on the input bit line, which is fed into the integrators. Compared to the current-steering DAC, the resistive DAC has less thermal noise [5]. Each unit element is formed by two parts: a D-flip-flop updates

Fig. 4 Fully differential operational amplifier schematic, including bias and CMFB circuit

- Fig. 5 Four-bit flash quantizer.

- a Quantizer architecture;

- **b** Comparator schematic

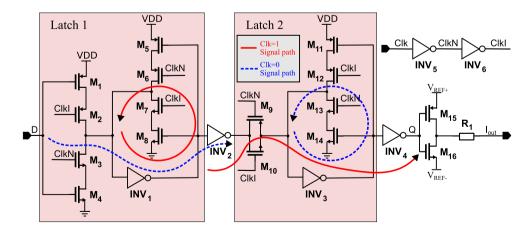

one sample at the clock edge, and the resistor converts the DAC reference voltage into the unit current [17]. The output of all the unit elements are connected together, which performs current summation of all the unit currents. This output current is injected directly into the virtual ground node of the integrator. The DAC unit element schematic is shown in Fig. 6. Two latches form a D-flip-flop, which stores a sample at each clock rising edge.  $I_{out}$

node is connected to the integrator's input, which can be regarded as a virtual ground and has a constant common mode voltage  $V_{CM}$ . Thus, depending on the voltage on node Q, an unit current will flow into or out of the integrator, as (11) shows.

$$I_{out} = \begin{cases} (V_{REF+} - V_{CM})/R_1, V(Q) = 0\\ (V_{REF-} - V_{CM})/R_1, V(Q) = 1 \end{cases}$$

(11)

Fig. 6 Resistive DAC unit element schematic. Signal paths are represented by dash and solid lines based on two different clock levels

Fig. 7 Clock gating architecture

#### 4.4 Digital synthesis and place and route

In the digital synthesis, standard cells are used. Standard threshold voltage (SVT) libraries are chosen, due to the balance between speed and power consumption. To fit timing, pipelines are implemented between the building blocks on the long critical paths.

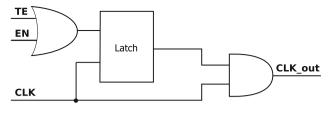

Furthermore, clock gating is utilized. Clock gating is a technique generally used for saving dynamic power dissipation on flip-flops by gating off the input clocks [18]. It is implemented with a combination of an AND gate and a latch to avoid glitches on the clocks. The architecture is illustrated in Fig. 7, where *TE* is test enable input, *EN* is enable input, *CLK* is clock input, *CLK\_out* is the gated clock output.

In this implementation, clock gating is done by inserting a clock gating cell into the  $CC_i$  calculation module, to disable the clock for certain blocks. For example, division module is not always in use. As discussed in Sect. 3.2, the division is invoked once in one frame of data. The multiplication of  $\frac{CCF_i}{CCF_i}$  and k (as in (3)) is also occasionally used. It is called once every set of samples. Therefore, the clock for these modules is disabled when not in use.

## 5 Simulation

#### 5.1 Simulation in Matlab

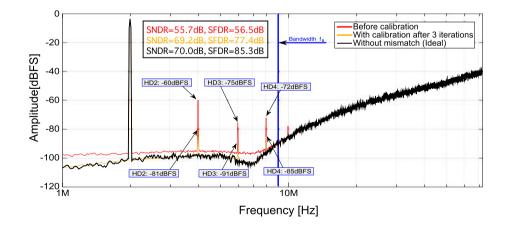

The system is verified using Simulink in Matlab. Random mismatches are added to the unit elements in  $DAC_1$ , which produces varying feedback gain. The unit element mismatch is set to 2 %, a pessimistic estimation of the real mismatch during chip fabrication. The input signal has an amplitude of -3 dB full scale (FS). Without calibration, a large distortion is clearly seen from the spectrum plotted in Fig. 8. After 3 iterations of digital calibration with the limited calculation accuracy (the same accuracy as in the digital implementation in VHDL), the simulated SNDR is improved by 13.5 dB, and spurious-free dynamic range

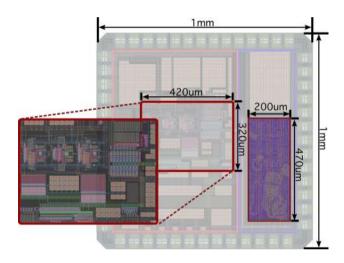

Fig. 9 Layout of the system, with an enlarged *box* showing the analog modulator core

Fig. 8 System level simulation in Matlab with 2 % unit element mismatch in the outer-most DAC. Original spectrum has SNDR of 55.7 dB (*red line*), spectrum of DAC calibration after 3 iterations has SNDR of 69.2 dB (*yellow line*) and the ideal spectrum has SNDR of 70 dB (*black line*) (Color figure online)

Total Power: 6.2mW

Total Active Area: 161468um<sup>2</sup>

(SFDR) by 20.9 dB. There is less than 1 dB SNDR difference comparing with an ideal mismatch-free spectrum.

### 5.2 Digital block verification

In this design, the digital block can be regarded as a standalone part. It is not inside the modulator loop and only slow varying control signals control the SL block in the analog part. The digital verification is done by comparing the digital behaviour model output and the result of Matlab output with the same accuracy and the same input data. They have identical results as expected.

# 6 Layout

The modulator with the digital calibration circuit has been implemented in 65 nm CMOS technology, as illustrated in Fig. 9. The modulator circuit is enlarged in the figure. The gaps between the active region and the pad frame are filled with decoupling capacitors, which stabilize the supply and bias voltage. In total 53 pads are placed in the pad ring,

Table 3 Performance comparison with other CT  $\Delta\Sigma$  modulators

| Parameter               | This work | [ <b>19</b> ] | [20] | [21] |

|-------------------------|-----------|---------------|------|------|

| Fs (MHz)                | 144       | 288           | 1152 | 600  |

| BW (MHz)                | 9         | 9             | 9    | 10   |

| SNDR (dB)               | 67.1      | 69            | 72   | 78   |

| Power (mW)              | 6.2       | 7.5           | 17   | 16   |

| Area (mm <sup>2</sup> ) | 0.16      | 0.08          | 0.07 | 0.36 |

| FOM (fJ/conversion)     | 180.3     | 181           | 290  | 125  |

| Technology (nm)         | 65        | 65            | 65   | 90   |

where 16 pads are used for the calibrated digital output signal.

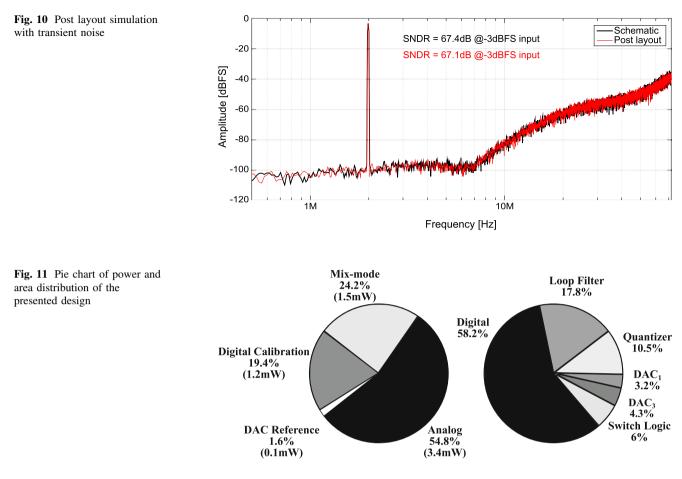

The post-layout simulation spectrum is plotted in Fig. 10, with an input sine wave at 2 MHz and transient noise activated. The NTF peaking visible in high frequency is caused by finite GBW of the amplifiers and the additional delay existing in the feedback DACs. The SNDR is 67.1 dB within 9 MHz signal bandwidth.

Figure 11 illustrates the power and area distribution of the presented design. Total power is 6.2 mW and total active area is 0.16 mm<sup>2</sup>. Analog circuits, which include the

loop filter and the bias circuit, consume the most power. One fifth of the total power is contributed by the proposed digital circuit. The digital calibration block occupies a relatively large area, which will be optimized to a denser design in the future.

Based on the result from the post layout simulation, the effective number of bits (ENOB) is

$$ENOB = \frac{SNDR - 1.76}{6.02} = 10.9 \, bits \tag{12}$$

and the figure of merit (FOM) is

$$FOM = \frac{P}{(2^{\text{ENOB}} \times 2f_{\text{B}})} = 180.3 \, fJ/conversion \tag{13}$$

The performance of the modulator is summarized in Table 3.

## 7 Conclusion

This work integrates both analog and digital circuits in a single layout in 65 nm CMOS technology, providing background digital calibration to correct for non-linearity in the DAC. A mismatch of 2 % is successfully calibrated, thereby improving the SNDR by 13.5 dB compared with a calibration deactivated system. The presented  $\Delta\Sigma$  converter post layout simulates 67.1 dB SNDR over 9 MHz bandwidth. The total active area is 0.16 mm<sup>2</sup> and the system consumes 6.2 mW power in 1.2 V supply voltage, including an 1.2mW digital calibration core.

**Open Access** This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://crea tivecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

#### References

- 1. Kauffman, J. G., Witte, P., Becker, J., & Ortmanns, M. (2011). An 8.5 mW continuous-time  $\Delta\Sigma$  modulator with 25 MHz bandwidth using digital background DAC linearization to achieve 63.5 dB SNDR and 81 dB SFDR. *IEEE Journal of Solid-State Circuits*, 46(12), 2869–2881.

- Ortmanns, M., & Gerfers, F. (2005). Continuous-time sigma-delta A/D conversion: Fundamentals, performance limits and robust implementations. Dordrecht, The Netherlands: Springer.

- Schreier, R. (2000). The delta-sigma toolbox for matlab. http:// www.mathworks.com/matlabcentral/fileexchange/. Accessed 05 June 2016.

- 4. Schreier, R., & Temes, G. (2004). Understanding delta-sigma data converters. New York: Wiley.

- 5. Andersson, M., Sundström, L., Anderson, M., & Andreani, P. (2013). Theory and design of a CT  $\Delta\Sigma$  modulator with low sensitivity to loop-delay variations. *Analog Integrated Circuits and Signal Processing*, 76(3), 353–366.

- Munoz, F., Philips, K., & Torralba, A. (2004). A 4.7 mW 89.5 dB DR CT complex ΔΣ ADC with built-in LPF. *IEEE International Solid-State Circuits Conference (ISSCC) Digital Technical Papers*, 1, 500–613.

- Cherry, J. A., & Snelgrove, W. M. (1999). Excess loop delay in continuous-time delta-sigma modulators. *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, 46(4), 376–389.

- Pavan, S. (2008). Excess loop delay compensation in continuoustime delta-sigma modulators. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 55(11), 1119–1123.

- 9. Vadipour, M., Chen, C., Yazdi, A., Nariman, M., Li, T., Kilcoyne, P., & Darabi, H. (2008). A 2.1 mw/3.2 mw delay-compensated gsm/wcdma  $\Delta\Sigma$  analog-digital converter. *IEEE Symposium on VLSI Circuits* (pp. 180–181).

- Maloberti, F. (2007). *Data converters*. Dordrecht, The Netherlands: Springer

- Witte, P., & Ortmanns, M. (2010). Background DAC error estimation using a pseudo random noise based correlation technique for sigma-delta analog-to-digital converters. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 57(7), 1500–1512.

- Oberman, S. F., & Flynn, M. J. (1997). Division algorithms and implementations. *IEEE Transations on Computers*, 46(8), 833–854.

- Cheng Wang, L., Cai Lin, Y., & Gang Jiang, W. (2011). Implementation of fast and high-precision division algorithm on FPGA. *Computer Engineering*, *37*(10), 240–242.

- Andersson, M., Anderson, M., Sundström, L., Mattisson, S., & Andreani, P. (2014). A filtering ΔΣ ADC for LTE and beyond. *IEEE Journal of Solid-State Circuits*, 49(7), 1535–1547.

- Gray, P. R., Hurst, P. J., Lewis, S. H., Meyer, R. G. (2009). *Analysis and design of analog integrated circuits* (5th ed). New York: Wiley.

- Cho, T., & Gray, P. (1995). A 10 b, 20 msample/s, 35 mw pipeline a/d converter. *IEEE Journal of Solid-State Circuits*, 30(3), 166–172.

- 17. Pavan, S., Krishnapura, N., Pandarinathan, R., & Sankar, P. (2008). A power optimized continuous-time  $\Delta\Sigma$  adc for audio applications. *IEEE Journal of Solid-State Circuits*, 43(2), 351–360.

- Man, X., & Kimura, S. (2011). Comparison of optimized multistage clock gating with structural gating approach. *TENCON* 2011–2011 IEEE Region 10 Conference, pp. 651–656.

- 19. Andersson, M., Anderson, M., Sundström, L., & Andreani, P. (2012). A 7.5 mw 9 mhz ct  $\Delta\Sigma$  modulator in 65 nm cmos with 69 db sndr and reduced sensitivity to loop delay variations. *Solid State Circuits Conference (A-SSCC), 2012 IEEE Asian*, pp. 245–248.

- Taylor, G., & Galton, I. (2010). A mostly-digital variable-rate continuous-time delta-sigma modulator adc. *IEEE Journal of Solid-State Circuits*, 45(12), 2634–2646.

- 21. Reddy, K., Rao, S., Inti, R., Young, B., Elshazly, A., Talegaonkar, M., & Hanumolu, P. K. (2012). A 16mw 78db-sndr 10mhz-bw ct-  $\Delta\Sigma$  adc using residue-cancelling vco-based quantizer. *Solid-State Circuits Conference Digest of Technical Papers* (*ISSCC*), 2012 IEEE International, pp. 152–154.

Siyu Tan was born in Beijing, China in 1990. He accomplished his bachelor study in Beijing University of Post and Telecommunications (BUPT) and received the B.Sc. in 2012. He received the M.Sc. degree in LUND University, Sweden in 2014 with a master's thesis focuses on continuous-time Delta-Sigma AD converter. He started doctoral study in Dept. of Electrical and Information Technology (EIT). Lund University, Sweden in 2015. His

Yun Miao received the Bache-

lor degree in electrical engi-

neering from Polytechnic of

Turin, Italy, in 2012. Then he received the M.Sc. degree in

Electrical Engineering from

Lund University, Sweden, in 2014 after completing his Master's thesis on digital calibration

then he chases his career as a Digital IC designer in GN

Mattias Palm (Andersson prior

to 6/6-2014) (S'09-M'13) was

born in 1982 in Lund, Sweden.

He received the M.S.E.E.

degree in Electrical Engineering

and the Ph.D. degree in circuit

design from Lund University in

2006 and 2014, respectively.

His doctoral studies focused on

the design of continuous-time

delta-sigma modulators for wireless communication. From 2006 to 2009, he was an Analog/RF IC Design Engineer with the TX-group of Cambridge

Resound A/S in Denmark.

continuous-time Delta-Sigma A/D converter. Since

main research interests include high speed circuit design and mixed signal design.

for

Silicon Radio (CSR) in Lund. Since 2014, he is with Ericsson

Research in Lund, performing research and development of integrated circuits. His research interest is towards analysis, modelling and design of high-performance data-converters and RF ASIC systems.

Joachim Neves Rodrigues  $(S^100-M^105-SM^111)$  received the Ph.D. degree in circuit design from Lund University, Lund, Sweden, in 2005. Currently, he is an Associate Professor in the Department of Electrical and Information Technology, Lund University. From 2005 to 2008, he acted as ASIC process lead in the Digital ASIC Department at Ericsson Mobile Platforms, Lund, Sweden. He rejoined his current department in 2008, and is cur-

rently the Program Director for System-on-Chip. His main research interests are modeling and implementation of digital and mixed-mode microelectronics, architectures for high performance ultra-low voltage designs, with a focus on biomedical circuits and systems. Dr. Rodrigues is a TC member of the Biomedical Circuits and Systems Society since 2010, and Chair of the Swedish SSC chapter.

Pietro Andreani received the M.S.E.E. degree from the University of Pisa, Italy, in 1988, and the Ph.D. degree from the Dept. of Electrical and Information Technology (EIT), Lund University, Sweden, in 1999. Between 2001 and 2007, he was Chair Professor with the Center for Physical Electronics. Technical University of Denmark. He was also a part-time IC designer at Ericsson Modems in Lund (2005-2014). Since 2007, he has been an Associate

Professor in IC design at EIT. He was a TPC member of ISSCC (2007-2012), guest editor of JSSC (Dec. 2012), and is a TPC member of ESSCIRC and RFIC.