# **Open Access Articles**

# A Continuous-Time Delta-Sigma Modulator for Biomedical Ultrasound Beamformer Using Digital ELD Compensation and FIR Feedback

The Faculty of Oregon State University has made this article openly available. Please share how this access benefits you. Your story matters.

| Citation     | Zhang, Y., Chen, C. H., He, T., & Temes, G. C. (2015). A Continuous-Time Delta-Sigma Modulator for Biomedical Ultrasound Beamformer Using Digital ELD Compensation and FIR Feedback. IEEE Transactions on Circuits and Systems I: Regular Papers, 62(7), 1689-1698. doi:10.1109/TCSI.2015.2434100 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DOI          | 10.1109/TCSI.2015.2434100                                                                                                                                                                                                                                                                         |

| Publisher    | IEEE - Institute of Electrical and Electronics Engineers                                                                                                                                                                                                                                          |

| Version      | Accepted Manuscript                                                                                                                                                                                                                                                                               |

| Terms of Use | http://cdss.library.oregonstate.edu/sa-termsofuse                                                                                                                                                                                                                                                 |

# A Continuous-Time Delta-Sigma Modulator for Biomedical Ultrasound Beamformer Using Digital ELD Compensation and FIR Feedback

Yi Zhang, Student Member, IEEE, Chia-Hung Chen, Member, IEEE, Tao He, Student Member, IEEE, and Gabor C. Temes, Life Fellow, IEEE

Abstract—This paper presents the design of a continuous-time  $\Delta\Sigma$  modulator (CTDSM) to be used in an ultrasound beamformer for biomedical imaging. To achieve better resolution, the prototype modulator operates at 1.2 GHz. It incorporates a digital excess loop delay (ELD) compensation to replace the active adder in front of the internal quantizer. A digitally controlled reference-switching matrix, combined with the dataweighted averaging (DWA) technique, results in a delay-free feedback path. A multi-bit FIR feedback DAC, along with its compensation path, is used to achieve lower clock jitter sensitivity and better loop filter linearity. The modulator achieves 79.4 dB dynamic range, 77.3 dB SNR and 74.3 dB SNDR over a 15 MHz signal bandwidth. Fabricated in a 65 nm CMOS process, the core modulator occupies an area of only 0.16 mm<sup>2</sup> and dissipates 6.96 mW from a 1 V supply. A 58.6 fJ/conversion-step figure of merit is achieved.

Index Terms—Ultrasound beamformer, continuous-time  $\Delta\Sigma$  modulator, digital excess loop delay compensation, FIR feedback DAC

# I. INTRODUCTION

MEDICAL ultrasound imaging is commonly used for obtaining diagnostic medical images, as a compact and affordable diagnostic tool. It uses beamforming techniques to construct an image of the interrogated medium.

The function of the beamforming receiver is to amplify and demodulate the separate echo signals, provide the proper time delay in each channel, and add the signals. Conventional digital beamformers use Nyquist rate ADCs as an interpolation filter to effectively up-sample the digital sample, so that accurately delayed samples are acquired [1][2]. However, this requires increased hardware complexity.

Oversampling  $\Delta\Sigma$  ADCs have recently become attractive in signal processing applications due to their simplicity and ease

Manuscript received January 09, 2015. This work was supported by Maxim Integrated.

Y. Zhang, C-H Chen, T. He, and G. C. Temes are with the School of Electrical Engineering and Computer Science, Oregon State University, Corvallis, OR 97331 USA

Copyright © 2015 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending an email to pubs-permissions@ieee.org.

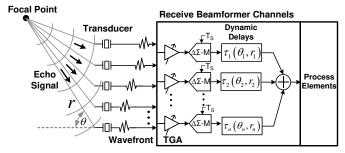

Fig. 1. Block diagram of an ultrasound receiver using dynamic focusing.

of integration [3][4]. As shown in Fig. 1, in the  $\Delta\Sigma$  ADC based beamforming receiver, the digital signal processing circuitry applies dynamic delays to the digitized output of the  $\Delta\Sigma$  modulator in the each channel, so that a coherent combination of the received signals is focused at points along a particular direction of interest [4][5]. In the few reported use of  $\Delta\Sigma$  modulation in biomedical ultrasound beamformers [6][7], the dynamic range was only around 60 dB. In the detection of the blood flow by a pulsed Doppler ultrasound receiver, the ultrasound system sends a signal pulse into the body at  $F_0$ . The returning echo has a very strong component at  $F_0$  from stationary tissue (the vessel walls) and a very weak signal within 1 kHz of  $F_0$  due to the slow blood flow. To detect this weak blood flow signal in the presence of the strong signal from the tissue, it requires a dynamic range larger than 12 bits.

In this work, a continuous-time  $\Delta\Sigma$  modulator (CTDSM) was chosen as a power-efficient solution to achieve 12-bit effective number of bits (ENOB) over the target signal bandwidth (BW = 15 MHz) of the medical ultrasound. However, CTDSM is susceptible to severe non-idealities, such as excess loop delay (ELD) and clock jitter. Their correction in this project will be discussed next.

In this paper, we give the details of the design, which was reported earlier in [13]. The remainder of the paper is organized as follows. Section II gives the architecture of the modulator. Section III provides a brief overview of prior art addressing the excess loop delay issue, and introduces the proposed technique. Section IV presents the FIR filtering applied in the feedback path, along with its compensation. Circuit design details of important building blocks of the prototype are discussed in Section V. Measurement results of the prototype test chip are provided in Section VI. Section VII concludes the paper.

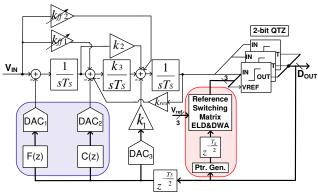

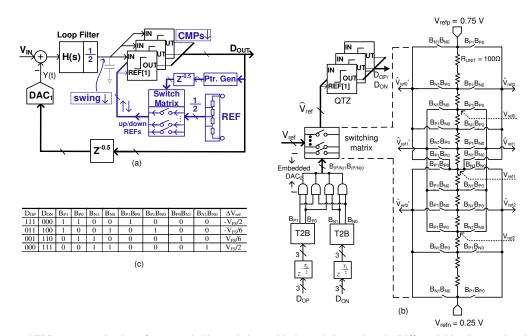

Fig. 2. Block diagram of the proposed CT  $\Delta\Sigma$  modulator using digital ELD compensation and FIR feedback.

#### II. ARCHITECTURE DETAILS

The architecture of the proposed CT  $\Delta\Sigma$  modulator is shown in Fig. 2 [18]. It is well known in loop filter design that the first-order path is usually required to be a fast one, since it largely determines the unity-gain bandwidth of the loop filter, and is essential for the loop stability [8]. Therefore, the parasitic poles of the first-order path may degrade stability [21]. In the conventional Cascade of Integrators with Feedforward (CIFF) topology, the first-order path is implemented by the first integrator feeding the adder at the input of the quantizer. Hence the amplifier used in the first stage integrator is required to be very fast, so as not to limit the unity gain bandwidth of the first-stage integrator. However, the in-band gain of the first-stage integrator also needs to be high enough to provide sufficient attenuation of the non-idealities from the following stages. Hence, it may not be a power-efficient solution to place the first integrator in the high-speed path as in the conventional CIFF topology.

In order to separate the requirements of both high gain and high speed in the first-stage integrator, this work incorporates a  $3^{\text{rd}}$ -order loop filter with combined feedforward and feedback paths. Instead of implementing the fastest first-order path by the first integrator, the first-order path is formed by the feedback path  $k_I$  to the input of the last integrator, which replaces an extra summation node required in the CIFF topology. The input feed-forward path  $k_{ffI}$  and  $k_{ff2}$  help to reduce the swing of the internal state.

In addition, a local resonator path  $k_{res}$  formed by the second and third integrator introduces zeros in the noise transfer function (NTF) to further suppress the in-band quantization noise. The out-of-band gain (OBG) of the NTF is chosen to be 2, allowed by the use of a 2-bit internal quantizer. Data Weighted Averaging (DWA) technique is employed to randomize the unit element mismatch in the feedback DAC. The feedback DAC is implemented with switched-resistors, which have better noise performance and matching under low supply voltage (1 V) than current steering DAC. To counter the RC time constant variation, the digitally tunable integrating capacitor arrays are employed.

The CTDSM suffers from the excess loop delay [9]. A reference-switching matrix for both ELD compensation and

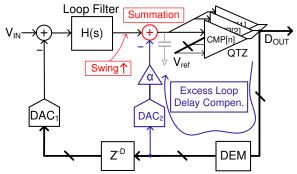

Fig. 3. Block diagram of a general continuous-time  $\Delta\Sigma$  modulator with a direct feedback path to compensate for the ELD [9].

Fig. 4. Prior art. (a) Discrete-time differentiation technique [8] (b) Comparator switching technique [11].

DWA technique is introduced as shown in Fig. 2. In addition, error due to the clock jitter applied in the feedback path increases the in-band noise of CTDSM. To mitigate this effect, a multi-bit FIR filtering path F(z) are employed with its compensation path C(z). Both techniques will be discussed in the following sections.

#### III. EXCESS LOOP DELAY COMPENSATION

#### A. Overview of the Prior Arts

A general block diagram of a continuous-time (CT)  $\Delta\Sigma$  modulator with ELD compensation is depicted in Fig. 3 [9][10]. It contains a CT loop filter H(s) for in-band noise attenuation; an internal quantizer; a feedback DAC; and a dynamic element matching (DEM) block to filter the DAC element mismatch signal. The ELD compensation absorbs the

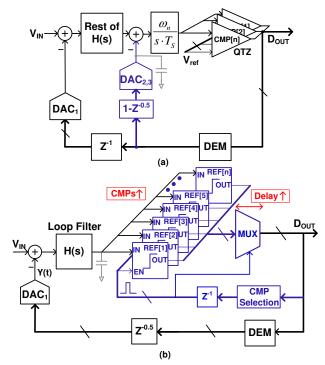

Fig. 5. (a) Proposed ELD compensation by reference-switching technique with the scaled quantizer (b) Differential implementation details of the control logic and reference-switching matrix, in which  $R_{\text{UNIT}} = 100\Omega$  (c) possible digitized output sample and the pointer generated to determine the shifted amount.

signal-dependent delay by introducing an intentional delay  $Z^{-D}$  between the quantizer and feedback DAC. As a result, a direct feedback path around the internal quantizer is necessary to compensate the inserted delay  $Z^{-D}$ . However, this compensation path requires the use of an adder in front of the quantizer. This adder is in the main path, and may introduce a parasitic pole, which is undesirable in high-speed operation.

Several techniques to eliminate the use of this adder have been proposed in recent years [8] [28]. In [8], as illustrated in Fig. 4(a), the addition is shifted to the input node of the last stage integrator using discrete-time differentiation. The pulse of the feedback DAC is first differentiated and then integrated on the capacitor of the last stage integrator, creating a path equivalent to summation in front of the quantizer. In [28], an equivalent feedforward path is introduced by putting a phaselead resistor (PLR) in series with the integrating capacitor in the last stage integrator. Thus it eliminates the use of a summing amplifier in front of the quantizer. Both technique suffer from one drawback: a feed-in path to the last integrator required to implement the ELD compensation. The extra feedin path mandates a wide opamp finite gain bandwidth (FGBW) in the last integrator. In addition, the increased parasitics at the input node of the last integrator make it difficult for this integrator to form the fast first-order feedback path, especially for high speed operation

Instead of using an analog feedback path, [11] proposed a digital ELD compensation method, shown in Fig. 4(b). The summation in front of the quantizer is replaced by a group of switching comparators with fixed reference voltages. The increased number of comparators mandates the following multiplexing of the quantizer outputs. The comparator selection logic takes the previous output sample of the modulator, enables the corresponding comparators upwards or downwards and controls the multiplexer to perform the digital summation for ELD compensation. This technique, however,

requires additional comparators in the quantizer, which results in the increased parasitic loading, and complicates the design of the last integrator. Furthermore, the multiplexing logic in the critical path, as shown in Fig 4(b), adds to the loop delay.

## B. Proposed Digital ELD Compensation

As illustrated in Fig. 5(a) [12][35], rather than switching in or out comparators with fixed reference voltages [11], this work proposes to switch the reference voltages of a fixed set of comparators, which eliminates the following multiplexing as in [11]. A reference-switching matrix, digitally controlled by the pointer generation logic, replaces both the direct feedback path and the signal adder before the quantizer. Fig. 5(b) shows the details of the differential implementation of the reference-switching matrix. In this work, an ELD coefficient α of 0.5, shown in Fig. 3, was implemented. In Fig. 5(b),  $\hat{V}_{refi}$ and  $\hat{V}_{refi}$  represent the differential threshold inputs to the  $i^{th}$ comparator in the quantizer. The full-scale quantization range is  $V_{FS} \triangleq V_{refp} - V_{refn}$ . The reference levels in the resistor string are shifted in the quantizer by an amount  $\Delta V_{ref} \triangleq \hat{V}_{refi} - \hat{V}_{refi}$ ', which is determined by the previous output sample  $D_{OP}/D_{ON}$  of the modulator. In other words, an equivalent summation is realized by shifting up or down the quantizer reference levels by  $\Delta V_{ref}$  given by:

$$\Delta V_{ref} = \alpha \cdot \left[ -V_{FS} - \frac{V_{FS}}{3} \quad \frac{V_{FS}}{3} \quad V_{FS} \right] \times \begin{bmatrix} B_{P1} \cdot B_{P0} \\ B_{P1} \cdot B_{N0} \\ B_{P0} \cdot B_{N1} \\ B_{N1} \cdot B_{N0} \end{bmatrix}$$

(1)

where  $\alpha$  is the ELD compensation coefficient which here is equal to 0.5;  $[-V_{FS} - \frac{V_{FS}}{3} \frac{V_{FS}}{3} V_{FS}]$  are the four quantization levels of the 2-bit quantizer.  $B_{Pi}$  and  $B_{Ni}$  are the converted

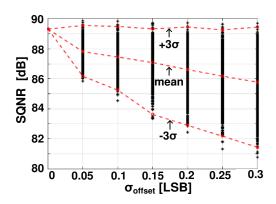

Fig. 6. Simulated SQNR as a function of comparator offsets with the line representing the mean SQNR and SQNR distributed within  $\pm 3\sigma$ .

binary representation of the digitized sample;  $B_{Pi} \cdot B_{Ni}$  are generated by the pointer generation logic, which involves a thermometer-to-binary conversion and an AND logic, as shown in the left part of Fig. 5(b); Fig. 5(c) gives all possible values of  $D_{OP}/D_{ON}$  and pointers  $B_{Pi} \cdot B_{Ni}$ ;  $\Delta V_{ref}$  corresponds to the shift in the reference levels. From (1), one shifted amount is selected out of the first vector for the next quantization based on the current quantized sample output in the second vector. Based on (1), it can further implement the ELD coefficient  $\alpha$  other than 0.5 by changing  $\Delta V_{ref}$  with appropriate design of the adjacent reference levels.

The operation of both the pointer generation logic and the reference-switching matrix is allocated half a clock period, so that the shifted reference voltages are able to settle within the other half a clock period for the next quantization. The unit resistor in the reference matrix, as shown in Fig. 5(b), is chosen to be 100  $\Omega$ , leading to around 420  $\mu$ W of power dissipation. Care has to be taken in the routing so as to minimize the parasitics along the reference-switching path and the resulting settling requirement. The settling error in the reference-switching matrix is approximated by an offset in the quantizer and fortunately it can be suppressed by the preceding loop filter. This technique effectively reduces the number of comparators in the quantizer and as a result, it eliminates the multiplexing logic delay in the critical path.

In the described ELD compensation techniques, however, the swing of the loop filter output is increased in the presence of the direct ELD compensation feedback path. In order to allow the use of a power supply as low as 1 V, the loop filter was scaled down by a factor of 2. Accordingly, the reference voltages of the quantizer were also scaled by the same factor. This effectively scales up the quantizer gain so that the loop gain remains unaffected. This downscaling of the quantizer reference voltages may make the comparator offset requirements harder to meet. However, the number of the comparators used in the quantizer is low, and extensive simulations were made to guarantee that the comparator offset in the quantizer would not be a major source of error in the modulator. For each level of comparator offset, 1000 samples

Fig. 7. Block diagram of (a) Conventional thermometer-code shuffling DWA (b) Reference shuffling DWA.

were simulated as shown in Fig. 6. The broken lines represent the mean SQNRs and the SQNRs distributed within  $\pm 3\sigma$ . It shows that in the quantizer with downscaled reference voltages, even with a 0.3 LSB 1- $\sigma$  offset (12.5 mV), the achieved SQNR is above 80 dB, leaving a 6 dB margin above the target of 12-bit ENOB. Careful sizing of the comparator input pair and common centroid layout technique were used to guarantee minimal degradation of the performance due to the offset of the comparator.

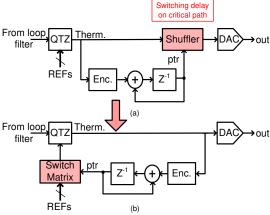

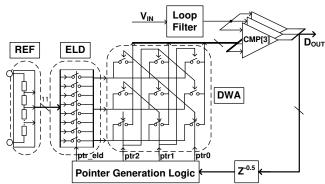

#### C. Reference Shuffling DWA

The use of 2-bit feedback DAC requires data-weighting averaging (DWA) to shape the DAC element mismatch error. In the conventional DWA technique, as shown Fig. 7(a), the thermometer output code of the quantizer is encoded and generates a pointer to select the quantizer output. However, the shuffler functions in the main feedback path, and hence its switching delay contributes to the excess loop delay. At a clock rate of 1.2 GHz, the delay through such a shuffler is comparable to the clock period, and thus significantly reduces the regeneration time budget of the comparators.

The converter described in this work uses a reference-switching matrix to eliminate the element shuffler located in the feedback path [21][22], as shown in Fig. 7(b). Rather than shuffling the thermometer code of the quantizer output, the pointer generation logic follows the DWA rotation algorithm, and drives the switching matrix to shuffle the quantizer reference voltages and obtain the next quantizer output to be applied to the DAC. This technique effectively results in a delay-free path.

Similar to the proposed ELD compensation technique, the pointer generation logic is also employed to manipulate the quantizer reference matrix. Thus, these two reference-switching matrices are merged.

# IV. PROTOTYPE CT $\Delta\Sigma$ ADC WITH FIR FEEDBACK

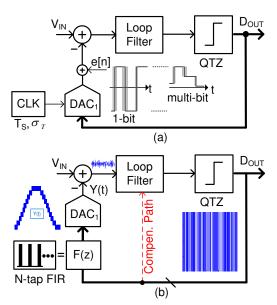

Another design challenge in CT  $\Delta\Sigma$  modulators comes from the error introduced by the jitter-affected clock applied to the feedback DAC. This error is referred to the input without being shaped by the loop filter, as demonstrated in Fig. 8(a). A modulator using multi-level feedback is less susceptible to

Fig. 8. Block diagram of (a) clock jitter induced error model (b) FIR feedback DAC, along with its compensation path.

clock jitter than a single-bit one due to the reduced step size in the DAC.

One technique to reduce the clock jitter sensitivity is the use of an FIR filter F(z) in the feedback path [15], as illustrated in Fig. 8(b). The in-band noise power J due to the clock jitter [16][17] with the FIR feedback path is:

$$J = \frac{\sigma_{jit}^2}{T_S^2} \frac{\sigma_{lsb}^2}{\pi OSR} \int_0^{\pi} \left| \left( 1 - e^{-j\omega} \right) NTF \left( e^{j\omega} \right) F \left( e^{j\omega} \right) \right|^2 d\omega \quad (2)$$

where  $\sigma_{jit}^2$  is the variance of the clock jitter;  $\sigma_{lsb}^2$  is the variance of the quantization noise of the internal quantizer; OSR is the oversampling ratio of the modulator;  $NTF(e^{j\omega})$  is the noise transfer function of the modulator; and  $F(e^{j\omega})$  is the transfer function of the FIR feedback path.

It is clear that the low-pass FIR filter F(z) attenuates the quantization noise at high frequency, and thus reduces the integrated noise power due to the clock jitter. In the time domain, the use of the FIR filter applied to the single-bit feedback DAC averages the adjacent samples, and reduces the step size from sample to sample, which simulates the benefits of the multi-level feedback. However, the introduction of the FIR feedback path necessitates a compensation path for the added delay and phase shift.

# A. Compensation of the FIR Feedback Delay

Techniques for the compensation of the FIR feedback delay have been proposed in recent works [19][20][25]. In [19], an analog feedback compensation path is employed. This technique increases the complexity, and the implemented NTF is changed from the ideal one. Ref. [20] adopts another FIR path to compensate for the delay of the main FIR feedback. This compensation path is fed into the last-stage transimpedance amplifier (TIA) output. Ref. [25] feeds the FIR compensation path to the input of the last stage integrator.

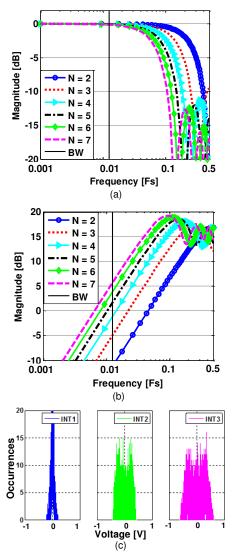

Fig. 9. (a) Frequency responses of FIR feedback path F(z). (b) Frequency responses of the FIR compensation path C(z) for different tap lengths N (c) Histograms of the each integrator output swing in the loop filter for tap length N=3.

Both methods tend to increase the parasitic in the last stage integrator, which is problematic for a modulator running at 1.2 GHz.

This work, as shown in Fig. 2, uses a simple FIR feedback path C(z) to compensate the delay introduced by the main FIR feedback F(z). As discussed in Section II, the last integrator implementing the fastest 1<sup>st</sup>-order path of the loop filter is in the high-speed path of the modulator loop. Additional feed-in paths to the last stage integrator will tend to create parasitic poles and result in increased delay. Hence, rather than connecting the compensation path to the last stage integrator, as in [20], the compensation path C(z) feeds into the input of the second integrator. Simulations shows that this simple change reduces the required unity gain bandwidth (UGBW) of the opamp of the last stage integrator from 1.6 times sampling frequency  $F_S$  to 1.2  $F_S$  while maintaining the same performance.

One concern about the feedback compensation path C(z) is the increased output swing at the first-stage integrator output,

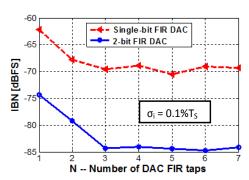

Fig. 10. In-band-noise due to a  $\sigma_j = 0.1\%T_S$  clock jitter versus the FIR tap length N, for both single-bit and 2-bit FIR DAC.

due to the input signal content feeding into this node. However, the compensation path C(z) can have a high-pass profile, as shown in Fig. 9(b). This is because the added low-pass main FIR F(z) mainly affects the high-frequency response of the loop filter, and hence the compensation path C(z) only needs to compensate the medium- to high-frequency loop gain.

Thus, the signal content is further attenuated before feeding into this node, and the output swing at the first-stage integrator can be kept at a reasonable level, as shown in Fig. 9(c), which illustrates the histograms of the integrator output swings, normalized to the full scale of the quantization. Note that the low output swing of the first-stage integrator is mandatory for low-voltage design.

# B. FIR Filter and Feedback DAC Design Considerations

Eq. (2) shows that the FIR feedback DAC reduces the sensitivity to clock jitter, due to its high frequency attenuation. This implies that increasing N must result in improved performance in terms of the sensitivity to the clock jitter, as more shaped quantization noise is filtered out. However, this holds true only for F(z) with a small number of tap N. As N increases, the main FIR feedback path F(z) exhibits better selectivity and higher stop-band attenuation, as shown in Fig. 9(a). In other words, F(z) with larger N results in larger attenuation in the medium-to-high frequency range. Therefore it requires a compensation path C(z) with higher out-of-band gain to stabilize the loop. This is illustrated in Fig. 9(b), where the frequency response of C(z) with different FIR lengths N is plotted. It is seen that F(z) with larger N leads to higher out-of-band-gain of C(z).

From (2), the input-referred jitter-induced noise power J due to C(z) can be found as:

$$J' = \int_0^{\frac{\pi}{OSR}} \frac{J_{C(z)}}{G_1(j\omega)} d\omega \tag{3}$$

$$J_{C(z)} = \frac{\sigma_{jit}^2}{T_s^2} \frac{\sigma_{lsb}^2}{\pi OSR} \int_0^{\pi} \left| \left( 1 - e^{-j\omega} \right) NTF \left( e^{j\omega} \right) C \left( e^{j\omega} \right) \right|^2 d\omega \quad (4)$$

where  $G_I(j\omega)$  is the frequency response of the first-stage integrator, and  $J_{C(z)}$  is the noise power due to C(z).

As (4) shows, higher out-of-band gain of C(z) tends to increase the jitter-induced noise power, and hence the input-

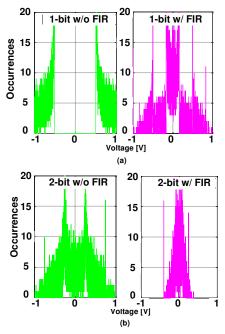

Fig. 11. Histograms of the loop filter input with or without FIR feedback for (a) 1-bit internal quantization (b) 2-bit internal quantization.

referred noise power J' even with the in-band attenuation by the first integrator, as in (3). For high values of N, the compensation path C(z) may cancel the effects of F(z) in reducing the input-referred noise power due to the clock jitter.

In the behavioural simulation, a 0.1% rms clock jitter was applied to the sampling clock period in the feedback path. The in-band-noise due to the clock jitter is plotted as a function of the FIR filter order N for both single-bit and 2-bit FIR feedback DACs. Fig. 10 compares the in-band noise power for single-bit and 2-bit internal resolutions as the FIR order N increases. An NTF with an out-of-band gain (OBG) is chosen to be 1.5 for a CTDSM with a single-bit quantizer, according to Lee's rule [36], and OBG = 2 for the one with a 2-bit quantizer. As Fig. 10 shows, for FIR tap length N > 3, the in-band noise power due to a 0.1% clock jitter saturates for both circuits.

Hence, this device uses a 3-tap FIR filter to achieve reduced clock jitter sensitivity while maintaining design simplicity. Fig. 11(a)(b) compares the histograms of the loop filter input with or without the FIR feedback path for both single-bit and 2-bit quantization, demonstrating the linearity advantage due to the introduction of the FIR feedback path. As shown in Fig. 11(b), the use of a 2-bit feedback achieves much smaller input swing compared to using a single-bit feedback. A 2-bit 3-tap FIR feedback branch was therefore adopted in our work.

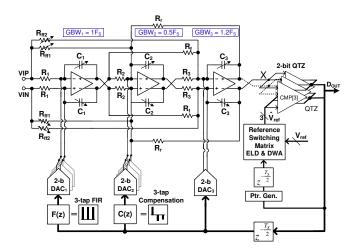

# V. CIRCUIT IMPLEMENTATION

The overall schematic of the CT  $\Delta\Sigma$  modulator is shown in Fig. 12. It includes a CT loop filter, a 2-bit flash quantizer, an FIR filtering feedback DAC F(z) with its compensation path C(z), and the reference-switching matrix for ELD compensation and DWA. The key building blocks are described next.

Fig. 12. Schematic of the overall continuous-time  $\Delta\Sigma$  modulator [13].

#### A. Loop Filter

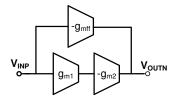

The circuit of the opamp used in the loop filter is a two-stage design that employs no capacitor feed-forward (NCFF) compensation rather than a Miller capacitor [13][23]. The single-end representation of the opamp block diagram is shown in Fig. 13. The feedforward path  $g_{mff}$  creates a zero to stabilize the two-stage opamp. Compared to a Miller-compensated design, this architecture is more power-efficient, since no extra power is spent on charging and discharging the Miller capacitors. Thanks to the FIR feedback DAC, the linearity requirement of the first integrator is greatly relaxed. All opamps used in the latter stages share the same topology.

The input resistance  $R_I$  and capacitance  $C_I$  of the first stage integrator are chosen to be 2.5 k $\Omega$  and 1.5 pF, respectively. Power reduction and linearity enhancement can be achieved by maximizing the  $R_I$  up to the thermal noise limit [37], which is given by:

$$P_{N} = 8kTB_{W} \left[ R_{1} + R_{DAC} \frac{R_{1}^{2}}{R_{DAC}^{2}} + \frac{2}{3g_{m,OTA}} \left( 1 + \frac{R_{1}}{R_{DAC}} \right)^{2} \right]$$

(5)

where  $P_N$  is the input-referred thermal noise of the modulator and  $B_W$  is the signal bandwidth;  $R_{DAC}$  refers to the resistors used for feedback DAC, and  $g_{m,OTA}$  represents the amplifier input transconductance.

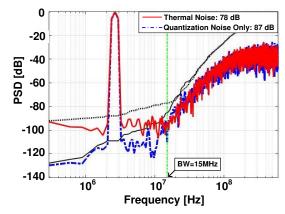

Fig. 14 shows the simulated modulator output power spectrum density (PSD) with only quantization noise and with thermal noise also included. The quantization noise is designed to be well below the thermal noise and hence the modulator performance is limited by the thermal noise. It achieves an SQNR of 87dB and an SNR of 78 dB.

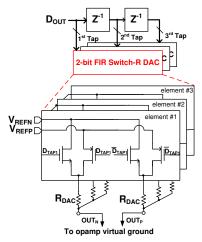

#### B. FIR Feedback DAC

Rather than using a current steering DAC, this work adopted a switched-resistor (SR) feedback DAC. This was because for low-voltage (1 V) implementation the SR DAC is less noisy than a current-steering DAC, whose noise performance is limited by the available voltage headroom. Also, the SR DAC can provide better matching performance than a current steering one with low headroom.

Fig. 13. Block diagram of the NCFF opamp.

Fig. 14. Simulated power spectrum density with only quantization noise, and thermal noise also included.

Fig. 15. Implemented 3-tap FIR DAC and its 2-bit switched-resistor elements.

The SR DAC has a non-return-to-zero (NRZ) output. As shown in Fig. 15, the switches are located at the reference levels, making the on-resistance of the switches unchanged with time. However, the distributed RC parasitics due to the resistor at the virtual ground of the loop filter may exacerbate the inter-symbol interference (ISI) effects, and add loop delay. Therefore great care has been taken in the sizing and routing of the SR feedback DAC.

The FIR feedback DAC is implemented by a semi-digital approach [24]. Equally weighted coefficients were chosen for the main FIR feedback path F(z), whereas the coefficients of the compensation path C(z) were determined by using the Impulse-Invariant-Transformation (IIT).

Fig. 16. The implemented reference-switching matrix for ELD and DWA.

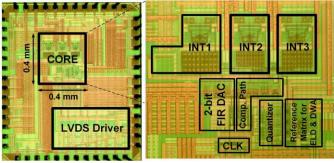

Fig. 17. Die microphotograph of the prototype [13].

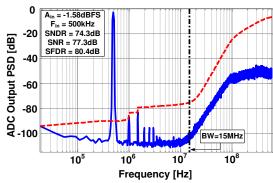

Fig. 18. Measured modulator output spectrum (65,536-point FFT with 15 averages) [13].

#### C. Reference-switching Matrix for ELD and DWA

The details of the reference-switching matrix for ELD compensation and DWA (Fig. 12) are shown in Fig. 16. The two switching matrices are merged, and controlled by their pointer generation logic.

Once an output sample of the modulator is generated, the pointer generator logic uses it to shift the reference voltage in the first matrix for ELD compensation. Then the shifted reference voltages are applied to the second matrix, and shuffled according to the pointer generated by the DWA algorithm. Both reference-switching operations are finished in a half clock period.

# VI. MEASUREMENT RESULTS

The prototype CTDSM was fabricated in a 65 nm CMOS process with MiM capacitors. It occupies an active core area of 0.16 mm<sup>2</sup>. The chip microphotograph is shown in Fig. 17.

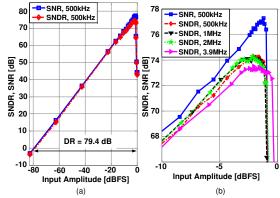

Fig. 19. Measured SNR/SNDR vs. input amplitude for (a) a 500 kHz input and (b) a magnified plot at high input amplitudes for four different input frequencies.

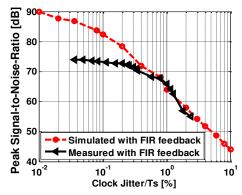

Fig. 20. Measured and simulated SNDR as functions of the clock jitter.

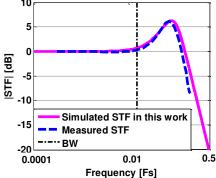

Fig. 21. Measured signal transfer function.

The die was packaged in a 40-pin QFN package.

A four-layer board is used to characterize the chip. The sine wave generated by the signal source (AWG710B) is applied to a passive band-pass filter (Allen Avionics) with a center frequency of 500 kHz, and then converted to a differential signal with a balun (Coilcraft PWB2010LB). An RF clock source (Agilent E4433B) is used to provide the clock signal of 1.2 GHz. The modulator output bit-stream, transmitted by a stubbed-series termination-logic (SSTL) interface, is captured by a logic analyzer (TLA7012), and post-processed to obtain the output spectrum.

Running at a 1.2 GHz sampling rate, the modulator dissipates 6.96 mW, of which 4.31 mW is consumed by the analog blocks, 2.17 mW by the digital blocks, and 0.47 mW

| Parameter                                 | arameter This Work |       | [8]<br>ISSCC<br>2006       | [26]<br>JSSC<br>2011 | [30]<br>JSSC<br>2011 | [19]<br>JSSC<br>2012 | [33]<br>JSSC<br>2012 | [31]<br>JSSC<br>2012 | [34]<br>JSSC<br>2013 | [11]<br>ISSCC<br>2013 | [28]<br>JSSC<br>2014 | [29]<br>JSSC<br>2014 | [32]<br>JSSC<br>2015 |      |

|-------------------------------------------|--------------------|-------|----------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|----------------------|----------------------|----------------------|------|

| Topology                                  | FF-FB              |       | FF-FB                      | CIFF                 | CIFF                 | FF-FB                | CIFF                 | CIFF                 | CIFF                 | CIFF                  | FF-FB                | MASH                 | CIFF                 |      |

| Adder required                            | No                 |       | No                         | No                   | Active               | No                   | Active               | Active               | Active               | No                    | No                   | Passive              | No                   |      |

| ELD Comp.                                 | $R.S^7$            |       | $D.D^3$                    | D.D                  | $D.F^4$              | D.D                  | D.F                  | D.F                  | D.F                  | C.S <sup>5</sup>      | PLR <sup>6</sup>     | D.F                  | R.S                  |      |

| Technology(nm)                            | 65                 |       | 130                        | 65                   | 130                  | 90                   | 180                  | 130                  | 130                  | 28                    | 90                   | 28                   | 20                   |      |

| Area (mm <sup>2</sup> )                   | 0.16               |       | 1.2                        | 0.15                 | 1.17                 | 0.12                 | 0.68                 | 0.38                 | 1.3                  | 0.08                  | 0.225                | 45                   | 0.1                  |      |

| $V_{DD}(V)$                               | 1.0                |       | 1.2                        | 1.2/1.3              | 1.2                  | 1.2                  | 1.8                  | 1.3                  | 1.2                  | 1.2/1.5               | 1.2                  | 0.9/1.8              | 1.2/1.5              |      |

| F <sub>s</sub> (MHz)                      |                    | 1200  |                            | 640                  | 250                  | 640                  | 3600                 | 800                  | 1000                 | 185                   | 640                  | 500                  | 3200                 | 2184 |

| Power (mW)                                | 6.96               |       | (Ana.)<br>(Dig.)<br>(Ref.) | 20                   | 10.5                 | 58                   | 15                   | 47.6                 | 4                    | 13.7                  | 3.9                  | 8.5                  | 235                  | 23   |

| BW (MHz)                                  | 15                 |       | 20                         | 20                   | 20                   | 25                   | 16                   | 15.6                 | 10                   | 18                    | 25                   | 45                   | 80                   |      |

| F <sub>IN</sub> (MHz)                     | 0.5                | 1     | 4                          | 3.7                  | 3.9                  | 1                    | 10                   | 5                    | 5                    | 1                     | 0.625                | 2                    | 15                   | 15   |

| SNR (dB)                                  | 77.3               | 77.2  | 76.4                       | 73.0                 | 62.0                 | 67.9                 | 80.2                 | 67                   | 64.5                 | 73.4                  | 75.4                 | 69.1                 | 84.6                 | 70   |

| SNDR (dB)                                 | 74.3               | 74.1  | 73.7                       | 74.0                 | 60.0                 | 63.9                 | 73.3                 | 65                   | 59.8                 | 71.9                  | 73.6                 | 67.5                 | 72.6                 | 67.5 |

| DR (dB)                                   | 79.4               | 78.8  | 78.1                       | 80.0                 | 68.0                 | 65.9                 | 86.0                 | 75                   | 67.0                 | 80                    | 78.1                 | 72.0                 | 90                   | 73   |

| ENOB (bits)                               | 12.0               | 12.0  | 12.0                       | 12.0                 | 9.7                  | 10.3                 | 11.9                 | 10.5                 | 9.7                  | 11.7                  | 11.9                 | 11.8                 | 11.8                 | 10.9 |

| FoM <sup>1</sup> <sub>Walden</sub> (fJ)   | 54.7               | 56.0  | 58.6                       | 122.1                | 321.2                | 1110                 | 79.4                 | 1020                 | 160                  | 210                   | 27.7                 | 87.7                 | 184                  | 74.2 |

| FoM <sup>2</sup> <sub>Schreier</sub> (dB) | 172.7              | 172.1 | 171.4                      | 170.0                | 160.8                | 151.1                | 178.2                | 160.3                | 162.9                | 168.6                 | 174.7                | 162.2                | 172.9                | 168  |

TABLE I

PERFORMANCE SUMMAY AND COMPARISON WITH PRIOR WORKS

- 1. FoMwalden = Power/(2<sup>(SNDR-1.76)/6.02</sup> x 2 x BW). 5. C.S; Comparator Switching as in [11].

- 2. FoM<sub>Schreier</sub> = DR + 10 x log<sub>10</sub> (BW / P). 6. PLR: Phase Lead Resistor as in [28].

- 3. D.D: Discrete-time Differentiation as in [8]. 4. D.F: Direct Feedback as in [9].

- 7. R.S: Reference-Switching as in this work

by the reference voltage generators. Both the analog and digital blocks operate with 1 V supply voltages.

Fig. 18 gives the measured ADC output power spectrum density (PSD) for a -1.58 dBFS input tone at 500 kHz. (The full scale or 0 dBFS is 2 V<sub>PP.</sub>) The sampling frequency was 1.2 GS/s. A 15-times averaged 65,536-point fast Fourier transform with a Hanning window was used for spectrum analysis. The ADC achieved a peak SNR of 77.3 dB, and an SNDR of 74.3 dB over a 15 MHz signal BW, resulting in an ENOB of 12. The measured SNR and SNDR are plotted for different input amplitudes in Fig. 19(a) for a 500 kHz input tone. A dynamic range of 79.4 dB was achieved. This validates the use of switched resistor feedback DAC with 1 V power supply. The SNDR curves for various input frequencies near the full-scale amplitude are plotted in Fig. 19(b). The peak SNDR is degraded by 0.6 dB over an input signal frequency range from 500 kHz to 4 MHz. The rms jitter of the applied clock source is around 300fs, or 0.1% of the sampling clock period.

To verify the effectiveness of the FIR feedback DAC, the measured and simulated SNDRs with FIR feedback path against the clock jitter are shown in Fig. 20. The clock jitter injection was obtained using the software interface to Agilent E4438C. The applied clock jitter is then characterized by the spectrum analyzer Agilent E4440A. It can be seen from Fig. 20 that the modulator achieves a measured SNDR larger than 70 dB when the applied rms clock jitter is less than 3 ps, which is 0.4% of the clock period. Within this range, the thermal noise contributed by the input-referred noise of the loop filter and switched-resistor feedback DAC dominates. In addition, even-order harmonic distortion is also found and contributes to the performance degradation due to the ISI effect in the feedback DAC. This results in a levelling of the noise in the measured result, which includes the thermal noise, the quantization error and the jitter-induced error. With the clock jitter larger than 0.6%T<sub>S</sub>, the noise power induced by the clock jitter becomes dominant, and matches well with the

simulated results.

The FIR feedback DAC will affect the signal transfer function (STF) of the modulator. A longer FIR filter results in a more out-of-band peaking of STF [25], which is not desirable when an out-of-band blocker is present. The measured STF, along with the simulated one is shown in Fig. 21. They coincide, and show a peaking around 6 dB, which is much lower than in prior work with FIR feedback path [19][25].

The performance of the ADC is summarized in Table I. It compares the performance of the state-of-the-art ADCs. It can be seen that the ADCs in which the active adder was eliminated achieved better power efficiency, as in [8][11][19] [29]. Furthermore, the ELD compensation without the conventional direct feedback path relaxes the requirements of the last integrator stage. This change helps to achieve an even better FoM, as in [11]. In our work, by removing the direct feedback path, the required UGBW of the opamp of the last integrator could be reduced from 1.6  $F_S$  to 1.2  $F_S$ . The proposed converter achieves a peak SNDR of 74.3 dB with 1 V power supply. The Walden and Schreier Figures of Merit are below 60 fJ/step and above 170 dB, respectively, which compare favorably with the state-of-the-art.

# VII. CONCLUSION

A  $\Delta\Sigma$ -based ultrasound beamforming receiver for biomedical imaging was described. It allows finer dynamic delay increments to achieve better image quality. A 3<sup>rd</sup>-order CT  $\Delta\Sigma$  modulator clocked at 1.2 GHz and operating with a 1 V power supply, was described. A digital ELD compensation technique is proposed to eliminate the power-hungry adder used in earlier circuits. Also, the DWA logic is incorporated into the reference-switching matrix used in the digital ELD compensation, in order to minimize the delay in the critical path. Finally, a 2-bit 3-tap FIR filter is introduced in the feedback path, to make the modulator less susceptible to the

clock jitter. The effect of increasing the FIR tap length on the clock jitter sensitivity was analyzed. Fabricated in a 65 nm CMOS process, the prototype modulator achieves a 79.4 dB dynamic range, 77.3 dB SNR and 74.3 dB SNDR over a 15 MHz signal bandwidth, with a FoM of 58.6 fJ/conversion-step.

#### ACKNOWLEDGEMENTS

The authors would like to thank Nancy Qian, Ed Liu, Philip Elliott and John Scampini from Maxim Integrated, and Brian Young for the helpful technical discussions and insights. The authors are also grateful to Patrick Chiang for arranging the chip fabrication.

### REFERENCES

- S. E. Noujaim, S. L. Garverick, and M. O'Donnell, "Phased array ultrasonic beam forming using oversampled A/D converters," U.S. Patent 5,203,335, April 20, 1993.

- [2] R. G. Pridham and R. A. Mucci, "Digital interpolation beamforming for low-pass and bandpass signals," *Proc. IEEE*, vol. 67, pp. 904-919, June 1979.

- [3] D. Lipschutz, "Delay interpolator for digital phased array ultrasound beamformers," U.S. Patent 4,809,184, February 28, 1989.

- [4] S. Freeman et al., "Delta-sigma oversampled ultrasound beamformer with dynamic delays," *IEEE Trans. Ultrasonics, Ferroelectrics, and Frequency Control.*, vol. 46, No. 2, Mar. 1999.

- [5] G. Gurun et al., "An analog integrated circuit beamformer for high-frequency medical ultrasound imaging," *IEEE Trans. Biomed. Circuits Syst.*, vol. 6, pp. 454 467, Oct. 2012.

- [6] P. Song, K-T Tiew, Y. Lam, and K. L. Mong, "A CMOS 3.4mW 200 MHz continuous-time delta-sigma modulator with 61.5 dB dynamic range and 5 MHz bandwidth for ultrasound application," in *Proc.* 50<sup>th</sup> Midwest Symp. Circuits and Systems, pp. 152-155, 2007.

- [7] B. Tov, M. Kozak, E. G. Friedman, "A 250 MHz delta-sigma modulator for low cost ultrasound/sonar beamforming applications," *IEEE ICECS*, pp. 113-116, Dec 2004.

- [8] G. Mitteregger et al., "A 14b 20mW 640MHz CMOS CT ΔΣ ADC with 20MHz signal bandwidth and 12b ENOB," IEEE ISSCC Dig. Tech. Papers, pp. 131-140, Feb. 2006.

- [9] J. Cherry, M. Snelgrove, "Excess loop delay in continuous-time deltasigma modulators," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 46, no.4, pp. 376-389, Apr. 1999

- [10] S. Yan and E. Sanchez-Sinencio, "A continuous-time sigma-delta modulator with 88-dB dynamic range and 1.1-MHz signal bandwidth," *IEEE J. Solid-State Circuits*, vol. 39, no. 1, pp. 75–86, Jan. 2004.

- [11] Y. Shu *et al.*, "A 28fJ/conv-step CT  $\Delta\Sigma$  modulator with 78dB DR and 18MHz BW in 28nm CMOS using a highly digital multibit quantizer," *IEEE ISSCC Dig. Tech. Papers*, pp 268-269, Feb 2013.

- [12] Y. Zhang, C-H Chen, and G. Temes, "Efficient technique for excess loop delay compensation in continuous-time  $\Delta\Sigma$  modulators," *Electron. Lett.*, vol. 49, no. 24, pp. 1522-1523, 2013.

- [13] Y. Zhang et al., "A 1 V 59 fJ/Step 15 MHz BW 74 dB SNDR continuous-time ΔΣ modulator with digital ELD Compensation and multi-bit FIR feedback," in Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC'14), pp. 321–324, Nov. 2014.

- [14] O. Oliaei, "Sigma-delta modulator with spectrally shaped feedback," IEEE Trans. Circuits Syst. II: Analog Digit. Signal Process. vol. 50, no. 9, pp. 518–530, Sep. 2003.

- [15] B. Putter, "ΣΔ ADC with finite impulse response feedback DAC," *IEEE ISSCC Dig. Tech. Papers*, pp. 76–77, Feb. 2004.

- [16] K. Reddy and S. Pavan, "Fundamental limitations of continuous-time delta–sigma modulators due to clock jitter," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 10, pp. 2184–2194, Oct. 2007.

- [17] L. Hernandez, A. Wiesbauer, S. Paton, and A. D. Giandomencio, "Modelling and optimization of low-pass continuous-time ΣΔ modulators for clock jitter noise reduction," in *Proc. IEEE Int. Symp. Circuits Syst (ISCAS)*, vol. 1, pp. 1072–1075, May 2004.

- [18] Y. Zhang et al., "A continuous-time ΔΣ modulator with a digital technique for excess loop delay compensation," in Proc. IEEE Int. Symp. Circuits Syst. pp. 934-937, May 2014.

- [19] P. Shettigar and S. Pavan, "Design technique for wideband single-bit continuous-time ΔΣ modulators with FIR feedback DACs," *IEEE J. Solid-State Circuits*, vol. 47, no. 12, pp. 2865-2879, Dec. 2012.

- [20] J. Gealow et al., "A 2.8mW ΔΣ ADC with 83 dB DR and 1.92MHz BW using FIR outer feedback and TIA-Based Integrator," IEEE Symp. VLSI Circuits, pp. 42-43, June 2011.

- [21] W. Yang, et al., "A 100mW 10MHz-BW CT ΔΣ modulator with 87dB DR and 91dBc IMD," IEEE ISSCC Dig. Tech. Papers, pp. 498-631, Feb. 2008.

- [22] L. Doerrer et al., "10-bit, 3 mW continuous-time Sigma-Delta ADC for UMTS in a 0.12 μm CMOS process," in Proc. European Solid-State Circuits Conf., pp. 245-248, 2003.

- [23] B. Thandri and J. Silva-Martinez, "A robust feedforward compensation scheme for multistage operational transconductance amplifiers with no miller capacitors," *IEEE J. Solid-State Circuits*, vol. 38, no. 2, pp. 237-243, Feb. 2003.

- [24] D. K. Su and B. A. Wooley, "A CMOS oversampling D/A Converter with a current-mode semi-digital reconstruction filter," *IEEE J. Solid-State Circuits*, vol. 28, pp. 1224-1233, Dec. 1993.

- [25] A. Sukumaran and S. Pavan, "A 280μW audio continuous-time modulator with 103 dB DR and 102 dB A-weighted SNR," in Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC'13), pp. 385–388, 2013.

- [26] V. Dhanasekaran et al., "A continuous time multi-bit ΔΣ ADC using time domain quantizer and feedback element," *IEEE J. Solid-State Circuits*, vol. 46, no. 3, pp. 639-650, Mar. 2011.

- [27] J. Kauffman et al., "A 72dB DR, CT ΔΣ modulator using digitally estimated, auxiliary DAC linearization achieving 88fJ/conv in a 25 MHz bandwidth," *IEEE J. Solid-State Circuits*, vol. 49, No. 2, pp. 392-404, Feb. 2014.

- [28] M. Vadipour, et al., "A 2.1 mW/3.2mW delay-compensated GSM/WCDMA ΔΣ analog-digital Converter," IEEE VLSI Symp., pp. 180-181, 2008.

- [29] Y. Dong et al., "A continuous-time 0-3 MASH ADC achieving 88 dB DR with 53 MHz BW in 28 nm CMOS," IEEE J. Solid-State Circuits, vol. 49, no. 12, pp. 2868-2877, Dec. 2014.

- [30] J. Jo, J. Noh, and C. Yoo, "A 20-MHz Bandwidth Continuous-time Sigma-delta modulator with jitter immunity improved full lock period SCR (FSCR) DAC and high-speed DWA," *IEEE J. Solid-State Circuits*, vol. 46, no. 11, pp. 2469-2477, Nov. 2011.

- [31] A. Jain, M. Venkatesan, and S. Pavan, "Analysis and design of a high speed continuous-time ΔΣ modulator using the assisted opamp technique," *IEEE J. Solid-State Circuits*, vol. 47, no. 7, pp. 1615-1625, Jul. 2012.

- [32] S. Ho, C. Lo, J. Ru and J. Zhao, "A 23 mW, 73 dB dynamic range, 80 MHz BW continuous-time delta-sigma modulator in 20 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 50, no. 4, pp. 908-919, Apr. 2015.

- [33] V. Singh *et al.*, "A 16 MHz BW 75 dB DR CT ΔΣ ADC Compensated for more than one cycle excess loop delay," *IEEE J. Solid-State Circuits*, vol. 47, no. 8, pp. 1884-1895, Aug. 2012.

- [34] R. Zanbaghi, P. Hanumolu, and T. Fiez, "An 80-dB DR, 7.2-MHz bandwidth single opamp biquad based CT ΔΣ modulator dissipating 13.7-mW," *IEEE J. Solid-State Circuits*, vol. 48, no. 2, pp. 487-501, Feb. 2013.

- [35] C. Ding et al., "Approaches to digital compensation for excess loop delay in continuous-time delta-sigma modulators using a scaled quantizer," in Proc. IEEE Int. Symp. Circuits. Syhst. (ISCAS), pp. 3001-3004, May 2012,

- [36] W. Lee, "A novel higher order interpolative modulator topology for high resolution A/D Converters," Master's thesis, Mass. Inst. of Technol. (MIT), Cambridge, MA, 1987.

- [37] L.J. Breems et al., "Design for optimum performance-to-power ratio of a continuous-time ΣΔ modulator," Proc. Eur. Solid-State Circuits Conf. pp. 318-321, Sep. 1999.

Yi Zhang (S'12) received the B.E degree in electrical engineering from Zhejiang University, Hangzhou, China, in 2007, and M.S degree from Fudan University, Shanghai, China, in 2010. He is currently working toward the Ph.D. degree at Oregon State University, Corvallis, OR, USA.

From 2010 to 2012, he was a Design Engineer with NXP Semiconductors, Shanghai, China. He was a Design Intern with Analog Devices, Wilmington, MA, during the summer of 2014. His research interest is in the area of high-speed delta-sigma modulators.

He received the Best Student Paper Award in Asian Technical Conference held by Analog Devices in 2009 and *A-SSCC* Student Travel Grant Award in 2014.

Chia-Hung Chen received B.S. degree in nuclear engineering from National Tsing Hua University, HsinChu, Taiwan, and M.S. degree in electrical engineering from Columbia University, New York, NY. During 2009 to 2013, he studied his Ph.D. in Oregon State University, Corvallis, OR. His

doctoral research is in micro-power delta-sigma incremental data converters.

Before his Ph.D. study in Oregon State University, he was had been with Analog Devices Taiwan during 2003 to 2006. And during 2006 to 2009, he was with start-up IC design houses in Taiwan, designing audio codec circuits, DC-DC power converters and PLL. In the summer of 2011, he was a design intern with Maxim Integrated, CA. After his Ph.D. degree, he was with Mediatek, Woburn, MA during 2013 to 2014. He is currently with Oregon State University, as a post-doctoral scholar. His research interests are in the design of precision analog circuit, energy-efficient data converters.

**Tao He** received the B.Sc degree in electrical and computer engineering from University of Macau, Macau, China, in 2010. Since 2012, he is now with school of electrical engineering and computer science in Oregon state university, pursuing his Ph.D. degree.

His research interest includes high performance analog and mixed-signal circuit

design in advanced CMOS technology.

**Gabor C. Temes** (SM'66–F'73–LF'98) received the undergraduate degrees from the Technical University of Budapest and Eötvös University, Budapest, Hungary, in 1952 and 1955, respectively. He received the Ph.D. degree in electrical engineering from the University of Ottawa, ON, Canada, in

1961, and an honorary doctorate from the Technical University of Budapest, Budapest, Hungary, in 1991.

He held academic positions at the Technical University of Budapest, Stanford University, Stanford, CA, and the University of California at Los Angeles (UCLA). He worked in industry at Northern Electric R&D Laboratories (now Bell-Northern Research), Ottawa, Canada, as well as at Ampex Corp. He is now a Professor in the School of Electrical Engineering and Computer Science at Oregon State University. His recent research has dealt with CMOS analog integrated circuits and data converters. He co-edited and coauthored many books; the most recent one is *Understanding*

*Delta-Sigma Data Converters* (IEEE Press/Wiley, 2005). He also wrote approximately 300 papers in engineering journals and conference proceedings.

Dr. Temes was Editor of the IEEE TRANSACTIONS ON CIRCUIT THEORY and Vice President of the IEEE Circuits and Systems (CAS) Society. In 1968 and in 1981, he was cowinner of the IEEE CAS Darlington Award, and in 1984 winner of the Centennial Medal of the IEEE. He received the Andrew Chi Prize Award of the IEEE Instrumentation and Measurement Society in 1985, the Education Award of the IEEE CAS Society in 1987, and the Technical Achievement Award of the IEEE CAS Society in 1989. He received the IEEE Graduate Teaching Award in 1998, and the IEEE Millennium Medal as well as the IEEE CAS Golden Jubilee Medal in 2000. He was the 2006 recipient of the IEEE Gustav Robert Kirchhoff Award, and the 2009 IEEE CAS Mac Valkenburg Award. He is member of the National Academy of Engineering.