Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier 10.1109/ACCESS.2017.Doi Number

# A Cross Connected Asymmetrical Switched-Capacitor Multilevel Inverter

Md Reyaz Hussan<sup>1</sup>, Adil Sarwar<sup>1</sup>, Senior Member, IEEE, Marif Daula Siddique<sup>2</sup>, Member, IEEE, Atif Iqbal<sup>2</sup>, Senior Member, IEEE, Basem Alamri<sup>3</sup>, Member, IEEE

<sup>1</sup>Department of Electrical Engineering, ZHCET, Aligarh Muslim University (AMU), Aligarh 202002, Uttar Pradesh, India

Corresponding author: Md Reyaz Hussan (md.reyazhussan@zhcet.ac.in).

The authors would like to acknowledge the financial support from Taif University Researchers Supporting Project Number (TURSP-2020/278), Taif University, Taif, Saudi Arabia. The authors also acknowledge the support provided by the Non-Conventional Energy (NCE.) Lab, Department of Electrical Engineering, Aligarh Muslim University, India.

**ABSTRACT** A Switched-Capacitor Multilevel Inverter (SCMLI) topology is proposed here, which can generate up to fifteen levels with one unit and can be extended further for getting higher levels. The proposed SCMLI has a lesser number of switching devices with respect to other recently proposed structures presented in this paper. It also has the capacitor self-balancing property. Power loss analysis has also been done using PLECS software. Maximum efficiency of 96.33 % has been achieved. A generalized comparative study has also been carried out with the newly presented topologies in different research articles considering several parameters. In order to validate the structure presented in this paper, simulation is done in Matlab<sup>®</sup>2018a, and the simulation results obtained are verified using an experimental prototype.

**INDEX TERMS** level-shifted PWM, switched-capacitor MLI, total harmonic distortion, multilevel inverter, self- voltage balancing

#### I. INTRODUCTION

Inverters play a very crucial role in various industrial applications. Enhanced power quality requirements in various industrial applications have led to the manifold increment in the research field of multilevel inverters, as conventional inverters have limitations in fulfilling these requirements. Multilevel inverters have superior output quality with respect to the conventional inverters, such as more sinusoidal-like output voltage, low total harmonic distortion (THD), low voltage and dv/dt stress, lesser power loss, minimized electromagnetic interference on output waveforms, the capability of handling higher power levels, etc. [1], [2]. MLIs have these qualities due to the fact that they have the potential to produce a staircase output waveform [3]. On the other hand, conventional MLIs require a higher component count to obtain more output levels, suffer from capacitor voltage balancing problems, and the absence of self-voltage boosting capability [4].

Different reduced device count MLIs have been presented in the literature [5]-[10] to remove the shortcoming of higher component requirements in conventional MLIs. However, these MLIs lack a boosting feature to get a desired output voltage level. To remove the problem of capacitor voltage unbalance in conventional MLIs, some complex control algorithms have been developed, or auxiliary circuits having multi-output boost converter have been added to the inverter

structure [11]-[14]. These capacitor voltage balancing methods result in the increment of weight, complexity, and overall cost of the inverter. To mitigate the problems mentioned above in conventional MLIs and reduced device count MLIs, SCMLIs have come into the picture. Capacitors act as alternate DC voltage sources in SCMLIs. These MLIs utilize the charging and discharging of the capacitors in order to produce near the sinusoidal output. Additionally, SCMLIs do not have any complex control logic or auxiliary circuits for balancing the capacitor voltages.

Lately, a good number of novel SCMLIs have come into the picture. Papers presented in [15], [16], [17] have topologies with an H- bridge inverter at the end connected in series with the switched capacitors. Self-voltage balancing, voltage gain, and only one DC source are the merits of these topologies over the conventional MLIs. Nevertheless, these topologies have more capacitors and higher active switch count, which lead to large size, overall high cost, and increased complexity. An SCMLI structure has a cascaded connection of a boost converter, and a two-level inverter is proposed in [18]. The inverter is used to generate polarity, and the boost converter generates the multilevel step voltage. An SCMLI topology which is having an SC- frontend and backend as H-bridge, is presented in [19]. Higher output levels are produced using the SC-frontend. In [20], a nine-level inverter has been proposed having ten switches compared to the one proposed in [21] with

VOLUME XX, 2017 1

<sup>&</sup>lt;sup>2</sup>Department of Electrical Engineering, Qatar University, Doha, Qatar

<sup>&</sup>lt;sup>3</sup> Department of Electrical Engineering, College of Engineering, Taif University, Taif 21944, Saudi Arabia

twelve switches and the one in [22] with eleven switches for the same level. All three proposed topologies have the advantage of voltage gain and capacitor voltage balancing ability. A new SC-topology having cross-connected switches is proposed in [23]. The topology configuration is such that the leakage current is eliminated, but it uses a higher number of components for higher levels. A seven-level SCMLI with a gain of 1.5 and capacitor voltage balancing ability has been proposed in [24], which uses only one DC source. Shiva et al. [25] have proposed a nine-level single-source SCMLI structure with self-voltage balancing, boosting capability, and low switch stress. A novel asymmetrical SCMLI has been proposed in [26], where voltage gain of 2 is achieved, and comparative analysis show improvement in different components like the number of dc supply, voltage gain, etc. A new inverter having switched series-parallel asymmetric sources has been proposed in [27]. Power losses are reduced using a unique combination of the basic unit, and its comparison is also shown graphically. A new type of SCMLI with a quasi-resonant inductor which is connected in series with the capacitor charging loop to suppress the current spikes, has been proposed in [28]. An improvement on the previous structures by eliminating the bidirectional switches using an appropriate positioning of the DC supply is proposed in [29].

This paper proposes a new cross-connected asymmetrical SCMLI topology with a low voltage power switch for a single-phase system. This topology has the merit of a lesser component requirement. The proposed topology comprises two DC voltage sources, two diodes, one bidirectional switch, eight unidirectional switches, and two capacitors and can generate up to fifteen voltage levels per unit, which can also be extended to higher levels. The capacitor voltage balancing problem is not there as the charge balance is maintained over the full cycle. The performance of the proposed topology is verified by comparing DC supply count, number of switches, and switch stress with several other topologies.

#### **II. THE PROPOSED 15 LEVEL INVERTER**

This section discusses the structure of the proposed 15 level inverter, its working principle, and its extension for higher levels.

#### A. CIRCUIT CONFIGURATION

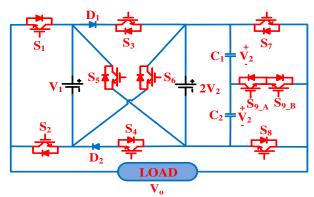

The proposed structure has been shown in Fig. 1. It has two asymmetrical DC supplies ( $V_1$  and  $2V_2$ ), two diodes ( $D_1$  and  $D_2$ ), two capacitors ( $C_1$  and  $C_2$ ), one bidirectional ( $S_{9\_A}$ ,  $S_{9\_B}$ ), and eight unidirectional ( $S_1$ -  $S_8$ ) switches. This structure is able to generate 15 levels at the output. The switch pairs ( $S_1$ ,  $S_2$ ), ( $S_3$ ,  $S_5$ ), ( $S_3$ ,  $S_6$ ), ( $S_4$ ,  $S_5$ ), ( $S_4$ ,  $S_6$ ), and ( $S_7$ ,  $S_8$ ) should not have simultaneous ON states so that short-circuiting of the DC voltage sources  $V_1$  and  $2V_2$  does not occur. The bidirectional switch is at the capacitor's midpoint, which clamps their voltage to  $V_2$  and taps any of the capacitor voltage to the load.

FIGURE 1. Proposed fifteen-level SCMLI topology.

# B. DESCRIPTION AND WORKING OF THE PROPOSED SCMLI TOPOLOGY

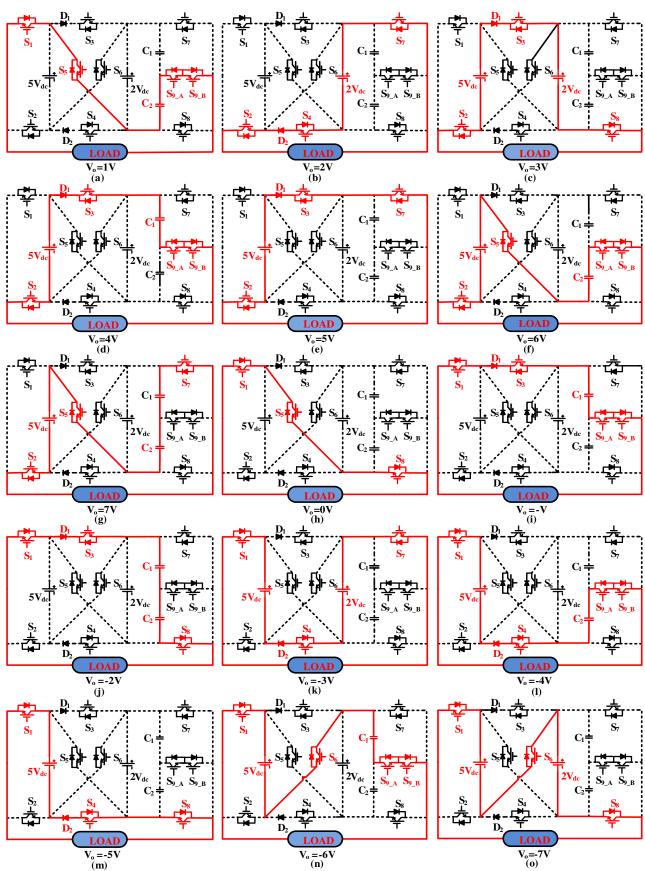

All the 15 switching states of the inverter are shown in Fig. 2 and Table 1. The red-marked loops in the figure are the conductive paths. '0' and '1' denote that the corresponding switch is turned OFF and turned ON, respectively. Charged capacitors in the respective switching states are also given in the table. Here, the DC voltage sources are related to each other according to the following equation:

$$V_2 = \frac{1}{5} V_1 = V_{dc} \tag{1}$$

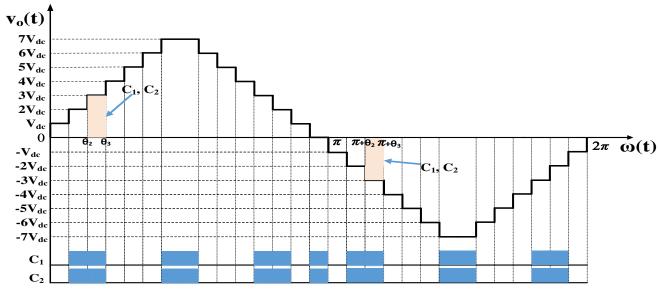

All the fifteen levels can be realized easily by looking at the switching table and its corresponding switching diagram. For instance, to generate the third level i:  $eV_0=3V$ , switches  $S_2$ ,  $S_3$ , and  $S_8$  have to be turned ON simultaneously, as shown in Fig. 2.  $C_1$  and  $C_2$  are charged to  $V_{dc}$  through the DC voltage source ' $2V_2$ '. Capacitor voltage balancing in the basic unit can be understood by visualizing Fig. 3. Capacitors  $C_1$  and  $C_2$  should have equal voltages. It means that the energy released from the capacitor  $C_1$  should be the same as that of the energy released from the capacitor  $C_2$  in one complete cycle. Taking  $3^{rd}$  level

TABLE 1. Different switching states of the proposed Inverter

| Switches       |       |                       |                |            |                |                       |                | Vo             | Charging Capacitor |            |

|----------------|-------|-----------------------|----------------|------------|----------------|-----------------------|----------------|----------------|--------------------|------------|

| S <sub>1</sub> | $S_2$ | <b>S</b> <sub>3</sub> | S <sub>4</sub> | <b>S</b> 5 | S <sub>6</sub> | <b>S</b> <sub>7</sub> | S <sub>8</sub> | S <sub>9</sub> |                    |            |

| 0              | 1     | 0                     | 0              | 0          | 1              | 1                     | 0              | 0              | 0                  | $C_1, C_2$ |

| 0              | 1     | 0                     | 0              | 0          | 1              | 0                     | 0              | 1              | $V_2$              |            |

| 0              | 1     | 0                     | 0              | 0          | 1              | 0                     | 1              | 0              | $2V_2$             | $C_1, C_2$ |

| 1              | 0     | 0                     | 1              | 0          | 0              | 1                     | 0              | 0              | $V_1 - 2V_2$       | $C_1, C_2$ |

| 1              | 0     | 0                     | 1              | 0          | 0              | 0                     | 0              | 1              | $V_1 - V_2$        |            |

| 1              | 0     | 0                     | 1              | 0          | 0              | 0                     | 1              | 0              | $V_1$              |            |

| 1              | 0     | 0                     | 0              | 0          | 1              | 0                     | 0              | 1              | $V_1 + V_2$        |            |

| 1              | 0     | 0                     | 0              | 0          | 1              | 0                     | 1              | 0              | $V_1 + 2V_2$       | $C_1, C_2$ |

| 1              | 0     | 0                     | 0              | 1          | 0              | 0                     | 1              | 0              | 0                  | $C_1, C_2$ |

| 1              | 0     | 0                     | 0              | 1          | 0              | 0                     | 0              | 1              | $-V_2$             |            |

| 1              | 0     | 0                     | 0              | 1          | 0              | 1                     | 0              | 0              | $-2V_2$            | $C_1, C_2$ |

| 0              | 1     | 1                     | 0              | 0          | 0              | 0                     | 1              | 0              | $-(V_1-2V_2)$      | $C_1, C_2$ |

| 0              | 1     | 1                     | 0              | 0          | 0              | 0                     | 0              | 1              | $-(V_1-V_2)$       |            |

| 0              | 1     | 1                     | 0              | 0          | 0              | 1                     | 0              | 0              | $-V_1$             |            |

| 0              | 1     | 0                     | 0              | 1          | 0              | 0                     | 0              | 1              | $-(V_1 + V_2)$     |            |

| 0              | 1     | 0                     | 0              | 1          | 0              | 1                     | 0              | 0              | $-(V_1+2V_2)$      | $C_1, C_2$ |

FIGURE 2. Switching states of the inverter.

FIGURE 3. Typical 15 level output voltage showing capacitor voltage balance.

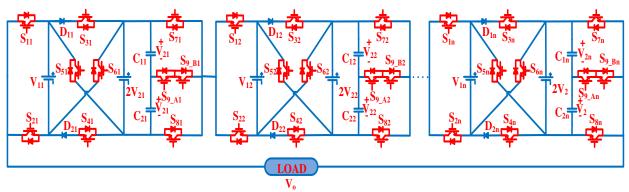

FIGURE 4. Extension of the proposed topology.

as an example, the voltage waveforms at level  $+3V_{dc}(\theta_2)$ to  $\theta_3$ ) and  $-3V_{dc}(\pi + \theta_2)$  to  $\pi + \theta_3$ ) are the same, as shown in Fig. 3. Similarly, the current waveforms will also be equal. Hence energy stored in positive and corresponding negative levels is equal, and thus the capacitor voltage balance is maintained.

### C. TOPOLOGY EXTENSION

Higher levels at the output can be achieved by connecting the basic unit in cascade form. Fig. 4 shows the extension of the presented structure. The output voltage of the overall system will be the sum of output voltages of the individual units i: e

$$V_o = V_1 + V_2 + \dots + V_n \tag{2}$$

Where  $V_1, V_2, V_n$  represents the output voltages of the first, second, and nth unit, respectively. The required number of switches  $(N_{sw})$ , the number of levels  $(N_L)$ , number of DC voltage sources  $(N_{dc})$ , number of capacitors  $(N_{cap})$ , number of drivers  $(N_{dr})$  maximum output voltage  $(V_{o,max})$  and total blocked voltage of all the switches  $(V_{TR})$  can be expressed by

$$N_{sw} = 10n \tag{3}$$

$$N_L = 15n \tag{4}$$

$$N_{cap} = N_{dc} = 2n$$

$$N_{dr} = 8n$$

(5)

$$N_{dr} = 8n \tag{6}$$

$$V_{o.max} = (15n - 1)/2 (7)$$

$$V_{TB} = 44(15n - 1)/14 (8)$$

Where, n is the number of basic units.

# **III. MODULATION STRATEGY**

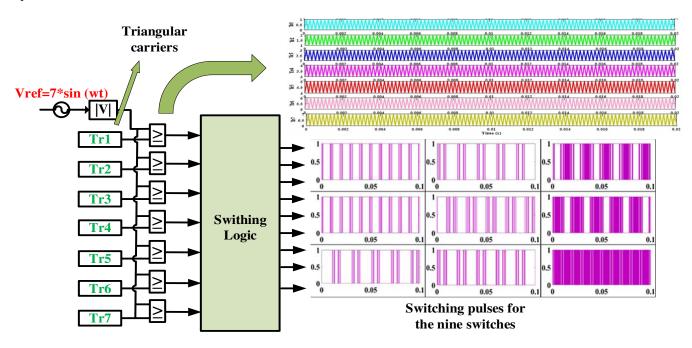

Modulation techniques play an important role in multilevel inverters since they affect control dynamics, harmonics, switching loss, filter size, etc. Increased switching loss, high complexity, higher switching harmonics, and increased switching frequency exist in traditional modulation methods. The level-shifted PWM method has been used here to obtain the necessary gate pulses. A single sinusoidal reference waveform is compared with the seven carrier signals (Tr1 to Tr7), as shown in Fig. 5, to generate seven new signals, which are then modified according to the switching logic given in Table 1 to obtain the required gate pulses. The reference and carrier signals have the amplitude of 7 and 1, respectively. Here carrier frequency is taken to be 5 kHz.

2 VOLUME XX. 2017

# IV. CALCULATION OF THE TOTAL BLOCKED VOLTAGE IN THE SWITCHES

The total blocked voltage  $(V_{TB})$  of all the switches is an essential parameter in the design of inverter as it influences the overall price of the inverter. Its low value suggests a lower cost of the inverter. We can calculate it by using the following equation:

$$V_{TB} = V_{TB.u} + V_{TB.b} \tag{9}$$

Where,  $V_{TB,u}$  and  $V_{TB,b}$  are the blocking voltages of the unidirectional and bidirectional switches, respectively. As there are eight unidirectional switches in each unit and the total unit count is 'n',  $V_{TB,u}$  is written as:

$$V_{TB,u} = \sum_{i=1}^{n} \sum_{j=1}^{8} V_{S_{ij}}$$

(10)

FIGURE 5. Level shifted PWM technique used for the proposed SCMLI.

Where,  $V_{Sii}$  is the blocking voltage of the j<sup>th</sup> unidirectional switch for the ith unit. These blocked voltages can be calculated as follows:

$$V_{S,i} = V_{S,i} = V_{1i} = 5V_{2i} \tag{11}$$

$$V_{\text{S}} = V_{\text{S}} = V_{\text{F}i} = V_{\text{G}i} = V_{1i} + 2V_{2i} = 7V_{2i}$$

(12)

$$V_{7i} = V_{0i} = 2V_{2i} \tag{13}$$

$V_{S_{1i}} = V_{S_{2i}} = V_{1i} = 5V_{2i}$   $V_{S_{3i}} = V_{S_{4i}} = V_{5i} = V_{6i} = V_{1i} + 2V_{2i} = 7V_{2i}$   $V_{7i} = V_{8i} = 2V_{2i}$   $V_{S_{1i}}, V_{S_{2i}}, \dots, V_{S_{8i}} \text{ are the blocked voltages of the}$  (11)unidirectional switches in the ith unit. So, the gross blocking voltage of the whole cascaded units will be the sum of all the individual units and can be written as:

$$V_{TB,u} = \sum_{i=1}^{n} 42 \, V_{2i} \tag{14}$$

Since there is only one bidirectional switch i: e switch number

$$V_{TB,b} = \sum_{i=1}^{n} V_{S_{9i}} = \sum_{i=1}^{n} 2V_{2i}$$

(15)

By substituting equations (14) and (15) in equation (9), the gross blocked voltage of all the switches will be:

$$V_{TB} = V_{TB,u} + V_{TB,b} = \sum_{i=1}^{n} 44V_{2i}$$

(16)

The maximum output voltage of the presented structure is given by:

$$V_{0 max} = \sum_{i=1}^{n} V_{1i} + \sum_{i=1}^{n} 2V_{2i}$$

(17)

$V_{o,max} = \sum_{i=1}^{n} V_{1i} + \sum_{i=1}^{n} 2V_{2i}$ Since,  $V_{1i} = 5V_{2i}$ , equation (17) can be written as:

$$V_{o,max} = \sum_{i=1}^{n} 7V_{2i} \tag{18}$$

$V_{o,max} = \sum_{i=1}^{n} 7V_{2i}$  Using equation (16) and (18), we have

$$V_{TB} = \frac{44}{7} V_{o,max} = 6.28 V_{o,max} \tag{19}$$

Relationship between  $V_{o,max}$  and  $N_L$  (number of levels) can also be written as:

$$V_{o,max} = \frac{N_L - 1}{2}$$

(20)

By combining equations (19) and (20), the value of overall blocked voltage will be:

$$V_{TB} = \frac{44}{14}(N_L - 1) = 3.14(N_L - 1) \tag{21}$$

Table 2 gives the number of levels  $(N_L)$ , number of units (n), number of DC voltage sources  $(N_{dc})$ , number of switches  $(N_{sw})$ , number of capacitors  $(N_{cap})$ , number of drivers  $(N_{dr})$ maximum output voltage  $(V_{o,max})$  and total blocked voltage of all the switches  $(V_{TB})$  based on  $N_L$  and n.

Different equations of the proposed MLI

| TABLE 2. Different equations of the proposed MLI |                                      |                                      |  |  |  |  |  |

|--------------------------------------------------|--------------------------------------|--------------------------------------|--|--|--|--|--|

| Parameters                                       | In terms of number of levels $(N_L)$ | In terms of<br>number of<br>units(n) |  |  |  |  |  |

| Units (n)                                        | $log_{15}(N_L)$                      | n                                    |  |  |  |  |  |

| Levels $(N_L)$                                   | $N_L$                                | 15n                                  |  |  |  |  |  |

| D.C. voltage sources $(N_{DC})$                  | $2log_{15}(N_L)$                     | 2n                                   |  |  |  |  |  |

| Diodes $(N_D)$                                   | $2log_{15}(N_L)$                     | 2n                                   |  |  |  |  |  |

| Switches $(N_{SW})$                              | $10log_{15}(N_L)$                    | 10n                                  |  |  |  |  |  |

| Drivers $(N_{DR})$                               | $9log_{15}(N_L)$                     | 8n                                   |  |  |  |  |  |

| Capacitors $(N_c)$                               | $2log_{15}(N_L)$                     | 2n                                   |  |  |  |  |  |

| Maximum output voltage $(V_{o,max})$             | $(N_L - 1)/2$                        | (15n-1)/2                            |  |  |  |  |  |

| Total blocked voltage $(V_{TB})$                 | $44(N_L-1)/14$                       | 44(15n-1)/14                         |  |  |  |  |  |

VOLUME XX. 2017 2

# V. COMPARISON OF THE PROPOSED MLI WITH OTHER STRUCTURES

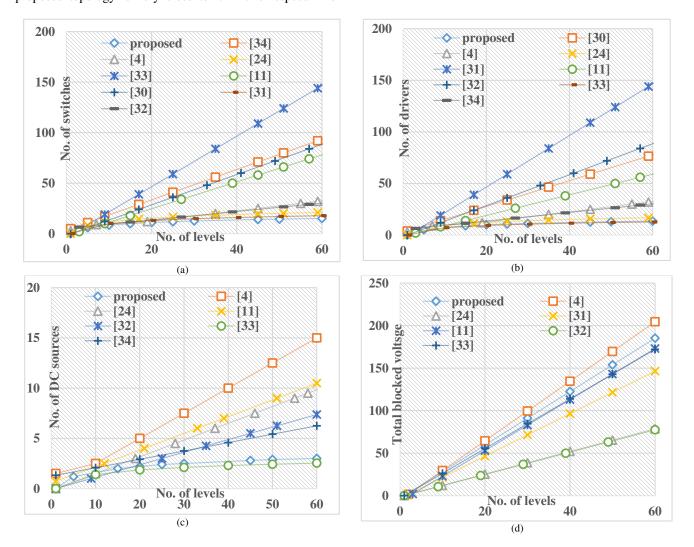

In this section, the practicality of the presented MLI is validated by comparing the number of switches  $(N_{SW})$ , number of drivers  $(N_{DR})$ , number of DC sources  $(N_{DC})$ , number of capacitors  $(N_C)$ , number of diodes  $(N_D)$  and total blocked voltage  $(V_{TB})$  of all the switches with recently published topologies [4], [11], [24], [30]-[34]. Fig. 6(a) compares the number of switches, i: e, power IGBTs with respect to the number of levels for the presented topology and topologies given in [4], [11], [24], [30]-[34]. The figure clearly shows that the presented structure uses the least switch count among these topologies. The driver required is plotted against the number of levels in Fig. 6(b). The presented structure and the structures presented in [33] use the lowest number of drivers compared to these topologies. Fig. 6(c) shows the plot between the DC supply count and the number of levels. The topology presented in [33] has the least DC supply, and the proposed topology is very close to it in this respect. The

proposed structure requires fewer DC sources than the structures presented in [4], [11], [24], [32], and [34]. Fig. 6(d) shows the plot of total blocked voltage and the number of levels. Structures presented in [11], [24], [31]-[33] have lower total block voltage values with respect to the proposed design. The proposed structure has a smaller gross blocked voltage than the one presented in [4]. Furthermore, a summary of recently published MLIs has been presented in Table 3.

TABLE 3. Comparison with 15 level MLIs

| Topologies | N <sub>DC</sub> | N <sub>SW</sub> | $N_{DR}$ | N <sub>C</sub> | $N_D$ | $V_{TB}/N_L$ | η<br>(%) |

|------------|-----------------|-----------------|----------|----------------|-------|--------------|----------|

| [3]        | 5               | 10              | 10       | 0              | 0     | -            | 93.73    |

| [20]       | 1               | 14              | 14       | 4              | 2     | 4.86         | -        |

| [32]       | 4               | 10              | 9        | 0              | 0     | 4.6          | 97.5     |

| [33]       | 3               | 8               | 8        | 0              | 0     | 2            | 95.2     |

| [34]       | 3               | 10              | 9        | 0              | 0     | 2.26         | -        |

| [35]       | 5               | 10              | 10       | 0              | 2     | 1.06         | 90       |

| Proposed   | 2               | 10              | 8        | 2              | 2     | 3.6          | 96.3     |

FIGURE 6. Comparison of presented structure with different structures in terms of (a) number of switches  $(N_{sw})$  (b) number of drivers  $(N_{dr})$  (c) number of DC sources  $(N_{dc})$  (d) total blocked voltage  $(V_{TB})$ .

#### VI. POWER LOSS ANALYSIS

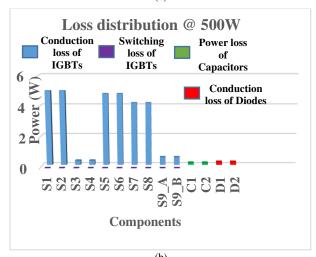

Estimation of the losses of the proposed structure has been done using PLECS software. By using these losses, the efficiency of the suggested topology is calculated. The thermal modeling part of the software is used for the calculation of different losses in the switches, capacitors, and diodes. The switch used for this study is IGA30N60H3. Losses considered under this study include: conduction losses ( $P_C$ ) of all the semiconductor devices, switching losses ( $P_S$ ), and ESR losses ( $P_{ESR}$ ) of the capacitors. Ripple loss is also there in capacitors, but here it is not included in the calculations. The calculations involved in this study are based on the fundamental switching frequency approach [15].

## A. SWITCHING LOSS $(P_S)$

Switching losses occur at the point of turning ON or OFF of the switches. By considering the linear approximation of the switch voltage and current at the time of switching, the following relations for the kth switch can be written as:

Power loss during switching  $ON = P_{S,on,k} =$

$$\int_0^{t_{on}} v(t)i(t)dt$$

$$= f \int_0^{t_{on}} \left( \frac{V_{S,k}}{t_{on}} t \right) \left( -\frac{I_k}{t_{on}} (t - t_{on}) \right) dt = \frac{1}{6} f V_{S,k} I_k$$

(22)

Loss of power during switching OFF=  $P_{S,off,k}$  =

$$\int_0^{t_{off}} v(t)i(t)dt$$

$$= f \int_0^{t_{off}} \left( \frac{V_{S,k}}{t_{off}} t \right) \left( -\frac{I_k'}{t_{off}} \left( t - t_{off} \right) \right) dt = \frac{1}{6} f V_{S,k} I_k' t_{off}$$

(23)

where  $I_k$  and  $I_k$  are the currents flowing through the kth switch at the time of switching ON, and before switching OFF respectively, f is the switching frequency and  $V_{S,k}$  is the voltage of the switch in OFF-state. Switching loss of all the ten switches can be obtained by multiplying the ON  $(N_{on})$  and the OFF number of switching states  $(N_{off})$  in a cycle with (22) and (23) following (24):

$$P_{S} = \sum_{k=1}^{10} \left( \sum_{m=1}^{N_{on}} P_{S,on,km} + \sum_{m=1}^{N_{off}} P_{S,off,km} \right)$$

(24)

#### B. CONDUCTION LOSS $(P_C)$

The internal resistance of power switches and diodes is also considered for the calculation of losses in conduction mode for the steady-state condition. All capacitors are supposed to be equal. PLECS software is used for taking the results. The load is taken as resistive since resistive loading is considered the worst-case scenario in analyzing loss of power in SCMLIs [39], [40], [41].

# C. CAPACITOR ESR LOSSES $(P_{ESR})$

The equivalent series resistance of the capacitors depends on the frequency of the current flowing through the capacitor [42]. It can be defined as the conduction loss caused by the internal resistance of the capacitor. Here 0.1 ohm is taken as the internal resistance of both the capacitors. These losses also affect the lifetime of capacitors due to thermal stress and heat dissipation caused. All these three losses are simulated in PLECS.

Therefore, the overall efficiency of the presented SCMLI is given by (25).

$$\eta = \frac{P_o}{P_o + P_S + P_C + P_{ESR}} \tag{25}$$

Fig. 7(a) shows the proposed topology's efficiency versus output power curve for a resistive load. The efficiency curve shows a peak value of about 96.33%, along with a 10 watts output power. The contribution of different components such as diodes, switches, and capacitors in the power loss has been given in Fig. 7(b). S9 is the bidirectional switch, as shown in Fig. 1. Both the switches S9\_A and S9\_B of the bidirectional switch have the same loss. Equal losses are there in the complementary switches since the turn ON and OFF count in a full cycle are equal.

FIGURE 7. (a) Inverter efficiency at different output power (b) Loss distribution of different components.

# **VII. RESULTS AND DISCUSSION**

Simulation of the suggested structure is done on Matlab® 2018a. For the verification of the simulation results obtained, results have also been taken on an experimental prototype. The subsequent subsection discusses the simulation and experimental results.

## A. SIMULATION RESULTS

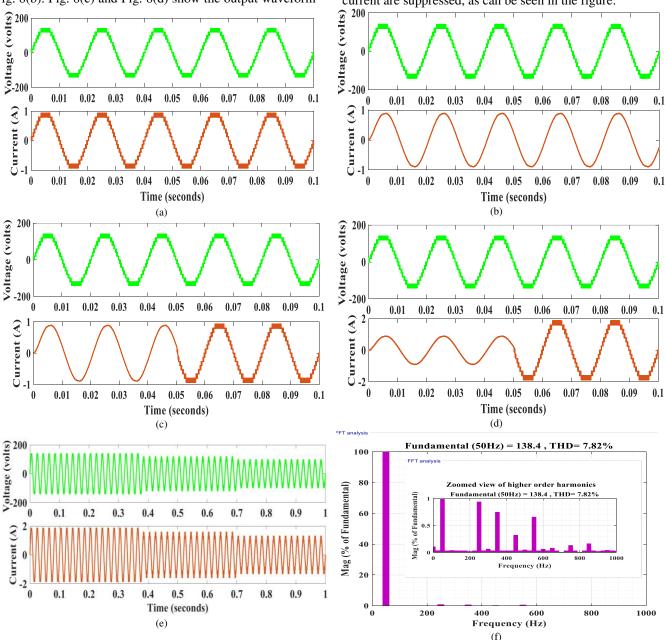

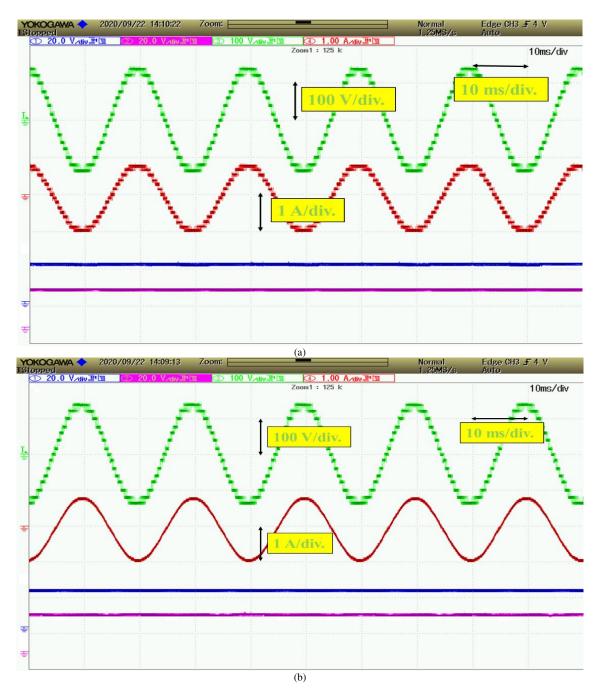

For the simulation purpose, DC supplies  $V_1$  and  $V_2$  have values of 100 volts and 20 volts. Both the capacitors used have the same magnitude of 4700  $\mu$ F with an internal resistance of 0.1 $\Omega$ . Fig. 8 and Fig. 9 show the different simulation results of the presented structure. Fig. 8(a) expresses the fifteen-level output waveform for the resistive load of 150 ohms. The output has a peak voltage of 140 V with a step voltage of 20 V. The output voltage and current waveforms for an RL load of Z=150 $\Omega$ +120mH are given in Fig. 8(b). Fig. 8(c) and Fig. 8(d) show the output waveform

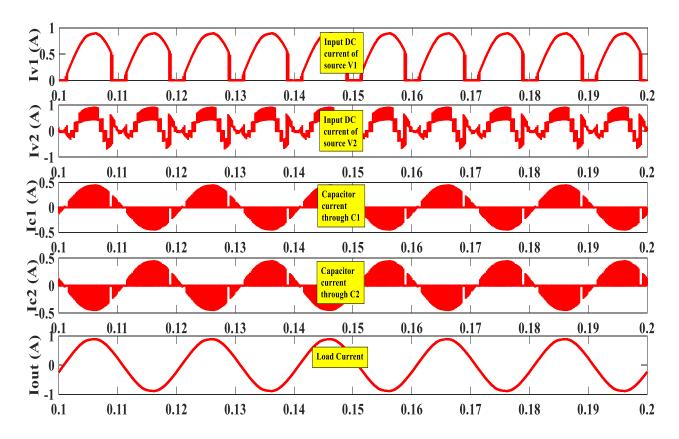

under a dynamic load change from Z=150 $\Omega$  +120mH to a resistive load of 150 ohms and from Z=150 $\Omega$  +120mH to a load of 75 ohms, respectively. Fig. 8(e) shows the output waveform under the dynamic alteration of the modulation index (MI). The output levels obtained is proportional to the MI. Fig. 8(f) depicts the FFT analysis. The figure displays the THD of the output voltage at 7.82%. Fig. 9 shows the current of the input DC sources  $V_1$  and  $V_2$ , the current flowing through capacitors  $C_1$  and  $C_2$ , and load current when an RL load of Z=150 $\Omega$ +120mH is taken. Spikes in capacitor current are suppressed, as can be seen in the figure.

FIGURE 8. Simulation results (a) Output waveform for the resistive load of  $150\Omega$  (b) Output waveform of RL load of Z= $150\Omega$  +120mH (c) Output waveform for dynamic change of load from Z= $150\Omega$  +120mH to resistive load of  $150\Omega$  (d) Output waveform for dynamic load change from Z= $150\Omega$  +120mH to a resistive load of  $75\Omega$  (e) Output voltage and current for dynamic alteration of MI (f) Harmonic profile of the output voltage at a load of  $75\Omega$ .

FIGURE 9. Waveforms showing Input DC current for sources  $V_1$  and  $V_2$ , Capacitor currents for Capacitors  $C_1$  and  $C_2$ , and load current at a load of Z=150 $\Omega$  +120mH.

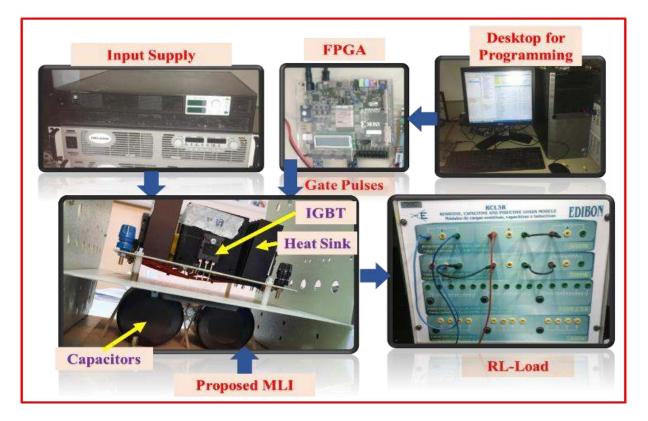

FIGURE 10. Experimental setup.

2

FIGURE 11. (a) Output waveform for a resistive load of 150 $\Omega$  (b) Output waveform of RL load of Z=150 $\Omega$  +120mH.

#### B. EXPERIMENTAL RESULTS

To verify the simulation results obtained, an experimental prototype has been developed, as shown in Fig. 10. Fig. 11 to Fig. 13 show similar results obtained experimentally for the same specification of different components. The switch used is Toshiba IGBT GT50J325, and the dSPACE 1104 is used as the controller to generate the required gate signals. For the experimental verification, DC supplies V1 and V2 are taken as 100 volts and 20 volts, respectively. Fig. 11(a) and Fig. 11(b) show the output waveform for a resistive load of 150 ohms and an RL load of  $Z=150\Omega+120 \mathrm{mH}$ ,

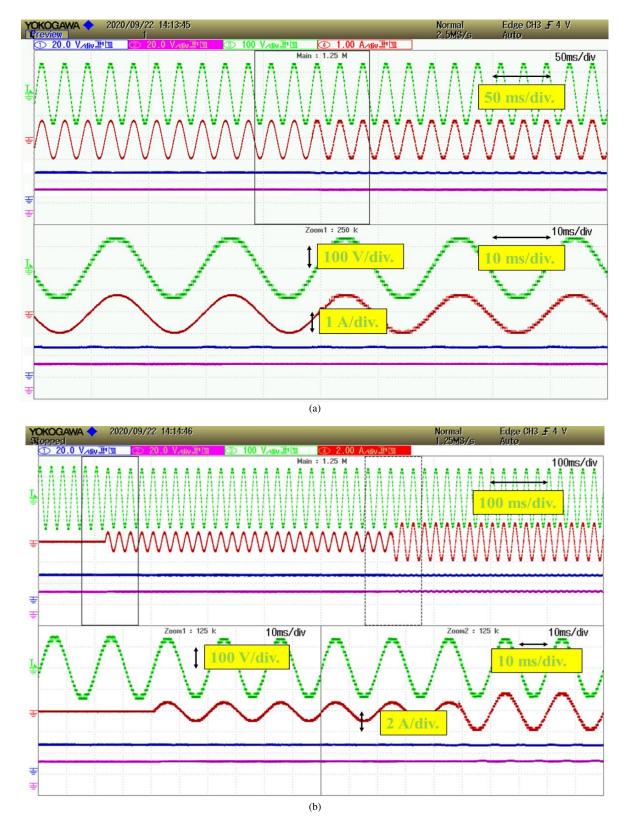

respectively. The output has a peak voltage of 140 V with a step voltage of 20 V. Fig. 12(a) and Fig. 12(b) show the output voltage and current for a dynamic load change from Z=150 $\Omega$  +120mH to a load of 150 ohms, and from 0 to Z=150 $\Omega$ +120mH to a load of 75 ohms respectively. Fig. 13 shows the output waveforms for the dynamic change in MI. The number of levels decreases proportionally as the modulation index is reduced as can be seen in the waveform.

FIGURE 12. (a) Output waveform for dynamic change of load from no load to Z=150 $\Omega$  +120mH to resistive load of 150  $\Omega$  (b) Output waveform for dynamic

FIGURE 13. Output waveform for dynamic alteration of modulation index.

#### VIII. CONCLUSION

A new SCMLI structure has been suggested here. The proposed topology can generate fifteen levels per unit, and it can also be extended for getting higher output levels. It has the lowest switch count, and the number of drivers required compared to the recent topologies present in the literature. Capacitor voltage balance is also maintained. A multicarrier level shifted modulation technique has been implemented here. Hardware implementation of the presented structure has been done for the validation of the simulation results at different loading conditions and changing modulation indices. Thus the presented structure can be a viable option for industrial use.

#### **REFERENCES**

- [1] S. Nagaraja Rao and V. Praveen Kumar, "Comparative analysis of switched capacitor based multilevel inverters with self voltage balancing," *J. Adv. Res. Dyn. Control Syst.*, vol. 10, no. 9 Special Issue, pp. 1841–1855, 2018.

- [2] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, "A survey on cascaded multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2197–2206, 2010.

- [3] B. Mahato, S. Majumdar, S. Vatsyayan, and K. C. Jana, "A New and Generalized Structure of MLI Topology with Half-bridge Cell with Minimum Number of Power Electronic Devices," *IETE Tech. Rev.* (Institution Electron. Telecommun. Eng. India), pp. 1–12, 2020.

- [4] T. Roy, P. K. Sadhu, and A. Dasgupta, "Cross-Switched Multilevel Inverter Using Novel Switched Capacitor Converters," *IEEE Trans. Ind. Electron.*, vol. 66, no. 11, pp. 8521–8532, 2019.

- [5] K. K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu, and S. Jain, "Multilevel Inverter Topologies With Reduced Device Count: A Review," *IEEE Trans. Power Electron.*, vol. 31, no. 1, pp. 135–151, Jan. 2016.

- [6] R. Samanbakhsh and A. Taheri, "Reduction of Power Electronic Components in Multilevel Converters Using New Switched Capacitor-Diode Structure," *IEEE Trans. Ind. Electron.*, vol. 63, no. 11, pp. 7204–7214, 2016.

- [7] R. Barzegarkhoo, E. Zamiri, N. Vosoughi, H. M. Kojabadi, and L. Chang, "Cascaded multilevel inverter using series connection of novel capacitor-based units with minimum switch count," *IET Power Electron.*, vol. 9, no. 10, pp. 2060–2075, 2016.

- [8] M. Tayyab, A. Sarwar, M. Tariq, R. K. Chakraborty, and M. J. Ryan, "Hardware-In-the-Loop Implementation of projectile target search algorithm for selective harmonic elimination in a 3-phase multilevel converter," *IEEE Access*, 2020.

- [9] A. Iqbal, M. D. Siddique, P. R. Bhimireddy, and K. M. Pandav, "Quadruple Boost Multilevel Inverter (QB-MLI) Topology with Reduced Switch Count," *IEEE Trans. Power Electron.*, vol. 36, no. 7, pp. 7372-7377, 2021.

- [10] B. P. Reddy, M. D. Siddique, A. Iqbal, S. Mekhilef, S. Rahman, and P. K. Maroti, "7L-SCBI topology with minimal semiconductor device count," vol. 13, pp. 3199–3203, 2020.

- [11] T. Roy and P. K. Sadhu, "A novel symmetric switched capacitor multilevel inverter using non-isolated power supplies with reduced number of components," Sadhana - Acad. Proc. Eng. Sci., vol. 45, no. 1, 2020.

- [12] R. Abdullah, N. A. Rahim, S. R. Sheikh Raihan, and A. Z. Ahmad, "Five-level diode-clamped inverter with three-level boost converter," *IEEE Trans. Ind. Electron.*, vol. 61, no. 10, pp. 5155–5163, 2014.

- [13] P. R. Kumar, R. S. Kaarthik, K. Gopakumar, J. I. Leon, and L. G. Franquelo, "Seventeen-level inverter formed by cascading flying capacitor and floating capacitor H-bridges," *IEEE Trans. Power Electron.*, vol. 30, no. 7, pp. 3471–3478, 2015.

- [14] M. R. Hussan *et al.*, "A novel switched-capacitor multilevel inverter topology for energy storage and smart grid applications," *Electron.*, vol. 9, no. 10, 2020.

- [15] R. Barzegarkhoo, H. M. Kojabadi, E. Zamiry, N. Vosooghi, and L. Chang, "Generalized Structure for a Single Phase Switched- Capacitor Multilevel Inverter Using a New Multiple Dc Link Producer with Reduced Number of Switches," *IEEE Trans. Power Electron.*, vol. 31, no. 8, 2015.

- [16] Y. Ye, K. W. E. Cheng, J. Liu, and K. Ding, "A step-up switched-capacitor multilevel inverter with self-voltage balancing," *IEEE Trans. Ind. Electron.*, vol. 61, no. 12, pp. 6672–6680, 2014.

- [17] Y. Hinago and H. Koizumi, "A switched-capacitor inverter using series/parallel conversion with inductive load," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 878–887, 2012.

- [18] B. Axelrod, Y. Berkovich, and A. Ioinovici, "A cascade boost-switched-capacitor-converter two level inverter with an optimized multilevel output waveform," *IEEE Trans. Circuits Syst. I Regul. Pap.*, vol. 52, no. 12, pp. 2763–2770, 2005.

- [19] J. Liu, K. W. E. Cheng, and Y. Ye, "A cascaded multilevel inverter based on switched-capacitor for high-frequency A.C. power distribution system," *IEEE Trans. Power Electron.*, vol. 29, no. 8, pp. 4219–4230, 2014.

- [20] M. J. Sathik, N. Sandeep, D. Almakhles, and F. Blaabjerg, "Cross Connected Compact Switched-Capacitor Multilevel Inverter (C3-SCMLI) Topology with Reduced Switch Count," *IEEE Trans. Circuits Syst. II Express Briefs*, vol. 67, no. 12, pp. 3287–3291, 2020.

- [21] S. S. Lee, "Single-Stage Switched-Capacitor Module (S3CM) Topology for Cascaded Multilevel Inverter," *IEEE Trans. Power Electron.*, vol. 33, no. 10, pp. 8204–8207, 2018.

- [22] J. Liu, J. Wu, and J. Zeng, "Symmetric/Asymmetric Hybrid Multilevel Inverters Integrating Switched-Capacitor Techniques," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 6, no. 3, pp. 1616–1626, 2018.

- [23] M. Samizadeh, X. Yang, B. Karami, W. Chen, F. Blaabjerg, and M. Kamranian, "A new topology of switched-capacitor multilevel inverter with eliminating leakage current," IEEE Access, vol. 8, pp. 76951–76965, 2020.

- [24] J. Liu, X. Zhu, and J. Zeng, "A Seven-Level Inverter with Self-Balancing and Low-Voltage Stress," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 8, no. 1, pp. 685–696, 2020.

- [25] B. Shiva Naik, Y. Suresh, and J. Venkataramanaiah, "Experimental verification of a hybrid multilevel inverter with voltage-boosting ability," *Int. J. Circuit Theory Appl.*, vol. 48, no. 3, pp. 420–434, 2020.

- [26] M. D. Siddique, S. Mekhilef, A. Sarwar, A. Alam, and N. M. Shah, "Dual asymmetrical dc voltage source based switched capacitor boost multilevel inverter topology," *IET Power Electron.*, vol. 13, no. 7, pp. 1481–1486, 2020.

- [27] M. S. Benmerabet, A. Talha, and E. M. Berkouk, "A novel asymmetrical inverter proposal based on switched series/parallel inverter," *Int. Trans. Electr. Energy Syst.*, vol. 29, no. 5, 2019.

- [28] S. Sabour, D. Nazarpour, S. Golshannavaz, R. Choupan, A. Yazdaninejadi, and M. Hassanifar, "A new quasi-resonant switched capacitor multilevel inverter with the self-voltage balancing capability," *Int. Trans. Electr. Energy Syst.*, no. April, pp. 1–18, 2020.

- [29] M. D. Siddique, S. Mekhilef, N. M. Shah, A. Sarwar, and M. A. Memon, "A new single-phase cascaded multilevel inverter topology with reduced number of switches and voltage stress," *Int. Trans. Electr. Energy Syst.*, vol. 30, no. 2, pp. 1–21, 2020.

- [30] M. Khenar, A. Taghvaie, J. Adabi, and M. Rezanejad, "Multilevel inverter with combined T-type and cross-connected modules," *IET Power Electron.*, vol. 11, no. 8, pp. 1–9, 2018.

- [31] A. Taghvaie, J. Adabi, and M. Rezanejad, "A Self-Balanced Step-Up Multilevel Inverter Based on Switched-Capacitor Structure," *IEEE Trans. Power Electron.*, vol. 33, no. 1, pp. 199–209, 2018.

- [32] M. Saeedian, E. Pouresmaeil, and E. Samadaei, "An Innovative Dual-Boost Nine-Level Inverter with Low-Voltage Rating Switches," vol. 12, no. 2, 2019.

- [33] A. Taheri, A. Rasulkhani, and H. P. Ren, "An Asymmetric Switched Capacitor Multilevel Inverter with Component Reduction," *IEEE Access*, vol. 7, pp. 127166–127176, 2019.

- [34] S. R. Raman, Y. C. Fong, Y. Ye, and K. W. E. Cheng, "Family of Multiport Switched-Capacitor Multilevel Inverters for High-Frequency A.C. Power Distribution," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4407–4422, 2019.

- [35] Z. Sarwer, M. D. Siddique, A. Iqbal, A. Sarwar, and S. Mekhilef, "An improved asymmetrical multilevel inverter topology with reduced semiconductor device count," *Int. Trans. Electr. Energy Syst.*, vol. 30, no. 11, pp. 1–19, 2020.

- [36] C. Dhanamjayulu, S. Padmanaban, J. B. Holm-Nielsen, and F. Blaabjerg, "Design and Implementation of a Single-Phase 15-Level

- Inverter with Reduced Components for Solar P.V. Applications," *IEEE Access*, vol. 9, pp. 581–594, 2021.

- [37] M. D. Siddique, S. Mekhilef, N. M. Shah, A. Sarwar, A. Iqbal, and M. A. Memon, "A New Multilevel Inverter Topology with Reduce Switch Count," *IEEE Access*, vol. 7, pp. 58584–58594, 2019.

- [38] P. R. Bana, K. P. Panda, S. Padmanaban, L. Mihet-Popa, G. Panda, and J. Wu, "Closed-Loop Control and Performance Evaluation of Reduced Part Count Multilevel Inverter Interfacing Grid-Connected PV System," *IEEE Access*, vol. 8, pp. 75691–75701, 2020.

- [39] E. Zamiri, N. Vosoughi, S. H. Hosseini, R. Barzegarkhoo, and M. Sabahi, "A New Cascaded Switched-Capacitor Multilevel Inverter Based on Improved Series-Parallel Conversion With Less Number of Components," *IEEE Trans. Ind. Electron.*, vol. 63, no. 6, pp. 3682–3694, 2016.

- [40] M. D. Siddique et al., "Low Switching Frequency Based Asymmetrical Multilevel Inverter Topology with Reduced Switch Count," *IEEE Access*, vol. 7, pp. 86374–86383, 2019.

- [41] A. Ahmad et al., "Realization of a generalized switched-capacitor multilevel inverter topology with less switch requirement," *Energies*, vol. 13, no. 7, 2020.

- [42] G. I. Orfanoudakis, S. M. Sharkh, and M. A. Yuratich, "Analysis of DC-link capacitor losses in three-level Neutral Point Clamped and Cascaded H-Bridge voltage source inverters," *IEEE Int. Symp. Ind. Electron.*, no. April 2015, pp. 664–669, 2010.

MD REYAZ HUSSAN was born in Gaya, India, in 1991. He received his B.Tech. degree in 2014 and M.Tech degree in 2016 in Electrical Engineering and Instrumentation and Control, respectively from the Aligarh Muslim University, Aligarh, India. He is currently a Research Scholar in the Department of Electrical Engineering, Aligarh Muslim University. His research interests include multilevel inverters and their control, photovoltaic systems, and

multilevel inverter for solar PV applications.

ADIL SARWAR (M'16 SM'21) is working with the Department of Electrical Engineering, Aligarh Muslim University, Aligarh, India since 2015. Earlier he was associated with the Electrical Engineering department of Galgotia College of Engineering and Technology, G. Noida, India from 2012 to 2015. He did his B. Tech, M. Tech and PhD from Aligarh Muslim University in 2006, 2008 and 2012

respectively. He has published more than 75 research papers in international journals and conferences. He is also working on world-bank sponsored research projects. He is a senior member of IEEE and a life member of systems society of India. He has contributed a chapter in Handbook of Power Electronics, 4ed. Edited by M. H. Rashid.

MARIF DAULA SIDDIQUE (M'20) was born in Chhapra, Bihar, India, in 1992. He received the B.Tech and M.Tech degrees in Electrical Engineering from Aligarh Muslim University (AMU) in 2014 and 2016, respectively. He received the Ph.D. degree in the Power Electronics and Renewable Energy Research Laboratory (PEARL), Department of Electrical Engineering, University of Malaya, Kuala Lumpur, Malaysia in 2021. He is currently working as Research Assistant

with the Department of Electrical Engineering, Qatar University, Doha, Qatar. He has authored or coauthored more than 50 publications in international journals and conference proceedings. His research interest includes step-up power electronics converters (dc/ac, and dc/dc), multilevel

VOLUME XX, 2017 9

inverter topologies and their control. He is serving as a regular reviewer for various journals of IEEE and IET.

ATIF IQBAL (M'08-SM'11), received B.Sc. (Gold Medal) and M.Sc. Engineering (Power System & Drives) degrees in 1991 and 1996, respectively, from the Aligarh Muslim University (AMU), Aligarh, India, and Ph.D. in 2006 from Liverpool John Moores University, Liverpool, UK. He became Fellow IET (U.K.) in 2018, Fellow I.E. (India) in 2012 and Senior Member IEEE in 2011, Ph.D. (UK)- Associate Editor IEEE Tran. on Industry Application, Editor-in-Chief, I' manager journal of Electrical Engineering, Associate Professor at Electrical

Engineering, Qatar University and Former Full Professor at Electrical Engineering, Aligarh Muslim University (AMU), Aligarh, India. Recipient of Outstanding Faculty Merit Award AY 2014-2015 and Research excellence award at Qatar University, Doha, Qatar. He has been employed as a Lecturer in the Department of Electrical Engineering, AMU, Aligarh since 1991 where he served as Full Professor until Aug. 2016. He is the recipient of Maulana Tufail Ahmad Gold Medal for standing first at B.Sc. Engg. Exams in 1991 from AMU. He has received the best research papers awards at IEEE ICIT-2013, IET-SESICON-2013, and SIGMA 2018. He has published widely in International Journals and Conferences his research findings related to Power Electronics and Renewable Energy Sources. Dr. Iqbal has authored/co-authored more than 300 research papers and one book and three chapters in two other books. He has supervised several large R&D projects. His principal area of research interest is Modeling and Simulation of Power Electronic Converters, Control of multi-phase motor drives and Renewable Energy sources.

BASEM ALAMRI (Member, IEEE) received the B.Sc. degree (Hons.) in electrical engineering from the King Fahd University of Petroleum and Minerals (KFUPM), the M.Sc. degree (Hons.) in electrical power systems from King Abdulaziz University, Jeddah, Saudi Arabia, the M.Sc. degree in sustainable electrical power from Brunel University, London, U.K., in 2007 and 2008, respectively, and the Ph.D. degree in electrical power engineering from Brunel University, in 2017.

He is currently an Assistant Professor of Electrical Engineering with the College of Engineering, Taif University. His research interests include power systems, power quality, power filter design, and smart grids, with a particular emphasis on the integration of renewable energy sources with power grids. He is a member of many international and local professional organizations. He is also a Certified Energy Auditor (CEA ®), Certified Energy Manager (CEM ®), and a Certified Measurement & Verification Professional (CMVP ®) of the Association of Energy Engineers (AEE), USA. He has received many awards and prizes, including a certificate from the Advance Electronics Company (AEC) in recognition of the Outstanding Academic Achievement during the B.Sc. degree with KFUPM. He also received the National Grid (NG) Prize, the Power Grid Operator in the U.K., for being the top distinction student of the M.Sc. degree of the SEP Program with Brunel.

VOLUME XX, 2017 9