Open access • Proceedings Article • DOI:10.23919/VLSIC.2019.8777971

### A Crystal-Free Single-Chip Micro Mote with Integrated 802.15.4 Compatible Transceiver, sub-mW BLE Compatible Beacon Transmitter, and Cortex M0

— Source link < □</p>

Filip Maksimovic, Brad Wheeler, David C. Burnett, Osama Khan ...+13 more authors

Institutions: University of California, Berkeley, Open University of Catalonia, French Institute for Research in Computer Science and Automation

Published on: 09 Jun 2019 - Symposium on VLSI Circuits

Topics: System on a chip, Transceiver, Radio transmitter design and Transmitter

#### Related papers:

- · A 1.53 mm 3 crystal-less standards-compliant Bluetooth Low Energy module for volume constrained wireless sensors

- A low-power monolithic CMOS transceiver for 802.11b wireless LANs

- A 0.85mm 2 BLE Transceiver with Embedded T/R Switch, 2.6mW Fully-Passive Harmonic Suppressed Transmitter and 2.3mW Hybrid-Loop Receiver

- A 0.85mm 2 BLE Transceiver Using an On-Chip Harmonic-Suppressed RFIO Circuitry With T/R Switch

- An ultra-low-power 868/915 MHz RF transceiver for wireless sensor network applications

# A Crystal-Free Single-Chip Micro Mote with Integrated 802.15.4 Compatible Transceiver, sub-mW BLE Compatible Beacon Transmitter, and Cortex M0

Filip Maksimovic, Brad Wheeler, David Burnett, Osama Khan, Sahar Mesri, Iona Suciu, Lydia Lee, Alex Moreno, Arvind Sundararajan, Bob Zhou, et al.

#### ▶ To cite this version:

Filip Maksimovic, Brad Wheeler, David Burnett, Osama Khan, Sahar Mesri, et al.. A Crystal-Free Single-Chip Micro Mote with Integrated 802.15.4 Compatible Transceiver, sub-mW BLE Compatible Beacon Transmitter, and Cortex M0. 2019 VLSI - IEEE Symposium on VLSI Technology & Circuits, Jun 2019, Kyoto, Japan. 10.23919/VLSIC.2019.8777971. hal-02420868

HAL Id: hal-02420868

https://hal.inria.fr/hal-02420868

Submitted on 7 Jan 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## A Crystal-Free Single-Chip Micro Mote with Integrated 802.15.4 Compatible Transceiver, sub-mW BLE Compatible Beacon Transmitter, and Cortex M0

Filip Maksimovic<sup>1</sup>, Brad Wheeler<sup>1</sup>, David C. Burnett<sup>1</sup>, Osama Khan<sup>1</sup>, Sahar Mesri<sup>1</sup>, Ioana Suciu<sup>3</sup>, Lydia Lee<sup>1</sup>, Alex Moreno<sup>1</sup>, Arvind Sundararajan<sup>1</sup>, Bob Zhou<sup>1</sup>, Rachel Zoll<sup>1</sup>, Andrew Ng<sup>1</sup>, Tengfei Chang<sup>2</sup>, Xavier Villajosana<sup>3</sup>, Thomas Watteyne<sup>2</sup>, Ali Niknejad<sup>1</sup>, and Kristofer S.J. Pister<sup>1</sup>

Dept. of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA, USA

<sup>2</sup>Inria, EVA Team, Paris, France<sup>2</sup>; <sup>3</sup>Universitat Oberta de Catalunya, Barcelona, Spain

#### **Abstract**

We present an 802.15.4 compatible transceiver that operates without any off-chip frequency reference. With integrated Cortex-M0, the chip can also transmit BLE beacons with only three external connections (power, ground, and antenna). The RF transmitter operates with >10% system efficiency at -10 dBm output power from a regulated supply. The entire chip, including the microprocessor, can operate below 1 mW peak power when transmitting. The analog receiver power consumption is 1.03 mW from a 1.5V battery. **Keywords:** low-power radio, system-on-chip, smart dust, crystal free, BLE, 802.15.4

#### Introduction

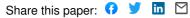

Building a standards compatible 802.15.4 or BLE radio with no crystal reference is challenging due to local oscillator (LO) frequency drift, phase noise, chip/bit clock jitter, and real time clock jitter (for time slotted protocols). We report a low-power transceiver (TRX) that, through one-time calibration and periodic network compensation, operates without the use of an external frequency reference while maintaining compatibility with commercial off-the-shelf 802.15.4 wireless SoCs. The key elements of our solution are a digital controlled oscillator (DCO) with a sourcedegenerated capacitor DAC for fine-tuning/ modulation, and a combination of room-temperature frequency calibration with a network-based IF-tracking loop in the receiver. The transmitter (TX) is also capable of transmitting BLE advertising (iBeacon) packets using only power, ground, and antenna connections, and no other external components. The TRX is co-integrated with a Cortex-M0 and packet handling.

#### **Implementation and Measured Results**

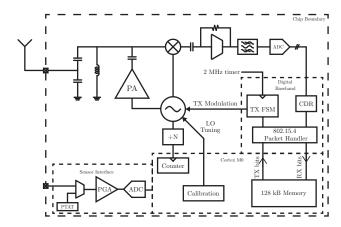

The RF DCO is implemented with a class-B CMOS LC tank architecture. The thick-metal 65 nm process allows for a large inductance and high Q (7.4 nH and a Q of 18, both simulated). A high LQ product is important for having a voltage large swing, which impacts both mixer and PA performance so that no power is burned in high frequency LO buffering. Two separate, overlapping, 5-bit capacitor DACs located at the drains of the cross-coupled devices are used for band and channel tuning. 5-bit fine tuning and direct frequency modulation is performed with a degenerated capacitor [1]. The minimum frequency resolution is between 90 kHz and 100 kHz across the ISM band (an equivalent ΔC of ~9.4 aF) without the use of a varactor, series capacitor, or dithering. The full DCO tuning range is 26%, and the peak FOM is -188 dBc/Hz. A benefit of operating without a PLL, in addition to power savings, is a reduced turn-on time. With a pre-set frequency, the LO settles from cold start within 50 μs (Fig. 2). This is limited by the settling time of the constant-g<sub>m</sub> current source that is filtered to prevent its noise from degrading the phase noise of the oscillator. An integer divider is used for LO frequency calibration and testing, and

can be used for chipping clocks of both 802.15.4 and BLE TX.

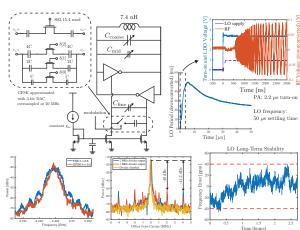

Transmitter efficiency versus output power is shown in Fig. 3. The peak system (LO + PA) sub-mW efficiency is 11.8% at approximately -10 dBm output power with a TX power consumption of 847  $\mu W$ . This power does not include microprocessor power and is calculated from the regulated PA and LO voltages (~800 mV). The transmitter can back off to -20 dBm output power with 600  $\mu W$  power consumption from a 1.5 V battery voltage, albeit at < 2% system efficiency.

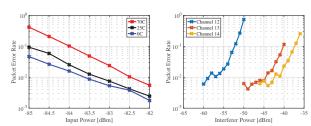

The receiver is a mixer-first low-IF architecture that uses a passive resonant tapped-capacitor match both for voltage gain and to boost the 50  $\Omega$  source impedance to approximately 1.1 k $\Omega$  (simulated). In-phase and quadrature oscillation is derived from the LO with a single stage RC polyphase filter. The complex down-conversion mixer is followed by an OTA with tunable resistive feedback for gain control. Filtering is performed using a series of three second-order discrete-time switched-capacitor IIR filter stages [2] that form a bandpass filter centered at the 2.5 MHz IF. The signal is sampled with two four-bit ADCs at 16 Msps. RX performance is in Fig. 4.

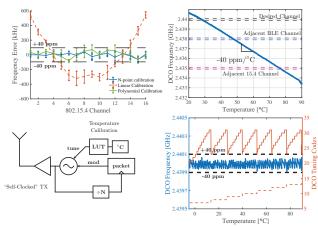

#### **Crystal-Free Operation**

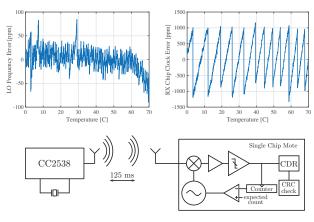

Single-temperature calibration is sufficient to find channels in the ISM band, as shown in Fig. 5. However, if temperature changes, the LO frequency will drift. Doing a one-time measurement of three frequency points at room temperature allows for a polynomial fit calibration accurate to within  $\pm 40$ ppm for all 802.15.4 channels (Fig. 5). Once an initial channel has been acquired, network based feedback can be used to maintain channel accuracy in the presence of temperature and supply variations. To demonstrate crystal-free operation across temperature, an off-the-shelf TI CC2538 was used to transmit 802.15.4 packets every 125 ms. The RX, which had already been calibrated to find the initial channel, locked onto this series of incoming packets and activated its radio in sync with the expected rate of incoming packets. For every packet received that had a valid CRC the receiver estimated the average IF and tuned the LO DAC to maintain a constant IF as in [3]. The RX chipping clock, which is derived from a free running RC oscillator, can be calibrated by making a comparison against the divided LO frequency. The resulting LO and RX chip clock accuracy is shown in Fig. 6.

#### Acknowledgements

The authors acknowledge the students, faculty, and sponsors of the Berkeley Wireless Research Center and the Berkeley Sensor and Actuator Center, silicon donation from TSMC, and Integrand and Lorenz tools. This work is funded in part by the Intel ULP Radios for IoT ISRA program.

#### References

[1] C.C. Li et al, ISSCC 2017. [2] S.Z. Lulec TCAS-II Jun. 2016. [3] B. Wheeler, RFIC 2017 [4] F.W. Kuo, et al, JSSC Apr. 2017. [5] Y.H. Liu et al, ISSCC 2015. [6] H. Liu et al, ISSCC 2018. [7] J. Prummel et al, ISSCC 2015

Fig. 1: Single Chip Mote architecture and block diagram. Supply conditioning circuits are not shown.

Fig. 2: Local Oscillator schematic and start-up transients, output spectra with MSK and GFSK modulation, and divider spurs

Fig. 3: Transmitter schematic with matching network and TX efficiencies Fig. 4: Receiver sensitivity across temperature (left) and blocker under various operating conditions. Power consumptions and efficiencies tolerance (right). For the blocker plot, the desired signal was at are calculated using regulated supply voltages.

-82 dBm input power on 802.15.4 channel 11. Modulated interferers are +5, +10, and +15 MHz away.

Fig. 5: Open-loop Local Oscillator calibration for channel selection at room temperature (top-left) and frequency change at single channel without compensation (top-right) and with temperature calibration (bottom-right)

Fig. 6: Network-based frequency compensation of LC oscillator using IF feedback (bottom), resulting LC frequency error (topleft) and derived IF chipping clock error (top-right).

|   | 1.5 mm LDO                               |  |  |  |  |

|---|------------------------------------------|--|--|--|--|

|   | Cortex M0                                |  |  |  |  |

|   | bits in/out                              |  |  |  |  |

|   | RX chips                                 |  |  |  |  |

| I | RX DBB                                   |  |  |  |  |

|   | TX chips LDO                             |  |  |  |  |

| 9 | $0  \mu \mathrm{m}$ 500 $\mu \mathrm{m}$ |  |  |  |  |

Fig. 7: Die Photo with annotated dimensions

|                         | This work      | [4] JSSC 2017 | [5] ISSCC 2015 | [6] ISSCC 2018 | [7] Dialog DA14580 |

|-------------------------|----------------|---------------|----------------|----------------|--------------------|

| Technology              | 65nm           | 28 nm         | 40 nm          | 65 nm          | 55 nm              |

| Comm. Type              | 802.15.4 TRX,  | BLE TRX       | 802.15.4 TRX,  | BLE TRX        | BLE TRX            |

|                         | BLE Adv. TX    |               | BLE TRX        |                |                    |

| Off-chip References     | none           | 1 - 40 MHz    | 32 MHz         | 26 MHz         | 16 MHz             |

| Integration Level       | RF + MCU + PMU | RF only       | RF + DBB +     | RF + DBB       | RF + DBB + MCU     |

|                         |                |               | MCU            |                | PMU                |

| Shared TX/RX Port       | yes            | yes           | no             | no             | yes                |

| TX Pout                 | -10 dBm        | 0 dBm         | -2 dBm         | -3 dBm         | 0 dBm              |

| TX Pdc                  | 847 μW *§+     | 3.7 mW        | 4.2 mW         | 3.1 mW         | 10.1 mW            |

| RX Pdc                  | 1.03 mW*       | 2.75 mW       | 3.3 mW         | 2.6 mW         | 11.2 mW            |

| Area [mm <sup>2</sup> ] | 3.06^          | 1.9           | 2.47°          | 1.64           | 5.9                |

- \* analog/RF power only

- + DC power calculated using regulated supply voltage § DC power at -10 dBm output, peak efficiency

- includes Cortex, TRX, baseband, and all LDOs; does not include sensor ADC or on-chip decoupling capacitance

o estimated from chip photo

Table 1: Comparison to previous literature