### **Aalborg Universitet**

#### A DC-Link Capacitor Voltage Ripple Reduction Method for a Modular Multilevel Cascade Converter With Single Delta Bridge Cells

Tanaka, Takaaki; Wang, Huai; Blaabjerg, Frede

Published in:

IEEE Transactions on Industry Applications

DOI (link to publication from Publisher): 10.1109/TIA.2019.2934024

Publication date: 2019

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Tanaka, T., Wang, H., & Blaabjerg, F. (2019). A DC-Link Capacitor Voltage Ripple Reduction Method for a Modular Multilevel Cascade Converter With Single Delta Bridge Cells. *IEEE Transactions on Industry* Applications, 55(6), 6115 - 6126. [8792104]. https://doi.org/10.1109/TIA.2019.2934024

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# A DC-link Capacitor Voltage Ripple Reduction Method for a Modular Multilevel Cascade Converter with Single Delta Bridge Cells (MMCC-SDBC)

Takaaki Tanaka<sup>1\*</sup>, Huai Wang <sup>2</sup>, and Frede Blaabjerg <sup>2</sup>

<sup>1</sup> R&D Headquarters, Fuji Electric Co., Ltd, Tokyo, Japan

<sup>2</sup> Department of Energy Technology, Aalborg University, Aalborg East, Denmark

\*E-mail: tanaka-takaaki@fujielectric.com

Abstract— This paper proposes a capacitor voltage ripple reduction method used for a Modular Multilevel Cascade Converter (MMCC) with Single Delta Bridge Cells (SDBC), by applying a third harmonic zero-sequence current. A practical case study on an 80 MVar/ 33 kV MMCC-SDBC based STATCOM is used to demonstrate the method. The impact of the third harmonic zero-sequence current level of the capacitor ripple reduction and the electro-thermal stresses on IGBT modules are analyzed. An optimal parameter of the current level is obtained by compromising the above performance factors. The obtained result shows that the required capacitance, as well as capacitor bank volume, are reduced by 20 % without increasing the total power semiconductor losses by using the proposed method.

Keywords— Modular Multilevel cascade Converter, STATCOM, Capacitor voltage ripple reduction, Zero-sequence current.

#### I. INTRODUCTION

The Modular Multilevel Cascade Converter (MMCC) family based on cascade connection of multiple single-phase converters has significant advantages for high power and high voltage applications compared with the conventional voltage source converters: such as easily scaling-up power and voltage ratings, lower harmonic distortion by multi-level voltage waveform and also modular/redundant operation. Therefore, the MMCC family has used for high voltage direct current (HVDC) transmission systems, High power Static Var Compensators (STATCOMs) and so on [1] [2].

A common disadvantage of the MMCC family is the low-frequency voltage ripple in each of the dc-link capacitors of the galvanic isolated single-phase converter. This increases size and cost and decreases the lifetime of the dc-link capacitors. In addition, the switching frequency of the single-phase converters of the MMCC family is set to be a very low value such as lower than several hundred Hz because of its multiple cascade connection structure. Although this can reduce the switching loss of each power module, this increases the capacitor voltage ripple. Therefore, the dc-link capacitor

design should take the impact of the Pulse Width Modulation (PWM) into account [3], [4].

Research works published so far have proposed the dclink capacitor voltage ripple reduction methods for one type of MMCC family with Double Star Chopper Cells (DSCC) based on cascade connection in a double star of multiple cascade chopper converters. The MMCC-DSCC solution is used in HVDC systems and Back-to-Back converter applications because of the function of converting AC/DC or DC/AC. The dc-link capacitor voltage ripple reduction methods can be classified into three principals. The first group is the second harmonic circulating current injection method [5-10]. The second group uses the circulating current with a combination of 2nd and 4th harmonic components. This enhances the reduction effect of the capacitor voltage ripple [11]. The third group uses both the circulating currents and the common-mode voltage of the DSCC, which enhances the reduction effect of the capacitor voltage ripple more [12],

However, no studies have proposed dc-link capacitor voltage ripple reduction methods for another type of the MMCC family with Single Delta Bridge Cells (SDBC), which is based on cascade connection of single delta of H-bridge single-phase converter. The MMCC-SDBC solution is typically used for STATCOM applications. Unfortunately, the above-mentioned dc-link capacitor voltage ripple reduction methods for the MMCC-DSCC cannot directly be applied to the MMCC-SDBC because of the different circuit architecture. The development of the capacitor voltage ripple reduction method for the MMCC-SDBC is useful to reduce the cost and size of the converter for the STATCOM [14].

This paper proposes a method for dc-link capacitor voltage ripple reduction used only for one type of MMCC family with Single Delta Bridge Cells (SDBC) under STATCOM operation, which way injects the third harmonic zero-sequence current. Firstly, a case study model of the STATCOM based on MMCC-SDBC having a rating of 80 MVar/ 33 kV is presented [15]. Secondly, the principle of the capacitor voltage ripple reduction by

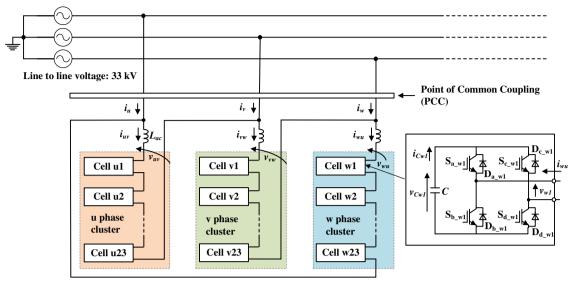

Fig. 1. The circuit configuration of the MMCC-SDBC.

using the proposed third harmonic zero-sequence current injection is presented. The mathematical formula of the dc-link capacitor voltage considering the Pulse Width Modulation (PWM) is also derived. Thirdly, the impact of the third harmonic zero-sequence current to the capacitor voltage ripple is analyzed based on the analytic model taking into account different reactive currents and grid voltages. Next, the electrical and thermal stress of each power module regarding the injected third harmonic zero-sequence current is analyzed based on the case study model. An optimum third-harmonic zero-sequence current to reduce the capacitor voltage ripple is also presented. Further, the capacitor bank of each case is designed considering the required capacitance and reliability. The capacitor bank volume reduction by applying the proposed method is finally discussed considering the obtained results.

### II. THE THEORETICAL BEHAVIOR OF THE DC-LINK CAPACITOR VOLTAGE

Fig. 1 shows the circuit configuration of the STATCOM based on an MMCC-SDBC having a rated 80 MVar power for the grid line of 33 kV, which is used as a case study model. Table I shows the detailed specifications of the MMCC-SDBC. Each phase-cluster of the MMCC-SDBC has an output maximum 59.8 kV (= 23 converter cells × 2600 Vdc) by using the series connection of galvanic isolated H-bridge converter cells using Insulated Gate Bipolar Transistor (IGBT) modules which have a 4500 V rated voltage. It is noted that the required isolation voltage to ground of each converter cell becomes more than 59.8 kV in this specification. The widely used Phase-Shift Pulse Width Modulation (PS-PWM) is selected due to the advantage that the voltage and current stress among the 69 single-phase converter cells are equally distributed. This makes the converter cell design simpler. Due to the large converter cell counts, the switching frequency of each power semiconductor device is reduced to a low value of 225 Hz in this specification. Although this suppresses the switching loss

TABLE I

THE DETAILED SPECIFICATION OF THE MMCC-SDBC

| THE DETAILED SPECIFICATION OF THE IMMCC-SDBC. |                         |  |  |

|-----------------------------------------------|-------------------------|--|--|

| Rated power $Q_r$                             | ±80 MVar                |  |  |

| Nominal grid voltage $V_S$                    | 33 kVrms ( $\pm 20\%$ ) |  |  |

| Nominal cell DC-side voltage $V_{Cref}$       | 2600 Vdc                |  |  |

| Nominal cell AC-side voltage $v_x$            | 1450 Vrms               |  |  |

| Equivalent switching frequency $f_{eq\_sw}$   | 10.35 kHz               |  |  |

| Rated line current $I_r$                      | 1400 Arms               |  |  |

| Carrier frequency $f_c$                       | 225 Hz                  |  |  |

| Grid frequency $f_g$                          | 50 Hz                   |  |  |

| Interconnection inductor $L_{ac}$             | 7.8 mH (% <i>L</i> =6%) |  |  |

| Dc-link capacitance each cell $C_x$           | 7.0 mF                  |  |  |

| Total cell counts $N_{cell}$                  | 23×3                    |  |  |

| IGBT module                                   | MBN900D45A<br>(HITACHI) |  |  |

of each power module, the impact of the PWM operation appears significantly on the dc-link capacitor voltage. The following section derives the formula of the dc-link capacitor voltage of each converter-cell in the MMCC-SDBC considering the PS-PWM operation. The dc-link capacitor voltage with both the original operation and the proposed operation using the voltage ripple reduction method are compared.

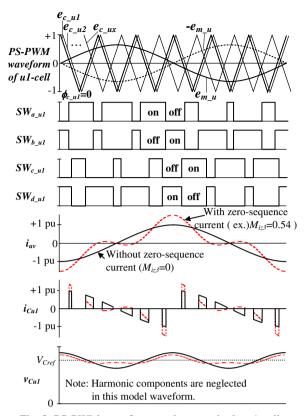

#### A. The original capacitor voltage

Fig. 2 shows with a solid line the conventional operation waveforms of the u1-cell converter (see Fig. 1) as an example. When the MMCC-SDBC is in steady state and each dc-link capacitor voltage is balanced, the output voltage reference of each cell in the u-phase cluster  $e_{m\_u}$  is given by

$$e_{m_u} = M_a \sin \omega_m t + e_{m_z} \tag{1}$$

$$M_a \equiv \frac{\sqrt{2}(v_S \pm \omega_m L_{ac} I/\sqrt{3})}{(N_{cell}/3) V_{Cref}}$$

(2)

with the modulation factor:  $M_a$ , the grid frequency:  $\omega_m$ , each cell output voltage of the zero-sequence component:  $e_{m_z}$ , the nominal grid voltage:  $V_s$ , the inductance of each

Fig. 2. PS-PWM waveforms and current in the u1-cell.

phase-cluster AC inductor:  $L_{ac}$ , the phase current at the PCC: I, the total cell number:  $N_{cell}$ , the dc-link voltage reference of each cell converter:  $V_{Cref}$ . The  $e_{m_{-}z}$  has zero value in this condition. It is noted that the polarity of the voltage drop of the AC inductor depends on a leading/lagging of the STATCOM output current.

The  $e_{c\ ul}$  is the carrier signal of the u1-cell converter. The phase delay of the  $e_{c ul}$  from the  $e_{m u}$ , which has a zero value in Fig. 2. Because of the PS-PWM, the phase delay  $\phi_{c ux}$  of the other cell converters in the u-phase cluster is given by

$$\phi_{c\_ux}|_{x=2,...,N_{cell}/3} = \phi_{c\_u1} + \frac{x-1}{N_{cell}/3} \frac{1}{\omega_c}$$

(3)

with the number of the optional cell in the u-phase cluster: x, the carrier frequency  $\omega_c$  [rad/s] of the PS-

The switching functions  $SW_{a_{-}ux}$ ,  $SW_{b_{-}ux}$ ,  $SW_{c_{-}ux}$ , and  $SW_{d \ ux}$  show the on/off states of the power semiconductor switches  $S_{a\_ux},\; S_{b\_ux},\; S_{c\_ux,}$  and  $S_{d\_ux},$  respectively, which is determined by the PS-PWM of the  $e_{m_u}$  and the  $e_{c_ux}$  by neglecting the dead time duration.  $SW_{a\_ux}$ ,  $SW_{b\_ux}$ ,  $SW_{c\_ux}$ , and  $SW_{d ux}$  are expressed as a Fourier series expansion in the following:

$$SW_{a_{.}ux} = \frac{1}{2}(1 + e_{m_{.}u}) + \sum_{n=1}^{m} \left[\frac{2}{n\pi}\sin\left\{\frac{n\pi}{2}(e_{m_{.}u} - 1)\right\}\cos(n\omega_{c}t - n\phi_{c_{.}ux})\right]$$

(4)

$$SW_{b_{.}ux} = 1 - SW_{b_{.}ux}$$

(5)

$$SW_{c_{.}ux} = \frac{1}{2}(1 - e_{m_{.}u}) + \sum_{n=1}^{m} \left[\frac{2}{n\pi}\sin\left\{\frac{n\pi}{2}(-e_{m_{.}u} - 1)\right\}\cos(n\omega_{c}t - n\phi_{c_{.}ux})\right]$$

(6)

$$SW_{d_{.}ux} = 1 - SW_{c_{.}ux}$$

(7)

The u1-cell output current, as well as the u-phase

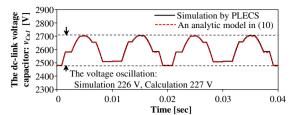

Note:  $M_a = 0.827$  p.u.,  $M_{a3} = 0$  p.u.  $\phi_{C_ul} = -3.11$  rad,  $V_{c_ini} = 2480$  V (a) Conventional operation as the  $M_{iz3} = 0$  p.u.

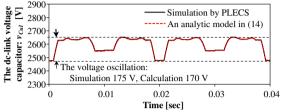

Note:  $M_a = 0.827$ ,  $M_{a3} = 0.0702$  p.u.  $\phi_{C_ul} = -3.11$  rad,  $V_{c_ini} = 2477$  V (b) Proposed operation with  $M_{iz3} = 0.5$  p.u and  $\phi_{iz3} = \phi_{pf}$ Fig. 3. The u1-cell capacitor voltage waveforms.

cluster current  $i_{uv}$ , is defined as

$$i_{uv} = \sqrt{\frac{2}{3}} I \sin(\omega_m t + \phi_{pf}) + i_{zero}$$

(8)

where  $\phi_{nf}$  is the power factor of the MMCC-SDBC,  $i_{zero}$  is the zero-sequence current. It is noted that the zerosequence current  $i_{zero}$  is controlled to zero value where all capacitor voltages are balanced.

The dc-link capacitor current  $i_{Cux}$  of each u-phase converter cell is given by using the switching functions as follows:

$$i_{Cux} = -i_{uv} \left( SW_{a\_ux} - SW_{c\_ux} \right) \tag{9}$$

By integrating (9), the dc-link capacitor voltage  $v_{cut}$ of each u-phase converter cell is expressed by (10) with the initial value of  $v_{cul}$ :  $V_{Cul\ ini}$ .

$$v_{Cux} = -\frac{1}{c} \int i_{Cux} dt + V_{Cux\_ini}$$

(10)

Fig. 3(a) plots the dc-link capacitor voltage  $v_{Cu1}$  of the u1 cell converter based on the analytic model in (10) and the simulation under the rated operation given in Table I. The simulation waveform is obtained by using the PLECS software on the practical scale model based on the specification of Table I. The  $\phi_{C\_uI}$  and  $V_{CuI\_ini}$  in the analytic model is set at - 3.11 rad and 2480 V, respectively, which values are adjusted to the simulation values. The analytic model corresponds reasonably well with the simulation result.

#### B. The proposed capacitor voltage ripple reduction method

Fig. 2 shows with a dotted line the proposed operation waveforms of the u1-cell converter. The  $i_{zero}$  is normally controlled at zero value where all capacitor voltages are balanced. However, it is possible to output an optional value. A third harmonic zero-sequence current, which has the same angle and amplitude among the three-phase clusters is to reduce the dc-link capacitor voltage ripple and it is considered in the next part.

The  $i_{zero}$  is defined as

Fig. 4. The numerical calculation flow for the dc-link capacitor voltage ripple stage.

$$i_{zero} = \sqrt{\frac{2}{3}} M_{iz3} I \sin(3\omega_m t + \phi_{iz3})$$

(11)

where  $M_{iz3}$  is the amplitude ratio of  $i_{zero}$  at the I,  $\phi_{iz3}$  is the phase difference from  $e_{m_u}$ .

In order to inject  $i_{zero}$ , each cell converter requires an additional output voltage. The additional output-voltage reference  $e_{m,z}$  is given by

$$e_{m_z} = M_{a3} \sin\left(3\omega_m t + \frac{\pi}{2} + \phi_{iz3}\right)$$

(12)

$$M_{a3} = \frac{\sqrt{6\omega_m L_{ac} IM_{iz3}}}{(N_{cell}/3)V_{Cref}}$$

(13)

$M_{a3} = \frac{\sqrt{6}\omega_m L_{ac} IM_{iz3}}{(N_{cell}/3)V_{Cref}} \tag{13}$  The switching functions  $SW_{a\_ux}$ ,  $SW_{b\_ux}$ ,  $SW_{c\_ux}$  and  $SW_{c ux}$  under the proposed dc-link capacitor voltage ripple reduction operation can be obtained by substituting (1), (2), (12) and (13) for (4), (5), (6) and (7).

The dc-link capacitor current  $i_{Cux}$  of each u-phase converter cell under the proposed dc-link capacitor voltage ripple reduction operation can be obtained by substituting the above-mentioned switching functions, (8) and (11) for (9).

The dc-link capacitor voltage  $v_{Cux}$  of each u-phase converter cell under the proposed dc-link capacitor voltage ripple reduction operation can be expressed by (14), by substituting the above-mentioned dc-link

capacitor current  $i_{Cux}$  for (10).

Fig. 3(b) shows the dc-link capacitor voltage  $v_{Cul}$  of the u1 converter cell based on the analytic model (14) and the simulations. In these results, 50% of the third harmonic zero-sequence current is injected with  $M_{iz3}$  = 0.5,  $\phi_{iz3} = \phi_{pf}$ ,  $\phi_{C\_uI} = -3.11$  rad,  $V_{CuI\_ini} = 2477$  V as an example. The simulation waveform is also obtained using PLECS software on the practical scale model based on the specifications in Table I. The analytic waveform corresponds well with the simulation waveforms. The proposed method reduces the capacitor voltage ripple by 23% compared with the original voltage ripple.

#### C. The optimum phase angle $\phi_{iz3}$ of the third harmonic zero sequence current

Equation (14) reveals that the dc-link capacitor voltage ripple consists of the following three components.

- The first component is some terms in (14), which are pulled out by the modulation factor  $M_a$  of the grid frequency. This becomes the main component of the dc-link capacitor voltage.

- The second component comes from some terms in (14), which are due to the modulation factor  $M_{a3}$  of the third harmonic voltage in order to inject the third harmonic zero-sequence current.

$$v_{Cux} = -\sqrt{\frac{2}{3}} \frac{M_a}{4\omega_m C} \left\{ I \sin(2\omega_m t + \phi_{pf}) - M_{iz3} I \sin(2\omega_m t + \phi_{iz3}) + \frac{M_{iz3} I}{2} \sin(4\omega_m t + \phi_{iz3}) \right\}$$

$$+ \sqrt{\frac{2}{3}} \frac{M_{a3}}{4\omega_m C} \left\{ I \sin(2\omega_m t - \phi_{iz3} + \frac{\pi}{2} - \phi_{pf}) - \frac{I}{2} \sin(4\omega_m t - \phi_{iz3} + \frac{\pi}{2} + \phi_{pf}) - \frac{M_{iz3} I}{3} \cos(6\omega_m t + \frac{\pi}{2}) \right\}$$

$$+ \sqrt{\frac{2}{3}} \frac{I}{C} \int \left\{ \sin(\omega_m t + \phi_{pf}) + M_{iz3} \sin(3\omega_m t + \phi_{iz3}) \right\} \sum_{n=1}^{\infty} \frac{4}{n\pi} \cos\left(\frac{n\pi}{2}\right) \sin\left[\frac{n\pi}{2} \left\{ M_a \sin\omega_m t + M_{a3} \sin\left(3\omega_m t - \phi_{iz3} + \frac{\pi}{2}\right) \right\} \right]$$

$$\cos(n\omega_C t - n\phi_{C} u_X) dt + V_{Cux} ini$$

(14)

The third component is the remaining terms in (14). Those terms are due to the PS-PWM.

The first component dominates the dc-link capacitor voltage ripple. For the sake of simplicity, the first component is in focus. When the amplitude  $M_{iz3}$  of the third harmonic zero-sequence current is zero, only the double frequency voltage ripple is remaining, which is the original capacitor voltage ripple component. When the  $M_{iz3}$  and the phase angle  $\phi_{iz3}$  of the third harmonic zero-sequence current are set to 1 p.u. and  $\phi_{pf}$ , the original capacitor voltage ripple component can be eliminated perfectly. This is the effect of the proposed capacitor voltage ripple reduction method. It is obvious, due to the optimum  $\phi_{iz3}$  to obtain the maximum voltage ripple reduction effect, the capacitor voltage ripple should be set to be the same as the power factor angle  $\phi_{pf}$ .

#### III. THE NUMERICAL ANALYSIS OF THE DC-LINK CAPACITOR VOLTAGE RIPPLE

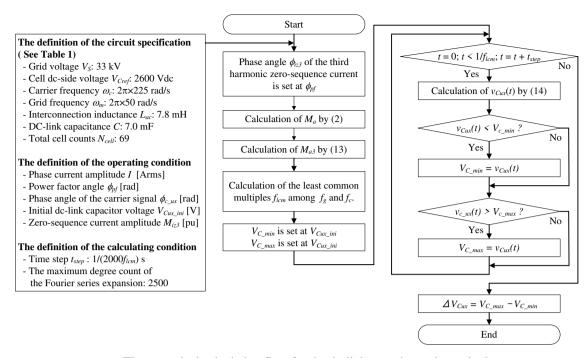

Fig. 4 shows the numeric calculation flow of the dclink capacitor voltage ripple  $\Delta V_{Cux}$  of each u-phase converter cell based on (14). The first process of this numeric calculation is the definition of the circuit specifications, the operating conditions, and the numeric calculation parameters. Next step is the definition of the phase angle  $\phi_{iz3}$  of the third harmonic zero-sequence current, which is set at  $\phi_{pu}$ , and is the optimum value to minimize the capacitor voltage ripple as described in Section II-C. Then, the numeric calculation period of  $v_{Cux}(t)$  is calculated, which becomes the least common multiples  $f_{lcm}$  among  $f_g$  and  $f_c$  because the  $v_{Cux}$  is the periodic function repeated over intervals of  $1/f_{lcm}$ . Finally, the capacitor voltage ripple  $\Delta V_{Cux}$  during the period  $1/f_{lcm}$ is calculated, which becomes the differential value between the maximum value  $V_{C\_max}$  and the minimum value  $V_{C_{min}}$  of  $v_{Cul}(t)$  for the period  $1/f_{lcm}$ . The following section analyzes the capacitor voltage ripple with respect to the PS-PWM condition, reactive current and grid voltage by using the numeric calculation method shown in Fig. 4.

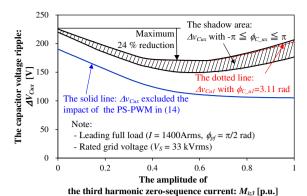

## A. The impact of the PS-PWM to the capacitor voltage ripple $\Delta V_{Cux}$ of a u-phase cluster cell converter

Fig. 5 shows the dc-link capacitor voltage ripple  $\Delta V_{Cux}$  of the u-phase converter cells regarding the amplitude  $M_{iz3}$  of the third harmonic zero-sequence current. The STATCOM operating condition is set to be leading with full load output (I=1400 Arms,  $\phi_{pf}=\pi/2$  rad) and the rated grid voltage ( $V_S=33$  kVrms). The following describes each of the plots.

- The dotted line plots show of the capacitor voltage ripple  $\Delta V_{Cul}$  of u1-cell converter. The phase angle  $\phi_{c\_ul}$  of the carrier signal is set to be -3.11 rad as an example, which value is the same as the analytic condition of Fig. 3 (b).

- The shadow area shows a range of values on the capacitor voltage ripple  $\Delta V_{Cux}$  of each of the u-phase converter cell can take in respect to the  $\phi_{c\_ux}$ . The  $\phi_{c\_ux}$  has the values in the range  $[-\pi, \pi]$  depending on

Fig. 5. The dc-link capacitor voltage ripple solved by the numeric calculation in Fig. 4.

Fig. 6 The capacitor voltage ripple in respect to the amplitude ratio  $M_{ir3}$ , with different value of the reactive current.

Fig. 7. The capacitor voltage ripple in respect to the amplitude ratio  $M_{iz3}$ , with different value of grid voltage.

the converter cell. It is obvious that the  $\Delta V_{Cux}$  has a significantly different value with respect to the  $\phi_{c_-ux}$ , which should be taken account when doing the capacitor design.

The lowest solid line plots show the capacitor voltage ripple, but this calculation is excluding the term related to the PS-PWM in the analytic model (14). Obviously, if the impact of the PS-PWM is excluded from the calculation, the capacitor voltage has a large difference. So, the impact of the harmonics coming from the PS-PWM should be considered, when the capacitor is designed.

In the following, the capacitor voltage ripple is defined as the maximum value  $\Delta V_C$  with respect to the phase angle  $\phi_{c\_ux}$  of the carrier signal and modulation waveform

between  $-\pi$  to  $+\pi$ .

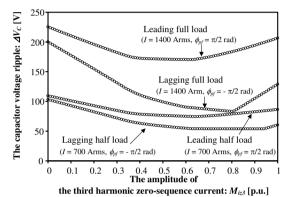

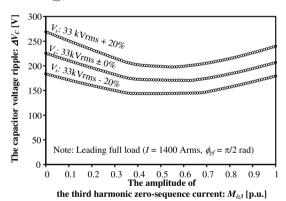

## B. The capacitor voltage ripple $\Delta V_C$ with respect to the reactive current output

Fig. 6 shows the plot of the capacitor voltage ripple  $\Delta V_C$  regarding the  $M_{iz3}$  [pu], with different values of the reactive output current. It is obvious that the capacitor voltage ripple has a maximum at the leading full load point. The effective parameters of  $M_{iz3}$  to reduce the capacitor voltage ripple stay constant at around 0.5 regarding the different values of the reactive output current. When the  $M_{iz3}$  is larger than 0.5, the capacitor voltage ripple increases depending on the reactive current condition.

### C. The capacitor voltage ripple $\Delta V_C$ with respect to the grid voltage

Fig.7 shows the plot of the capacitor voltage ripple in respect to the  $M_{iz3}$  [pu] with different amplitudes of the grid voltage  $V_S$  [pu] within the specification as shown in Table I, under leading full load condition. It is noted that the capacitor voltage ripple decreases relative to  $V_S$ . It is obvious that the effective parameters of  $M_{iz3}$  to reduce the voltage ripple stays constant at around 0.5 independent of the  $V_S$ .

### IV. ELECTRICAL AND THERMAL STRESS OF THE POWER MODULES

The proposed method can reduce the dc-link capacitor voltage ripple of the MMCC-SDBC by the injection of third harmonic zero-sequence current. However, it may increase the power semiconductor losses, peak junction temperature and peak current by using the third harmonic current. This paragraph analyzes the electrical and thermal stress of the power modules used in the practical 80 MVar / 33 kV scaled STATCOM based on the MMCC-SDBC using the proposed method.

#### A. Electrical and thermal simulation model

The electrical and thermal stress of the power modules in the MMCC-SDBC in respect to the  $M_{iz3}$  are simulated by using the simulation software PLECS. The specifications of the MMCC - SDBC are shown in Fig. 1 and Table I. The reactive current reference is set to be rated 1 p.u. The grid voltage is also set to be the rated 33 kV

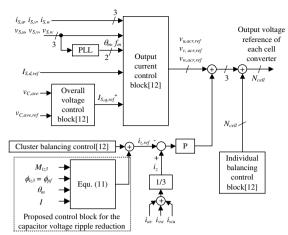

Fig. 8 depicts the overall control block diagram of the MMCC-SDBC with the proposed capacitor voltage ripple reduction method by using third harmonic zero-sequence current. The output current and the capacitor voltage control method are applied [16]. The third harmonic zero-sequence current given in (11) is added to the reference value of the zero-sequence current. The phase angle  $\phi_{iz3}$  of the third harmonic zero-sequence current is set to be  $\phi_{pf}$ . The amplitude  $M_{iz3}$  of the third harmonic zero-sequence current is normalized by the output current I and is set to have a value in the range between 0 and 1.

The power loss of each power module is simulated by the active component block function in the PLECS

Fig. 8. The overall control block diagram for the MMCC-SDBC with the proposed capacitor voltage ripple reduction method.

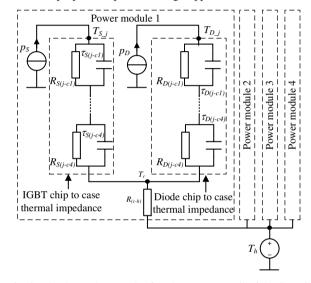

Fig. 9. The thermal network of each converter cell of the SDBC.

software. The on-state voltage  $V_{ce}(I_c, T_{S\_j})$  of the IGBT side is set to be a line (15) in respect to the junction temperature  $T_{S\_j}$  of the IGBT and the collector current  $I_C$ .

$$V_{ce}(I_c, T_{S_j}) = V_{ce,25C^{\circ}}(I_c) + \frac{T_{S_j-25}}{100} \{V_{ce,125C^{\circ}}(I_c) - V_{ce,25C^{\circ}}(I_c)\}$$

(15)

Here,  $V_{ce,25^{\circ}C}(I_c)$  and  $V_{ce,125^{\circ}C}(I_c)$  are the on state voltage at the junction temperature  $T_{S\_j} = 25^{\circ}\text{C}$ ,  $125^{\circ}\text{C}$ , respectively, in response to the collector current  $I_c$ . This information is obtained from the datasheets of the manufacturers [17]. The on-state voltage  $V_f(I_{\beta} \ T_{D\_j})$  of the Free Wheeling Diode (FWD) side is set to be (16) in respect to the junction temperature  $T_{D\_j}$  of the FWD and the forward current  $I_C$  of the FWD.

$$V_{f}(I_{f}, T_{D_{-}j}) = V_{f,25C^{\circ}}(I_{f}) + \frac{T_{D_{-}j-25}}{100} \{V_{f,125C^{\circ}}(I_{f}) - V_{f,25C^{\circ}}(I_{f})\}$$

(16)

Here,  $V_{f,25^{\circ}C}(I_f)$  and  $V_{f,125^{\circ}C}(I_f)$  are the on state voltage at the junction temperature  $T_{D_-j} = 25^{\circ}\text{C}$ ,  $125^{\circ}\text{C}$ , respectively, as a function of the  $I_c$ , which information is obtained from the datasheets of the manufacture [17]. The turn on energy loss  $E_{on}(I_C, v_c)$ , turn off loss  $E_{off}(I_C, v_c)$  and reverse recovery loss  $E_{rr}(I_{\beta}v_c)$  of the power module at every

Fig. 10. Key simulation waveforms of the MMCC-SDBC including thermal loading.

switching behavior are set to be calculated line in (17), (18) and (19), respectively, which are dependent on the current flow and the applied voltage  $v_c$  at the switching operation.

$$E_{on}(I_c, v_c) = \frac{v_c}{2600} E_{on, 2600V}(I_c)$$

(17)

$$E_{off}(I_c, v_c) = \frac{v_c}{2600} E_{off, 2600V}(I_c)$$

(18)

$$E_{on}(I_c, v_c) = \frac{v_c}{2600} E_{on,2600V}(I_c)$$

$$E_{off}(I_c, v_c) = \frac{v_c}{2600} E_{off,2600V}(I_c)$$

$$E_{rr}(I_f, v_c) = \frac{v_c}{2600} E_{rr,2600V}(I_f)$$

(18)

$$E_{rr}(I_f, v_c) = \frac{v_c}{2600} E_{rr,2600V}(I_f)$$

(19)

Here,  $E_{on,2600V}(I_c, v_c)$ ,  $E_{off,2600V}(I_c, v_c)$  and  $E_{rr,2600V}(I_f, v_c)$  are the turn-on energy loss, turn off energy loss and reverse recovery energy loss at  $v_c = 2600$ V at every switching operation in response to the current flow, which information is obtained by the datasheet from the manufacturers [17].

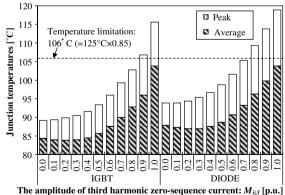

The junction temperature of each power module is simulated by the thermal simulation function in the PLECS software. The thermal impedance between junction and heatsink is based on the Foster RC network which is shown in Fig. 9, and they are selected from the datasheets for the power modules [17]. Here,  $p_S$  is the power loss of the IGBT;  $p_D$  is the power loss of the FWD;  $T_{S,i}$  is the junction temperature of the IGBT;  $T_{D,i}$  is the junction temperature of the FWD;  $T_c$  is the case temperature in the power module;  $T_h$  is the heat sink temperature;  $R_S(j-cn)$ ,  $\tau_S(j-cn)$ ,  $R_D(j-cn)$  and  $\tau_D(j-cn)$  are thermal parameters for the Foster RC network of the power module (n:1-4). The limitation temperature is set to be 106°C determined by the absolute maximum value of 125°C provided by the manufacturer. A design margin of 0.85 is considered in this paper. As the temperature of the heatsink is normally much lower and more stable compared with the junction temperature in a properly designed converter system, the heat sink temperature is considered as a constant value of 60°C in this paper.

#### B. Electrical and thermal waveforms

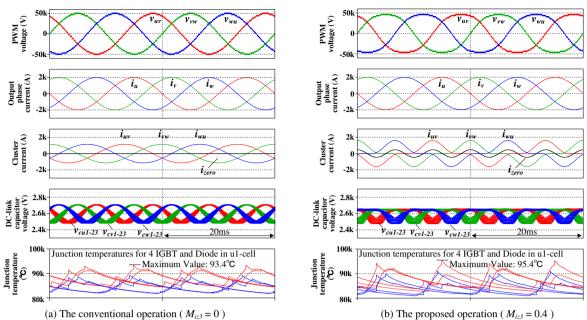

Fig. 10 shows the electrical and thermal simulation

Fig. 11. The total semiconductor loss of the MMCC-SDBC.

Fig. 12. The junction temperature of an IGBT and Diode switch selected as the maximum of switches of the MMCC-SDBC.

waveforms with  $M_{iz3} = 0$  (the conventional operation) and  $M_{iz3} = 0.4$  as an example (the proposed operation). These waveforms show no evidence of abnormalities. The total harmonic distortion of the output phase current with  $M_{iz3}$ = 0 and  $M_{iz3}$  = 0.4 operations are almost the same, which are 0.35% and 0.4%, respectively. The peak modulation factors of each converter cell with  $M_{iz3} = 0$  and 0.4 are 0.80 pu and 0.76 pu, respectively. The peak phase-cluster current for the proposed case increases by 40 % (1600 A) by the injection of the third harmonic zero-sequence current. This value is still lower than the allowable peak current value of 1800 A of the used power modules as mentioned in Table I. The peak junction temperature of the power module increases 2 Kelvin, which values are below the upper limit temperature of 106°C. The capacitor voltage ripple for the proposed case will decrease by 20 % in this operating condition.

### C. Power semiconductor losses and junction temperatures

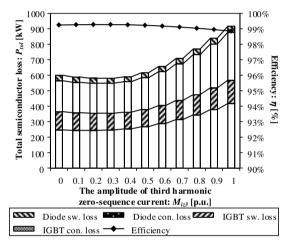

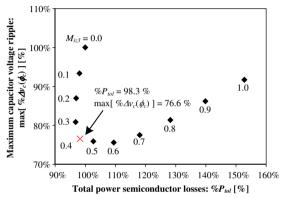

Fig. 11 shows the total semiconductor losses and electrical efficiency of the MMCC-SDBC with respect to the  $M_{iz3}$ . It is noted that the total semiconductor losses increase when  $M_{iz3}$  is above 0.3 p.u. because the r.m.s. value of each cluster current increases. However, the total semiconductor losses are slightly reduced when  $M_{iz3}$  is below 0.3 because of the  $V_{ce}$  -  $I_c$  characteristics of the used bipolar devices.

Fig. 12 shows the instant peak and average junction temperature of the IGBT and FWD having maximum thermal stress among the 276 modules with respect to  $M_{iz3}$ . It is noted that the average junction temperature exhibits similar trends as the total losses. On the other hand, the peak junction temperature increases as a function of the  $M_{iz3}$  because the peak value of the phase-cluster current increases due to the  $M_{iz3}$ . It is noted that the third harmonic zero-sequence current has not exceeded above 0.7 of  $M_{iz3}$ , because of the limitation of the peak junction temperature in this case.

#### D. Peak current stress of the power modules

Fig. 13 shows with solid line the peak phase-cluster current  $i_{peak}$  as a function of  $M_{iz3}$  under full load condition, which can be calculated by

$$i_{peak} = \sqrt{\frac{2}{3}} I_r (1 + M_{iz3})$$

(20)

where  $I_r$  is the rated phase current as mentioned in Table I. It should be noted that the amplitude  $M_{iz3}$  of the injection of the third harmonic zero-sequence current should not exceed above 0.55 p.u. due to the peak current limitation of the used power module.

#### E. The optimum amplitude of the third harmonic zerosequence current M<sub>1:3</sub>

Fig. 14 shows the total semiconductor losses and the capacitor voltage ripple regarding the  $M_{iz3}$ . The total semiconductor losses and the capacitor voltage ripple are normalized by each value at  $M_{iz3} = 0$ . The optimum value of  $M_{iz3}$  is selected to be 0.4 p.u. where the capacitor voltage ripple could be reduced to a minimum without any total power semiconductor loss increase compared with the conventional method ( $M_{iz3} = 0$ ).

Fig. 13. The peak phase-cluster current as a function of  $M_{iz3}$ .

Fig. 14. The total semiconductor loss and the capacitor voltage ripple as a function of  $M_{iz3}$ .

#### V. CAPACITOR BANK DESIGN

The final purpose of the proposed capacitor voltage ripple reduction method is to reduce the entire capacitor bank size. Surely, the required capacitance is reduced by applying the proposed method, but the equivalent series resistance of the capacitor bank will be increased. Therefore, the core temperature of capacitor bank as well as the expected lifetime of the capacitor bank may get worse, which may influence the reduction of the capacitor bank volume [18], [19]. In order to clarify the capacitor bank size reduction effect of the proposed method, the capacitor bank is designed in this section.

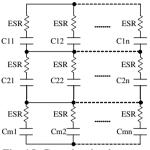

#### A. Capacitor bank structure

Table II shows the target specification of the capacitor bank for the MMCC-SDBC having the specification given in Table I. The type of the dc-link capacitor is selected to be metalized polypropylene film capacitor (MPPF-Cap), which is commonly chosen for the medium and high voltage class MMCC solutions because of a high reliability [20], [21]. The capacitance of the dc-link capacitor bank with the conventional operation and the proposed method are set to be 7 mF and 5.4 mF, respectively, where the capacitor voltage ripples are suppressed to be less than 10%.

Fig. 15 shows the dc-link capacitor bank structure. In the actual STATCOM product case, the dc-link capacitor bank typically becomes one capacitor, which is custom made product provided by a capacitor manufacturer. In

### TABLE II THE TARGET SPECIFICATION OF THE CAPACITOR BANK

| THE TAKGET SI ECH ICATION OF THE CALACITOR BANK. |                          |                 |  |  |

|--------------------------------------------------|--------------------------|-----------------|--|--|

|                                                  | Conventional method      | Proposed method |  |  |

| Compositor trans                                 | Metallized polypropylene |                 |  |  |

| Capacitor type                                   | film capacitor           |                 |  |  |

| Rated dc voltage                                 | 2600 Vdc                 |                 |  |  |

| Capacitance                                      | 7 mF or more             | 5.4 mF or more  |  |  |

| Expected life time                               | 20 years or more         |                 |  |  |

| Ambient temperature                              | 60 °C                    |                 |  |  |

Fig. 15. Capacitor bank structure.

TABLE III

CAPACITOR BANK SPECIFICATION

| CAI ACTION BAINS SI ECII ICATION. |                                       |               |  |  |

|-----------------------------------|---------------------------------------|---------------|--|--|

|                                   | Conventional case                     | Proposed case |  |  |

|                                   | 560 μF, 1300 Vdc, 85 °C, Type 947C    |               |  |  |

| Used capacitor                    | Polypropylene Film DC-Link Capacitors |               |  |  |

|                                   | from Cornell Dubilier                 |               |  |  |

| Series connection                 | 2                                     | 2.            |  |  |

| count: m                          | <i>2</i>                              | 2             |  |  |

| Parallel connection               | 25                                    | 20            |  |  |

| counts: n                         | 23                                    |               |  |  |

| Total count: $m \times n$         | 50                                    | 40            |  |  |

| Total capacitance                 | 7.00 mF                               | 5.60 mF       |  |  |

| Rated voltage                     | 2600 Vdc                              |               |  |  |

| Total capacitor volume            | 87.2 L                                | 69.8 L        |  |  |

this paper, the capacitor bank is constructed by series and parallel connection of small capacitor elements. It should be noted that the total volume of the dc-link capacitor bank constructed by smaller capacitor elements becomes similar to the custom made product because of the same total energy stored in the capacitor. Table III shows the capacitor bank specification for both the conventional and the proposed case. The capacitor bank is selected to use 560  $\mu F$ , 1300 Vdc, Type 947C MPPF-Cap. from Cornell Dubilier [22]. In order to overcome the applied dc voltage to the capacitor bank, the series connection number is designed to be 2 for both cases. In order to provide the capacitor bank with the required capacitance, the parallel counts of the conventional and the proposed case are designed to be 25 and 20, respectively. The total volumes of each dc-link capacitor bank for the conventional and proposed case are 87.2 L and 69.8 L, respectively. The capacitor bank volume is reduced by 20% by applying the proposed method.

#### B. The thermal stress of each MPPF-Cap

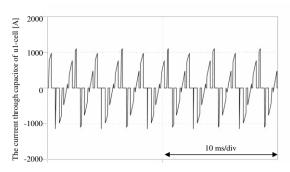

The hot spot temperatures of the dc-link capacitors under the conventional and proposed condition are calculated, which have to be kept below the rated temperature determined by the manufacturer. Fig. 16 and

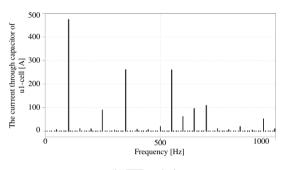

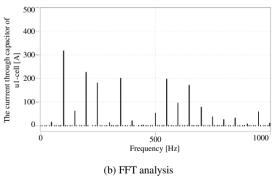

(a) Current waveform through the capacitor bank (473 Arms)

(b) FFT analysis

Fig. 16. The current through the capacitor bank under conventional condition.

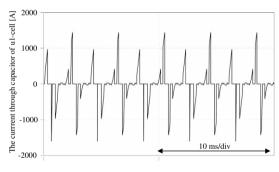

(a) Current waveform through the capacitor bank (426 Arms)

(6) 11 1 unui jois

Fig. 17.The current through the capacitor bank using the proposed method.

Fig. 17 show the current waveforms through the dc-link capacitor bank of the u-1 cell and an FFT analysis with or without the proposed method. The simulation conditions are the same as shown in Fig. 10. By applying the proposed method, the main current ripple component as

the double fundamental frequency is reduced by 33% and distributed to higher frequency components. The r.m.s. values of the current through the capacitor bank in the conventional and proposed case are 473 Arms and 426 Arms, respectively.

In order to simplify the calculations, it is assumed that the current through each individual capacitor in the capacitor bank is balanced. The power loss of each capacitor is given by

$$P_{loss} = \sum_{f} ESR(f) \cdot I_{C}^{2}(f) \tag{21}$$

$P_{loss} = \sum_{f} ESR(f) \cdot I_{C}^{2}(f)$  where ESR(f) is the Equivalent Series Resistance of the capacitor according to the frequency f,  $I_C$  is the r.m.s. current through each capacitor in respect to f. The core temperature of the capacitor is given by

$$T_C = T_a + P_{Loss} \cdot R_{th} \tag{22}$$

where  $T_a$  is the ambient temperature around the capacitor, and  $R_{th}$  is the thermal resistance of the capacitor.

Table IV shows the  $P_{loss}$  and  $T_c$  of the individual capacitors for the conventional and proposed case. The power loss and hot spot temperature of the proposed capacitor case become slightly higher than in the conventional case in order to reduce a parallel number of capacitors. However, because the ESR of the film capacitors has enough small value, the core temperatures of the used capacitor for both cases become lower than its absolute temperature of 85 °C.

#### C. The expected lifetime of the capacitor bank

Generally, MPPF-Caps have very long lifetime under adequate operating conditions including the applied dcvoltage, the core temperature of the capacitor and the humidity when comparing with Aluminum Electrolytic Capacitors, which have wear out failure modes. For such kind of components, it is important to estimate the reliability by using its lifetime model. In this paper, the lifetime of the capacitor bank under the conventional and the proposed case is estimated by using the provided information from the capacitor manufacturer.

A widely used capacitor lifetime model applicable for film capacitor is as follows [23]:

$$L = L_0 \times \left(\frac{V}{V_0}\right)^{-n} \times 2^{\frac{T_0 - T}{k}}$$

(23)

where L is the lifetime under the thermal and electrical stress T and V,  $L_o$  is the lifetime under the reference temperature  $T_0$  and the nominal voltage  $V_0$ . The coefficients k and n are a temperature dependent constant and voltage stress constant. The parameters  $L_0$ ,  $T_0$ , n, and k for the used capacitor are obtained from a provided lifetime curve which are fitted to be 200000, 66 °C, 19.4, and 3.9, respectively.

Actually, there is a probability on a lifetime of individual capacitors, which also is considered [24]. It is assumed that a variation of the lifetime obeys the normal distribution. The cumulative distribution function (CDF) for the normal distribution can be calculated by

$$F(t) = \frac{1}{2} \left\{ 1 + \operatorname{erf}\left(\frac{t - \mu}{\sigma\sqrt{2}}\right) \right\}$$

(24)

where  $\mu$  is the mean of the distribution,  $\sigma$  is the standard

TABLE IV POWER LOSS AND HOT SPOT TEMPERATURE OF EACH CAPACITOR.

|                      | Conventional case | Proposed case |

|----------------------|-------------------|---------------|

| Power loss           | 1.11 W            | 1.36 W        |

| Hot spot temperature | 63.3 °C           | 64.1 °C       |

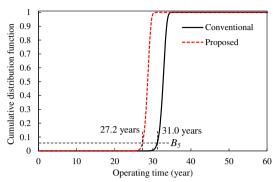

Fig. 18. Probability curves of wear-out failure for the capacitor banks.

deviation, erf is the error function. The  $\mu$  is determined by the expected lifetime calculated by (12). The  $\sigma$  is determined by considering±10% variation with a 95% confidence interval (CI).

It is assumed that all the considered devices are connected in series in the reliability model, i.e., any capacitor in the capacitor bank failure will lead to system failure. Then the capacitor bank wear-out failure  $F_{CB}(t)$ can be calculated by

$$F_{CB}(t) = 1 - \prod (1 - F_i(t))$$

(25)

where  $F_i(t)$  is the CDF for each individual capacitor which is constructing the capacitor bank.

Fig. 18 shows the probability curves of wear-out failures of the capacitor bank for the conventional and the proposed case. It is noted that the lifetime  $B_5$  means that 5% of the total amount of capacitor bank fails both for the conventional and for the proposed case, which are 31.0 years and 27.2 years, respectively. The proposed case is slightly worse than the conventional case, because of the slightly higher capacitor temperature due to reduced capacitor count. However, the  $B_5$  lifetimes for both cases have enough high value for satisfying the target, which is expected to be longer than 20 years, as also specified in Table II.

#### VI. **CONCLUSIONS**

This paper proposes a method to reduce the dc-link capacitor voltage ripple for use in one power converter type of the MMCC family with Single Delta Bridge Cells (SDBC) under STATCOM operation by injecting the third harmonic zero-sequence current  $i_{zero}$ . The capacitor voltage formula is considering the injection of  $i_{zero}$  and applying the widely used Phase Shift PWM. The impact of the  $i_{zero}$  to the capacitor voltage ripple for different values of the output current and grid voltage condition is analyzed based on the method derived. The electrical and thermal stress of the power module is simulated on the practical-scaled MMCC-SDBC model having 80 MVar / 33 kV specifications. The proposed method can reduce

the capacitor voltage ripple by maximally 23 % without increasing the total power semiconductor losses and the junction temperature limitation by the injection of the  $i_{zero}$ at a current amplitude  $M_{iz3} = 0.4$  p.u. and a phase angle  $\phi_{iz3}$  = power factor angle. The capacitor bank is designed considering the capacitor voltage ripple, electrical and thermal stress. The obtained results show that the proposed method can reduce the capacitor bank volume by 20 %.

It is noted that, the converter peak current increases proportionally to the  $M_{iz3}$ . Therefore, the allowable amplitude  $M_{iz3}$  may be reduced at the practical product stage, considering each product design requirement, such as overcurrent level of gate block function and peak surge voltage at turn-off operation of power semiconductor devices.

#### REFERENCES

- [1] H. Akagi, "Multilevel Converters: Fundamental Circuits and Systems," Proceedings of the IEEE, vol. 105, No. 11, pp. 2048-2065, Nov. 2017

- M. Claus, S. Mcdonald, P. Cahill, D. Retzmann, M. Pereira and K. Uecker, "Innovative VSC Technology for Integration of "Green Energy" - without Impact on System Protection and Power Quality," in Proc. CIRED 21st International Conference on Electricity Distribution, 2011, pp. 1-4.

- K. Ilves, L. Harnefors, S. Norrga, and H. Nee, "Analysis and Operation of Modular Multilevel Converters With Phase-Shifted Carrier PWM," IEEE Trans. on Power Electron., vol. 30, no. 1, pp. 268-283, Jan. 2015.

- E. Behrouzian, M. Bongiorno, and R. Teodorescu, "Impact of Switching Harmonics on Capacitor Cells Balancing in Phase-Shifted PWM-Based Cascade H-Bridge STATCOM," IEEE Trans. on Power Electron., vol. 32, no. 1, pp. 815-824, Jan.

- P. Bordignon, G. Maragliano, M. Marchesoni, L. Vaccaro, "Effects of the 2nd Order Harmonic Leg Current in a MMC Converter," in Proc. of EPE, 2014, pp. 1-10.

- K. Li, C. Li, F. C. Lee, M. Mu, and Z. Zhao, "Precise Control Law of MMC and Its Application in Reducing Capacitor Voltage Ripple by Injecting Circulating Current," in Proc. of International Conference on Electrical Machines and system (ICEMS), 2015, pp. 371-377.

- [7] J. Pou, S. Ceballos, G. Konstantinou, V. G. Agelidis, R. Picas, and J. Zaragoza, "Circulating Current Injection Methods Based on Instantaneous Information for the Modular Multilevel Converter," IEEE Trans. on Ind. Electron., vol. 62, no. 2, pp. 777-788, Feb. 2015

- [8] H. R. Parikh, R. S. M. Loeches, G. Tsolaridis, R. Teodorescu, L. Mathe, and S. Chaudhary, "Capacitor voltage ripple reduction and arm energy balancing in MMC-HVDC," in Proc. of International Conference on Environment and Electrical Engineering (EEEIC), 2016, pp. 1-6.

- X. Li, Q. Song, W. Liu, S. Xu, Z. Zhu, and X. Li, "Performance Analysis and Optimization of Circulating Current Control for Modular Multilevel Converter," IEEE Trans. on Ind. Electron., vol. 63, no. 2, pp. 716-727, Feb. 2016.

- [10] H. Kim, S. Kim, Y. Chung, D. Yoo, C. Kim, and K. Hur, "Operating Region of Modular Multilevel Converter for HVDC With Controlled Second-Order Harmonic Circulating Current: Elaborating P-Q Capability," IEEE Trans. on Power Delivery, vol. 31, no. 2, pp. 493-502, Apr. 2016.

- [11] A. Marzoughi, R. Burgos, D. Boroyevich, and Y. Xue, Analysis of Capacitor Voltage Ripple Minimization in Modular Multilevel Converter Based on Average Model," in Proc. of Control and Modeling for Power Electronics (COMPEL), 2015,

- Perez, S. Bernet, "Capacitor Voltage Ripple Minimization in Modular Multilevel Converters," in Proc. of

- International Conference on Industrial Technology (ICIT), 2015,

- pp. 3022-3027 [13] C.D. Townsend, R. Aguilera, P. Acuna, G. Konstantinou, J. Pou, G. Mirzaeva, and G.C. Goodwin, "Capacitance Minimization in Modular Multilevel Converters: Using Model Predictive Control to Inject Optimal Circulating Currents and Zero-Sequence Voltage," in Proc. of Annual Southern Power Electronics Conference (SPEC), 2016, pp. 1-6.

- [14] T. Tanaka, H. Wang, F. Blaabjerg, "A DC-link Capacitor Voltage Oscillation Reduction Method for a Modular Multilevel Cascade Converter with Single Delta Bridge Cells (MMCC-SDBC)," in Proc. of ECCE-Asia, 2018, pp. 1-7.

- [15] T. Tanaka, K. Ma, H. Wang, F. Blaabjerg, "Asymmetrical Reactive Power Capability of Modular Multilevel Cascade Converter (MMCC) based STATCOMs for Offshore Wind Farm." IEEE Trans. on Power Electron. (Early access).

- [16] M. Hagiwara, R. Maeda, and H. Akagi, "Negative-Sequence Reactive-Power Control by a PWM STATCOM Based on a Modular Multilevel Cascade Converter (MMCC-SDBC)," IEEE Trans. Ind. Appl., vol. 48, no. 2, pp. 720-729, Mar./Apr. 2012.

- [17] Website of Hitachi Power Semiconductor Device, Ltd., Product Lineup of 4500V-IGBT module. [Online]. Available: http://www.hitachi-power-semiconductor-

- device.co.jp/en/product/ igbt/ list/4500v.html [18] H. Wang, and F. Blaabjerg, "Reliability of Capacitors for DC-Link Applications in Power Electronic Converters - An Overview," IEEE Trans. Ind. App., vol. 50, no. 5, pp. 3569-3578, Sep./Oct. 2014

- [19] Y. Song, and B. Wang, "Survey on Reliability of Power Electronics System," IEEE Trans. on Power Electron.., vol. 28, no. 1, pp. 591-604, Jan. 2013

- V. Najmi, J. Wang, R. Burgos, and D. Boroyevich, "High Reliability Capacitor Bank Design for Modular Multilevel Converter in MV Applications," in Proc. Energy Conversion Congress and Exposition (ECCE), 2014, pp. 1051-1058.

- [21] K. Sharifabadi, L. Harnefors, H. Nee, S. Norrga, and R. Teodorescu, Design, Control, and Application of Modular Multilevel Converters for HVDC Transmission Systems. Wiley-IEEE Press, 2016.

- [22] Website of Cornell Dubilier Company, Type Polypropylene, DC Link Capacitors. [Online]. Available: http://www.cde.com/ resources/catalogs/947C.pdf

- [23] S. G. Parler, "Deriving life multipliers for electrolytic capacitors," IEEE Power Electron. Soc. Newsl., vol. 16, no. 1, pp. 11-12, Feb. 2004.

- Y. Shen, A. Chub, H. Wang, D. Vinnikov, E. Liivik, and F. Blaabjerg, "Wear-out Failure Analysis of an Impedance-Source PV Microinverter Based on System-Level Electro-Thermal Modeling," IEEE Trans. Ind. Electron., 2018 (in press)

Takaaki Tanaka (M'18) received the B.E. degree in electrical engineering from National Institute of Technology, Maizuru College, Kyoto, Japan, in 2010 and the M.E. degree in electrical engineering from Nagaoka University of Technology, Niigata, Japan, in 2012. Since 2012, he has been with Fuji Electric, Co., Ltd., Tokyo, Japan.

Dr. Tanaka was a Visiting Researcher with the Center of Reliable Power Electronics (CORPE), Aalborg University, Aalborg, Denmark from Dec. 2015 to Nov. 2017. He received the Ph.D. degree in power electronics from CORPE, Aalborg University, in 2019. His research interests include power electronics and its applications such as in renewable energy, transportation, reliability, power density, WBG devices and circuit architecture.

Huai Wang (M'12, SM'17) received the B.E. degree in electrical engineering, from Huazhong University of Science and Technology, Wuhan, China, in 2007 and the Ph.D. degree in power electronics, from the City University of Hong Kong, Hong Kong, in 2012.

He is currently Professor with the Center of Reliable Power Electronics (CORPE), Department of Energy Technology at Aalborg University, Denmark. He was a Visiting Scientist with the ETH Zurich, Switzerland, from Aug. to Sep. 2014, and with the Massachusetts Institute of Technology (MIT), USA, from Sep. to Nov. 2013. He was with the ABB Corporate Research Center, Switzerland, in 2009. His research addresses the fundamental challenges in modelling and validation of power electronic component failure mechanisms, and application issues in system-level predictability, condition monitoring, circuit architecture, and robustness design.

Dr. Wang received the Richard M. Bass Outstanding Young Power Electronics Engineer Award from the IEEE Power Electronics Society in 2016, and the Green Talents Award from the German Federal Ministry of Education and Research in 2014. He is currently the Chair of IEEE PELS/IAS/IES Chapter in Denmark. He serves as an Associate Editor of IET Electronics Letters, IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS, and IEEE TRANSACTIONS ON POWER ELECTRONICS.

Frede Blaabjerg (S'86–M'88–SM'97–F'03) was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. From 1988 to 1992, he got the PhD degree in Electrical Engineering at Aalborg University in 1995. He became an Assistant Professor in 1992, an Associate Professor in 1996, and a Full Professor of power

electronics and drives in 1998. From 2017 he became a Villum Investigator. He is honoris causa at University Politehnica Timisoara (UPT), Romania and Tallinn Technical University (TTU) in Estonia.

His current research interests include power electronics and its applications such as in wind turbines, PV systems, reliability, harmonics and adjustable speed drives. He has published more than 600 journal papers in the fields of power electronics and its applications. He is the co-author of four monographs and editor of ten books in power electronics and its applications.

He has received 31 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award 2014, the Villum Kann Rasmussen Research Award 2014 and the Global Energy Prize in 2019. He was the Editor-in-Chief of the IEEE TRANSACTIONS ON POWER ELECTRONICS from

2006 to 2012. He has been Distinguished Lecturer for the IEEE Power Electronics Society from 2005 to 2007 and for the IEEE Industry Applications Society from 2010 to 2011 as well as 2017 to 2018. In 2019-2020 he serves a President of IEEE Power Electronics Society. He is Vice-President of the Danish Academy of Technical Sciences too.

He is nominated in 2014-2018 by Thomson Reuters to be between the most 250 cited researchers in Engineering in the world.