Aalborg Universitet

# A Digital Twin based Estimation Method for Health Indicators of DC-DC Converters

peng, yingzhou; Zhao, Shuai; Wang, Huai

Published in: I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2020.3009600

Publication date: 2021

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA): peng, Y., Zhao, S., & Wang, H. (2021). A Digital Twin based Estimation Method for Health Indicators of DC-DC Converters. *I E E Transactions on Power Electronics*, *36*(2), 2105-2118. [9141430]. https://doi.org/10.1109/TPEL.2020.3009600

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# A Digital Twin based Estimation Method for Health Indicators of DC-DC Converters

Yingzhou Peng, Student Member, IEEE, Shuai Zhao, Member, IEEE, Huai Wang, Senior Member, IEEE

Abstract—This paper proposes a health indicator estimation method based on the digital-twin concept aiming for condition monitoring of power electronic converters. The method is noninvasive, without additional hardware circuits, and calibration requirements. An application for a Buck DC-DC converter is demonstrated with theoretical analyses, practical considerations, and experimental verifications. The digital replica of an experimental prototype is established, which includes the power stage, sampling circuit, and close-loop controller. Particle Swarm Optimization (PSO) algorithm is applied to estimate the unknown circuit parameters of interest based on the incoming data from both the digital twin and the physical prototype. Cluster-data of the estimated health indicators under different testing conditions of the Buck converter is analyzed and used for observing the degradation trends of key components, such as capacitor and MOSFET. The outcomes of this study serve as a key step for achieving non-invasive, cost-effective, and robust condition monitoring for power electronic converters.

Index Terms—IGBT, DC-DC power converters, digital twin, parameter identification, reliability, condition monitoring

# I. INTRODUCTION

Power converters are subject to frequent functional and environmental strains, which can induces failures. The failure mechanisms of power converter are generally separated into two categories: (1) abrupt failure due to over stress conditions; and (2) wearing out and degradation due to long-term operation. The fault diagnosis has been researched for many years to deal with abrupt failures, which is not the content of this paper. After long-term operation, some components of power converter become too fragile to withstand the normal electrical and thermal stresses and a collapse of the entire system may happen.

Therefore, the anticipation of the degradation progress of power converter is important and meaningful so the fragile components can be replaced before a breakdown happens and it is called condition monitoring. It is revealed that the degradation progress of the key components in converters can be indicated by the change of their characteristic parameters, such as the on-state resistance of MOSFET and capacitance of capacitor [1], [2]. Therefore, the measurement of those health indicators is critical and the first step of condition monitoring. Then, data processing method is used to assess the health condition of those key components with considering practical environmental and operational conditions. Overall, condition monitoring could be useful for predictive maintenance based

Y. Peng, S. Zhao and H. Wang are with the Department of Energy Technology, Aalborg University, Aalborg, Denmark (email: ype@et.aau.dk, szh@et.aau.dk, hwa@et.aau.dk). on the estimated degradation level and remaining useful lifetime of the components of interest.

1

Component-level health indicators have been proposed for monitoring the degradation of power semiconductors and capacitors individually as shown in Table I [3]–[5], which can be classified into two groups: electrical and thermal indicators. Further, electrical indicators can be obtained from either the drain-source/collector-emitter terminals, such as the on-state voltage or resistance of power semiconductors, which can be measured by using measurement circuits [1], [6]-[8]. These indicators show higher sensitivity to the degradation of power semiconductors among existing indicators. But additional circuits are needed, which increases the implementation complexity. Existing gate-emitter related indicators includes the threshold voltage and miller plateau of power semiconductor, which can be obtained from the gate turn-on transient voltage waveform [9]–[12]. Since junction temperature is strongly related to the health condition of power semiconductors, temperature sensitive electrical parameters (TSEPs) can also be used as health indicator, such as pre-threshold voltage in [13], peak gate current in [14], kelvin-emitter voltage [15], and switching time in [16]. However, all of these gate related indicators are high frequency signals, demanding the high speed data acquisition circuit with good noise-immune ability, which increases the complexity further. Moreover, the malfunction of the added circuit may induce the failure of the gate driver. Thermal signals are also proposed for condition monitoring, such as case temperature in [17], [18] and thermal resistance in [19]. However, case temperature may be easily interfered by other heat sources (e.g. the neighboring power modules and components, the ambient temperature) and shows a low degradation sensitivity. The measurement of thermal resistance strongly depends on the accuracy of measuring junction temperature, case temperature and power losses of interested module, which is complicated and difficult.

As for the capacitor, the condition monitoring can be achieved through two ways: 1) taking advantage of the discharge process of capacitor when the power converter is in off-line [20]; 2) by measuring the ripple of capacitor voltage and current, the equivalent series resistance (ESR) and capacitance of the capacitor can be obtained [2], [21]. However, in practice, obtaining the ripple requires more steps: First, capacitor current is measured indirectly by combining the input current, output current, and the switching information of the power converter [22], [23], which may cause transfer errors. Then, measuring the ripple requires both the data acquisition apparatus with higher sampling rate and higher resolution, and high frequency pass filter circuit.

|                                    |                            | IADLE I                                                                               |                              |                               |                                |  |

|------------------------------------|----------------------------|---------------------------------------------------------------------------------------|------------------------------|-------------------------------|--------------------------------|--|

|                                    | Conv                       | ENTIONAL CONDITION MONIT                                                              | ORING METHODS                |                               |                                |  |

| Items                              | Measured signals           | Health indicators                                                                     | Implementation<br>complexity | Sensitivity to<br>degradation | Invasion to<br>original system |  |

|                                    |                            | On-state voltage [6]-[8]                                                              | +++                          | ++++                          | +++                            |  |

|                                    |                            | On-state resistance [1]                                                               | +++                          | ++++                          | +++                            |  |

| Component-level                    | Electrical signals         | Threshold voltage [9] ++++                                                            |                              | +++                           | ++++                           |  |

| (power                             |                            | Miller plateau [10], [11]                                                             | ++++                         | +++                           | ++++                           |  |

| semiconductor)                     |                            | TSEPs [13]–[16]                                                                       | ++++                         | +++                           | ++++                           |  |

|                                    | Thermal signals            | Case temperature [17], [18]                                                           | +                            | +                             | ++                             |  |

|                                    |                            | Thermal resistance [19]                                                               | ++++                         | ++++                          | +++                            |  |

| Component-level                    | Discharge process          | Capacitor voltage [20]                                                                | ++                           | +++                           | +                              |  |

| (capacitor)                        | Capacitor voltage and      | Capacitance and ESR [2],                                                              | ++++                         | ++                            | +++                            |  |

|                                    | current ripple             | [21]–[23]                                                                             |                              |                               |                                |  |

| System-level<br>(single component) |                            | Frequency response [24]                                                               | ++++                         | +                             | +++                            |  |

|                                    | System signals             | Harmonic [25]                                                                         | ++++                         | +                             | ++++                           |  |

|                                    |                            | ANN [26], [27]                                                                        | ++++                         | ++                            | +                              |  |

| System-level                       | System signals             | Parameter identification                                                              | ++                           | ++                            | +++                            |  |

| (multi-<br>components)             |                            | [28]–[31]                                                                             |                              |                               |                                |  |

| Data process                       | Calibration [6]            | Indicators are also sensitive to temperature and current, they need to be calibrated. |                              |                               |                                |  |

|                                    | Noise reduction [32], [33] | The measured indicators may consist of massive noises.                                |                              |                               |                                |  |

| TCED                               |                            | A NINI                                                                                | ECD                          |                               |                                |  |

|           | TABLE I                          |

|-----------|----------------------------------|

| CONVENTIO | NAL CONDITION MONITORING METHODS |

TSEPs: temperature sensitive electrical parameters. ANN: artificial neural network. ESR: equivalent series resistance

From the system-level view, various methods have been proposed to monitor the power semiconductors and capacitors, respectively, as listed in Table I. The frequency response of DC-DC converters is sensitive to the on-state resistance of power semiconductors in specific situations [24]. In addition, the output current harmonic of inverter is investigated to monitor the degradation of the solder layer of power semiconductor in [25]. Both methods require extra setups and show invasive to the system of interest. Moreover, they cannot distinguish the degradation of power semiconductor and capacitor. Artificial neural network is also a potential way for monitoring the degradation of capacitor [26], [27]. However, it requires offline testing to obtain the enough training data, which is difficult to achieve in practice.

Conventional model based parameter identification methods are used to modify the controller of power converters as listed in Table I. It is known that the transfer function between the output voltage and duty cycle ratio is discretized when design controller. Thus, the coefficients of transfer function can be calculated by using different algorithms, such as recursive least square (RLS) in [28] and Kalman filter (KF) in [29], which is effective in tuning controller and improving the system performance. However, mapping the coefficients of transfer function into the internal parameters of the converter could cause transfer errors and even doesn't have feasible solutions when the number of unknown parameters are more than that of the known equations. In [31], a simplified model of boost converter is built and a generalized gradient descent algorithm is applied to calculate the inductance and capacitance. A model for buck converter is developed in [30], where biogeographybased optimization (BBO) method is used to identify the internal parameters. The main issues with the above methods are that none of them focus on the degradation monitoring of the key components. Moreover, only the coefficients of the model (e.g. transfer function) or part of those physical parameters (e.g. inductance and capacitance) can be obtained. In addition, all of the above methods need to inject extra signal into the controller.

It is worth to mentioning that these measured indicators need to be processed further to reduce noises and to indicate the health status of power converter numerically. Such as lowpass filter and gaussian process [32], [33]. Finally, Calibration with other impactors (e.g. temperature and current) is needed as well. [6].

2

According to the analysis above, the challenges are still existed in these existing methods and they are expected to updated with the features of non-invasive, calibration-free, without additional circuits and the ability of monitoring both power semiconductor and capacitor.

Digital twin is a virtual representation of a physical system that virtually shares the same characteristics with its physical counterpart. It enables customers to better understand, optimize, predict, and monitor the performance of its installed systems [34], [35]. The concept of digital twin has been applied in power converters for fault diagnosis recently [36], [37], which is achieved by comparing the output signals of the digital twin and its physical counterpart in real-time. In this paper, the digital twin concept is used to estimate the health indicators of the key components in power converter, so as the degradation progress of power converter can be monitored. The digital twin technology includes two parts: the digital presentation of a physical system and an advanced algorithm for data analysis.

Firstly, a digital twin concept-based health indicator estimation method is proposed for a DC-DC converter case study. This digital twin is a virtual replica of physical converter and is able to update itself continuously according to the data coming from existing sensors in its physical counterpart. Then, PSO algorithm is applied to do data analysis and make the difference between the digital twin and its physical counterpart smaller than a pre-set threshold. Finally, a data-cluster concept is proposed to cover the estimated indicators at different possible operations.

The contributions of the presented study are: 1) it is easy to implement by taking advantage of existing sensors; 2) without additional hardware and modification in the system

Fig. 1. An example of the application of digital twin.

of interest; 3) it is capable of monitoring the degradation of the key components simultaneously; 4) by taking advantage of cluster-data based method to achieve the calibration-free and compensate the shortage of the proposed method in the low sensitivity to degradation. Part of the contents of this paper have been presented in [38], which mainly discussed the basic idea of the proposed method. In this paper, the stateof-the-arts discussion is enriched by considering componentlevel, system-level, single component and multi-components based condition monitoring methods. Moreover, the detail of the digital twin concept is illustrated through a MOSFETbased example and the experimental validation is carried out in a buck converter demonstrator with practical considerations, such as different voltages, currents, loadings and temperatures. In addition, a data analysis method is also given in this paper.

# II. DIGITAL TWIN OF BUCK CONVERTER

# A. Digital Twin Concept

An example of MOSFET-based digital twin is taken to illustrate the principle of digital twin firstly as shown in Fig.1 with seven components and they are explained as below:

- 1) Physical system: A real physical object or process.

- Sensors: Sensors are used to capture the operational signals of physical system, which could be voltage, current or temperature, etc.

- Data: The data from the sensors represent the operational condition or characteristics of physical system and they are used to update the digital twin continuously.

- 4) Digital twin: A digital replica of physical system.

- 5) Analytics: Analytics techniques are used to process the data from the sensors by using advanced algorithms and make the insights of digital twin same with the insights of its physical counterpart as much as possible.

- 6) Insight: The inside information of digital twin. The insights could be used to guide the action of physical system and better its performance. Also, it can be used to assess the operation condition of physical system.

- Action: According to the insights from analytics, action could be performed to better the performance of physical system or protect the physical system.

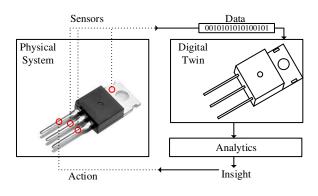

Fig. 2. Equivalent circuits of buck converter: (a)MOSFET is in on-state; (b)MOSFET is in off-state.

# B. Buck Converter Modeling

Fig.2 shows the equivalent circuits of Buck converter operating at on-state and off-state, which is represented by

$$\begin{bmatrix} \frac{di_{\rm L}}{dt} \\ \frac{dv_{\rm c}}{dt} \\ v_{\rm o} \end{bmatrix} = \begin{bmatrix} -\frac{1}{L}A & -\frac{1}{L}\left(\frac{R}{R_{\rm c}+R}\right) \\ \frac{1}{C}\left(\frac{R}{R_{\rm c}+R}\right) & -\frac{1}{C}\left(\frac{1}{R_{\rm c}+R}\right) \\ \frac{R_{\rm c}R}{R_{\rm c}+R} & \frac{R}{R_{\rm c}+R} \end{bmatrix} \times \begin{bmatrix} i_{\rm L} \\ v_{\rm c} \end{bmatrix} \\ +D\begin{bmatrix} \frac{1}{L}v_{\rm in} \\ 0 \\ 0 \end{bmatrix} + (1-D)\begin{bmatrix} -\frac{1}{L}V_{\rm f} \\ 0 \\ 0 \end{bmatrix} \\ A = \left(DR_{\rm dson} + R_{\rm L} + \frac{R_{\rm c}R}{R_{\rm c}+R}\right) \tag{1}$$

where  $i_{\rm L}$  is the inductor current,  $v_{\rm o}$  is the output voltage and  $v_{\rm c}$  is the capacitor voltage;  $R_{\rm dson}$ ,  $R_{\rm L}$  and  $R_{\rm C}$  are the parasitic resistances of MOSFET, inductor and capacitor, respectively;  $v_{\rm in}$  is the input voltage and  $V_{\rm f}$  is the forward voltage of diode; D is 1 when the MOSFET is on and 0 when the MOSFET is off.

Two ways can be applied to solve (1), and obtain  $i_{\rm L}$  and  $v_{\rm c}$ . One is to calculate the eigenvector and eigenvalue of differential equations and construct the general solution. Then, by using the initial values of  $i_{\rm L}$  and  $v_{\rm c}$ , the specific solution of these differential equations can be obtained [30]. This method demands heavy computation, especially the calculation of eigenvector and eigenvalue. The other one is to linearize the differential equations with acceptable accuracy, which is used in this paper. Then, the output voltage  $v_{\rm o}$  can be described with discrete time step:

$$v_{\rm o,n+1} = i_{\rm L,n+1} \frac{R_{\rm c}R}{R_{\rm c}+R} + v_{\rm c,n+1} \frac{R}{R_{\rm c}+R}$$

(2)

where the  $n^{th}$  time step is defined as the present time interval, the  $(n+1)^{th}$  time step represents the next one.  $v_{o,n+1}$  indicates the output voltage at  $(n+1)^{th}$  step, which is unknown at This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2020.3009600, IEEE Transactions on Power Electronics

#### IEEE TRANSACTIONS ON POWER ELECTRONICS

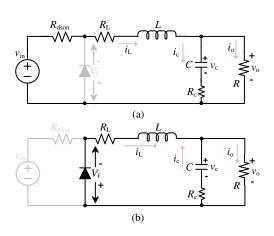

Fig. 3. Case study of the application of digital twin concept in condition monitoring with a buck converter (n = n + 1 means updating the time step,  $R_1$ - $R_4$ ,  $R_f$ , and  $C_f$  are the parameters of sampling circuit,  $v_{tri}$  is the triangular carrier,  $f_{obj}$  is the objective function, w is the learning factor in (13), N is the number of sampled output voltage and inductor current from physical converter, n is the total iteration steps of the digital twin for updating parameters one time,  $t_s$  is the sampling period of measuring output voltage, inductor current, and input voltage from physical converter, h is the calculation time step interval inside the digital twin).

present  $n^{th}$  step. Therefore, in the following discussions,  $i_{L,n+1}$  and  $v_{c,n+1}$  are derived based on the present values  $i_{L,n}$  and  $v_{c,n}$ , so that the output voltage at the  $(n+1)^{th}$  time step can be represented by the inductor current and capacitor voltage at  $n^{th}$  time step.

Runge-Kutta is a typical method to solve differential equations [39]. A typical 4th-order Runge-Kutta method is used in this paper to linearize the differential equations and it is considered as sufficient for buck converter modeling to achieve an negligible error. To simplify the analysis process, (1) is rewritten as below:

$$\begin{cases} f_1(i_{\rm L}, v_{\rm c}) = \frac{di_{\rm L}}{dt} \\ f_2(i_{\rm L}, v_{\rm c}) = \frac{dv_{\rm c}}{dt} \end{cases}$$

(3)

With 4th-order Runge-Kutta method,  $i_{L,n+1}$  and  $v_{c,n+1}$  can be expressed as:

$$\begin{cases} i_{\mathrm{L,n+1}} = i_{\mathrm{L,n}} + \frac{h}{6} \left( k_{\mathrm{a1}} + 2k_{\mathrm{a2}} + 2k_{\mathrm{a3}} + k_{\mathrm{a4}} \right) \\ v_{\mathrm{c,n+1}} = v_{\mathrm{c,n}} + \frac{h}{6} \left( k_{\mathrm{b1}} + 2k_{\mathrm{b2}} + 2k_{\mathrm{b3}} + k_{\mathrm{b4}} \right) \end{cases}$$

(4)

where  $k_{a1}$ - $k_{a4}$  and  $k_{b1}$ - $k_{b4}$  are used to calculate the average

change rate between  $(n)^{th}$  and  $(n+1)^{th}$  step as shown below:

$$\begin{cases} k_{a1} = f_{1} (x_{n}, y_{n}) \\ k_{b1} = f_{2} (x_{n}, y_{n}) \\ k_{a2} = f_{1} \left( x_{n} + \frac{h}{2} k_{a1}, y_{n} + \frac{h}{2} k_{b1} \right) \\ k_{b2} = f_{2} \left( x_{n} + \frac{h}{2} k_{a1}, y_{n} + \frac{h}{2} k_{b1} \right) \\ k_{a3} = f_{1} \left( x_{n} + \frac{h}{2} k_{a2}, y_{n} + \frac{h}{2} k_{b2} \right) \\ k_{b3} = f_{2} \left( x_{n} + \frac{h}{2} k_{a2}, y_{n} + \frac{h}{2} k_{b2} \right) \\ k_{a4} = f_{1} (x_{n} + h k_{a3}, y_{n} + h k_{b3}) \\ k_{b4} = f_{2} (x_{n} + h k_{a3}, y_{n} + h k_{b3}) \end{cases}$$

(5)

4

where h is the calculation step time between  $n^{th}$  and  $(n+1)^{th}$  time step.

Substitute (3) into (5), (5) into (4), and (4) into (2), the final expression of  $v_o$  can be obtained as :

<sup>0885-8993 (</sup>c) 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Aalborg Universitetsbibliotek. Downloaded on July 21,2020 at 12:52:51 UTC from IEEE Xplore. Restrictions apply.

$$\begin{cases} v_{o,n+1} = ai_{L,n} + bv_{c,n} + c \\ a = f_3(L, C, R_L, R_C, R_{dson}) \\ b = f_4(L, C, R_L, R_C, R_{dson}) \\ c = f_5(L, C, R_L, R_C, R_{dson}) \end{cases}$$

(6)

where coefficients a, b, and c are constructed by seven parameters (L, C,  $R_{\rm L}$ ,  $R_{\rm C}$ ,  $R_{\rm dson}$ , D, and  $v_{\rm in}$ ) with complicated combinations since there are five layers substitution from (3) to (2). Among them, L, C,  $R_{\rm L}$ ,  $R_{\rm C}$ , and  $R_{\rm dson}$  are unknown parameters. D is calculated through the sampling circuit model and close-loop controller model described later.  $v_{\rm in}$  is measured from the physical converter. Therefore, the output voltage at  $(n+1)^{th}$  step can be calculated by using the inductor current and capacitor voltage at  $n^{th}$  step. Then,  $v_{\rm o}$  is used to determine the on-off state of MOSFET D through the following sampling circuit and close-loop controller model.

### C. Sampling Circuit

A typical sampling circuit is adopted which includes a differential amplifier circuit and a  $R_{\rm f}C_{\rm f}$  low-pass filter as shown in Fig.3. The amplifier output voltage  $v_{\rm p}$  is:

$$v_{\mathrm{p,n+1}} = \frac{(R_3 + R_4)R_2}{(R_1 + R_4)R_5} v_{\mathrm{o,n+1}} \tag{7}$$

The output of  $R_{\rm f}C_{\rm f}$  filter  $v_{\rm ad}$  is:

$$\begin{cases} v_{\rm ad,n+1} = v_{\rm p} - R_{\rm f}C_{\rm f}\frac{dv_{\rm ad,n+1}}{dt} \\ f_{\rm 6}(v_{\rm ad,n+1}) = \frac{dv_{\rm ad,n+1}}{dt} = \frac{v_{\rm p} - v_{\rm ad,n+1}}{R_{\rm f}C_{\rm f}} \end{cases}$$

(8)

Based on 4th-order Rung-Kutta method, (8) can be linearized as below:

#### D. Close-Loop controller

To obtain modulation signal  $v_{\rm m}$ , the close-loop controller is built in digital twin as shown in Fig.3. The process of controller can be expressed by following linear equations:

$$v_{e,n} = v_{e,n+1}$$

$$v_{m,n} = v_{m,n+1}$$

$$v_{e,n+1} = V_{ref} - v_{ad,n+1}$$

$$v_{m,n+1} = v_{m,n} + K_p(v_{e,n+1} - v_{e,n}) + K_I h v_{e,n+1}$$

(10)

where  $V_{\rm ref}$  is the reference of the output voltage,  $v_{\rm e}$  is the error between the output voltage and its reference,  $v_{\rm m}$  is the modulation signal,  $K_{\rm P}$  and  $K_{\rm I}$  are the parameters of the PI controller. Based on (10), the digital twin of buck converter can generate the modulation signal by itself instead of accessing to the physical controller. It is worth to mentioning that the sampling rate of physical buck converter system is usually set to the switching frequency and the time delay in updating the duty cycle ratio should be considered.

Then, the on-off state of MOSFET D is decided by comparing  $v_{\rm m}$  with a triangular carrier signal  $v_{\rm tri}$  as below:

$$D_{n+1} = \begin{cases} 1(v_{m,n+1} \ge v_{tri,n+1})\\ 0(v_{m,n+1} < v_{tri,n+1}) \end{cases}$$

(11)

# III. APPLICATION OF DIGITAL TWIN IN CONDITION MONITORING

The final model of the buck converter developed in this paper is expressed by (6). It can be seen that the coefficients a, b, and c are highly nonlinear functions with five variables. Therefore, the traditional algorithms, like recursive least squares (RLS) and Kalman filter (KF), are not able to estimate the developed model in this paper [40]. Further, the extended Kalman filter (EKF) is proposed to solve the nonlinear problem. However, It suffers instability due to the linearization and costly derivative calculation of Jacobian or Hessian matrices, and its performance deteriorates when the signal model is highly nonlinear [41]. More importantly, a critical point during the design of EKF and unscented Kalman filter (UKF) is the determination of the covariance matrices of the process noise, the measurement noise, and the initial state vector, which are often estimated from a tedious trail-and-error tuning or self-tuning algorithms [29], [40], [42]. Considering the complex process and restrictions of EKF, PSO is chosen in this case study because it is an end-to-end solution, and has a simpler implementation process and better generality to different models. It is agreed that PSO requires more computation than KF-based algorithms. But the computation time of the algorithm is not critical in the application presented here, since the degradation of power electronic components is a slow process itself.

PSO is a population-based iterative optimization algorithm that mimics the swarm behavior in birds flocking and fish schooling to guide the particles to search for the globally optimal solutions [43]. Based on this, it is possible to search for the optimal solutions of the internal parameters of digital twin buck converter. To implement PSO, the first step is to construct an objective function. In this paper, the objective function is:

$$f_{\rm obj} = \frac{\sum_{j=1}^{N} \left[ (i_{\rm L,j} - i_{\rm Lm,j})^2 + (v_{\rm o,j} - v_{\rm om,j})^2 \right]}{N}$$

(12)

where  $i_{L,j}$  and  $v_{o,j}$  are the calculated inductor current and output voltage from the digital twin buck converter.  $i_{Lm,j}$  and  $v_{om,j}$  are the measured data from the physical buck converter, N is the sample size of the measured data. The internal parameters of physical buck converter can be obtained by minimizing the objective function defined in (12) with PSO algorithm.

The procedure of the proposed digital twin-based condition monitoring method is shown in Fig.3, which includes three parts: digital world, physical world, and the interface (PSO algorithm) between them. P represents the parameter set including L, C,  $R_c$ ,  $R_L$ , and  $R_{dson}$ . Firstly, the parameter set P,  $i_L$ ,  $v_c$ , and the on-off state D are initialized and n is 0 at the beginning time step. Then, the inductor current  $i_L$ , capacitor voltage  $v_c$ , and output voltage  $v_o$  at next step can be calculated through (4) and (6), and the time step is updated by n = n + 1. Finally, D is updated through the developed sampling circuit and close-loop controller model and sent back into converter model to do next loop calculation.

Because the calculation time step h is different with the sampling period  $t_s$ . The number of calculated  $i_L$  and  $v_o$  n is reduced to N by  $N = hn/t_s$  evenly. Then the calculated  $i_L$  and  $v_o$  sets from the digital twin and the measured  $i_{Lm}$  and  $v_{om}$  sets from the physical one are used to calculate  $f_{obj}$  by (12). Thereafter, perturbation mechanism is added to avoid trapping into local optima by constructing a series of new  $f_{obj}$ . After that, the best  $f_{obj}$  among all  $f_{obj}$  is found. If the  $f_{obj}$  is smaller than the pre-set threshold, the output parameter set from the digital twin represents the operational condition of physical buck converter. Otherwise, the parameter set will be updated by the following equations:

$$V_{i,j} = \omega_{i-1} V_{i-1,j} + 2r_{1,i-1,j} \left( P_{G} - P_{i-1,j} \right) + 2r_{2,i-1,j} \left( P_{L,i-1,j} - P_{i-1,j} \right)$$

(13)

$$P_{i,j} = P_{i-1,j} + V_{i,j} \tag{14}$$

where *i* is the number of iteration, *j* is the number of particle,  $V_{i,j}$  is the moving velocity of the  $j^{th}$  particle in  $i^{th}$  iteration;  $P_G$  is the global optimization,  $P_{L,i-1,j}$  is the individual optimization of the  $j^{th}$  particle until  $(i - 1)^{th}$  iteration;  $P_{i,j}$  is the position of the  $j^{th}$  particle in  $i^{th}$  iteration; *w* is the learning factor that is updated continuously according to the method presented in [43].  $r_1$  and  $r_2$  are weighting factors and they are set to 2. The detail about how to chose these factors can be found in [43].

Finally, the new obtained P is sent back into the digital twin of buck converter to do next step calculation.

In addition, the converging process of PSO may trap into local optima. To avoid this, a proper perturbation is needed. In this paper, after obtaining the global optimization  $P_{\rm G}$  in each iteration, a perturbation factor is introduced to construct a series of new particles. Then, a series of new  $f_{\rm obj}$  can be obtained. The detail of the perturbation process can be see in [44].

# IV. APPLICATION FOR CONDITION MONITORING AND EXPERIMENTAL VALIDATION

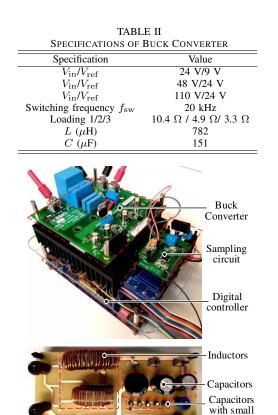

To validate the proposed method, a buck converter demonstrator is built as shown in Fig.4(a) and its specifications are presented in Table II. The LC filter module is built by using several different inductors and capacitors, then they can be switched easily during test. This study leverages the

6

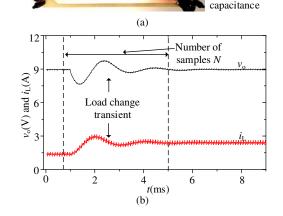

Fig. 4. Experimental setup: (a) physical Buck converter system; (b) load change transient waveforms of  $i_{\rm L}$  and  $v_{\rm o}$ .

load change transients, which is relevant to many practical applications. The example waveforms are shown in Fig.4(b) and part of the waveform data are used in this study.

#### A. Parameter Identification

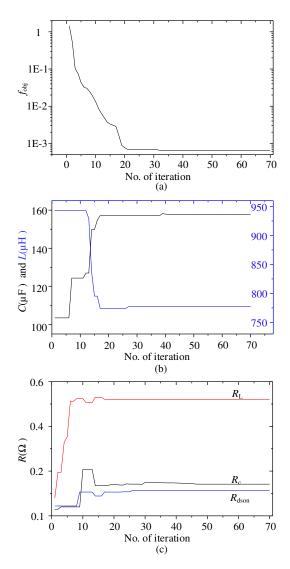

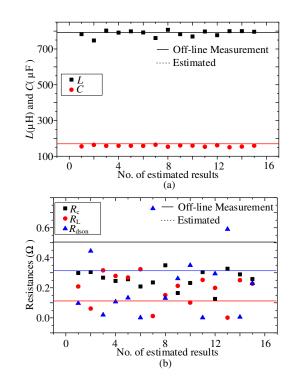

By following the procedure shown in Fig.3, the parameters of buck converter can be obtained. Fig.5(a) shows the descending process of  $f_{obj}$  and its final value is 6e-4 after 50 generations. Meanwhile, these parameters converge to a stable value after 50 generations as illustrated in Fig.5(b) and Fig.5(c), which means the difference of the output waveforms between the digital twin buck converter and its physical counterpart is 6e-4. At this moment, these estimated parameters represent the condition of physical buck converter.

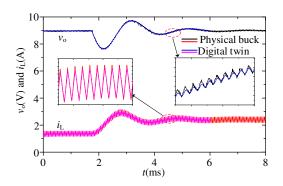

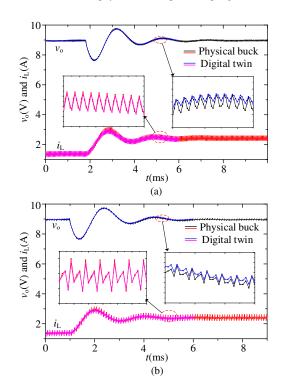

The comparisons of  $i_{\rm L}$  and  $v_{\rm o}$  between the digital twin buck converter and the physical one are shown in Fig.6. It can be

Authorized licensed use limited to: Aalborg Universitetsbibliotek. Downloaded on July 21,2020 at 12:52:51 UTC from IEEE Xplore. Restrictions apply.

Fig. 5. Process of parameter convergence: (a) Descent process of objective function; (b) capacitance and inductance; (c) parasitic resistances  $R_{\rm L}$ ,  $R_{\rm c}$  and  $R_{\rm dson}$ .

seen that the waveforms are almost overlapped with each other in both dynamic and static responses, which indirectly prove that the estimated parameters by using the proposed method are very close to the real parameters in the physical one.

For condition monitoring, practical issues should be considered. In the rest of this paper, the impact of sampling rate, the uncertainty caused by errors, the different voltage conversions, loadings, and temperatures are discussed. Simultaneously parameter degradation monitoring for capacitor and MOSFET is investigated quantitatively as well.

#### B. Impact of Sampling Rate

The digital twin works as a sensor-enabled digital model of a physical system. Thus, the sampling rate may affect the accuracy of the results of the digital twin. To uncover this, the proposed method is performed in different sampling rate situations and the results are shown in Fig.7 (the situation when  $f_{\rm sr}$ =1 MHz is presented in Fig.6). With different sampling rate, the ripples of  $i_{\rm L}$  and  $v_{\rm o}$  in digital twin and

7

Fig. 6. Comparisons of inductor current and output voltage between digital twin buck converter and its physical counterpart (sampling rate = 1MHz).

Fig. 7. Comparisons of inductor current and output voltage between digital twin buck converter and its physical counterpart in different sampling rate (the situation when  $f_{\rm sr}$ =1 MHz is presented in Fig.6): (a)  $f_{\rm sr}$ = 100 kHz; (b)  $f_{\rm sr}$ = 50 kHz.

physical one are different. However, they show the same result in dynamic responses. it is known that inductance and capacitance are sensitive to the dynamic responses of  $i_{\rm L}$ and  $v_{\rm o}$ , while the parasitic resistances are sensitive to the ripples of  $i_{\rm L}$  and  $v_{\rm o}$ . Therefore, lower sampling rate could cause higher measurement errors in the ripples of  $i_{\rm L}$  and  $v_{\rm o}$ , which may lead to errors in estimating the results of parasitic resistances. Therefore, to sense the change of the switching ripple, a sampling rate with at least double switching frequency is needed as shown in Fig.7(b). In the rest of this paper, 50 kHz sampling rate is chosen to acquire  $i_{\rm L}$  and  $v_{\rm o}$ .

# C. Impact of errors

To investigate the consistency of the proposed method, Fig.8 includes the results of the estimated inductance, capacitance,

TABLE III

| DIFFEF | DIFFERENT OPERATIONAL CONDITIONS |                        |  |  |  |  |

|--------|----------------------------------|------------------------|--|--|--|--|

| Cases  | $V_{\rm in}/V_{\rm o}$ (V)       | Load change $(\Omega)$ |  |  |  |  |

| case1  | 24/9                             | 4.85/3.32              |  |  |  |  |

| case2  | 24/9                             | 10.43/4.85             |  |  |  |  |

| case3  | 48/24                            | 4.85/3.32              |  |  |  |  |

| case4  | 48/24                            | 10.43/4.85             |  |  |  |  |

| case5  | 110/24                           | 4.85/3.32              |  |  |  |  |

| case6  | 110/24                           | 10.43/4.85             |  |  |  |  |

and parasitic resistances for 15 repeated estimations. It can be noted that the estimated capacitance and inductance exhibit smaller fluctuation along with the results measured off-line (LC and their parasitic resistances are measured by LCR meter,  $R_{\rm dson}$  is measured by conducting a certain current), compared to that of parasitic resistances, since the capacitor and inductor are more sensitive to the load dynamics of the buck converter. Among parasitic resistances, the estimated result of  $R_{\rm c}$  is more stable than the results of  $R_{\rm L}$  and  $R_{\rm dson}$ . Because the inductor and MOSFET in buck converter can be seen as in series, which is discussed in the part F of Section IV. Overall, the certain level of estimation errors exist with the proposed method and are caused by: 1) the developed digital twin without considering the parasitic parameters of wires; 2) the sampling circuit without sensing very accurate voltage and current; 3) the different processor of close-loop controller between physical buck converter (DSP) and digital twin (computer); and 4) In relative to the results measured offline, those parameters experience changes when the converter is in operation.

#### D. Impact of environmental and operation conditions

In practice, the environmental and operation conditions can also affect the values of the health indicators, besides the degradation level of the components of interest, which is a common issue to various condition monitoring methods to date. Moreover, as shown in Fig.8, there are certain level of estimation errors. One way to address the issue is to calibrate the components of interest at different environmental and operation conditions, as applied in [6] and [7]. Nevertheless, it is time consuming and may not be practical by considering that it is necessary to calibrate each components in each produced unit due to the initial parameter variations among a population of units. In order to avoid the calibration process, this study proposes a data-cluster based method for condition monitoring.

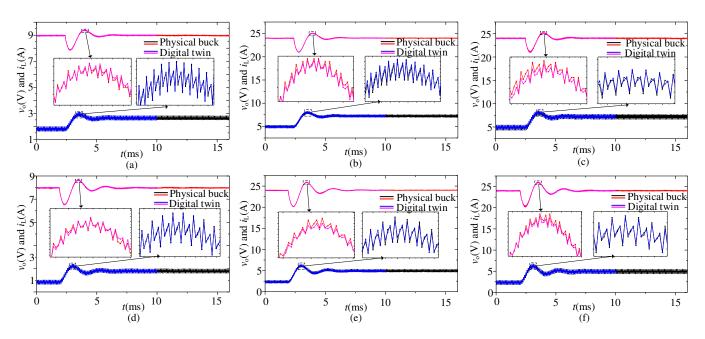

To achieve this, the proposed method is tested in six different operational conditions as listed in Table III. The corresponding results are depicted in Fig.9, showing that the proposed digital twin is able to present the similar operation characteristics with its physical counterpart even in different operational conditions. The identified parameters are given in next section. In this paper, five capacitances and five MOS-FETs are used to simulate the degradation level of capacitor and MOSFET as listed in Table IV and Table V, respectively. It should be noted that the case temperatures of MOSFETS are different in operation due to the different power losses as recorded in Table VI.

8

Fig. 8. Estimated results when  $V_{\rm in}/V_{\rm o}$  is 24/9 V and the load is changed from 4.85 to 3.32  $\Omega$ , and the measured results off-line (the proposed method is repeated for 15 times to show the fluctuation of estimated results, but the load change transient data is measured for only 1 time. The  $R_{\rm dson}$  is measured off-line by conducting a certain current): (a) inductance and capacitance; (b) parasitic resistances.

| TABLE IV<br>Percentage Change of Capacitance During Test |             |       |       |       |       |

|----------------------------------------------------------|-------------|-------|-------|-------|-------|

| Caps                                                     | C1          | C2    | C3    | C4    | C5    |

| $\Delta C$                                               | 0% (165 μF) | -2.2% | -4.4% | -6.6% | -8.8% |

| TABLE V<br>ON-STATE RESISTANCES OF THE MOSFETS UNDER TEST |      |       |       |       |      |  |  |

|-----------------------------------------------------------|------|-------|-------|-------|------|--|--|

| MOSFETs                                                   | M1   | M2    | M3    | M4    | M5   |  |  |

| $R_{\rm dson}$ ( $\Omega$ ) 0                             | ).11 | 0.241 | 0.385 | 0.495 | 0.75 |  |  |

TABLE VI CASE TEMPERATURE OF THE MOSFETS UNDER TEST IN DIFFERENT OPERATIONAL CONDITIONS (UNIT: °C)

| OTERATIONAL CONDITIONS (ONTL. C) |                |                |            |                |            |  |

|----------------------------------|----------------|----------------|------------|----------------|------------|--|

| Cases                            | $T_{\rm c-M1}$ | $T_{\rm c-M2}$ | $T_{c-M3}$ | $T_{\rm c-M4}$ | $T_{c-M5}$ |  |

| case1                            | 27.5           | 27.8           | 28         | 28.8           | 28.3       |  |

| case2                            | 25.7           | 26.8           | 26.5       | 27.1           | 26.5       |  |

| case3                            | 29             | 39.4           | 40.9       | 44             | 55         |  |

| case4                            | 26.5           | 29.1           | 29.3       | 32.8           | 34.8       |  |

| case5                            | 28.4           | 32.4           | 36.7       | 37.3           | 39.5       |  |

| case6                            | 26.1           | 27.5           | 28.4       | 29.7           | 30.8       |  |

#### E. Capacitor Degradation Monitoring

It has been revealed that the capacitance may drop by 5%-20% after a long-term operation [5]. Therefore, in this paper, another four capacitors with small capacitance (3.6  $\mu$ F for each one) are in parallel with the original capacitor (151  $\mu$ F) as shown in Fig.4(a) and Table IV. Then, these extra four capacitors are taken away one by one to simulate the degradation of capacitor (each one represents the drop of capacitance by 2.2%). In order to cover the fluctuations of the estimated results, the procedure shown in Fig.3 is

Fig. 9. Comparisons of the output waveforms between the digital twin and its physical counterpart in different operational conditions: (a) case1; (b) case3; (c) case5; (d) case2; (e) case4; (f) case6.

Fig. 10. Estimated results in different operational cases and when C is manually decreased from C1 to C5 (here MOSFET M1 is applied. case 1-6 are described in Table III, C1-C5 are described in Table IV): (a) L; (b)  $R_{\rm L}$ ; (c)  $R_{\rm dson}$ ; (d) C; (e)  $R_{\rm c}$ .

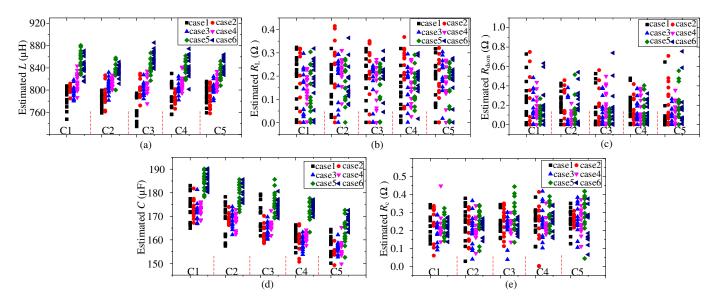

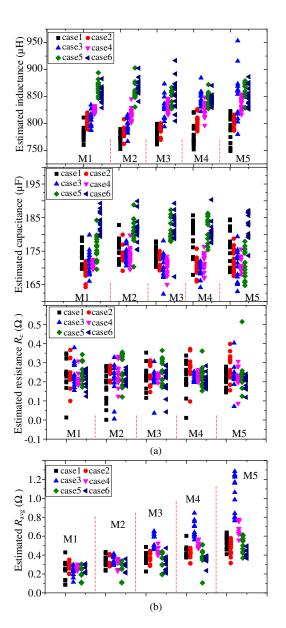

performed for 15 times with an individual recorded  $i_{\rm L}$  and  $v_{\rm o}$ . Fig.10 summarizes the estimated results. The simulated degradation levels of capacitor are indicated with the data clusters from C1 to C5. The operational cases are represented by different colors. The data with the same color represents the distribution of the estimated results at a given condition. Among them, the estimated L,  $R_{\rm L}$ , and  $R_{\rm dson}$  are independent from the change of capacitance. While, for the capacitor related parameters, after taking away the paralleled capacitors one by one, although part of the data within the adjacent clusters are overlapped, collectively, the estimated  $R_{\rm c}$  has a slightly increasing trend.

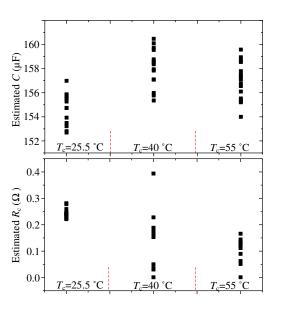

capacitor  $T_c$  by 3 °C. Therefore, a heater is sticked on the surface of the capacitor to increase the  $T_c$  and to investigate the effect of the temperature on the proposed method. It can be seen from Fig.11 that the capacitance is increased by only 2-3  $\mu$ F when  $T_c$  is increased by 30 °C. While the perturbations of the estimated C and  $R_c$  are 9  $\mu$ F and 0.4  $\Omega$  with increasing  $T_c$  by 30 °C, respectively. However, this perturbation is still within the perturbation of the results in Fig.10. Thus, the proposed cluster-data based method is still effective when the  $T_c$  of capacitor is changed.

9

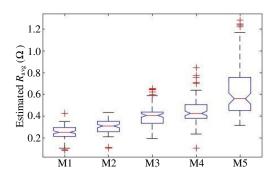

# F. MOSFET Degradation Monitoring

Conventionally, the on-state resistance of MOSFET  $R_{dson}$  is effective in indicating its health condition. As discussed

The self-heating can only increase the case temperature of

0885-8993 (c) 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Aalborg Universitetsbibliotek. Downloaded on July 21,2020 at 12:52:51 UTC from IEEE Xplore. Restrictions apply.

Fig. 11. Estimated C and  $R_c$  when case temperature  $T_c$  is changed (case 6).

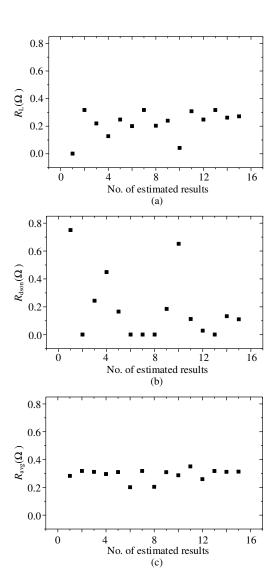

before, the estimated  $R_{\rm L}$  and  $R_{\rm dson}$  fluctuate in a large range. Therefore, it is challenging to monitor the degradation of MOSFET by using the estimated  $R_{\rm dson}$  directly. However, according to Fig.2 and (1), it can be seen that  $R_{\rm L}$  and  $R_{\rm dson}$  have almost same impact on  $v_{\rm o}$  and  $i_{\rm L}$ , which means distinguishing them is virtually impossible. To overcome this challenge, a new equivalent period average resistance is proposed and defined as below to represent both  $R_{\rm L}$  and  $R_{\rm dson}$  in this paper:

$$R_{\rm avg} = R_{\rm L} + DR_{\rm dson} \tag{15}$$

D can be obtained from the digital twin controller.  $R_{\rm dson}$ works only when the MOSFET is turned on, while  $R_{\rm L}$  works in the whole switching period. Therefore,  $R_{\rm L}$  and  $R_{\rm dson}$ can be represented by an equivalent average resistance  $R_{\rm avg}$ . To verify this, the estimated  $R_{\rm L}$  and  $R_{\rm dson}$  are illustrated in Fig.12(a) and Fig.12(b), respectively, which shows they fluctuate within a relative large range, but  $R_{\rm avg}$  keeps stable within a relative small range as shown in Fig.12(c). In addition, it is worth to mentioning that inductor usually possesses very stable characteristics and its parameters are not changed during operation. Thus,  $R_{\rm avg}$  enables the proposed method to monitor the degradation of MOSFET.

An accelerated power cycling platform was designed in [45], where  $R_{\rm dson}$  is used as the indicator of aging process. In this study,  $\Delta R_{\rm dson}$  reaches higher value before the MOSFETs actually fail (0.3  $\Omega$  -1  $\Omega$ ). Usually, package related aging may only causes 5%-20% increase in  $R_{\rm dson}$ . Such higher increase shown in [45] is mainly due to the degradation of MOSFET chip as the significantly decrease of the gate-oxide capacitance, which results in the driving voltage drops lower than normal value. Then, the MOSFET operating in saturation region exhibits high output impedance [24]. Based on this, five MOSFETs with different  $R_{\rm dson}$  are chosen in this paper to simulate the degradation of MOSFET as listed in Table V (the  $R_{\rm dson}$  of those MOSFETs are measured experimentally off-line). The case temperature of the MOSFETs in each

Fig. 12. Estimated parasitic resistances (the proposed calculation procedure is repeated for 15 times): (a) the parasitic resistance of inductor; (b) the on-state resistance of MOSFET; (c) defined equivalent average resistance of  $R_{\rm L}$  and  $R_{\rm dson}$  by using equation (15).

operational condition is recorded as listed in Table VI, showing higher temperature with higher on-state resistance, current, and duty cycle, such as those MOSFETs operating in case3. Then, the estimated results over different operational cases and MOSFETs are indicated with different colors and from M1 to M5, respectively, as shown in Fig.13. The estimated L, C, and  $R_c$  are immune from the simulated degradation of MOSFET. While the estimated  $R_{avg}$  shows increasing trend from M1 to M5. Especially the relative large increment in case3 and case4 due to the higher temperature, which proves the ability of the proposed method in detecting the degradation progress of the MOSFET in a buck converter.

# G. Simultaneous degradation test

In practice, the degradation of capacitor and MOSFET may happen simultaneously. Therefore, it is necessary to verify the ability of the proposed method in monitoring the simultaneous degradation among these two key components. The estimated

Fig. 13. Estimated results over different operational cases and simulated degradation levels of MOSFET (here the applied capacitor is 165  $\mu$ F(C1). case 1-6 are described in Table III, the case temperature of MOSFETs are listed in Table VI, M1-M5 are described in Table V): (a) *L*, *C*, and *R*<sub>c</sub>; (b)  $R_{\rm avg}$ .

results are shown in Fig.14, which proves the degradation trend of capacitor and MOSFET can be identified simultaneously by the proposed method.

#### H. Data analysis

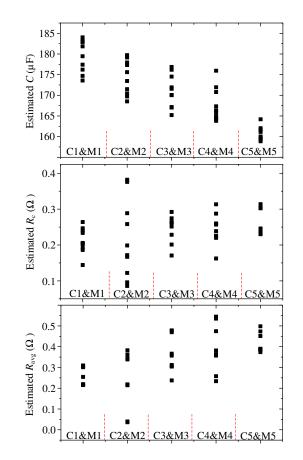

Due to the variations from the measurement errors, the temperature factors, and the workloads, the component parameters are obtained as a data cluster. To provide an evaluation standard, the boxplot technique is applied to derive the statistical measures of the data cluster so as to quantify the degradation levels. Boxplot technique is an effective method for the representation of data structure by calculating the statistics including median and quantiles, based on which the degradation trend can be clearly determined. With the data

11

Fig. 14. Estimated C,  $R_c$  and  $R_{avg}$  when capacitor and MOSFET are degraded simultaneously (case6) (M1-M5 are described in Table.V, C1-C5 are described in Table.IV).

TABLE VII Obtained Median Value of the Identified Parameters After Data Process

| DATA I ROCESS |                          |                                                                                               |                                                                                                                                               |                                                                                                                                                                                               |  |  |

|---------------|--------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| C1            | C2                       | C3                                                                                            | C4                                                                                                                                            | C5                                                                                                                                                                                            |  |  |

| 174.9         | 170.9                    | 167.3                                                                                         | 162.2                                                                                                                                         | 158                                                                                                                                                                                           |  |  |

| 224           | 232                      | 233                                                                                           | 254                                                                                                                                           | 273                                                                                                                                                                                           |  |  |

| M1            | M2                       | M3                                                                                            | M4                                                                                                                                            | M5                                                                                                                                                                                            |  |  |

| 252           | 310                      | 407                                                                                           | 426                                                                                                                                           | 561                                                                                                                                                                                           |  |  |

|               | C1<br>174.9<br>224<br>M1 | C1         C2           174.9         170.9           224         232           M1         M2 | C1         C2         C3           174.9         170.9         167.3           224         232         233           M1         M2         M3 | C1         C2         C3         C4           174.9         170.9         167.3         162.2           224         232         233         254           M1         M2         M3         M4 |  |  |

clusters in Fig.10(d), Fig.10(e), and Fig.13(b), the respective boxplots of these clusters are calculated and shown in Fig.15 and Fig.16. As can be seen, there is a clear degradation trend according to the medians of the data cluster, and the details are given in Table VII. Those outliers are those data is out of 95% confidence interval and the existing of those outliers is reasonable due to the experimental noise. The more narrower box means the data are more concentrated. Specifically, the estimated medians of C and  $R_c$  are decreased by 9.7% and increased by 21% respectively when the capacitor is degraded by 8.8%. Meanwhile, the median of  $R_{\rm avg}$  is increased from 0.243  $\Omega$  to 0.561  $\Omega$  when the  $R_{\rm dson}$  is manually increased from 0.11  $\Omega$  to 0.75  $\Omega$ . Although the estimated parameters are not quite close to the real ones, the relative degradation change of each parameter can be identified, which demonstrates that the proposed method is effective in monitoring the degradation level of the key components in Buck converters.

The Buck converter is considered as the simplest topology to prove the proposed concept of this study. Nevertheless, it

Fig. 15. Probability density distribution of the estimated C and  $R_c$  of all obtained data from case 1 to case 7 (C1-C5 are described in Table.IV).

Fig. 16. Probability density distribution of the estimated  $R_{\text{avg}}$  of all obtained data from case 1 to case 7 (M1-M5 are described in Table.V).

represents the features of many other Buck-type converters and voltage-source inverters. Therefore, the applicability of the same concept for single-phase inverters and three-phase inverters can also be expected in the future. Even though, various challenges still need to be further solved.

### V. CONCLUSION

In this paper, a digital twin concept-based condition monitoring method is proposed and verified through a Buck converter case study. The experimental tests are performed to verify its feasibility and the results show that the digital twin of the Buck converter can achieve similar output waveforms (inductor current  $i_L$  and output voltage  $v_o$ ) with the physical Buck converter. Then, practical considerations are discussed (impact of sampling rate, different operation conditions, temperature and the uncertainty caused by errors). To avoid calibrating the relationship between the health indicator and their impact factors, a cluster-data based method is used in this paper. Finally, the capability of monitoring the degradation of key components (capacitor and MOSFET) in converter is

verified experimentally. When the capacitance is decreased by 2.2% for each step, the identified cluster of capacitances are able to indicate the degradation process. For MOSFET, the identified  $R_{\rm dson}$  cannot be used directly to indicate the degradation of MOSFET. To overcome this, a new equivalent resistance between  $R_{\rm L}$  and  $R_{\rm dson}$  are defined in this paper as  $R_{\text{avg}}$ . Similarly, by calculating a cluster of this new defined resistance, the increase of  $R_{\rm dson}$  can be identified. Finally, the probability density distribution-based data process method is used to achieve the characteristic value of each cluster-data which can be used as the final degradation level indicator. For implementation, three signals need to be measured from the physical Buck converter by using regular sensors: inductor current, output voltage and input voltage. In addition, dynamic waveforms are prerequisite for this method, which can be achieved from the load change events, input voltage change transient, start-up and shut-down transient.

In conclusion, the feasibility and effectiveness of the proposed method in monitoring the degradation level of capacitor and MOSFET are proved experimentally and practical issues are also considered. Compare to conventional methods, the proposed method provides a feasible and practical solution for condition monitoring of power converter with superiorities in non-invasive, calibration-free, and without additional hardware circuits.

#### REFERENCES

- S. Dusmez and B. Akin, "An accelerated thermal aging platform to monitor fault precursor on-state resistance," in 2015 IEEE International Electric Machines Drives Conference (IEMDC), May 2015, pp. 1352– 1358.

- [2] M. A. Vogelsberger, T. Wiesinger, and H. Ertl, "Life-cycle monitoring and voltage-managing unit for dc-link electrolytic capacitors in pwm converters," *IEEE Transactions on Power Electronics*, vol. 26, no. 2, pp. 493–503, Feb. 2011.

- [3] H. Oh, B. Han, P. McCluskey, C. Han, and B. D. Youn, "Physics-of-failure, condition monitoring, and prognostics of insulated gate bipolar transistor modules: A review," *IEEE Transactions on Power Electronics*, vol. 30, no. 5, pp. 2413–2426, May 2015.

- [4] S. Yang, D. Xiang, A. Bryant, P. Mawby, L. Ran, and P. Tavner, "Condition monitoring for device reliability in power electronic converters: A review," *IEEE Transactions on Power Electronics*, vol. 25, no. 11, pp. 2734–2752, Nov. 2010.

- [5] H. Soliman, H. Wang, and F. Blaabjerg, "A review of the condition monitoring of capacitors in power electronic converters," *IEEE Transactions* on *Industry Applications*, vol. 52, no. 6, pp. 4976–4989, Nov. 2016.

- [6] U. Choi, S. JÃ, rgensen, and F. Blaabjerg, "Advanced accelerated power cycling test for reliability investigation of power device modules," *IEEE Transactions on Power Electronics*, vol. 31, no. 12, pp. 8371–8386, Dec. 2016.

- [7] S. Beczkowski, P. Ghimre, A. R. de Vega, S. Munk-Nielsen, B. Rannestad, and P. Thogersen, "Online vce measurement method for wearout monitoring of high power igbt modules," in 2013 15th European Conference on Power Electronics and Applications (EPE), Sep. 2013, pp. 1–7.

- [8] B. Ji, X. Song, W. Cao, V. Pickert, Y. Hu, J. W. Mackersie, and G. Pierce, "In situ diagnostics and prognostics of solder fatigue in igbt modules for electric vehicle drives," *IEEE Transactions on Power Electronics*, vol. 30, no. 3, pp. 1535–1543, March 2015.

- [9] D. Astigarraga, F. M. Ibanez, A. Galarza, J. M. Echeverria, I. Unanue, P. Baraldi, and E. Zio, "Analysis of the results of accelerated aging tests in insulated gate bipolar transistors," *IEEE Transactions on Power Electronics*, vol. 31, no. 11, pp. 7953–7962, Nov. 2016.

- [10] X. Ye, C. Chen, Y. Wang, G. Zhai, and G. J. Vachtsevanos, "Online condition monitoring of power mosfet gate oxide degradation based on miller platform voltage," *IEEE Transactions on Power Electronics*, vol. 32, no. 6, pp. 4776–4784, Jun. 2017.

0885-8993 (c) 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Aalborg Universitetsbibliotek. Downloaded on July 21,2020 at 12:52:51 UTC from IEEE Xplore. Restrictions apply.

- [11] J. Liu, G. Zhang, Q. Chen, L. Qi, Y. Geng, and J. Wang, "In situcondition monitoring of igbts based on the miller plateau duration," *IEEE Transactions on Power Electronics*, vol. 34, no. 1, pp. 769–782, Jan. 2019.

- [12] C. H. van der Broeck, A. Gospodinov, and R. W. De Doncker, "Igbt junction temperature estimation via gate voltage plateau sensing," *IEEE Transactions on Industry Applications*, vol. 54, no. 5, pp. 4752–4763, Sep. 2018.

- [13] R. Mandeya, C. Chen, V. Pickert, and R. T. Naayagi, "Prethreshold voltage as a low-component count temperature sensitive electrical parameter without self-heating," *IEEE Transactions on Power Electronics*, vol. 33, no. 4, pp. 2787–2791, April 2018.

- [14] N. Baker, S. Munk-Nielsen, F. Iannuzzo, and M. Liserre, "Igbt junction temperature measurement via peak gate current," *IEEE Transactions on Power Electronics*, vol. 31, no. 5, pp. 3784–3793, May 2016.

- [15] H. Luo, Y. Chen, P. Sun, W. Li, and X. He, "Junction temperature extraction approach with turn-off delay time for high-voltage high-power igbt modules," *IEEE Transactions on Power Electronics*, vol. 31, no. 7, pp. 5122–5132, July 2016.

- [16] H. Niu and R. D. Lorenz, "Sensing power mosfet junction temperature using gate drive turn-on current transient properties," *IEEE Transactions* on *Industry Applications*, vol. 52, no. 2, pp. 1677–1687, March 2016.

- [17] Z. Wang, B. Tian, W. Qiao, and L. Qu, "Real-time aging monitoring for igbt modules using case temperature," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 2, pp. 1168–1178, Feb. 2016.

- [18] D. Xiang, L. Ran, P. Tavner, A. Bryant, S. Yang, and P. Mawby, "Monitoring solder fatigue in a power module using case-above-ambient temperature rise," *IEEE Transactions on Industry Applications*, vol. 47, no. 6, pp. 2578–2591, Nov. 2011.

- [19] W. Lai, M. Chen, L. Ran, O. Alatise, S. Xu, and P. Mawby, "Lowδt<sub>j</sub> stress cycle effect in igbt power module die-attach lifetime modeling," *IEEE Transactions on Power Electronics*, vol. 31, no. 9, pp. 6575–6585, Sep. 2016.

- [20] Y. Wu and X. Du, "A ven condition monitoring method of dc-link capacitors for power converters," *IEEE Transactions on Industrial Electronics*, vol. 66, no. 2, pp. 1296–1306, Feb. 2019.

- [21] N. Agarwal, M. W. Ahmad, and S. Anand, "Quasi-online technique for health monitoring of capacitor in single-phase solar inverter," *IEEE Transactions on Power Electronics*, vol. 33, no. 6, pp. 5283–5291, Jun. 2018.

- [22] A. Wechsler, B. C. Mecrow, D. J. Atkinson, J. W. Bennett, and M. Benarous, "Condition monitoring of dc-link capacitors in aerospace drives," *IEEE Transactions on Industry Applications*, vol. 48, no. 6, pp. 1866–1874, Nov. 2012.

- [23] Y. Jo, T. H. Nguyen, and D. Lee, "Condition monitoring of submodule capacitors in modular multilevel converters," in 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Sep. 2014, pp. 2121– 2126.

- [24] S. Dusmez, M. Bhardwaj, L. Sun, and B. Akin, "In situ condition monitoring of high-voltage discrete power mosfet in boost converter through software frequency response analysis," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 12, pp. 7693–7702, Dec. 2016.

- [25] D. Xiang, L. Ran, P. Tavner, S. Yang, A. Bryant, and P. Mawby, "Condition monitoring power module solder fatigue using inverter harmonic identification," *IEEE Transactions on Power Electronics*, vol. 27, no. 1, pp. 235–247, Jan. 2012.

- [26] A. Soualhi, M. Makdessi, R. German, F. R. EcheverrÃa, H. Razik, A. Sari, P. Venet, and G. Clerc, "Heath monitoring of capacitors and supercapacitors using the neo-fuzzy neural approach," *IEEE Transactions on Industrial Informatics*, vol. 14, no. 1, pp. 24–34, Jan. 2018.

- [27] H. Soliman, H. Wang, B. Gadalla, and F. Blaabjerg, "Condition monitoring for dc-link capacitors based on artificial neural network algorithm," in 2015 IEEE 5th International Conference on Power Engineering, Energy and Electrical Drives (POWERENG), May 2015, pp. 587–591.

- [28] M. Algreer, M. Armstrong, and D. Giaouris, "Active online system identification of switch mode dc-dc power converter based on efficient recursive dcd-iir adaptive filter," *IEEE Transactions on Power Electronics*, vol. 27, no. 11, pp. 4425–4435, Nov. 2012.

- [29] M. Ahmeid, M. Armstrong, S. Gadoue, M. Al-Greer, and P. Missailidis, "Real-time parameter estimation of dc-dc converters using a self-tuned kalman filter," *IEEE Transactions on Power Electronics*, vol. 32, no. 7, pp. 5666–5674, July 2017.

- [30] B. X. Li and K. S. Low, "Low sampling rate online parameters monitoring of dc-dc converters for predictive-maintenance using biogeographybased optimization," *IEEE Transactions on Power Electronics*, vol. 31, no. 4, pp. 2870–2879, April 2016.

[31] J. Poon, P. Jain, C. Spanos, S. K. Panda, and S. R. Sanders, "Fault prognosis for power electronics systems using adaptive parameter identification," *IEEE Transactions on Industry Applications*, vol. 53, no. 3, pp. 2862–2870, May 2017.

13

- [32] A. Alghassi, S. Perinpanayagam, M. Samie, and T. Sreenuch, "Computationally efficient, real-time, and embeddable prognostic techniques for power electronics," *IEEE Transactions on Power Electronics*, vol. 30, no. 5, pp. 2623–2634, May 2015.

- [33] S. H. Ali, M. Heydarzadeh, S. Dusmez, X. Li, A. S. Kamath, and B. Akin, "Lifetime estimation of discrete igbt devices based on gaussian process," *IEEE Transactions on Industry Applications*, vol. 54, no. 1, pp. 395–403, Jan. 2018.

- [34] Parrott Warshaw. (2017, Aug.) Α. and L. Industry 4.0 and the digital twin. [Online]. Available: https://www2.deloitte.com/content/dam/Deloitte/cn/Documents/ cip/deloitte-cn-cip-industry-4-0-digital-twin-technology-en-171215.pdf

- [35] O. white paper. (2017, Jan.) Digital twin for iot applications. [Online]. Available: http://www.oracle.com/us/solutions/internetofthings/ digital-twins-for-iot-apps-wp-3491953.pdf

- [36] M. Milton, C. A. De La O, H. L. Ginn, and A. Benigni, "Controllerembeddable probabilistic real-time digital twins for power electronic converter diagnostics," *IEEE Transactions on Power Electronics*, pp. 1– 1, 2020.

- [37] P. Jain, J. Poon, J. P. Singh, C. Spanos, S. R. Sanders, and S. K. Panda, "A digital twin approach for fault diagnosis in distributed photovoltaic systems," *IEEE Transactions on Power Electronics*, vol. 35, no. 1, pp. 940–956, 2020.

- [38] Y. Peng and H. Wang, "Application of digital twin concept in condition monitoring for dc-dc converters," in 2019 IEEE Energy Conversion Congress and Exposition (ECCE), Oct. 2019.

- [39] J. Hult, "A fourth order runge kutta in the interaction picture method for simulating supercontinuum generation in optical fibers," *Journal of Lightwave Technology*, vol. 25, no. 12, pp. 3770–3775, Dec. 2007.

- [40] J. W. Kimball and P. T. Krein, "A current-sensorless digital controller for active power factor correction control based on kalman filters," in 2008 Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition. IEEE, 2008, pp. 1328–1333.

- [41] P. Dash and R. Mallick, "Accurate tracking of harmonic signals in vschvdc systems using pso based unscented transformation," *International Journal of Electrical Power & Energy Systems*, vol. 33, no. 7, pp. 1315– 1325, 2011.

- [42] S. Bolognani, L. Tubiana, and M. Zigliotto, "Extended kalman filter tuning in sensorless pmsm drives," *IEEE Transactions on Industry Applications*, vol. 39, no. 6, pp. 1741–1747, 2003.

- [43] Z. Zhan, J. Zhang, Y. Li, and H. S. Chung, "Adaptive particle swarm optimization," *IEEE Transactions on Systems, Man, and Cybernetics, Part B (Cybernetics)*, vol. 39, no. 6, pp. 1362–1381, Dec. 2009.

- [44] W. Wang, A. C. Liu, H. S. Chung, R. W. Lau, J. Zhang, and A. W. Lo, "Fault diagnosis of photovoltaic panels using dynamic current-voltage characteristics," *IEEE Transactions on Power Electronics*, vol. 31, no. 2, pp. 1588–1599, Feb. 2016.

- [45] S. Dusmez, H. Duran, and B. Akin, "Remaining useful lifetime estimation for thermally stressed power mosfets based onon-state resistance variation," *IEEE Transactions on Industry Applications*, vol. 52, no. 3, pp. 2554–2563, May 2016.