Received September 16, 2018, accepted December 17, 2018, date of publication January 9, 2019, date of current version February 4, 2019. Digital Object Identifier 10.1109/ACCESS.2019.2891625

# A Family of Scalable Non-Isolated Interleaved DC-DC Boost Converters With Voltage Multiplier Cells

# AHMAD ALZAHRANI<sup>®1,2</sup>, (Student Member, IEEE), MEHDI FERDOWSI<sup>®1</sup>, (Member, IEEE), AND POURYA SHAMSI<sup>1</sup>, (Member, IEEE)

<sup>1</sup>Electrical Engineering Department, Missouri University of Science and Technology, Rolla, MO 65401, USA

<sup>2</sup>Electrical Engineering Department, Najran University, Najran, Saudi Arabia

Corresponding author: Ahmad Alzahrani (asakw9@mst.edu)

**ABSTRACT** In this paper, a family of non-isolated interleaved high-voltage-gain DC–DC converters is presented. This family can be used in a wide variety of applications, such as in a photovoltaic systems interface to a high voltage DC distribution bus in a microgrid and an X-ray system power supply. The general structure of this family is illustrated and consists of two stages: an interleaved boost stage and a voltage multiplier stage. The interleaved boost stage is a two-phase boost converter, and it converts the input DC voltage to an AC square waveform. Moreover, using the interleaved boost stage increases the frequency of the AC components so that it can be easily filtered with smaller capacitors and, therefore, makes the input current smoother than the one from the conventional boost converter. The voltage multiplier cell (VMC) can be a Dickson cell, Cockcroft–Walton (CW), or a combination of the two. The VMC stage rectifies the squareshaped voltage waveform coming from the interleaved boost stage and converts it to a high DC voltage. Several combinations of VMCs and how they can be extended are illustrated, and the difference between them is summarized so that designers can be able to select the appropriate topology for their applications. An example of this converter family is illustrated with detailed modes of operation, a steady-state analysis, and an efficiency analysis. The example converter was simulated to convert 20  $V_{DC}$  to 400  $V_{DC}$ , and a 200 W hardware prototype was implemented to verify the analysis and simulation. The results show that the example has a peak efficiency of 97% of this family of converters and can be very suitable for interfacing renewable energy sources to a 400  $V_{DC}$  DC distribution system.

**INDEX TERMS** Interleaved, boost, step-up, high-gain, DC-DC, renewable, microgrid, PV, DC distribution, VMC, modular.

### I. INTRODUCTION

The total power generation from renewable energy sources has been increasing rapidly and is predicted to increase threefold in the near future [1], [2]. The transition from using conventional and depletable energy sources in electricity generation to renewable and sustainable sources requires adaptable power infrastructure and high-efficiency power electronic converters. The power electronics play an indispensable role in renewable energy sources' integration to the main electric grid. Using highly efficient power converters could help customers save energy and therefore increase the economic benefits [3], [4]. The renewable energy market necessitates not only efficient, but also versatile and multipurpose, converters. Recently, the idea of integrating a low voltage PV panel to a 400 V DC distribution bus became a research interest due to the advantage of the DC distribution bus over AC. The DC distribution system has less conversion units and better efficiency, power quality, and performance than the AC distribution systems [5]–[9]. Integration of a single PV panel to a 400 V DC distribution system requires a high-gain DC-DC converter [10].

Several topologies found in the literature can be used as high-gain DC-DC converters [11]–[22]. However, there is no superior solution for all applications. The most common topology used to step up the input voltage is the conventional boost converter, which is the most straightforward step-up converter [23]. However, the conventional boost converter would not have enough voltage gain for integrating renewable energy sources to a 400 V, but if it were to have enough voltage gain, it would be only when operating at a higher

duty cycle, which might lead to the appearance of reverse recovery phenomena and low overall efficiency, especially if the inductor DC equivalent resistance is high. Moreover, the required inductance to stay in the continuous conduction mode is very large, and therefore, the converter requires large and bulky magnetics [24], [25].

Cascaded boost converters were introduced to replace the conventional boost converter. Such solutions increase the overall voltage gain and allow each converter to operate at a lower duty cycle [26]. However, cascading two or more converters at least doubles the power being processed, and that might compromise the efficiency as well. Moreover, controlling cascaded converters requires that the output impedance of a converter be lower than the input impedance of the following converter to ensure stability [27]. That might lead to complications in the design and control. Stacking two or more converters helps by sharing the power among different converters and allows the use of lower current rating devices [28]. However, the overall voltage gain is still the same as the voltage gain of the conventional boost converter.

Several converters can achieve higher voltage by incorporating either coupled inductors or transformers [29], [30]. Such topologies increase the voltage gain by increasing the turn ratio. However, several issues can arise. First, the leakage inductance can cause some voltage spikes across switching devices, and that might require some voltage clamp circuits. Second, incorporating such devices reduces the power density of the converter and increases the weight. Furthermore, the semiconductor materials will improve rapidly, while magnetic materials will not. Therefore, with the increase of switching frequency, the magnetic-based components might become the most significant culprits for power loss inside the converter. Thus, this paper introduces a family of converters that can have a high-voltage-gain ratio, continuous current, low stress across both active and passive devices, and high power density. The proposed family consists of two stages: an interleaved boost stage and voltage multiplier cells. The interleaved boost stage reduces the variation of the input current so that it is easy to obtain more accurate measurements of the PV current to track the maximum power. The voltage multiplier cells increase the voltage gain and reduce the voltage stresses across switching devices. Moreover, the converter can achieve a high-voltage-gain ratio while operating at a lower duty cycle. The proposed family requires the lower value of critical inductance to keep the converter operating in the continuous conduction mode (CCM). The rest of the paper is structured as follows: Section II provides the theory of operation and the general structure of the proposed family. Section III presents different variations of the converter belonging to the proposed family. In Section IV, an example of the proposed converter is given and analyzed. In Section V and VI, the simulation and experimental results of the example converter are provided, respectively. Finally, conclusions and future work are described in Section VII.

# II. THEORY OF OPERATION AND GENERAL STRUCTURE OF THE PROPOSED FAMILY

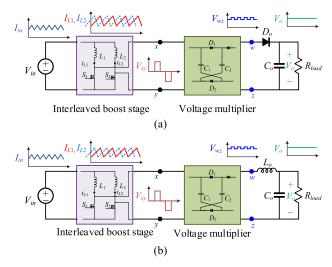

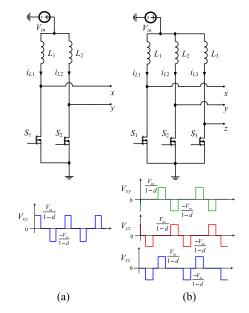

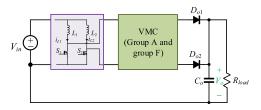

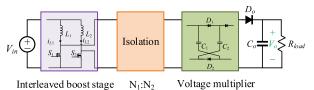

The general structure of the proposed family is shown in Fig. 1, which consists of an interleaved boost stage followed by a voltage multiplier cell, and then it is either filtered using an output diode and capacitor capacitor as in Fig. 1(a) or using an LC filter as shown in Fig. 1(b). By using an output diode and a capacitor filter, the output of VMC is further increased by  $\frac{1}{1-d}$  but the output current is discontinuous. On the contrary, when using an LC filter, the output voltage of the VMC is not increased, but the output current is continuous if the inductor is large enough to operate in the CCM mode. Several papers present members belonging to the proposed family [31]–[37]. However, no information about extending the VMC cells or the interleaved boost phases has been reported. The following sections present details about each stage of the proposed family.

FIGURE 1. General structure of the proposed family: (a) with output diode and capacitor (b) with LC filter output.

#### A. INTERLEAVED BOOST STAGE

The IBC stage consists of two or more phases. Each phase consists of an inductor and a low-side active switch. Since the IBC stage is a current source, the active switches can be closed simultaneously with no need for a dead time insertion circuit as in the voltage-fed converters. A phase shift between the active switches is vital to reduce the current ripples from the input current and therefore reduce the size of the input filter. A recommended phase shift between active switches can be given by

$$Shift \ge \frac{360^{\circ}}{\phi} \tag{1}$$

where  $\phi$  is the number of interleaved phases, which is a positive integer greater than or equal to two. To ensure the continuity of the input current and to prevent a voltagesecond imbalance in the inductors, the minimum duty cycle is given by

$$D \ge \frac{\phi - 1}{\phi}.$$

(2)

Besides reducing the current ripples, the interleaved boost stage reduces the magnetic storage. In the case of two-phase, and assuming the inductors share the input current equally, the reduction in the magnetic element is half as follows:

$$\frac{E_2}{E_1} = \frac{\frac{1}{2}L\left(\frac{I}{2}\right)^2 + \frac{1}{2}L\left(\frac{I}{2}\right)^2}{\frac{1}{2}LI^2} \times 100 = 50\%.$$

(3)

The reduction for  $E_{\phi}$  is given by  $\kappa$  as

....

$$\kappa(\%) = (1 - \frac{1}{\phi}) \times 100.$$

(4)

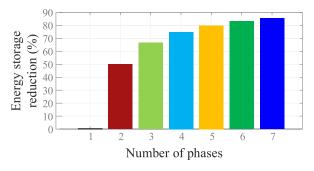

Figure 2 shows the percentage of the reduction of a different number of phases. The reduction becomes insignificant as the number of phases increases. The reduction of the magnetic volume  $\zeta$  does not follow (4) as illustrated in [38]. Instead, one should compare the volume reduction as follows:

$$\zeta = \frac{Volume_{n=1} - \phi Volume_{n=\phi}}{Volume_{n=1}} \times 100$$

(5)

FIGURE 2. Reduction of energy storage at multiple phases. In case of two phases, the required energy storage is reduced by 50%.

where  $Volume_{n=1}$  is the volume of the magnetic element in a single phase converter and  $Volume_{n=\phi}$  is the volume of the magnetic element of a multiphase converter with  $\phi$  phases. Another advantage of interleaving is that the total conduction loss in the inductors and the active switching devices is reduced if the current is shared equally between the phases as follows:

$$P_{L_{total}} = \frac{I_L^2 \times R_{DC}}{\phi},\tag{6}$$

$$P_{S,cond_{total}} = \frac{I_{S,rms}^2 \times R_{ON}}{\phi}.$$

(7)

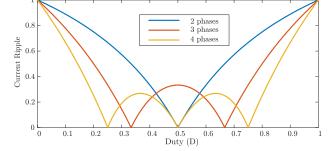

The input current ripples depend on the number of interleaved phases and the duty cycle. Figure 3 shows the relationship between the number of stages and the normalized input ripples. Increasing the number of phases reduces the ripples and allows ripple cancellation to occur at multiple duty cycle values. Two phases can have one point of ripple cancellation

FIGURE 3. The normalized current ripples with respect to a single phase boost converter.

at the 0.5 duty cycle; while in three phases the ripple cancellation occurs at two points: the 0.25 and 0.75 duty cycles. For more phases, the duty cycle values where ripple cancellation can occur are given by

$$d_{\Delta\nu=0} = \left[\frac{1}{\phi}, \frac{2}{\phi}, ..., \frac{\phi - 1}{\phi}\right]$$

(8)

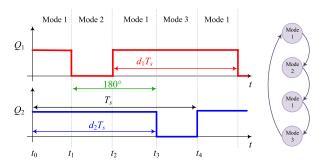

Figures 4(a) and (b) show the schematic and output waveforms of the interleaved boost stage for two and three phases, respectively. The switching waveforms and modes of operations are shown in Fig. 5 for two phases and Fig. 6 for three phases. More phases can be used, such as in [39], but three or more phases will not have a uniform pattern of connections to the VMC, and the permutation of variation of the topologies is large. Therefore, the number of phases is limited to two in this paper.

FIGURE 4. Interleaved boost stage with output waveforms: (a) two phases (b) three phases.

# **B. VOLTAGE MULTIPLIER STAGE**

The voltage multiplier stage rectifies the modified squared waveform that comes from the interleaved boost stage and

**FIGURE 5.** The switching pattern for the two-phase interleaved boost converter. The active switches are driven by two out of phase signals, and the converter operates in three modes of operation in the CCM.

FIGURE 6. The switching pattern for a three-phase interleaved boost converter. The converter is driven by three signals with a phase shift of 120°, and the converter operates at four modes of operation in the CCM.

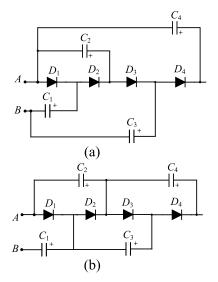

FIGURE 7. Two main voltage multiplier cells: (a) Dickson VMC (b) Cockcroft-Walton VMC.

boosts the voltage to a higher level. The VMC stage consists of capacitors and diodes. The two main extendable VMCs are the Dickson VMC and Cockcroft-Walton VMC, as shown in Fig. 7. The main difference between these VMCs is the way capacitors are connected. In the Dickson VMC, all negative sides of the even capacitors are connected to phase a, and all negative sides of the odd capacitors are connected to phase b. In the Cockcroft-Walton VMC, each negative side of the odd capacitor is connected to the positive side of the previous odd capacitor, and each negative side of the even capacitor is connected to the positive side of the previous even capacitor. Various combinations are derived out of these two VMCs, as in [40]–[45].

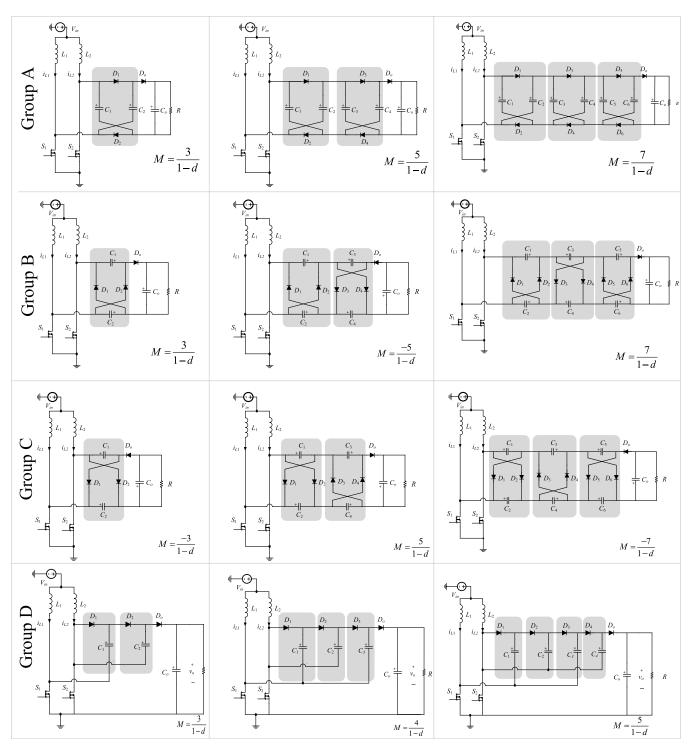

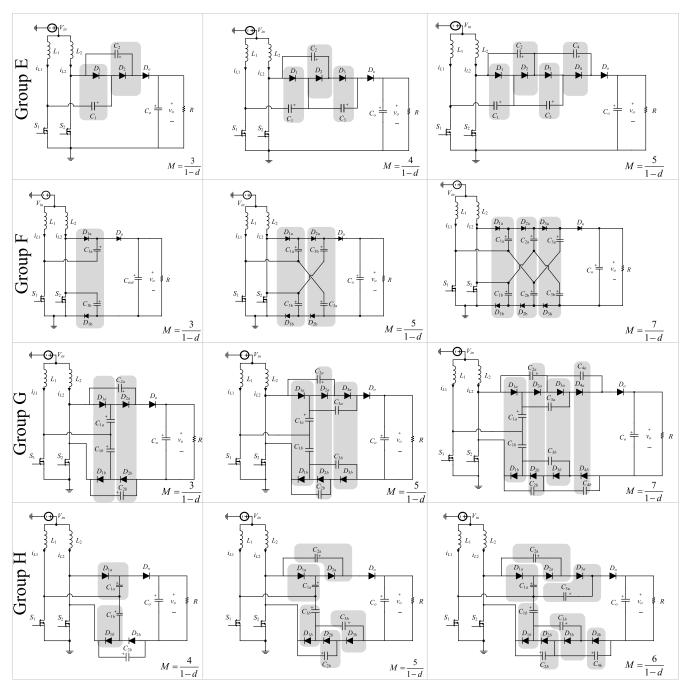

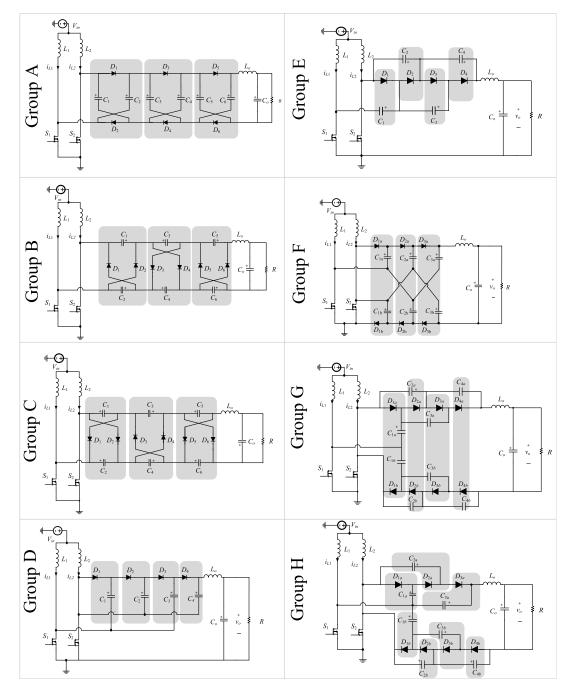

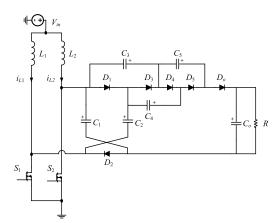

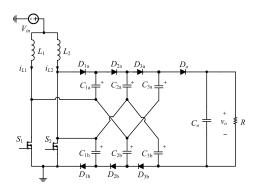

## C. TOPOLOGIES OF A TWO-PHASE INTERLEAVED BOOST CONVERTER WITH VMCS

Figures 8 and 9 show different interleaved boost converters with different VMCs and a diode capacitor filter. Figure 10 shows the same groups, but with an LC output filter instead of a diode-capacitor filter. Group A uses cross capacitor VMC cells. This group is analyzed in [46]. Group B and C have cross diode VMC cells, and similar work is presented in [47]. The cells can start in the inverting cells, as in group B, or noninverting VMC stage, as in group C. To extend the VMC in these two groups, each cell must be followed by a cell with the opposite polarity. For example, the first stage in group B is positive (the diodes are upward), so it must be followed by a negative cell (diodes are downward), and vice versa. The polarity of the output voltage depends on the polarity of the last cell. Group D has Dickson VMC [10], and group E consists of Cockcroft-Walton [48]. Group F contains the example converter and will be analyzed in this paper. Group G has two CW chains, and it can have either the same or a different number of cells on each chain. Finally, Group H uses Dickson cells on one phase and Cockcroft-walton VMC on the other phase with either the same or a different number VMC stages. Several interleaved boost converters with VMCs belonging to this family can be found in the literature such as [49], where the Dickson VMC is modified to have lower voltage stress across capacitors without changing the overall voltage gain.

The main difference between these groups is how internal capacitors are charged and discharged. Some other differences including the load connection type (floating, inverted, or grounded), the stress on the capacitors and diodes, and the number of components in each VMC stage. The VMC structure affects the sharing of the input current between phases in the interleaved boost stage. That is, in converters that have an output diode, if there is a single diode in each stage, then the current sharing can be equal if the number of stages is even. However, if there is an output diode and each stage of the VMC has two diodes, then there will never be equal current sharing between the inductors. In converters where an LC filter is used, there will not be equal current sharing between phases. Table 2 summarizes the differences between the VMCs and illustrates this.

#### D. POSSIBLE MODIFICATIONS TO THE TOPOLOGIES

The presented family can be modified to obtain specific features such as isolation, where a transformer can be inserted between the interleaved boost stage and the VMC stage, or to convert a topology with a floating output to a grounded output.

FIGURE 8. Various topologies belong to the interleaved boost converter with voltage multiplier cells (group A-D). The output is filtered using an output diode and a capacitor filter.

# 1) CONVERT A FLOATING OUTPUT CONVERTER TO GROUNDED OUTPUT

Groups A and F have a floating output, where the output has a different reference point than the input. In voltage control mode, a differential sensor is required for the feedback loop. Designers can convert floating outputs to grounded outputs by adding a diode to the VMC, and connecting the output to the ground, as shown in Fig. 11. Although the voltage stress across the components in the grounded output converter are still the same as the ones in the floating output converter, the voltage gain is significantly reduced. Figure 12 shows group A and F with the grounded output.

FIGURE 9. Various topologies belong to the interleaved boost converter with voltage multiplier cells (group A-H): with an output diode and a capacitor filter.

# 2) MODIFICATION TO MAKE THE CONVERTER ISOLATED.

This family can easily be a family of isolated converters by adding a transformer or coupled inductors between the interleaved boost stage and the VMC stage, as shown in Fig. 13. After adding the isolation device with an  $N_1 : N_2$  turns ratio, the voltage gain can be calculated as

$$M_{isolated} = M_{nonisolated} \times \frac{N_2}{N_1} \tag{9}$$

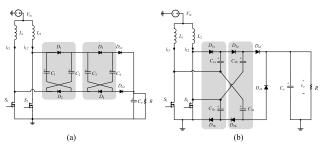

# 3) CONNECTING TWO DIFFERENT VMCS TO OBTAIN THE OVERALL NONUNIFORM CONVERTER.

Extra possible combinations of different voltage multiplier cells can be derived, e.g., but will be unable to expand one or both VMCs. The analysis of nonuniform converters is performed on a case by case basis. Figure 14 shows an example of nonuniform combinations. The converter consists of one cell from group F followed by Cockcroft-Walton cells.

FIGURE 10. Using an output LC filter instead of a diode-capacitor for the same groups aforementioned.

# III. MODES OF OPERATION AND STEADY-STATE ANALYSIS OF AN EXAMPLE CONVERTER

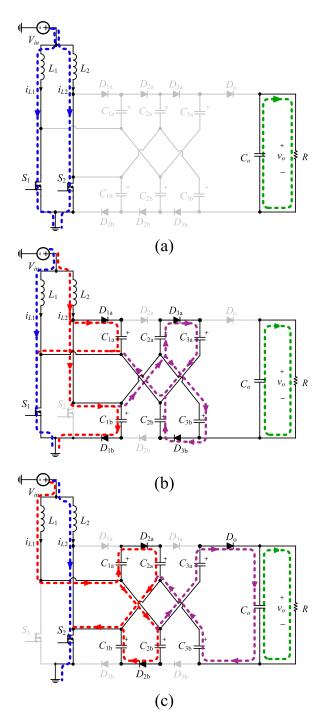

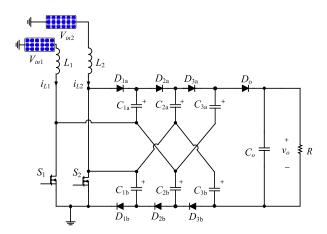

This section presents a detailed analysis of the circuit, shown in Fig. 15. The converter is driven by two 180° out phase signals, as shown in Fig. 6. The equivalent circuit of the three modes is shown in Fig. 16 (a-c). The analysis was performed with several assumptions: 1) All components are ideal; 2) The capacitors are large enough that ripples can be neglected; 3) The converter is operating in the steady-state condition; 4) The duty cycles of the active switches are symmetrical; and 5) The converter is fed by a single voltage source.

#### A. MODE 1: BOTH MOSFETS ARE ON

In this mode, both inductors draw energy from the source, and all diodes are in reverse biased mode. The voltage across the inductors is given by

$$v_{L_1} = v_{L_2} = V_{in}.$$

(10)

## B. MODE 2: S<sub>1</sub> IS ON AND S<sub>2</sub> IS OFF

In this mode  $L_1$  still draws energy from the source,  $L_2$  discharges into the VMC capacitors, and all diodes are in reverse biased mode. The voltage across the inductors is

TABLE 1. Comparison of different interleaved DC-DC converters.

|       |                     |                              |                              | With output diode and capacitor filter (Figs. 8 and 9)                                                                                                            |                                                                                            | With $LC$ filter (Fig. 10)                                                                              |                                                                                                                                                                                                                                                                           |

|-------|---------------------|------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Group | Output              | Diodes/stage                 | Caps/stage                   | Ideal voltage gain                                                                                                                                                | $\frac{\langle I_{L_1} \rangle}{\langle I_{L_2} \rangle}$                                  | Ideal voltage gain                                                                                      | $rac{\langle I_{L_1} \rangle}{\langle I_{L_2} \rangle}$                                                                                                                                                                                                                  |

| A     | Floating            | 2                            | 2                            | $\frac{2N+1}{1-d}$                                                                                                                                                | $\frac{N}{N+1}$                                                                            | $\frac{2N}{1-d}$                                                                                        | $\begin{cases} \frac{N-1+d}{N+1-d} & N \ even \\ \frac{N-d}{N+d} & N \ odd \end{cases}$                                                                                                                                                                                   |

| В     | Floating/ inverting | 2                            | 2                            | $\begin{cases} \frac{-(2N+1)}{1-d} & N \ even \\ \frac{2N+1}{1-d} & N \ odd \end{cases}$                                                                          | $\frac{N+1}{N}$                                                                            | $\left\{\begin{array}{c} \frac{-(2N)}{1-d} & N \ even\\ \\ \frac{2N}{1-d} & N \ odd \end{array}\right.$ | $\begin{cases} \frac{N+1-d}{N-1+d} & N \ even \\ \frac{N+d}{N-d} & N \ odd \end{cases}$                                                                                                                                                                                   |

| С     | Floating/ inverting | 2                            | 2                            | $\begin{cases} \frac{-(2N+1)}{1-d} N \ odd \\ \frac{2N+1}{1-d} N \ even \end{cases}$                                                                              | $\frac{N}{N+1}$                                                                            | $\left\{\begin{array}{c} \frac{-(2N)}{1-d} & N \ odd \\ \frac{2N}{1-d} & N \ even \end{array}\right.$   | $\begin{cases} \frac{N-d}{N+d} & N \text{ odd} \\ \frac{N+d-1}{N+1-d} & N \text{ even} \end{cases}$                                                                                                                                                                       |

| D     | Grounded            | 1                            | 1                            | $\frac{N+1}{1-d}$                                                                                                                                                 | $\left\{ \begin{array}{ll} \frac{N}{N+2} & N \ even \\ \\ 1 & N \ odd \end{array} \right.$ | $\frac{N+1-d}{1-d}$                                                                                     | $\left\{\begin{array}{cc} \frac{N+1-2d}{N+1} & N \ odd\\ \frac{N}{N+2(1-d)} & N \ even \end{array}\right.$                                                                                                                                                                |

| Е     | Grounded            | 1                            | 1                            | $\frac{N\pm 1}{1-d}$                                                                                                                                              | $\left\{ \begin{array}{ll} \frac{N}{N+2} & N \ even \\ \\ 1 & N \ odd \end{array} \right.$ | $\frac{N+1-d}{1-d}$                                                                                     | $\left\{\begin{array}{ll} \frac{N+1-2d}{N+1} & N \ odd\\ \frac{N}{N+2(1-d)} & N \ even \end{array}\right.$                                                                                                                                                                |

| F     | Floating            | 2                            | 2                            | $\frac{2N+1}{1-d}$                                                                                                                                                | $\frac{N}{N+1}$                                                                            | $\frac{2N}{1-d}$                                                                                        | $\frac{N+d}{N-d}$                                                                                                                                                                                                                                                         |

| G     | Floating            | 2                            | 2                            | $\frac{2N+1}{1-d}$                                                                                                                                                | $\frac{N}{N+1}$                                                                            | $\frac{2N}{1-d}$                                                                                        | $\frac{N+d}{N-d}$                                                                                                                                                                                                                                                         |

| Н     | Floating            | $1/VMC_{dn}$<br>$1/VMC_{dn}$ | $1/VMC_{dn}$<br>$1/VMC_{dn}$ | $\left\{ \begin{array}{ll} \frac{2 \max(N_{up},N_{dn})}{1-d} & N_{up} + N_{dn} \ odd \\ \frac{N_{up} + N_{dn}}{1-d} & N_{up} + N_{dn} \ even \end{array} \right.$ | 1                                                                                          | $\frac{N_{up} + N_{dn}}{1 - d}$                                                                         | $ \left\{ \begin{array}{cccc} 1 & N_{up} + N_{dn} & even \\ \\ \left\{ \begin{array}{cccc} \frac{N_{up} - (1-d)}{N_{dn} + (1-d)} & N_{up} > N_{dn} \\ & N_{up} + N_{dn} & odd \\ \\ \frac{N_{up} + (1-d)}{N_{dn} - (1-d)} & N_{up} < N_{dn} \end{array} \right. \right. $ |

# TABLE 2. Output voltage at different cases of the input current and duty cycles.

| Case                                        | the output voltage                                      |

|---------------------------------------------|---------------------------------------------------------|

| $d_1 \neq d_2$ and $V_{in_1} \neq V_{in_2}$ | $\frac{NV_{in_1}}{1-d_1} + \frac{(N+1)V_{in_2}}{1-d_2}$ |

| $d_1 \neq d_2$ and $V_{in_1} = V_{in_2}$    | $V_{in}(\frac{N}{1-d_1} + \frac{(N+1)}{1-d_2})$         |

| $d_1 = d_2$ and $V_{in_1} \neq V_{in_2}$    | $\frac{1}{1-d}(NV_{in_1} + (N+1)V_{in_2})$              |

| $d_1 = d_2$ and $V_{in_1} = V_{in_2}$       | $\tfrac{(2N+1)V_{in}}{1-d}$                             |

**FIGURE 11.** Modification to convert a floating output converter to a grounded output converter.

given by

$$= V_{in} + V_{C_{2a}} - V_{C_{3a}} = V_{in} + V_{C_{2b}} - V_{C_{3b}}.$$

(12)

**FIGURE 12.** Group A and F can be converted to have a grounded output. Both have an ideal voltage gain of  $M = \frac{N+1}{1-d}$ , which is  $\frac{N}{1-d}$  less than the ones with floating outputs.

FIGURE 13. The presented family can be modified by adding an isolation

# device to meet the isolation requirement and improve the voltage gain.

# C. MODE 3: S<sub>1</sub> IS OFF AND S<sub>2</sub> IS ON

In this mode  $L_1$  discharges into the VMC capacitors,  $L_2$  draws energy from the source, and all diodes are in reverse biased mode. The voltage across the inductors is given by

$$v_{L_1} = V_{in} + V_{C_{1a}} - V_{C_{2a}} = V_{in} + V_{C_{1b}} - V_{C_{2b}}$$

=  $V_{in} + V_{C_{3a}} + V_{C_{3b}} - V_o$ , (13)

$$v_{L_2} = V_{in}.$$

(14)

**FIGURE 14.** Example of nonuniform topologies. The converter features two different types of VMCs, a cell from group F and Cockcroft-Walton VMC.

FIGURE 15. Example converter; an interleaved boost stage with a 3 level VMC.

### D. STEADY-STATE VOLTAGE GAIN

Steady state equations can be derived from the state equations by a voltage-second balance on the inductors. The average voltage across the inductors is given by

$$\left\langle v_{L_1} \right\rangle = \left\langle v_{L_2} \right\rangle = 0 \tag{15}$$

The voltage across each first-stage capacitor is given by

$$V_{C_{1a}} = V_{C_{1b}} = \frac{V_{in}}{1 - D}.$$

(16)

The voltage of each second-stage capacitor is given by

$$V_{C_{2a}} = V_{C_{2b}} = \frac{2V_{in}}{1 - D}.$$

(17)

Each third-stage capacitor's voltage is given by

$$V_{C_{3a}} = V_{C_{3b}} = \frac{3V_{in}}{1-D}.$$

(18)

Therefore, the output voltage transfer function is given by

$$M = \frac{V_o}{V_{in}} = \frac{7}{1 - D}.$$

(19)

For N number of VMC stages, the transfer function is given by

$$M = \frac{2N+1}{1-D}.$$

(20)

FIGURE 16. Modes of operation of the example converter; (a) mode 1 (b) mode 2 (c) mode 3.

The previous analysis was for a converter that is being fed by a single source, and equal duty cycles were assumed. The proposed converter is capable of being fed by two independent voltage sources, e.g., different PV panels, as shown in Fig. 17. Also, it can operate at different duty ratios, which is suitable for tracking the maximum power point for each PV panel. The table 2 summarizes the voltage gain in cases with two different sources and asymmetrical duty cycles.

FIGURE 17. The example converter can convert the voltage from two independent power sources.

# IV. COMPONENT SELECTIONS AND EFFICIENCY ANALYSIS

This section presents details about the design and component selections of the example converter.

### A. INDUCTOR SELECTION

The critical inductance that ensures CCM operation is given by

$$L_{1_{crit}} = \frac{Rd(1-d)^2}{N(2N+1)f_s},$$

(21)

$$L_{2_{crit}} = \frac{Rd(1-d)^2}{(N+1)(2N+1)f_s}.$$

(22)

However, to select an inductor based on the percentage of the ripple, one should follow

$$L_1 = \frac{V_{in}d}{\Delta i_{L_1}f_s},\tag{23}$$

$$L_2 = \frac{V_{in}d}{\Delta i_{L_3}f_s}.$$

(24)

The average current passing through inductors  $L_1$  and  $L_2$  is as follows:

$$I_{L_{1,avg}} = \frac{V_o}{R} \frac{N}{(1-d)},$$

(25)

$$I_{L_{2,avg}} = \frac{V_o}{R} \frac{N+1}{(1-d)}.$$

(26)

The peak currents can be calculated as follows:

$$I_{L_{1,pk}} = \frac{V_o}{R} \frac{N}{(1-d)} + \frac{dV_{in}}{Lf_s},$$

(27)

$$I_{L_{2,pk}} = \frac{V_o}{R} \frac{N+1}{(1-d)} + \frac{dV_{in}}{Lf_s}.$$

(28)

The RMS currents are given by

$$I_{L_{1,rms}} = \sqrt{\left(\frac{V_o N}{R(1-d)}\right)^2 + \left(\frac{dV_{in}}{2\sqrt{3}Lf_s}\right)^2},$$

(29)

$$I_{L_{2,rms}} = \sqrt{\left(\frac{V_o(N+1)}{R(1-d)}\right)^2 + \left(\frac{dV_{in}}{2\sqrt{3}Lf_s}\right)^2}.$$

(30)

### **B. ACTIVE SWITCHES SELECTION**

The voltage stress across MOSFETs can be calculated by

$$V_{S_1} = V_{S_2} = \frac{V_{in}}{1 - d} \tag{31}$$

and the average current passing through the MOSFETs is given by

$$I_{S_{1,avg}} = \frac{V_o}{R} \left( \frac{dN}{1-d} + N + 1 \right), \tag{32}$$

$$I_{S_{2,avg}} = \frac{V_o}{R} \left( \frac{d(N+1)}{1-d} + N \right).$$

(33)

The maximum input current passing through the MOSFETs is given by

$$I_{S_{1,pk}} = I_{S_{2,pk}} = \frac{V_o(2N+1)}{R(1-d)} + \frac{V_{in}(2d-1)}{Lf_s}.$$

(34)

The root mean square value of the switch current is given by

$I_{S_{1rms}}$

$$=\sqrt{\left(\frac{V_o}{R}\left(\frac{dN}{1-d}+N+1\right)\right)^2 + \left(\frac{(2N+1)V_{in}(2d-1)}{2Lf_s}\right)^2},$$

(35)

$I_{S_{2,rms}}$

$$= \sqrt{\left(\frac{V_o}{R}\left(\frac{d(N+1)}{1-d} + N\right)\right)^2 + \left(\frac{(2N+1)V_{in}(2d-1)}{2Lf_s}\right)^2}.$$

(36)

### C. DIODE SELECTION

The voltage stress across the diodes is a function of the number of stages. The voltage stress is reduced as the number of stages increases, and that comes at the cost of efficiency. The voltage stress is given by

$$V_D = \frac{2V_o}{(2N+1)}.$$

(37)

The average current passing through each diode can be calculated by

$$I_{D_N,avg} = I_o \tag{38}$$

and the RMS value of the diodes can be calculated as

$$I_{D,rms} = I_o \sqrt{\frac{1}{1-d}}.$$

(39)

#### D. CAPACITOR SELECTION

The capacitor is selected based on the tolerated voltage ripple, and it can be calculated using the following equation

$$C = \frac{I_o(1-d)}{f\,\Delta v}.\tag{40}$$

The RMS value of the current passing through the output capacitor is given by

$$I_{C_{o,rms}} = I_o \sqrt{\frac{d}{(1-d)}} \tag{41}$$

and the RMS current of the other capacitors can be calculated by

# $I_{C_{n,rms}} = I_o(1 + \sqrt{\frac{d}{(1-d)}})$ (42)

# V. POWER LOSSES AND EFFICIENCY ANALYSIS

The power losses in the inductors are given by

$$P_L = I_{L_{1,rms}}^2 DCR_1 + I_{L_{2,rms}}^2 DCR_2$$

(43)

where  $DCR_1$  and  $DCR_2$  are the DC resistance.

The power losses in the active switches can be divided into two parts: switching loss and conduction loss. The switching loss can be calculated using the following equation:

$$P_{SW} = 2(\frac{1}{2} \times I_{L,avg} \times V_S \times (t_{OFF} + t_{ON})f_s + \frac{1}{2} \times f_s \times C_{oss} \times V_S^2).$$

(44)

The conduction loss part is given by

$$P_{S,conduction} = I_{s_{1,rms}}^2 R_1(on) + I_{S_{2,rms}}^2 R_2(on)$$

(45)

where  $R_1(on)$  and  $R_2(on)$  are the drain-source resistance of  $S_1$  and  $S_2$ . The power loss in the diodes can be calculated by

$$P_D = \sum_{i=1}^{N} I_{D_{avg}} \times V_F + \sum_{i=1}^{N} I_{D_{rms}} \times r_f$$

(46)

where  $V_F$  is the forward voltage of the diode, and  $r_f$  is the bulk resisor. The power loss in the capacitors due to the equivalent series resistance (ESR) is given by

$$P_{C,total} = NI_{C_{n,rms}}^2 ESR_n + I_{C_{o,rms}}^2 ESR_o.$$

(47)

The total loss is given by

$P_{loss} = P_{D,total} + P_{C,total} + P_{S,conduction} + P_{SW} + P_L \quad (48)$

The overall efficiency of the converter is given by

$$\eta\% = \frac{P_o}{P_{loss} + P_o} \times 100. \tag{49}$$

#### **VI. SIMULATION**

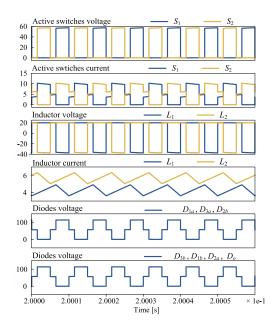

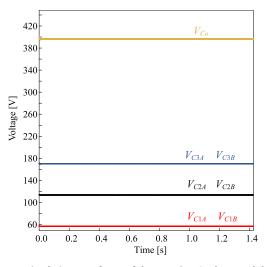

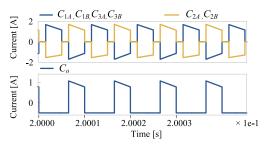

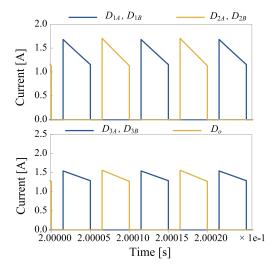

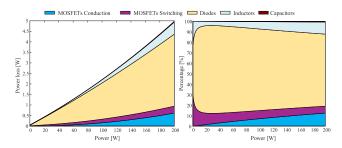

The example converter was simulated in PLECS/MATLAB, with a maximum time step of  $10^{-7}$  s and tolerance of  $10^{-3}$ . The parameters used in the simulation are listed in Table 3. The major waveforms are plotted in Fig. 18. The voltage stress across the active switches is 57 V. The average current on  $L_1$  and  $L_2$  is 4.28 A and 5.7 A, respectively. The maximum voltage across the diodes is 114 V. The average and effective values of the current passing through each diode are 0.5 A and 0.84 A. The voltage across the capacitors is shown in Fig. 19. The currents passing through the diodes and capacitors are shown in Fig. 20 and Fig. 21, respectively. The first-stage capacitors  $C_{1A}$  and  $C_{1B}$  have a voltage of 57 V, the secondstage capacitors have a voltage of 114 V, and the third-stage capacitors have a voltage of 171 V. The RMS current of the output capacitor is 0.68 A, while the other capacitors

#### TABLE 3. List of Parameters used in simulation.

| Parameter           | Value         |

|---------------------|---------------|

| Input voltage       | 20 V          |

| Output voltage      | $400\;V$      |

| Load resistance     | $800~\Omega$  |

| Ideal duty cycle    | 0.65          |

| Switching frequency | $100 \; kHz$  |

| Inductors           | $100 \ \mu H$ |

| Capacitors          | $10 \ \mu F$  |

FIGURE 18. Simulation waveforms of voltages and currents across semiconductor switches and inductors.

have an RMS current of 1.18 *A*. The efficiency analysis was performed using the loss equations of the components and the rating from the datasheets of the components used for implementing the hardware prototype. The approximate loss breakdown and breakdown percentage as a function of the output load is depicted in Fig. 22. The total loss at 200 *W* is about 4.98 *W*. The major source of loss is the conduction loss in the diodes, which counts for about 68%. The conduction loss is about 7% of the total loss. The conduction loss in the inductors counts for about 11%, and the total loss caused by the ESR of the capacitors is less than 1%.

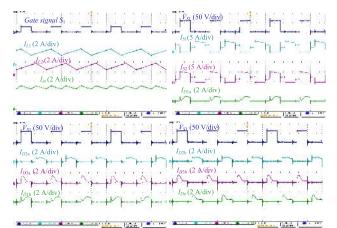

#### **VII. EXPERIMENTAL IMPLEMENTATION AND RESULTS**

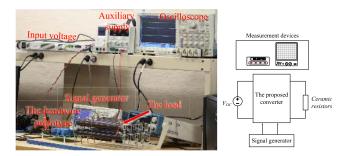

A 200 *W* hardware prototype was implemented and tested to further verify the operation of the example converter. The components used to construct the hardware prototype are listed in Table 4, and the experimental setup is shown in Fig. 23. The converter was designed for a nominal duty cycle of 0.65 and increased to roughly 0.657 to compensate for the gain reduction caused by the diodes' forward voltage

**FIGURE 19.** Simulation waveforms of the capacitors' voltage and the output voltage in the steady-state.

FIGURE 20. Simulation of the capacitors' currents.

FIGURE 21. Simulation waveforms of the diodes' currents.

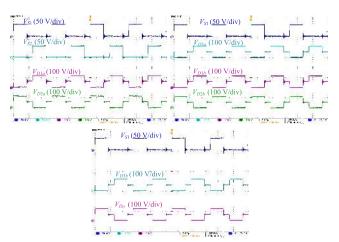

and losses in wires. The AFG3052C signal generator was used to generate gate signals with a switching frequency of 50 kHz. The converter is fed by 20 V, where N5700 power supply is used, and the output load is implemented using ceramic resistors with various values. The voltage stress across the active switches and diodes are shown in Fig. 24, which supports the simulation results as the voltage across

**FIGURE 22.** Efficiency analysis of the example converter; the actual losses (left) and the loss breakdown (right).

| TABLE 4. Lis | st of Com | ponents used | d for the | hardware | prototype. |

|--------------|-----------|--------------|-----------|----------|------------|

|--------------|-----------|--------------|-----------|----------|------------|

| Item      | Designation                                      | Rating                                                  | Part No.                                    |

|-----------|--------------------------------------------------|---------------------------------------------------------|---------------------------------------------|

| Inductor  | $L_{1}, L_{2}$                                   | $100 \ \mu H, DCR = 25 \ m\Omega,$                      | 60B104C                                     |

| Capacitor | $C_{1A}, C_{2A} \\ C_{1B}C_{2B} \\ C_{3A}C_{3B}$ | $10~\mu\mathrm{F}$                                      | B32674D3106K                                |

| Capacitor | $C_o$                                            | $22 \ \mu F$                                            | B32774D4226K000                             |

| MOSFET    | $Q_1, Q_2$                                       | $\frac{150 \ V, 37 \ A}{R_{ds(on)} = 10.525 \ m\Omega}$ | IPA105N15N3                                 |

| Diode     | $D_{1A}, D_{2A} \\ D_{1B}, D_{2B}$               | 250V, 40A<br>$V_F = 0.86 V, t_{rr} = 35 ns$             | MBR40250G                                   |

| load      | $R_{load}$                                       | multiple values                                         | L100J100E, L225J50RE<br>L225J250E,L225J500E |

FIGURE 23. The hardware prototype and the experimental setup.

FIGURE 24. Experimental results of the voltage across the active switches and the diodes.

the active switches equals 57 V, and the maximum voltage stress across the diodes equals 124 V. The voltage across the capacitors is shown in Fig. 25. The voltage across each

FIGURE 25. Experimental results of the voltage across the capacitors.

FIGURE 26. Experimental results of the input current, inductor currents, active switches and diode currents.

**FIGURE 27.** Experimental results of the capacitors' currents and the output current.

capacitor in the first stage equals 57 V, in the second stage equals 133 V, and in the third stage equals 200 V. The output voltage equals 400 V. The current waveforms of inductors and switches were acquired at  $\approx 100 W$ , as shown in Fig. 27. The peak efficiency of the converter is about 97% at 160 W and about 96.3% at 200 W.

### **VIII. CONCLUSION**

In this paper, the family of an interleaved boost converter with voltage multiplier cells was presented. The general structure of the family consists of two sections: an interleaved boost stage and voltage multiplier cells. The structure comes in two configurations. Configuration 1's output is filtered using an output diode and a capacitor filter, where configuration 2's output is filtered using an LC filter. The difference between the two configurations was explained, and a comparison between the various family members was presented. An example of this family was given with a detailed steadystate analysis and component selection, which was evinced by simulation. A 200-W hardware prototype was implemented to further verify the analysis and the simulation. The converter is capable of drawing power from both a single or dual independent input voltage and with the same or different duty cycles of the active switches. These cases were summarized and compared. The family has good features besides the highvoltage gain. The input current ripple has twice frequency of the one in the conventional boost converter, which reduces the filter requirements and increases the accuracy of the current sensing for better tracking of MPPT. Although the converter is efficient, the efficiency can be further increased by either replacing the diodes with better ones or with active switches, with a trade-off of the complexity.

#### REFERENCES

- R. Teodorescu, M. Liserre, and P. Rodríguez, *Grid Converters for Photovoltaic and Wind Power Systems*, vol. 29. Hoboken, NJ, USA: Wiley, 2011.

- [2] F. Blaabjerg, Y. Yang, and K. Ma, "Power electronics—Key technology for renewable energy systems—Status and future," in *Proc. 3rd Int. Conf. Electr. Power Energy Convers. Syst.*, Oct. 2013, pp. 1–6.

- [3] J. W. Kolar, J. Biela, S. Waffler, T. Friedli, and U. Badstüebner, "Performance trends and limitations of power electronic systems," in *Proc. 6th Int. Conf. Integr. Power Electron. Syst. (CIPS)*, Mar. 2010, pp. 1–20.

- [4] J. D. van Wyk and F. C. Lee, "On a future for power electronics," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 1, no. 2, pp. 59–72, Jun. 2013.

- [5] V. A. K. Prabhala, B. P. Baddipadiga, and M. Ferdowsi, "DC distribution systems—An overview," in *Proc. Int. Conf. Renew. Energy Res. Appl. (ICRERA)*, Oct. 2014, pp. 307–312.

- [6] A. Pratt, P. Kumar, and T. V. Aldridge, "Evaluation of 400 V DC distribution in telco and data centers to improve energy efficiency," in *Proc. 29th Int. Telecommun. Energy Conf. (INTELEC)*, Sep./Oct. 2007, pp. 32–39.

- [7] P. T. Krein, "Data center challenges and their power electronics," CPSS Trans. Power Electron. Appl., vol. 2, no. 1, pp. 39–46, 2017.

- [8] D. J. Hammerstrom, "Ac versus DC distribution systemsdid we get it right?" in *Proc. IEEE Power Eng. Soc. Gen. Meeting*, Jun. 2007, pp. 1–5.

- [9] A. Mohamed and O. Mohammed, "Connectivity of DC microgrids involving sustainable energy sources," in *Proc. IEEE Ind. Appl. Soc. Annu. Meeting*, Oct. 2011, pp. 1–8.

- [10] V. A. K. Prabhala, P. Fajri, V. S. P. Gouribhatla, B. P. Baddipadiga, and M. Ferdowsi, "A DC–DC converter with high voltage gain and two input boost stages," *IEEE Trans. Power Electron.*, vol. 31, no. 6, pp. 4206–4215, Jun. 2016.

- [11] R.-J. Wai, C.-Y. Lin, R.-Y. Duan, and Y.-R. Chang, "High-efficiency DC-DC converter with high voltage gain and reduced switch stress," *IEEE Trans. Ind. Electron.*, vol. 54, no. 1, pp. 354–364, Feb. 2007.

- [12] L. S. Yang, T. J. Liang, and J. F. Chen, "Transformerless DC–DC converters with high step-up voltage gain," *IEEE Trans. Ind. Electron.*, vol. 56, no. 8, pp. 3144–3152, Aug. 2009.

- [13] Q. Zhao and F. C. Lee, "High-efficiency, high step-up DC-DC converters," *IEEE Trans. Power Electron.*, vol. 18, no. 1, pp. 65–73, Jan. 2003.

- [14] S.-M. Chen, T.-J. Liang, L.-S. Yang, and J.-F. Chen, "A cascaded high step-up DC–DC converter with single switch for microsource applications," *IEEE Trans. Power Electron.*, vol. 26, no. 4, pp. 1146–1153, Apr. 2011.

- [15] N. Denniston, A. M. Massoud, S. Ahmed, and P. N. Enjeti, "Multiplemodule high-gain high-voltage DC–DC transformers for offshore wind energy systems," *IEEE Trans. Ind. Electron.*, vol. 58, no. 5, pp. 1877–1886, May 2011.

- [16] Z. Liang, R. Guo, J. Li, and A. Q. Huang, "A high-efficiency PV module-integrated DC/DC converter for PV energy harvest in FREEDM systems," *IEEE Trans. Power Electron.*, vol. 26, no. 3, pp. 897–909, Mar. 2011.

- [17] B. Axelrod, Y. Berkovich, and A. Ioinovici, "Transformerless DC-DC converters with a very high DC line-to-load voltage ratio," in *Proc. Int. Symp. Circuits Syst. (ISCAS)*, vol. 3, May 2003, p. 3.

- [18] S. Dwari and L. Parsa, "An efficient high-step-up interleaved DC–DC converter with a common active clamp," *IEEE Trans. Power Electron.*, vol. 26, no. 1, pp. 66–78, Jan. 2011.

- [19] T.-F. Wu, Y.-C. Chen, J.-G. Yang, and C.-L. Kuo, "Isolated bidirectional full-bridge DC–DC converter with a flyback snubber," *IEEE Trans. Power Electron.*, vol. 25, no. 7, pp. 1915–1922, Jul. 2010.

- [20] F. S. F. Silva et al., "High gain DC-DC boost converter with a coupling inductor," in Proc. Brazilian Power Electron. Conf. (COBEP), Bonito-Mato Grosso do Sul, Brazil, Sep./Oct. 2009, pp. 486–492.

- [21] V. Yaramasu and B. Wu, "Three-level boost converter based medium voltage megawatt PMSG wind energy conversion systems," in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*, Sep. 2011, pp. 561–567.

- [22] J. M. Kwon, B. H. Kwon, and K. H. Nam, "Three-phase photovoltaic system with three-level boosting MPPT control," *IEEE Trans. Power Electron.*, vol. 23, no. 5, pp. 2319–2327, Sep. 2008.

- [23] R. W. Erickson and D. Maksimovic, Fundamentals of Power Electronics. Springer, 2007.

- [24] F. L. Tofoli, D. de Souza Oliveira, R. P. Torrico-Bascopé, and Y. J. A. Alcazar, "Novel nonisolated high-voltage gain DC–DC converters based on 3SSC and VMC," *IEEE Trans. Power Electron.*, vol. 27, no. 9, pp. 3897–3907, Sep. 2012.

- [25] F. L. Tofoli, D. de Castro Pereira, W. J. de Paula, and D. de Sousa Oliveira Júnior, "Survey on non-isolated high-voltage step-up DC–DC topologies based on the boost converter," *IET Power Electron.*, vol. 8, no. 10, pp. 2044–2057, Oct. 2015.

- [26] R. Haroun, A. E. Aroudi, A. Cid-Pastor, G. Garcia, C. Olalla, and L. Martínez-Salamero, "Impedance matching in photovoltaic systems using cascaded boost converters and sliding-mode control," *IEEE Trans. Power Electron.*, vol. 30, no. 6, pp. 3185–3199, Jun. 2015.

- [27] M. Veerachary and S. B. Sudhakar, "Stability analysis of cascaded DC-DC power electronic system," in *Proc. 7th Int. Conf. Power Electron. Drive Syst.*, Nov. 2007, pp. 1422–1426.

- [28] M. T. V and I. Barbi, "Nonisolated high step-up stacked DC-DC converter based on boost converter elements for high power application," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2011, pp. 249–252.

- [29] M. Forouzesh, Y. P. Siwakoti, S. A. Gorji, F. Blaabjerg, and B. Lehman, "Step-up DC–DC converters: A comprehensive review of voltage-boosting techniques, topologies, and applications," *IEEE Trans. Power Electron.*, vol. 32, no. 12, pp. 9143–9178, Dec. 2017.

- [30] B. P. R. Baddipadiga, V. A. K. Prabhala, and M. Ferdowsi, "A family of high-voltage-gain DC–DC converters based on a generalized structure," *IEEE Trans. Power Electron.*, vol. 33, no. 10, pp. 8399–8411, Oct. 2018.

- [31] R. Gules, L. L. Pfitscher, and L. C. Franco, "An interleaved boost DC-DC converter with large conversion ratio," in *Proc. IEEE Int. Symp. Ind. Electron.*, vol. 1, Jun. 2003, pp. 411–416.

- [32] C.-M. Lai, Y.-C. Lin, and D. Lee, "Study and implementation of a two-phase interleaved bidirectional DC/DC converter for vehicle and DC-microgrid systems," *Energies*, vol. 8, no. 9, pp. 9969–9991, 2015.

- [33] M. Prudente, L. L. Pfitscher, G. Emmendoerfer, E. F. Romaneli, and R. Gules, "Voltage multiplier cells applied to non-isolated DC–DC converters," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 871–887, Mar. 2008.

- [34] W. Li, Y. Zhao, Y. Deng, and X. He, "Interleaved converter with voltage multiplier cell for high step-up and high-efficiency conversion," *IEEE Trans. Power Electron.*, vol. 25, no. 9, pp. 2397–2408, Sep. 2010.

- [35] P. Kim, S. Lee, J. Park, and S. Choi, "High step-up interleaved boost converters using voltage multiplier cells," in *Proc. 8th Int. Conf. Power Electron.-ECCE Asia (ICPE ECCE)*, May/Jun. 2011, pp. 2844–2851.

- [36] W. Li and X. He, "Review of nonisolated high-step-up DC/DC converters in photovoltaic grid-connected applications," *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1239–1250, Apr. 2011.

- [37] L.-W. Zhou, B.-X. Zhu, Q.-M. Luo, and S. Chen, "Interleaved non-isolated high step-up DC/DC converter based on the diode-capacitor multiplier," *IET Power Electron.*, vol. 7, no. 2, pp. 390–397, Feb. 2014.

- [38] M. O'Loughlin, An Interleaving PFC Pre-Regulator for High-Power Converters. Dallas, TX, USA: Texas Instruments, 2006, pp. 1–14.

- [39] J. Roy and R. Ayyanar, "Sensor-less current sharing over wide operating range for extended-duty-ratio boost converter," *IEEE Trans. Power Electron.*, vol. 32, no. 11, pp. 8763–8777, Nov. 2017.

- [40] T. Nouri, S. H. Hosseini, E. Babaei, and J. Ebrahimi, "Generalised transformerless ultra step-up DC–DC converter with reduced voltage stress on semiconductors," *IET Power Electron.*, vol. 7, no. 11, pp. 2791–2805, Nov. 2014.

- [41] E. H. Ismail, M. A. Al-Saffar, and A. J. Sabzali, "High conversion ratio DC–DC converters with reduced switch stress," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 7, pp. 2139–2151, Aug. 2008.

- [42] J. C. Rosas-Caro, J. C. Mayo-Maldonado, R. Salas-Cabrera, A. Gonzalez-Rodriguez, E. N. Salas-Cabrera, and R. Castillo-Ibarra, "A family of DC-DC multiplier converters," *Eng. Lett.*, vol. 19, no. 1, pp. 57–67, 2011.

- [43] Y. J. A. Alcazar, D. de Souza Oliveira, F. L. Tofoli, and R. P. Torrico-Bascopé, "DC–DC nonisolated boost converter based on the three-state switching cell and voltage multiplier cells," *IEEE Trans. Ind. Electron.*, vol. 60, no. 10, pp. 4438–4449, Oct. 2013.

- [44] M. A. Al-Saffar and E. H. Ismail, "A high voltage ratio and low stress DC-DC converter with reduced input current ripple for fuel cell source," *Renew. Energy*, vol. 82, pp. 35–43, Oct. 2015.

- [45] A. A. Fardoun, E. H. Ismail, A. J. Sabzali, and M. A. Al-Saffar, "Bidirectional converter for high-efficiency fuel cell powertrain," *J. Power Sources*, vol. 249, pp. 470–482, Mar. 2014.

- [46] A. Alzahrani, P. Shamsi, and M. Ferdowsi, "A novel non-isolated highgain DC-DC boost converter," in *Proc. North Amer. Power Symp. (NAPS)*, Sep. 2017, pp. 1–6.

- [47] A. Alzahrani, P. Shamsi, and M. Ferdowsi, "An interleaved nonisolated DC-DC boost converter with diode-capacitor cells," in *Proc. IEEE 6th Int. Conf. Renew. Energy Res. Appl. (ICRERA)*, Nov. 2017, pp. 216–221.

- [48] L. Müller and J. W. Kimball, "High gain DC–DC converter based on the Cockcroft–Walton multiplier," *IEEE Trans. Power Electron.*, vol. 31, no. 9, pp. 6405–6415, Sep. 2016.

- [49] B. P. Baddipadiga and M. Ferdowsi, "A high-voltage-gain DC-DC converter based on modified dickson charge pump voltage multiplier," *IEEE Trans. Power Electron.*, vol. 32, no. 10, pp. 7707–7715, Oct. 2017.

AHMAD ALZAHRANI (S'09) received the B.Sc. degree in electrical engineering from Umm Alqura University, Makkah, Saudi Arabia, in 2009, the M.S. degree in electrical engineering from the University of Denver, Denver, CO, USA, in 2013, and the Ph.D. degree in electrical engineering from the Missouri University of Science and Technology, Rolla, MO, USA, in 2018. He joined the Electrical Engineering Department, Najran University, in 2019. His research interests include

power electronics, renewable energy systems, and artificial intelligence application in power and energy systems.

**MEHDI FERDOWSI** (S'02–M'04) received the B.S. degree in electronics from the University of Tehran, Tehran, Iran, in 1996, the M.S. degree in electronics from the Sharif University of Technology, Tehran, in 1999, and the Ph.D. degree in electrical engineering from the Illinois Institute of Technology, Chicago, in 2004. He joined the Faculty of the Missouri University of Science and Technology, Rolla, MO, USA, in 2004, where he is currently a Professor with the Electrical and

Computer Engineering Department. His research interests include the areas of power electronics, energy storage, smart grid, vehicular technology, and wide bandgap devices. He was a recipient of the National Science Foundation CAREER Award, in 2007. He is an Associate Editor of the IEEE TRANSACTIONS ON POWER ELECTRONICS. Since 2004, he has been successful in securing more than \$5 million in funding—his individual share. The published results of his scholarly activities include two book chapters and over 140 archival journals and conference proceedings. He has graduated more than 30 M.Sc. and Ph.D. students. He has received several Outstanding Teaching Awards and Recognitions from Missouri S&T. He received the Missouri S&T's Faculty Excellence Award, in 2017. He and his students received the Best Paper Award from the IEEE Vehicle Power and Propulsion Conference, in 2008. They also received the Best Poster Award from the IEEE International Conference on Renewable Energy Research and Applications, in 2014.

**POURYA SHAMSI** (S'05–M'13) received the B.Sc. degree in electrical engineering from the University of Tehran, Tehran, Iran, in 2007, and the Ph.D. degree in electrical engineering from the University of Texas at Dallas, Richardson, TX, USA, in 2012. He is currently an Assistant Professor of electrical engineering with the Missouri University of Science and Technology (formerly UMR), Rolla, MO, USA. His research interests include microgrids, reliability and reachability,

hybrid systems, networked control systems, power electronics, and motor drives.

. . .