To appear in ACM Transactions on Computer Systems.

An earlier version of this work also appears in *Proceedings of the 10th International Conference* on Parallel Architectures and Compilation Techniques. September 2001.

# A General Framework for Prefetch Scheduling in Linked Data Structures and its Application to Multi-Chain Prefetching

Seungryul Choi<sup>‡</sup>, Nicholas Kohout<sup>††</sup>, Sumit Pamnani<sup>\*</sup>, Dongkeun Kim<sup>†</sup>, Donald Yeung<sup>†</sup>

<sup>‡</sup>Computer Science Dept. Univ. of Maryland, College Park choi@cs.umd.edu ††Intel Corp. nicholas.j.kohout @intel.com

\*AMD Inc. sumitkumar.pamnani @amd.com †Electrical & Computer Eng. Dept. Univ. of Maryland, College Park {dongkeun,yeung}@eng.umd.edu

#### Abstract

Pointer-chasing applications tend to traverse composite data structures consisting of multiple independent pointer chains. While the traversal of any single pointer chain leads to the serialization of memory operations, the traversal of independent pointer chains provides a source of memory parallelism. This article investigates exploiting such *inter-chain memory parallelism* for the purpose of memory latency tolerance, using a technique called *multi-chain prefetching*. Previous works [30, 31] have proposed prefetching simple pointer-based structures in a multichain fashion. However, our work enables multi-chain prefetching for arbitrary data structures composed of lists, trees, and arrays.

This article makes five contributions in the context of multi-chain prefetching. First, we introduce a framework for compactly describing LDS traversals, providing the data layout and traversal code work information necessary for prefetching. Second, we present an off-line scheduling algorithm for computing a prefetch schedule from the LDS descriptors that overlaps serialized cache misses across separate pointer-chain traversals. Our analysis focuses on static traversals. We also propose using speculation to identify independent pointer chains in dynamic traversals. Third, we propose a hardware prefetch engine that traverses pointer-based data structures and overlaps multiple pointer chains according to the computed prefetch schedule. Fourth, we present a compiler that extracts LDS descriptors via static analysis of the application source code, thus automating multi-chain prefetching. Finally, we conduct an experimental evaluation of compiler-instrumented multi-chain prefetching and compare it against jump pointer prefetching [21], prefetch arrays [14], and predictor-directed stream buffers (PSB) [33].

Our results show compiler-instrumented multi-chain prefetching improves execution time by 40% across six pointer-chasing kernels from the Olden benchmark suite [29], and by 3% across four SPECint2000 benchmarks. Compared to jump pointer prefetching and prefetch arrays, multi-chain prefetching achieves 34% and 11% higher performance for the selected Olden and SPECint2000 benchmarks, respectively. Compared to PSB, multi-chain prefetching achieves 27% higher performance for the selected Olden benchmarks, but PSB outperforms multi-chain prefetching by 0.2% for the selected SPECint2000 benchmarks. An ideal PSB with an infinite markov predictor achieves comparable performance to multi-chain prefetching, coming within 6% across all benchmarks. Finally, speculation can enable multi-chain prefetching for some dynamic traversal codes, but our technique loses its effectiveness when the pointer-chain traversal order is highly dynamic.

## 1 Introduction

A growing number of important non-numeric applications employ linked data structures (LDSs). For example, databases commonly use index trees and hash tables to provide quick access to large amounts of data. Several compression algorithms and voice recognition programs use hash tables to store lookup values. Finally, object-oriented programming environments such as C++ and Java track dynamic objects using object graphs and invoke methods via function tables, both requiring linked data structures. Moreover, current trends show these non-numeric codes will become increasingly important relative to scientific workloads on future high-performance platforms.

The use of LDSs will likely have a negative impact on memory performance, making many non-numeric applications severely memory-bound on future systems. LDSs can be very large owing to their dynamic heap construction. Consequently, the working sets of codes that use LDSs can easily grow too large to fit in the processor's cache. In addition, logically adjacent nodes in an LDS may not reside physically close in memory. As a result, traversal of an LDS may lack spatial locality, and thus may not benefit from large cache blocks. The sparse memory access nature of LDS traversal also reduces the effective size of the cache, further increasing cache misses.

In the past, researchers have used prefetching to address the performance bottlenecks of memory-bound applications. Several techniques have been proposed, including software prefetching techniques [2, 16, 25, 26], hardware prefetching techniques [5, 9, 13, 28], or hybrid techniques [4, 6, 35]. While such conventional prefetching techniques are highly effective for applications that employ regular data structures (e.g. arrays), these techniques are far less successful for non-numeric applications that make heavy use of LDSs due to memory serialization effects known as the pointer chasing problem. The memory operations performed for array traversal can issue in parallel because individual array elements can be referenced independently. In contrast, the memory operations performed for LDS traversal must dereference a series of pointers, a purely sequential operation. The lack of memory parallelism during LDS traversal prevents conventional prefetching techniques from overlapping cache misses suffered along a pointer chain.

Recently, researchers have begun investigating prefetching techniques designed for LDS traversals. These new LDS prefetching techniques address the pointer-chasing problem using several different approaches. Stateless techniques [21, 23, 30, 37] prefetch pointer chains sequentially using only the natural pointers belonging to the LDS. Existing stateless techniques do not exploit any memory parallelism at all, or they exploit only limited amounts of memory parallelism. Consequently, they lose their effectiveness when the LDS traversal code contains insufficient work to hide the serialized memory latency [21].

A second approach [14, 21, 31], which we call jump pointer techniques, inserts additional pointers into the LDS to connect non-consecutive link elements. These "jump pointers" allow prefetch instructions to name link elements further down the pointer chain without sequentially traversing the intermediate links, thus creating memory parallelism along a single chain of pointers. Because they create memory parallelism using jump pointers, jump pointer techniques tolerate pointer-chasing cache misses even when the traversal loops contain insufficient work to hide the serialized memory latency. However, jump pointer techniques cannot commence prefetching until the jump pointers have been installed. Furthermore, the jump pointer installation code increases execution time, and the jump pointers themselves contribute additional cache misses.

Finally, a third approach consists of *prediction-based techniques* [12, 33, 34]. These techniques perform prefetching by predicting the cache-miss address stream, for example using hardware predictors [12, 33]. Early hardware predictors were capable of following striding streams only, but

more recently, correlation [3] and markov [12] predictors have been proposed that can follow arbitrary streams, thus enabling prefetching for LDS traversals. Because predictors need not traverse program data structures to generate the prefetch addresses, they avoid the pointer-chasing problem altogether. In addition, for hardware prediction, the techniques are completely transparent since they require no support from the programmer or compiler. However, prediction-based techniques lose their effectiveness when the cache-miss address stream is unpredictable.

This article investigates exploiting the natural memory parallelism that exists between independent serialized pointer-chasing traversals, or *inter-chain memory parallelism*. Our approach, called *multi-chain prefetching*, issues prefetches along a single chain of pointers sequentially, but aggressively pursues multiple independent pointer chains simultaneously whenever possible. Due to its aggressive exploitation of inter-chain memory parallelism, multi-chain prefetching can tolerate serialized memory latency even when LDS traversal loops have very little work; hence, it can achieve higher performance than previous stateless techniques. Furthermore, multi-chain prefetching does not use jump pointers. As a result, it does not suffer the overheads associated with creating and managing jump pointer state. And finally, multi-chain prefetching is an execution-based technique, so it is effective even for programs that exhibit unpredictable cache-miss address streams.

The idea of overlapping chained prefetches, which is fundamental to multi-chain prefetching, is not new: both Cooperative Chain Jumping [31] and Dependence-Based Prefetching [30] already demonstrate that simple "backbone and rib" structures can be prefetched in a multi-chain fashion. However, our work pushes this basic idea to its logical limit, enabling multi-chain prefetching for arbitrary data structures (our approach can exploit inter-chain memory parallelism for any data structure composed of lists, trees, and arrays). Furthermore, previous chained prefetching techniques issue prefetches in a greedy fashion. In contrast, our work provides a formal and systematic method for scheduling prefetches that controls the timing of chained prefetches. By controlling prefetch arrival, multi-chain prefetching can reduce both early and late prefetches which degrade performance compared to previous chained prefetching techniques.

In this article, we build upon our original work in multi-chain prefetching [17], and make the following contributions:

- 1. We present an *LDS descriptor framework* for specifying static LDS traversals in a compact fashion. Our LDS descriptors contain data layout information and traversal code work information necessary for prefetching.

- 2. We develop an off-line algorithm for computing an exact prefetch schedule from the LDS descriptors that overlaps serialized cache misses across separate pointer-chain traversals. Our algorithm handles static LDS traversals involving either loops or recursion. Furthermore, our algorithm computes a schedule even when the extent of dynamic data structures is unknown. To handle dynamic LDS traversals, we propose using speculation. However, our technique cannot handle codes in which the pointer-chain traversals are highly dynamic.

- 3. We present the design of a programmable prefetch engine that performs LDS traversal outside of the main CPU, and prefetches the LDS data using our LDS descriptors and the prefetch schedule computed by our scheduling algorithm. We also perform a detailed analysis of the hardware cost of our prefetch engine.

- 4. We introduce algorithms for extracting LDS descriptors from application source code via static analysis, and implement them in a prototype compiler using the SUIF framework [11].

Our prototype compiler is capable of extracting all the program-level information necessary for multi-chain prefetching fully automatically.

5. Finally, we conduct an experimental evaluation of multi-chain prefetching using several pointer-intensive applications. Our evaluation compares compiler-instrumented multi-chain prefetching against jump pointer prefetching [21, 31] and prefetch arrays [14], two jump pointer techniques, as well as predictor-directed stream buffers [33], an all-hardware prediction-based technique. We also investigate the impact of early prefetch arrival on prefetching performance, and we compare compiler- and manually-instrumented multi-chain prefetching to evaluate the quality of the instrumentation generated by our compiler. In addition, we characterize the sensitivity of our technique to varying hardware parameters. Lastly, we undertake a preliminary evaluation of speculative multi-chain prefetching to demonstrate its potential in enabling multi-chain prefetching for dynamic LDS traversals.

The rest of this article is organized as follows. Section 2 further explains the essence of multichain prefetching. Then, Section 3 introduces our LDS descriptor framework. Next, Section 4 describes our scheduling algorithm, Section 5 discusses our prefetch engine, and Section 6 presents our compiler for automating multi-chain prefetching. After presenting all our algorithms and techniques, Sections 7 and 8 then report on our experimental methodology and evaluation, respectively. Finally, Section 9 discusses related work, and Section 10 concludes the article.

# 2 Multi-Chain Prefetching

This section provides an overview of our multi-chain prefetching technique. Section 2.1 presents the idea of exploiting inter-chain memory parallelism. Then, Section 2.2 discusses the identification of independent pointer chain traversals.

# 2.1 Exploiting Inter-Chain Memory Parallelism

The multi-chain prefetching technique augments a commodity microprocessor with a programmable hardware prefetch engine. During an LDS computation, the prefetch engine performs its own traversal of the LDS in front of the processor, thus prefetching the LDS data. The prefetch engine, however, is capable of traversing multiple pointer chains simultaneously when permitted by the application. Consequently, the prefetch engine can tolerate serialized memory latency by overlapping cache misses across independent pointer-chain traversals.

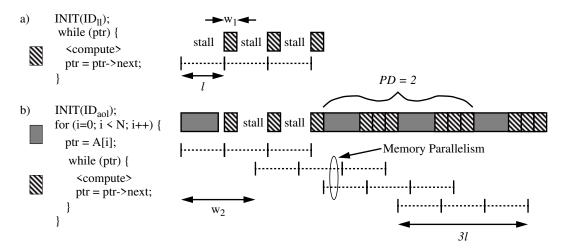

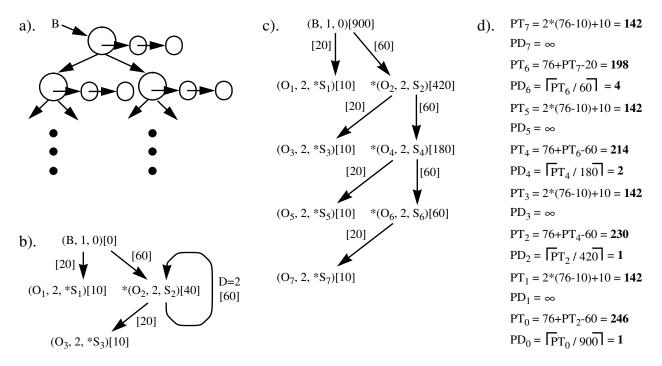

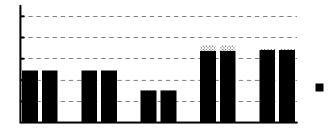

To illustrate the idea of exploiting inter-chain memory parallelism, we first describe how our prefetch engine traverses a single chain of pointers. Figure 1a shows a loop that traverses a linked list of length three. Each loop iteration, denoted by a hashed box, contains  $w_1$  cycles of work. Before entering the loop, the processor executes a prefetch directive,  $INIT(ID_{ll})$ , instructing the prefetch engine to initiate traversal of the linked list identified by the  $ID_{ll}$  label. If all three link nodes suffer an l-cycle cache miss, the linked list traversal requires 3l cycles since the link nodes must be fetched sequentially. Assuming  $l > w_1$ , the loop alone contains insufficient work to hide the serialized memory latency. As a result, the processor stalls for  $3l - 2w_1$  cycles. To hide these stalls, the prefetch engine would have to initiate its linked list traversal  $3l - 2w_1$  cycles before the processor traversal. For this reason, we call this delay the pre-traversal time (PT).

While a single pointer chain traversal does not provide much opportunity for latency tolerance,

Figure 1: Traversing pointer chains using a prefetch engine. a). Traversal of a single linked list. b). Traversal of an array of lists data structure.

pointer chasing computations typically traverse many pointer chains, each of which is often independent. To illustrate how our prefetch engine exploits such independent pointer-chasing traversals, Figure 1b shows a doubly nested loop that traverses an array of lists data structure. The outer loop, denoted by a shaded box with  $w_2$  cycles of work, traverses an array that extracts a head pointer for the inner loop. The inner loop is identical to the loop in Figure 1a.

In Figure 1b, the processor again executes a prefetch directive,  $INIT(ID_{aol})$ , causing the prefetch engine to initiate a traversal of the array of lists data structure identified by the  $ID_{aol}$  label. As in Figure 1a, the first linked list is traversed sequentially, and the processor stalls since there is insufficient work to hide the serialized cache misses. However, the prefetch engine then initiates the traversal of subsequent linked lists in a pipelined fashion. If the prefetch engine starts a new traversal every  $w_2$  cycles, then each linked list traversal will initiate the required PT cycles in advance, thus hiding the excess serialized memory latency across multiple outer loop iterations. The number of outer loop iterations required to overlap each linked list traversal is called the  $prefetch\ distance\ (PD)$ . Notice when PD>1, the traversals of separate chains overlap, exposing inter-chain memory parallelism despite the fact that each chain is fetched serially.

#### 2.2 Finding Independent Pointer-Chain Traversals

In order to exploit inter-chain memory parallelism, it is necessary to identify multiple independent pointer chains so that our prefetch engine can traverse them in parallel and overlap their cache misses, as illustrated in Figure 1. An important question is whether such independent pointer-chain traversals can be easily identified.

Many applications perform traversals of linked data structures in which the order of link node traversal does not depend on runtime data. We call these *static traversals*. The traversal order of link nodes in a static traversal can be determined a priori via analysis of the code, thus identifying the independent pointer-chain traversals at compile time. In this paper, we present an LDS descriptor framework that compactly expresses the LDS traversal order for static traversals. The descriptors in our framework also contain the data layout information used by our prefetch engine to generate the sequence of load and prefetch addresses necessary to perform the LDS traversal at runtime.

```

B = \&(data[0].value)

a), for (i = 0; i \le N; i++)

(B,L,S)

L = N

... = data[i].value;

S = sizeof(data[0])

data-

В

B = \&(root->next)

b), for (ptr = root; ptr != NULL; ) {

L = N

(B,L,*S)

ptr = ptr->next;

S = \&(type \ of \ ptr) \ 0 - next

root

N elements

```

Figure 2: Two LDS descriptors used to specify data layout information. a). Array descriptor. b). Linked list descriptor. Each descriptor appears inside a box, and is accompanied by a traversal code example and an illustration of the data structure.

While compile-time analysis of the code can identify independent pointer chains for static traversals, the same approach does not work for *dynamic traversals*. In dynamic traversals, the order of pointer-chain traversal is determined at runtime. Consequently, the simultaneous prefetching of independent pointer chains is limited since the chains to prefetch are not known until the traversal order is computed, which may be too late to enable inter-chain overlap. For dynamic traversals, it may be possible to *speculate* the order of pointer-chain traversal if the order is predictable. In this paper, we focus on static LDS traversals. Later in Section 8.7, we illustrate the potential for predicting pointer-chain traversal order in dynamic LDS traversals by extending our basic multi-chain prefetching technique with speculation.

# 3 LDS Descriptor Framework

Having provided an overview of multi-chain prefetching, we now explore the algorithms and hardware underlying its implementation. We begin by introducing a general framework for compactly representing static LDS traversals, which we call the *LDS descriptor framework*. This framework allows compilers (and programmers) to compactly specify two types of information related to LDS traversal: data structure layout, and traversal code work. The former captures memory reference dependences that occur in an LDS traversal, thus identifying pointer-chasing chains, while the latter quantifies the amount of computation performed as an LDS is traversed. After presenting the LDS descriptor framework, subsequent sections of this article will show how the information provided by the framework is used to perform multi-chain prefetching (Sections 4 and 5), and how the LDS descriptors themselves can be extracted by a compiler (Section 6).

#### 3.1 Data Structure Layout Information

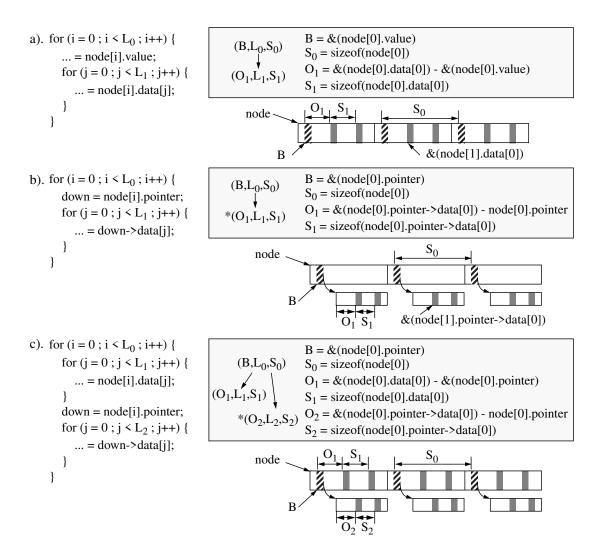

Data structure layout is specified using two descriptors, one for arrays and one for linked lists. Figure 2 presents each descriptor along with a traversal code example and an illustration of the traversed data structure. The array descriptor, shown in Figure 2a, contains three parameters: base

Figure 3: Nested descriptor composition. a). Nesting without indirection. b). Nesting with indirection. c). Nesting multiple descriptors. Each descriptor composition appears inside a box, and is accompanied by a traversal code example and an illustration of the composite data structure.

(B), length (L), and stride (S). These parameters specify the base address of the array, the number of array elements traversed by the application code, and the stride between consecutive memory references, respectively. The array descriptor specifies the memory address stream emitted by the processor during a constant-stride array traversal. Figure 2b illustrates the linked list descriptor which contains three parameters similar to the array descriptor. For the linked list descriptor, the B parameter specifies the root pointer of the list, the L parameter specifies the number of link elements traversed by the application code, and the \*S parameter specifies the offset from each link element address where the "next" pointer is located. The linked list descriptor specifies the memory address stream emitted by the processor during a linked list traversal.

To specify the layout of complex data structures, our framework permits descriptor composition. Descriptor composition is represented as a directed graph whose nodes are array or linked list descriptors, and whose edges denote address generation dependences. Two types of composition are allowed. The first type of composition is *nested composition*. In nested composition, each

```

main() {

foo(root, depth_limit);

}

foo(node, depth) {

depth = depth - 1;

if (depth == 0 || node == NULL)

return;

foo(node->child[0], depth);

foo(node->child[1], depth);

foo(node->child[2], depth);

}

```

Figure 4: Recursive descriptor composition. The recursive descriptor appears inside a box, and is accompanied by a traversal code example and an illustration of the tree data structure.

address generated by an outer descriptor forms the B parameter for multiple instantiations of a dependent inner descriptor. An offset parameter, O, is specified in place of the inner descriptor's B parameter to shift its base address by a constant offset. Such nested descriptors capture the memory reference streams of nested loops that traverse multi-dimensional data structures. Figure 3 presents several nested descriptors, showing a traversal code example and an illustration of the traversed multi-dimensional data structure along with each nested descriptor.

Figure 3a shows the traversal of an array of structures, each structure itself containing an array. The code example's outer loop traverses the array "node," accessing the field "value" from each traversed structure, and the inner loop traverses each embedded array "data." The outer and inner array descriptors,  $(B, L_0, S_0)$  and  $(O_1, L_1, S_1)$ , represent the address streams produced by the outer and inner loop traversals, respectively. (In the inner descriptor, " $O_1$ " specifies the offset of each inner array from the top of each structure). Figure 3b illustrates another form of descriptor nesting in which indirection is used between nested descriptors. The data structure in Figure 3b is similar to the one in Figure 3a, except the inner arrays are allocated separately, and a field from each outer array structure, "node[i].pointer," points to a structure containing the inner array. Hence, as shown in the code example from Figure 3b, traversal of the inner array requires indirecting through the outer array's pointer to compute the inner array's base address. In our framework, this indirection is denoted by placing a "\*" in front of the inner descriptor. Figure 3c, our last nested descriptor example, illustrates the nesting of multiple inner descriptors underneath a single outer descriptor to represent the address stream produced by nested distributed loops. The code example from Figure 3c shows the two inner loops from Figures 3a-b nested in a distributed fashion inside a common outer loop. In our framework, each one of the multiple inner array descriptors represents the address stream for a single distributed loop, with the order of address generation proceeding from the leftmost to rightmost inner descriptor.

It is important to note that while all the descriptors in Figure 3 show two nesting levels only, our framework allows an arbitrary nesting depth. This permits describing higher-dimensional LDS traversals, for example loop nests with > 2 nesting depth. Also, our framework can handle non-recurrent loads using "singleton" descriptors. For example, a pointer to a structure may be dereferenced multiple times to access different fields in the structure. Each dereference is a single non-recurrent load. We create a separate descriptor for each non-recurrent load, nest it underneath its recurrent load's descriptor, and assign an appropriate offset value, O, and length value, L=1.

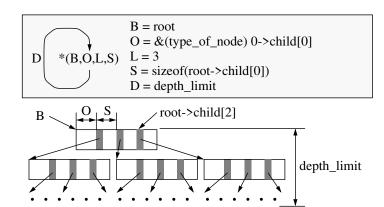

In addition to nested composition, our framework also permits recursive composition. Recur-

Figure 5: Each LDS descriptor graph is extended with work parameter and offset parameter annotations to specify the traversal code work information. Annotations for a). nested composition and b). recursive composition are shown. Each example shows the descriptor graph with annotations. In addition, the amount of work associated with each annotation parameter is indicated next to the source code.

sively composed descriptors describe depth-first tree traversals. They are similar to nested descriptors, except the dependence edge flows backwards. Since recursive composition introduces cycles into the descriptor graph, our framework requires each backwards dependence edge to be annotated with the depth of recursion, D, to bound the size of the data structure. Figure 4 shows a simple recursive descriptor in which the backwards dependence edge originates from and terminates to a single array descriptor. The "L" parameter in the descriptor specifies the fanout of the tree. In our example, L=3, so the traversed data structure is a tertiary tree, as shown in Figure 4. Notice the array descriptor has both B and O parameters—B provides the base address for the first instance of the descriptor, while O provides the offset for all recursively nested instances.

In Figures 2 and 4, we assume the L parameter for linked lists and the D parameter for trees are known a priori, which is generally not true. Later in Section 4.3, we discuss how our framework handles these unknown descriptor parameters. In addition, our prefetch engine, discussed in Section 5, does not require these parameters, and instead prefetches until it encounters a null pointer.

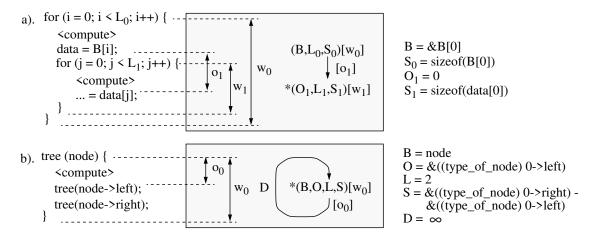

#### 3.2 Traversal Code Work Information

The traversal code work information specifies the amount of work performed by the application code as it traverses the LDS. Our LDS descriptor framework extends the descriptor graph with annotations to specify the traversal code work information. Two types of annotations are provided. First, the work parameter annotation specifies the work per iteration of a traversal loop in cycles. Each array or linked list descriptor in an LDS descriptor graph contains a work parameter annotation, appearing inside brackets at the end of the descriptor. Figure 5 illustrates the work parameter annotations for nested and recursively composed descriptors. In Figure 5a,  $w_0$  and  $w_1$  specify the work per iteration of the outer and inner loops, respectively, in a nested composition. For nested compositions, each work parameter includes the work of all nested loops, so  $w_0$  includes the work of an entire inner loop instance,  $L_1 * w_1$ . In Figure 5b,  $w_0$  specifies the work per instance of each recursive function call in a recursive composition. For recursive compositions, each work

parameter includes the work of a single function call instance only, and excludes all recursively called instances. Our scheduling algorithm computes the work of the recursive instances through recursive descriptor unrolling, discussed later in Section 4.1.2.

The second type of annotation, called the offset parameter annotation, specifies the work separating the first iteration of a descriptor from each iteration of its parent descriptor. Each dependence edge in an LDS descriptor graph contains an offset parameter annotation, appearing inside brackets beside the dependence edge. Figures 5a and b illustrate the offset parameter annotations,  $o_1$  and  $o_0$ , for the nested and recursively composed descriptors, respectively.

Values for both the work and offset parameters are architecture dependent, and measuring them would require detailed simulation. We make the simplifying assumption that CPI (assuming all memory references take 1 cycle as a result of perfect prefetching) is 1.0, and use static instruction counts to estimate the parameter values. While this provides only an estimate, we find the estimates are sufficiently accurate. Furthermore, in many LDS traversals, there may be multiple paths through the traversal code. When multiple paths exist, the work and offset parameters are computed assuming the shortest path, thus yielding minimum work and offset parameter values. Choosing minimum values for the traversal code work information tends to schedule prefetches earlier than necessary. While this guarantees that prefetches never arrive late, early prefetches can have negative performance consequences. Later in Section 8, we will evaluate the performance impact of early prefetches.

# 4 Prefetch Chain Scheduling

The LDS descriptor framework, presented in Section 3, captures all the information necessary for multi-chain prefetching. In the next two sections, we discuss how this information is used to perform prefetching. We begin by presenting an algorithm for computing a prefetch chain schedule from an LDS descriptor graph. Sections 4.1 and 4.2 describe our basic scheduling algorithm, and demonstrate how it works using a detailed example. Our basic scheduling algorithm computes an exact prefetch chain schedule which requires the size of all data structures to be known a priori, including the length of linked lists and the depth of trees (i.e. the L and D parameters from Section 3.1). In Sections 4.1 and 4.2, we optimistically assume these parameters are available to facilitate a clean exposition of our scheduling algorithm. Then, in Section 4.3, we discuss how our scheduling algorithm handles the more general case in which these parameters are not known.

We note our scheduling algorithm is quite general. While Section 2 illustrated the multi-chain prefetching idea using a simple array of lists example, the scheduling algorithm presented in this section can handle any arbitrary data structure composed of lists, trees, and arrays. However, our technique works only for static traversals. Later, in Section 8.7, we will discuss extensions for dynamic traversals.

#### 4.1 Scheduling Algorithm

This section presents our basic scheduling algorithm. Section 4.1.1 describes the algorithm assuming acyclic LDS descriptor graphs. Then, Section 4.1.2 discusses how our scheduling algorithm handles LDS descriptor graphs that contain cycles.

```

for (i = N-1 \text{ down to } 0) {

(PT_k - o_k)

(1)

PTnest_i =

composed k via indirection

if ((descriptor i is pointer-chasing) and (l > w_i)) {

PT_i = L_i * (l - w_i) + w_i + PTnest_i

(2)

PD_i = \infty;

(3)

} else {

PT_i = l + PTnest_i

(4)

PD_i = \lceil PT_i / w_i \rceil

(5)

}

```

Figure 6: The basic scheduling algorithm for acyclic descriptor graphs.

## 4.1.1 Scheduling for Acyclic Descriptor Graphs

Figure 6 presents our basic scheduling algorithm that computes the scheduling information necessary for prefetching. Given an LDS descriptor graph, our scheduling algorithm computes three scheduling parameters for each descriptor i in the graph: whether the descriptor requires asynchronous or synchronous prefetching, the pre-traversal time,  $PT_i$  (i.e. the number of cycles in advance that the prefetch engine should begin prefetching a chain of pointers prior to the processor's traversal), and the prefetch distance,  $PD_i$  (i.e. the pre-traversal time in terms of iterations of the loop containing the pointer-chain traversal). These parameters were introduced in Section 2.1. As we will explain below, the scheduling parameters at each descriptor i are dependent upon the parameter values in the sub-graph nested underneath i; hence, descriptors must be processed from the leaves of the descriptor graph to the root. The "for (N-1) down to 0)" loop processes the descriptors in the required bottom-up order assuming we assign a number between 0 and N-1 in top-down order to each of the N descriptors in the graph, as is done in Figures 3 and 5 (and later in Figure 7). As mentioned earlier, our basic scheduling algorithm assumes there are no cycles in the descriptor graph. Our basic scheduling algorithm also assumes the cache miss latency to physical memory, l, is known.

We now describe the computation of the three scheduling parameters for each descriptor visited in the descriptor graph. First, we determine whether a descriptor requires asynchronous or synchronous prefetching. We say descriptor i requires asynchronous prefetching if it traverses a linked list and there is insufficient work in the traversal loop to hide the serialized memory latency  $(i.e.\ l > w_i)$ . Otherwise, if descriptor i traverses an array or if  $l \le w_i$ , then we say it requires synchronous prefetching.<sup>1</sup> The "if" conditional test in Figure 6 computes whether asynchronous or synchronous prefetching is used.

Next, we compute the pre-traversal time,  $PT_i$ . The computation of  $PT_i$  is different for asynchronous prefetching and synchronous prefetching. For asynchronous prefetching, we must overlap that portion of the serialized memory latency that cannot be hidden underneath the traversal loop itself with work prior to the loop. Figure 1 shows  $PT = 3l - 2w_1$  for a 3-iteration pointer-chasing loop. If we generalize this expression, we get  $PT_i = L_i * (l - w_i) + w_i$ . In contrast, for synchronous prefetching, we need to only hide the cache miss for the first iteration of the traversal loop, so  $PT_i = l$ . Equations 2 and 4 in Figure 6 compute  $PT_i$  for asynchronous and synchronous prefetching, respectively. Notice these equations both contain an extra term,  $PTnest_i$ .  $PTnest_i$  serializes

<sup>&</sup>lt;sup>1</sup>This implies that linked list traversals in which  $l \le w_i$  use synchronous prefetching since prefetching one link element per loop iteration can tolerate the serialized memory latency when sufficient work exists in the loop code.

$PT_i$  and  $PT_k$ , where  $PT_k$  is the pre-loop time of any descriptor k nested underneath descriptor i using indirection (i.e. the nested composition illustrated in Figure 3b). Serialization occurs between composed descriptors that use indirection because of the data dependence caused by indirection. We must sum  $PT_k$  into  $PT_i$ ; otherwise, the prefetches for descriptor k will not initiate early enough. Equation 1 in Figure 6 considers all descriptors composed under descriptor i that use indirection and sets  $PTnest_i$  to the largest  $PT_k$  found. The offset,  $o_k$ , is subtracted because it overlaps with descriptor k's pre-loop time.

Finally, we compute the prefetch distance,  $PD_i$ . Descriptors that require asynchronous prefetching do not have a prefetch distance; we denote this by setting  $PD_i = \infty$ . The prefetch distance for descriptors that require synchronous prefetching is exactly the number of loop iterations necessary to overlap the pre-traversal time, which is  $\lceil \frac{PT_i}{w_i} \rceil$ . Equations 3 and 5 in Figure 6 compute the prefetch distance for asynchronous and synchronous prefetching, respectively.

#### 4.1.2 Recursive Descriptor Unrolling

Cycles can occur in LDS descriptor graphs due to recursive composition, as discussed in Section 3.1. To handle cyclic descriptor graphs, we remove the cycles to obtain an equivalent acyclic descriptor graph, and apply the basic scheduling algorithm for acyclic descriptor graphs introduced in Section 4.1.1. The technique used to remove the cycles is called *recursive descriptor unrolling*.

Recursively composed descriptors can be "unrolled" by replicating all descriptors along the cycle D times, where D is the depth of recursion associated with the backwards dependence edge. Each replicated descriptor is nested underneath its parent in a recursive fashion, preserving the LDS traversal order specified by the original recursively composed descriptor.

In addition to descriptor replication, recursive descriptor unrolling must also update the work parameter annotations associated with replicated descriptors. Specifically, each work parameter along the chain of replicated descriptors should be increased to include the work of all nested descriptors created through replication. To update the work parameters, we visit each replicated descriptor in the unrolled descriptor graph in bottom-up order. For each visited descriptor, we sum the work from all child descriptors into the visited descriptor's work parameter, where each child descriptor i contains work  $L_i * w_i$ .

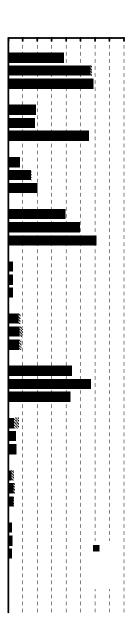

## 4.2 Example of an Exact Prefetch Chain Schedule

This section presents a detailed prefetch chain scheduling example using the techniques described in Section 4.1. Figure 7 illustrates each step of our technique applied to the example, and Figure 8 graphically shows the final prefetch chain schedule computed by our scheduling algorithm. In this example, we assume the size of data structures is known, allowing our scheduling algorithm to compute an exact prefetch chain schedule.

We have chosen the traversal of a tree of lists data structure as our example. This particular LDS traversal resembles the computation performed in the Health benchmark from the Olden suite [29], one of the applications used in our performance evaluation presented in Section 8. The tree of lists data structure appears in Figure 7a. We assume a balanced binary tree of depth 4 in which each tree node contains a linked list of length 2.<sup>2</sup> Furthermore, we assume a depth-first

<sup>&</sup>lt;sup>2</sup>Our tree of lists data structure differs slightly from the one in the Health benchmark. Health uses a balanced quad tree of depth 5 in which each tree node contains several variable-length linked lists. One of the linked lists, which causes most of the cache misses in Health, contains roughly 150 link elements.

Figure 7: Prefetch chain scheduling example for a tree of lists traversal. a). Tree of lists data structure. b). Cyclic LDS descriptor graph representation. c). Equivalent acyclic LDS descriptor graph after unrolling. d). Scheduling parameter solutions using l = 76 cycles.

traversal of the tree in which the linked list at each tree node is traversed before the recursive call to the left and right child nodes. (Note Figure 7a only shows two levels of our depth-four tree.)

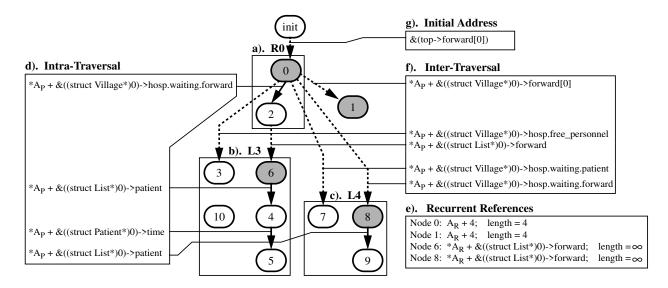

First, we extract data layout and traversal code work information via static analysis of the application code (this is the compiler's job, and will be described later in Section 6). Figure 7b shows the LDS descriptor graph resulting from this analysis. Descriptor 0, the root of the descriptor graph, is a "dummy" descriptor that provides the root address of the tree, "B." Descriptors 1 and 2, nested directly underneath descriptor 0, traverse the linked list and tree node, respectively, at the root of the tree. Composed under descriptor 2 are the descriptors that traverse the linked list (descriptor 3 which is identical to descriptor 1) and tree node (descriptor 2 itself composed recursively) at the next lower level of the tree. The data layout information in this descriptor graph is exactly the information used by our prefetch engine, described later in Section 4.

Second, we apply recursive descriptor unrolling to the cyclic descriptor graph in Figure 7b to remove cycles. Figure 7c shows the equivalent acyclic descriptor graph after unrolling. Descriptor replication creates two copies of the recursively composed descriptors since D=2 in Figure 7b, producing descriptors 4 and 6 (copies of descriptor 2), and descriptors 5 and 7 (copies of descriptor 3). After copying, the work parameters are updated to reflect the work in the newly created descriptors as described in Section 4.1.2.

Finally, we compute the pre-loop time,  $PT_i$ , and the prefetch distance,  $PD_i$ , for each descriptor  $i \in \{0..7\}$  in Figure 7c using the basic scheduling algorithm. Figure 7d shows the computation of the scheduling parameters for each descriptor in bottom-up order, following the algorithm in Figure 6. For this computation, we assume an arbitrary memory latency, l, of 76 cycles.

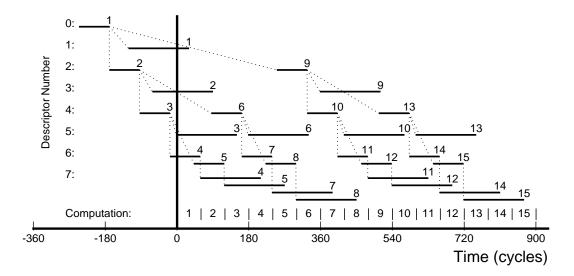

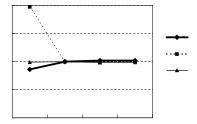

Figure 8 graphically displays the prefetch chain schedule specified by the scheduling parameters in Figure 7d by plotting the initiation and completion of prefetch requests from different descriptors

Figure 8: A graphical display of the final prefetch chain schedule computed by our scheduling algorithm for the tree of lists example. Short horizontal lines denote prefetches for the tree nodes, long horizontal lines denote prefetches for the linked lists, and dotted lines indicate address generation dependences. The "Computation" timeline shows the traversal of the tree nodes by the application code. We assume all prefetches take 76 cycles to complete.

$(y\text{-}\mathrm{axis})$  as a function of time  $(x\text{-}\mathrm{axis})$ . Short solid horizontal lines denote prefetches for the tree nodes, long solid horizontal lines denote 2 serialized prefetches for each linked list, and dotted lines indicate address generation dependences. The "Computation" timeline shows the traversal of the tree nodes by the application code, with a unique ID assigned to each instance of a recursive function call. Each prefetch request has been labeled with the function call instance ID that consumes the prefetched data. Notice all prefetch requests complete by the time the processor consumes the data. After an initial startup period which ends at Time = 0, the processor will not have to stall. The figure also shows our scheduling algorithm exposes significant inter-chain memory parallelism in the tree of lists traversal.

#### 4.3 Handling Unknown Descriptor Graph Parameters

Throughout Sections 4.1 and 4.2, we have assumed that LDS descriptor graph parameters are known statically, enabling our scheduling algorithm to compute an exact prefetch chain schedule off line. This assumption is optimistic since certain LDS data layout parameters may not be known until runtime. In particular, static analysis typically cannot determine the list length, L, in linked list descriptors, and the recursion depth, D, in recursively composed descriptors (see Section 3.1 for a description of these parameters). As a consequence, it is impossible to compute an exact prefetch chain schedule statically for many LDS traversals.

One potential solution is to obtain the missing information through profiling. Unfortunately, this approach has several drawbacks. First, profiling can be cumbersome because it requires profile runs, and the accuracy of the profiles may be sensitive to data inputs. Furthermore, profiling cannot determine the data layout parameters exactly if the size of data structures varies during program execution. Rather than using profiles, we propose another solution that uses only static information. The key insight behind our solution is that the scheduling parameters computed by

$$PT_{7}(L) = L(76 - 10) + 10 = 66L + 10$$

$$PD_{7} = \infty$$

$$PT_{6}(L) = 76 + PT_{7} - 20 = 66L + 66$$

$$PD_{6}(L) = \left[\frac{PT_{6}(L)}{10L + 40}\right] = \left[\frac{66L + 66}{10L + 40}\right]$$

$$PD_{6}(L \to \infty) \to \left[\frac{66}{10}\right] = 7$$

Figure 9: Computing scheduling parameters for the leaf nodes as a function of the list length, L, for the tree of lists example.

our scheduling algorithm are *bounded* regardless of the size of dynamic data structures. Hence, our scheduling algorithm can compute a bounded solution when an exact solution cannot be determined due to incomplete static information.

To illustrate how bounded prefetch chain schedules can be computed for linked lists and trees, consider once again the tree of lists example from Figure 7. We will first assume the length of each linked list (the L parameter in descriptors 1 and 3 in Figure 7b) is not known. Then, we will assume the depth of recursion (descriptor 2's D parameter in Figure 7b) is not known.

#### 4.3.1 Unknown List Length

Without the list length, the pre-loop time of the linked list descriptors  $(PT_7, PT_5, PT_3, \text{ and } PT_1)$  in Figure 7d) cannot be computed, which in turn prevents computing the prefetch distance for the tree node descriptors  $(PD_6, PD_4, PD_2, \text{ and } PD_0)$ . However, it is possible to express these quantities as a function of the list length. Figure 9 shows the computation for descriptors 6 and 7 from Figure 7d as a function of the list length, L.

In Figure 9, the prefetch distance for the list,  $PD_7$ , remains  $\infty$  because this linked list should be prefetched as fast as possible independent of its length. However, the prefetch distance for the tree node,  $PD_6$ , becomes a function of L. Notice in the limit, as  $L \to \infty$ ,  $PD_6 \to \left\lceil \frac{66}{10} \right\rceil = 7$ . Such a bounded prefetch distance exists because both the pre-loop time of the list (66L+66) and the work of its parent loop (10L+40) depend linearly on the list length. Consequently,  $PD_6$  does not grow unbounded, but instead grows towards an asymptotic value as list length increases. In general, the prefetch distances for the predecessors of a linked list descriptor in an LDS descriptor graph are always bounded, and can be determined statically by solving the scheduling equations in the limit, as illustrated in Figure 9.

Although the prefetch distances associated with linked lists are bounded, buffering requirements may not be. A bounded prefetch distance only fixes the number of lists prefetched simultaneously; the number of prefetches issued in advance of the processor for each list grows linearly with its length. Hence, buffering for prefetched data is in theory unbounded. Applications requiring large amounts of buffering may suffer thrashing, limiting performance. Fortunately, we find lists are relatively short and do not grow unbounded in practice, most likely because long lists are undesirable from an algorithmic standpoint. Programmers typically employ data structures such as hash tables and trees to reduce chain length, and thus reduce buffering requirements. In Section 8, we will evaluate the impact of finite buffering on multi-chain prefetching performance.

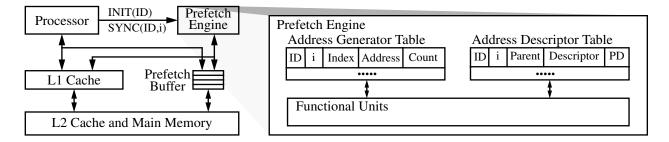

Figure 10: Prefetch engine hardware and integration with a commodity microprocessor.

#### 4.3.2 Unknown Recursion Depth

Without the recursion depth, recursively composed descriptors (e.g. descriptors 2 and 3 in Figure 7b) cannot be unrolled, and their scheduling parameters thus cannot be computed. However, the prefetch distance of any descriptor created during unrolling is guaranteed not to exceed the prefetch distance of the leaf descriptor (e.g. descriptor 7 in Figure 7d). This is because the leaf descriptor contains the least amount of work among all descriptors created during unrolling; hence, it has the largest prefetch distance. So, the leaf descriptor's prefetch distance is an upper bound on the prefetch distances for all other descriptors associated with the tree traversal. For example, in Figure 7d, the prefetch distance of the leaf descriptor,  $PD_6$ , is 4, while the prefetch distances for its predecessor descriptors,  $PD_4$ ,  $PD_2$ , and  $PD_0$  are only 2, 1, and 1, respectively.

Furthermore, the leaf descriptor's prefetch distance is independent of recursion depth. This is because a descriptor's predecessors in the LDS descriptor graph do not affect any of its data layout or traversal code work parameters. In particular, regardless of the recursion depth, the traversal code work associated with the leaf descriptor is exactly the amount of work in a single function call instance since there are no other recursive calls beyond a leaf node. Consequently, all LDS descriptor graph parameters necessary to compute the prefetch distance for the leaf descriptor are available statically. So, our scheduling algorithm can compute the leaf descriptor's prefetch distance exactly, which yields the bound on the prefetch distance for all descriptors contained in the tree traversal as well, despite the fact that the recursion depth is not known.

We propose to handle unknown recursion depth by computing the prefetch distance for the leaf descriptor, and then using this prefetch distance for descriptors at all levels in the tree traversal. This approach ensures that nodes at the leaves of the tree are prefetched using an exact prefetch distance, and that all other tree nodes are prefetched using a prefetch distance that is larger than necessary. Since a large fraction of a tree's nodes are at the leaves of the tree, our approach should provide good performance.

# 5 Prefetch Engine

In this section, we introduce a programmable prefetch engine that performs LDS traversal outside of the main CPU. Our prefetch engine uses the data layout information described in Section 3.1 and the scheduling parameters described in Section 4.1 to guide LDS traversal.

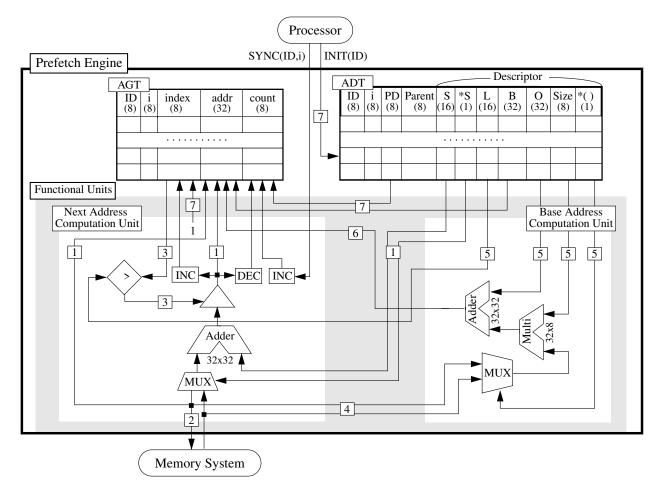

The left of half of Figure 10 shows the integration of the prefetch engine with a commodity microprocessor. The design requires three additions to the microprocessor: the prefetch engine itself, a prefetch buffer, and two new instructions called *INIT* and *SYNC*. During LDS traversal,

the prefetch engine fetches data into the prefetch buffer if it is not already in the L1 cache at the time the fetch is issued (a fetch from main memory is placed in the L2 cache on its way to the prefetch buffer). All processor load/store instructions access the L1 cache and prefetch buffer in parallel. A hit in the prefetch buffer provides any necessary data to the processor in 1 cycle, and also transfers the corresponding cache block from the prefetch buffer to the L1 cache (in the case of a store, the write is then performed in the L1 cache).

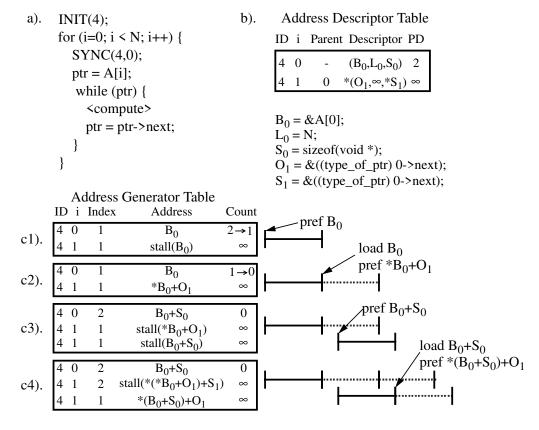

The prefetch engine, shown in the right half of Figure 10, consists of two hardware tables, the Address Descriptor Table and the Address Generator Table, and some functional units. The rest of this section discusses how the prefetch engine works. First, Sections 5.1 and 5.2 describe the Address Descriptor and Address Generator tables in detail, explaining how these tables are used to compute prefetch addresses from the LDS descriptors introduced in Section 3. This discussion uses the array of lists example from Figure 1; the code for this example, annotated with INIT and SYNC instruction macros, appears in Figure 11a. Then, Section 5.3 discusses how prefetches are scheduled according to the scheduling information computed by our scheduling algorithm. Finally, Section 5.4 presents a detailed implementation of the prefetch engine, including a description of the functional units, and analyzes its cost.

# 5.1 Address Descriptor Table

The Address Descriptor Table (ADT) stores the data layout information from the LDS descriptors described in Section 3.1. Each array or linked list descriptor in an LDS descriptor graph occupies a single ADT entry, identified by the graph number, ID (each LDS descriptor graph is assigned a unique ID), and the descriptor number, i, assuming the top-down numbering of descriptors discussed in Section 4.1.1. The Parent field specifies the descriptor's parent in the descriptor graph. The Descriptor field stores all the parameters associated with the descriptor such as the base, length, and stride, and whether or not indirection is used. Finally, the PD field stores the prefetch distance computed by our scheduling algorithm for descriptor i. Figure 11b shows the contents of the ADT for our array of lists example, where ID = 4.

Before prefetching can commence, the ADT must be initialized with the data layout and prefetch distance information for the application. We memory map the ADT and initialize its contents via normal store instructions. Most ADT entries are filled at program initialization time. However, some ADT parameters are unknown until runtime (e.g. the base address of a dynamically allocated array). Such runtime parameters are written into the ADT immediately prior to each *INIT* instruction. Although Figure 11a does not show the ADT initialization code, our compiler described later in Section 6 generates all the necessary code to initialize the ADT.

Notice the ADT contents should be saved and restored across process switches by the operating system. On a process switch, the OS must flush the AGT to terminate prefetching (the next section explains the AGT), and save out the contents of the ADT. When the process is rescheduled, its ADT contents will be restored, but we assume the AGT contents will not. This simplifies the save and restore operation, but it can prematurely terminate prefetching. Since process switches are infrequent, these effects should not impact performance significantly (for frequent exceptions like TLB faults that do not result in a process switch, the OS does not have to save and restore the ADT). In our benchmarks, system calls are extremely infrequent; moreover, we only consider single-program workloads. Consequently, our simulator assumes both the ADT and AGT contents persist across all context switches and does not model switching-related overheads.

Figure 11: LDS traversal example. a). Array of lists traversal code annotated with prefetch directives. b). ADT contents. c). AGT contents at 4 different times during LDS traversal.

#### 5.2 Address Generator Table

The Address Generator Table (AGT) generates the LDS traversal address stream specified by the data layout information stored in the ADT. AGT entries are activated dynamically. Once activated, each AGT entry generates the address stream for a single LDS descriptor. AGT entry activation can occur in one of two ways. First, the processor can execute an INIT(ID) instruction to initiate prefetching for the data structure identified by ID. Figure 11c1 shows how executing INIT(4) activates the first entry in the AGT. The prefetch engine searches the ADT for the entry matching ID = 4 and i = 0 (i.e. entry (4,0) from Figure 11b which is the root node for descriptor graph #4). An AGT entry (4,0) is allocated for this descriptor, the Index field is set to one, and the Address field is set to  $B_0$ , the base parameter from ADT entry (4,0). Once activated, AGT entry (4,0) issues a prefetch for the first array element at address  $B_0$ , denoted by a solid bar in Figure 11c1.

Second, when an active AGT entry computes a new address, a new AGT entry is activated for every node in the descriptor graph that is a child of the active AGT entry. (Note, address computation for the AGT occurs in the functional units shown in Figure 10; these will be described in detail in Section 5.4). As shown in Figure 11c1, a second AGT entry, (4,1), is activated after AGT entry (4,0) issues its prefetch because (4,0) is the parent of (4,1) in the ADT. This new AGT entry is responsible for prefetching the first linked list; however, it stalls initially because it must wait for the prefetch of  $B_0$  to complete before it can compute its base address,  $*B_0$ . Eventually, the prefetch of  $B_0$  completes, AGT entry (4,1) loads the value, and issues a prefetch for address  $*B_0$ , denoted by a dashed bar in Figure 11c2.

Figures 11c3 and 11c4 show the progression of the array of lists traversal. In Figure 11c3, AGT entry (4,0) generates the address and issues the prefetch for the second array element at  $B_0 + S_0$ . As a result, its Index value is incremented, and another AGT entry (4,1) is activated to prefetch the second linked list. Once again, this entry stalls initially, but continues when the prefetch of  $B_0 + S_0$  completes, as shown in Figure 11c4. Furthermore, Figures 11c3 and 11c4 show the progress of the original AGT entry (4,1) as it traverses the first linked list serially. In Figure 11c3, the AGT entry is stalled on the prefetch of the first link node. Eventually, this prefetch completes and the AGT entry issues the prefetch for the second link node at address  $*B_0 + S_1$ . In Figure 11c4, the AGT entry is waiting for the prefetch of the second link node to complete.

AGT entries are deactivated once the Index field in the AGT entry reaches the L parameter in the corresponding ADT entry, or in the case of a pointer-chasing AGT entry, if a null pointer is reached during traversal.

#### 5.3 Prefetch Scheduling

When an active AGT entry generates a new memory address, the prefetch engine must schedule a prefetch for the memory address. Prefetch scheduling occurs in two ways. First, if the prefetches for the descriptor should issue asynchronously (i.e.  $PD_i = \infty$ ), the prefetch engine issues a prefetch for the AGT entry as long as the entry is not stalled. Consequently, prefetches for asynchronous AGT entries traverse a pointer chain as fast as possible, throttled only by the serialized cache misses that occur along the chain. The (4,1) AGT entries in Figure 11 are scheduled in this fashion.

Second, if the prefetches for the descriptor should issue synchronously (i.e.  $PD_i \neq \infty$ ), then the prefetch engine synchronizes the prefetches with the code that traverses the corresponding array or linked list. We rely on the compiler to insert a SYNC instruction at the top of the loop or recursive function call that traverses the data structure to provide the synchronization information, as shown in Figure 11a. Furthermore, the prefetch engine must maintain the proper prefetch distance as computed by our scheduling algorithm for such synchronized AGT entries. A Count field in the AGT entry is used to maintain this prefetch distance. The Count field is initialized to the PD value in the ADT entry (computed by the scheduling algorithm) upon initial activation of the AGT entry, and is decremented each time the prefetch engine issues a prefetch for the AGT entry, as shown in Figures 11c1 and 11c2. In addition, the prefetch engine "listens" for SYNC instructions. When a SYNC executes, it emits a descriptor graph ID and a descriptor number i that matches an AGT entry (essentially matching up the loop with the AGT entry generating its address stream). On a match, the Count value in the matched AGT entry is incremented. The prefetch engine issues a prefetch as long as Count > 0. Once Count reaches 0, as it has in Figure 11c2, the prefetch engine waits for the Count value to be incremented before issuing the prefetch for the AGT entry, which occurs the next time the corresponding SYNC instruction executes (not shown in Figure 11).

#### 5.4 Hardware Implementation and Cost

Figure 12 presents an implementation of the prefetch engine. This figure is similar to Figure 10, but illustrates the ADT, AGT, and functional units in greater detail. Enough detail has been provided to permit an estimate of the prefetch engine's hardware cost.

In Figure 12, the ADT and AGT are identical to the ones in Figure 10 except for two differences. First, the AGT Descriptor field has been expanded to show the descriptor parameters. The B, L, S, and O parameters are the same as those described in Section 3.1; the "\*S" parameter

Figure 12: Prefetch engine implementation, detailing the ADT and AGT, and two functional units, the Next Address Computation Unit and the Base Address Computation Unit.

specifies whether the descriptor is an array descriptor or a linked-list descriptor; the "\*()" parameter indicates whether indirection is used to generate the base address of a nested descriptor; and the "Size" parameter is used during base address computation for nested descriptors (this parameter is needed for indexed array addressing only). Second, the size (in bits) of all ADT and AGT fields have been specified in parentheses.

From the field sizes in Figure 12, we see that each ADT entry is 18 bytes wide, while each AGT entry is 8 bytes wide. To determine the total size of the ADT and AGT, we must also select the number of entries. The number of ADT entries should be selected to accommodate the LDS descriptors, and the number of AGT entries should be selected to accommodate AGT activation. We have found that for the benchmarks used in our evaluation, 75 and 128 entries are sufficient for the ADT and AGT, respectively. Consequently, the ADT is 1.32 Kbytes and the AGT is 1 Kbytes. (Later, in Section 8.5, we will vary table size and study the impact on performance).

Figure 12 also shows two functional units, the *Next Address Computation Unit* (NACU) and the *Base Address Computation Unit* (BACU), for computing addresses during LDS traversal. The NACU consists of a 32x32 adder, 2 incrementers, and 1 decrementer, and is responsible for computing the address stream for active AGT entries. Every cycle, the NACU selects a single active AGT entry, computes its next address, and writes the new address back into the AGT (wires labeled

"1"). Computed addresses are also issued to the memory system for prefetching (wire labeled "2"). In addition, the NACU compares the AGT entry's *Index* to its corresponding *Length* parameter (wires labeled "3"), and deactivates the AGT entry if the address stream is exhausted. Every time the NACU computes a new address for an AGT entry that has nested child descriptors, it forwards the address to the BACU (wires labeled "4"). The BACU consists of a 32x8 multiplier and a 32x32 adder, and is responsible for activating AGT entries for nested descriptors (see Section 5.2 for a discussion on AGT entry activation). For each address forwarded from the NACU, the BACU computes a new base address using descriptor parameters (wires labeled "5"), and activates a new AGT entry (wire labeled "6"). As described in Section 5.2, AGT entry activation can also occur when the processor executes an *INIT(ID)* instruction; the wires labeled "7" perform this action.

Both the NACU and BACU have modest hardware complexity. An important question, however, is how many units are necessary to sustain an adequate prefetch throughput? Surprisingly, even with an 128-entry AGT, we have found that a single NACU and a single BACU is sufficient. Address computation is not the bottleneck in multi-chain prefetching. In fact, we have observed in our experiments that the prefetch engine is idle most of the time waiting for long-latency memory operations to complete. Given that address generation concurrency is not important, the functional units contribute very little to the cost of the prefetch engine.

Finally, the last major hardware component in the prefetch engine is the prefetch buffer, shown in Figure 10. The prefetch buffer should be large enough to hold all prefetched data prior to their access by the processor. Too small a prefetch buffer can lead to thrashing, defeating the benefits of prefetching. We have found that for the benchmarks used in our evaluation, a 1 Kbyte prefetch buffer provides good performance. (Later, in Sections 8.3 and 8.5, we study the thrashing problem and the performance impact of varying prefetch buffer size).

In summary, our prefetch engine consumes roughly 4.32 Kbytes of on-chip RAM. In addition, it requires combinational logic to implement the functional units, consisting of 2 32x32 adders, a 32x8 multiplier, 2 incrementers, and a decrementer. Overall, we find the hardware complexity of the prefetch engine to be modest.

# 6 Compiler Support

Sections 3 through 5 presented the algorithms and hardware for performing multi-chain prefetching based on our LDS descriptor framework. An important question is how are the LDS descriptors constructed? Also, how is the software support (*i.e.* the *INIT* and *SYNC* instructions, and the ADT initialization code) instrumented? One approach is to rely on the programmer to carry out these tasks. Unfortunately, this approach is ad hoc and error prone, and requires significant programmer effort. A more desirable approach is to develop systematic algorithms for performing these tasks and to implement them in a compiler, thus automating multi-chain prefetching.

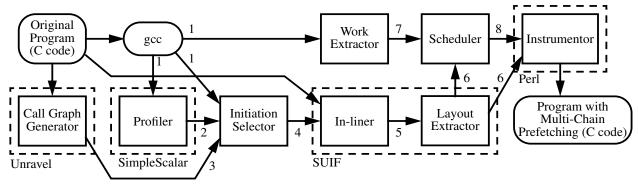

This section addresses the compiler support necessary to automate multi-chain prefetching. Our approach consists of three major steps. First, we analyze the program structure to determine where to initiate prefetching. Second, for each selected prefetch initiation site, we extract an LDS descriptor graph. Finally, from the extracted LDS descriptors, we compute the scheduling information following the algorithms already presented in Section 4, and instrument the application code. The following sections discuss these compiler steps in detail. Sections 6.1 and 6.2 introduce the algorithms for performing the first two steps. Then, Section 6.3 describes a prototype compiler that implements all of our algorithms, and performs the necessary software instrumentation.

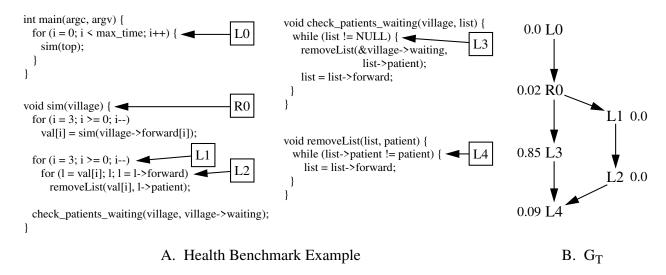

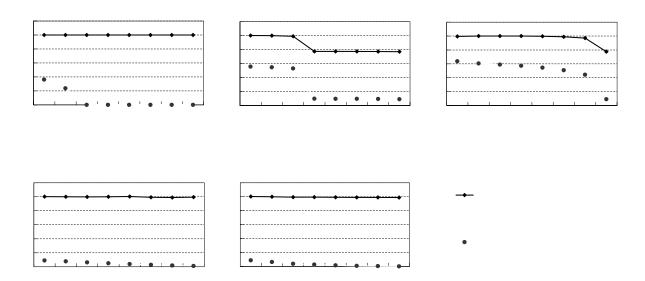

Figure 13: Constructing a traversal nesting graph. A. Kernel code from the Health benchmark. Boxed labels indicate the possible prefetch initiation sites. B.  $G_T$  annotated with cache-miss breakdowns acquired via profiling.

#### 6.1 Prefetch Initiation

The first step that a compiler for multi-chain prefetching must perform is to determine where to initiate prefetching. For simplicity, we only permit prefetch initiation immediately prior to a loop or a call to a recursive function, *i.e.* at a point in the program where a new LDS traversal begins. To provide the information necessary for identifying such prefetch initiation sites, we build a data structure called the traversal nesting graph, or  $G_T$ .  $G_T$  is a directed acyclic graph whose nodes represent loops or recursive functions defined in the source code, and whose edges connect those nodes corresponding to loops or recursive functions that are nested. Hence,  $G_T$  reflects the nesting structure of all possible prefetch initiation sites in a program. Moreover, we construct  $G_T$  globally, so its edges capture nesting relationships across procedures as well as within procedures.

Figure 13 illustrates  $G_T$  for the Health benchmark. In Figure 13A, a kernel code from Health consisting of 4 functions is shown. For readability, only function headers, loops, and function call sites appear in the figure. The boxed labels indicate the 5 loops ("L0" through "L4") and recursive function ("R0") that are candidates for prefetch initiation. In Figure 13B, the corresponding  $G_T$  for this code is shown. The graph reports the nesting structure of the possible prefetch initiation sites identified in Figure 13A. (Note, in our example, we construct  $G_T$  for the kernel code only; the actual analysis would consider the entire Health benchmark).

After constructing  $G_T$ , we compute the set of prefetch initiation sites, which we call P. Figure 14 presents our algorithm for computing P given  $G_T$ . The main procedure in our algorithm, select\_prefetch\_sites, visits every node, N, in  $G_T$  (lines 2 and 18), and considers nodes for initiating prefetching based on two criteria. First, only nodes corresponding to LDS traversals that incur a significant number of cache misses are considered. This minimizes runtime overhead, thus increasing the potential performance gain of prefetching. Unfortunately, accurately predicting cache-miss behavior from static information alone  $(e.g.\ G_T)$  is difficult; hence, we augment our static analysis with profiling. We built a profiling tool, which we will describe in Section 6.3, that breaks down the total cache misses into the fraction incurred by each loop and recursive function, and annotates the corresponding nodes in  $G_T$  with the breakdown values. As an example, the

```

select_prefetch_sites(G<sub>T</sub>)

no_gain(N)

overlap(N, P)

Given: G<sub>T</sub> node, N, set of prefetch

Given: G<sub>T</sub> node, N

Given: traveresal nesting graph, G<sub>T</sub>

Compute: potential for gain

initiation sites, P

Compute: prefetch initiation sites, P

Compute: nesting conflict

1: P = Φ:

19: if ((cache_miss(N) < 0.01) \parallel

31: do {

2: do {

(no_pointer_references(N)))

32.

if (nested(N, S) || nested(S, N))

if (no_gain(N) || too_complex(N))

21.

return TRUE:

3:

33.

return TRUE:

continue:

22: else

34: \} \forall S \text{ in P};

23:

return FALSE;

5:

if (recursive(N) && (fanout(N) > 1)) {

35: return FALSE;

if (!(overlap(N, P)))

P = P \cup \{N\};

7:

8:

} else {

too_complex(N)

9:

Q = \Phi:

Given: G<sub>T</sub> node, N

10:

do {

Compute: too complex for prefetch engine?

if (!(too\_complex(M)) &\& !(overlap(M, P \cup Q)))

11:

12:

Q = Q \cup \{M\};

24: if (no_loop_induction(N) ||

13:

\} \forall M \text{ that is a parent of } N \text{ in } G_T;

25:

contains_goto_statements(N) ||

if ((Q == \Phi) \&\& !(overlap(N, P)))

complex_address generation(N) ||

14:

26:

27.

data_dependent_traversal(N))

15:

Q = \{N\};

P = P \cup Q;

28:

return TRUE;

16:

29: else

17:

18: \forall N in G<sub>T</sub> from most to least cache_miss(N);

30:

return FALSE;

```

Figure 14: Algorithm for computing the set of prefetch initiation sites, P, from the traversal nesting graph,  $G_T$ .

cache-miss breakdowns acquired by our profiling tool for Health are annotated in the  $G_T$  from Figure 13B. For every node in  $G_T$  visited by select\_prefetch\_sites, our algorithm examines the corresponding cache-miss breakdown annotation (line 19). If this value is below 1%, we skip over the node and do not consider it further for prefetch initiation (lines 3 and 4).

Second, only nodes corresponding to LDS traversals that are implementable in the prefetch engine are considered for prefetch initiation. As described in Section 5, our prefetch engine can only perform static traversals involving simple address computation and memory indirection. Hence, our algorithm analyzes the loops and recursive functions corresponding to each visited node in  $G_T$ , and skips over nodes that perform traversals too complex for our prefetch engine (lines 3 and 4). Specifically, we skip nodes that perform unstructured traversals (lines 24 and 25), traversals containing complex address computations (line 26), and data dependent traversals (line 27).

For every node, N, that satisfies both our performance and complexity criteria, we choose one or more nodes in  $G_T$  to initiate prefetching for N. The primary factor affecting this choice is memory parallelism: prefetching should be initiated from a point where sufficient memory parallelism exists to tolerate the (potentially serialized) cache misses incurred within N. The node that best provides this memory parallelism depends on N's LDS traversal type. If node N represents a recursive function that pursues multiple child pointers at each level of recursion (i.e. its "fanout" is greater than 1), then we assume N performs a tree traversal. Tree traversals contain significant memory parallelism since the sub-trees at each tree node can be pursued in parallel. Hence, in this case, we select node N itself for initiating prefetching (lines 5 and 7). (Note, recursive functions with a fanout equal to 1 are treated as linked list traverals, and are discussed next).

The situation is different if node N represents a loop. For pointer-chasing loops that traverse linked lists (*i.e.* the induction variable update is of the form ptr=ptr->next), all pointer accesses in N are serialized, and there is no memory parallelism. For affine loops that traverse non-recursive ribs (*i.e.* the induction variable update is of the form i+=constant, but the loop body dereferences

$<sup>^3</sup>$ We chose 1% arbitrarily; any small fraction would suffice. Our intention is simply to skip over traversals that contribute an insignificant number of cache misses.

pointers derived from the induction variable), all pointer accesses within a single iteration of N are serialized, and there is only limited memory parallelism.<sup>4</sup> In both cases, our algorithm assumes there is insufficient memory parallelism within node N alone to effectively tolerate the pointer-chasing cache misses. Rather than select node N, our algorithm instead considers all nodes M that are parents of N in  $G_T$  (lines 10 and 13). We select every node M that meets our traversal complexity criterion (line 11), adding it to the set of prefetch initiation sites (lines 12 and 16). By initiating prefetching from N's parents, the degree of memory parallelism is increased since multiple instances of N can be prefetched simultaneously. In the event that none of N's parents meet the traversal complexity criterion, we just choose N itself (lines 14 and 15). This ensures that N will be prefetched, even if it is from a point in  $G_T$  that provides only limited memory parallelism. Lastly, in addition to the two looping cases described above, there is a third case: node N may represent a loop that contains no pointer-chasing references whatsoever (line 20). Since our technique focuses on LDS traversals, we simply skip over all such nodes (lines 3 and 4).

Finally, it is possible for our algorithm to select two or more prefetch initiation sites that are nested in  $G_T$ . Nested prefetch initiation leads to multiple traversals of the same data structures. To avoid such redundant prefetching, our algorithm calls the procedure overlap each time it discovers a new node for initiating prefetching (lines 6, 11, and 14). overlap checks if the candidate node, N, has a nesting conflict with any node currently in P (lines 31–34), and includes N in P only if no nesting conflicts are found. Note, if N is included in P, all parents of N in  $G_T$  become unprefetchable since they will have nesting conflicts with N and cannot be selected for prefetch initiation. (While the children of N similarly cannot be selected for prefetch initiation, they will get prefetched from the prefetch initiation site at N, as we will see in Section 6.2). However, since our algorithm considers nodes in descending order of their cache-miss annotations (line 18), the most important nodes are highly likely to be prefetched.

Applying our algorithm to Figure 13B, nodes "L0," "L1," and "L2" are skipped since their cache-miss breakdown annotations are less than 1%. The remaining nodes are considered in the order of their annotation values, "L3," "L4," and "R0," to select the prefetch initiation nodes. (Note, all nodes in Figure 13B meet the complexity criteria, but ascertaining this requires analyzing more code than has been provided in Figure 13A). For "L3," our algorithm selects "R0." For "L4," our algorithm tries to select "L3," but fails because of a nesting conflict with the already selected "R0." And for "R0," our algorithm selects "R0" again. Hence, the final solution is  $P = \{R0\}$ .

# 6.2 LDS Descriptor Graphs

After computing the set of prefetch initiation sites, P, the next step that a compiler for multichain prefetching must perform is to extract the LDS descriptor graphs—one for each node, N, in P. We begin this step by constructing code fragments from which our compiler will extract the LDS descriptor graphs. Each code fragment contains the code corresponding to a node, N, in P as well as the nodes nested underneath N in  $G_T$  whose cache-miss breakdown annotations meet the minimum threshold (1%). By including all such LDS traversal codes, we ensure the LDS descriptor graph eventually extracted from the code fragment will provide prefetching for all the loops and recursive functions associated with node N that incur a large number of cache misses. It is important to note these code fragments are not part of the application; they are constructed for the sole purpose of extracting LDS descriptor graphs, and are discarded afterwards.

$<sup>^4</sup>$ In this case, there is memory parallelism between iterations of N since the induction variable updates are not serialized. However, if the loop executes a small number of iterations, which is common in affine loops from non-numeric programs, there is typically not enough memory parallelism for our technique to provide performance gains.

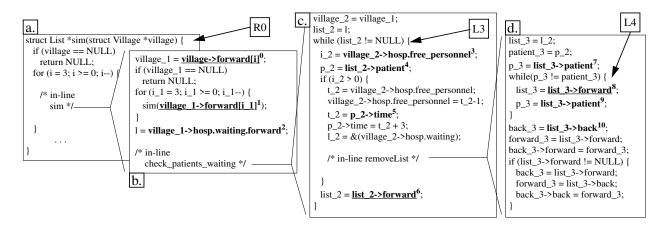

Figure 15: Construction of a code fragment for the Health benchmark. a. Code for sim containing "R0." b. In-lining of recursive call to sim. c. In-lining of check\_patients\_waiting containing "L3." d. In-lining of removeList containing "L4."

Figure 15 illustrates the construction of a code fragment for the Health benchmark example. As described in Section 6.1, "R0" is selected as the prefetch initiation site for Health. And as shown by the  $G_T$  graph in Figure 13B, "L3" and "L4" are nested underneath "R0," and have > 1% cache-miss breakdown annotations. Hence, we construct a code fragment starting at sim, the procedure containing "R0," and include check\_patients\_waiting and removeList, the procedures containing "L3" and "L4," respectively. Figures 15a, c, and d show the contents of these procedures (they are simply more complete versions of the procedures shown in Figure 13).