### University of Tennessee, Knoxville

# TRACE: Tennessee Research and Creative **Exchange**

**Doctoral Dissertations**

Graduate School

8-2015

# A GHz-range, High-resolution Multi-modulus Prescaler for **Extreme Environment Applications**

Benjamin Matthew McCue University of Tennessee - Knoxville, bmccue@utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

McCue, Benjamin Matthew, "A GHz-range, High-resolution Multi-modulus Prescaler for Extreme Environment Applications. " PhD diss., University of Tennessee, 2015. https://trace.tennessee.edu/utk\_graddiss/3444

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Benjamin Matthew McCue entitled "A GHz-range, High-resolution Multi-modulus Prescaler for Extreme Environment Applications." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Benjamin J. Blalock, Major Professor

We have read this dissertation and recommend its acceptance:

Charles Britton, Jeremy Holleman, Jayson Hayward

Accepted for the Council:

Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# A GHz-range, High-resolution Multi-modulus Prescaler for Extreme Environment Applications

A Dissertation Presented for the

Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Benjamin Matthew McCue

August 2015

Copyright © 2015 by Benjamin McCue All rights reserved In loving memory of

Larry T. Petrowski & David D. McCue

### **ACKNOWLEDGEMENTS**

I would like to express my utmost gratitude to my advisor Dr. Benjamin Blalock for all his guidance and support as I worked toward completing this dissertation. Dr. Blalock has always demonstrated the highest level of commitment to his students. I enjoyed my entire time studying under Dr. Blalock, and I am very thankful I was fortunate enough to have him as my advisor.

I would also like to thank my committee members, Dr. Charles Britton, Dr. Jeremy Holleman, and Dr. Jason Hayward for their feedback and expertise while guiding me through the dissertation process. A special thanks goes to Dr. Britton as he has been an indispensable advisor during my entire tenure at the University of Tennessee.

I enjoyed working with all of the students in the Integrated Circuits and Systems

Laboratory (ICASL) and thank them for their support and insights, as well as their friendship. I

am also grateful for the assistance and support I received from the E.E.C.S. department

(especially the administrative personnel), as they helped me stay on track to complete my

education.

I am very grateful to Frequency Management International (FMI) for the technical and financial support they provided toward this research effort. FMI provide support above and beyond the requirements of the research contract, which allowed this dissertation to be possible.

Most of all, I would like to thank my family for all their love and support during my education. My wife, Jenna, has unwaveringly supported me during this long, challenging process and my gratitude to her cannot be understated. Finally, I would like to thank my father-in-law, Larry Petrowski, and my father, David, for demonstrating to me what it is to be a man. These two men exemplified integrity and character their entire lives, and I am eternally grateful for their influence on my life. We love and miss you both.

### **ABSTRACT**

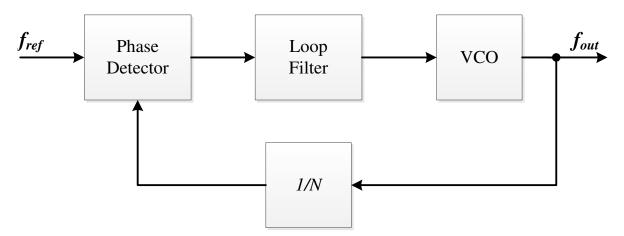

The generation of a precise, low-noise, reliable clock source is critical to developing mixed-signal and digital electronic systems. The applications of such a clock source are greatly expanded if the clock source can be configured to output different clock frequencies. The phase-locked loop (PLL) is a well-documented architecture for realizing this configurable clock source. Principle to the configurability of a PLL is a multi-modulus divider. The resolution of this divider (or prescaler) dictates the resolution of the configurable PLL output frequency. In integrated PLL designs, such a multi-modulus prescaler is usually sourced from a GHz-range voltage-controlled oscillator. Therefore, a fully-integrated PLL ASIC requires the development of a high-speed, high-resolution multi-modulus prescaler.

The design challenges associated with developing such a prescaler are compounded when the application requires the device to operate in an extreme environment. In these extreme environments (often extra-terrestrial), wide temperature ranges and radiation effects can adversely affect the operation of electronic systems. Even more problematic is that extreme temperatures and ionizing radiation can cause permanent damage to electronic devices. Typical commercial-off-the-shelf (COTS) components are not able withstand such an environment, and any electronics operating in these extreme conditions must be designed to accommodate such operation.

This dissertation describes the development of a high-speed, high-resolution, multimodulus prescaler capable of operating in an extreme environment. This prescaler has been developed using current-mode logic (CML) on a 180-nm silicon-germanium (SiGe) BiCMOS process. The prescaler is capable of operating up to at least 5.4 GHz over a division range of 16-48 with a total of 27 configurable moduli. The prescaler is designed to provide excellent ionizing radiation hardness, single-event latch-up (SEL) immunity, and single-event upset (SEU) resistance over a temperature range of  $-180^{\circ}$ C to  $125^{\circ}$ C.

# TABLE OF CONTENTS

| CHAP | TER 1: INTRODUCTION AND GENERAL INFORMATION         | 1  |

|------|-----------------------------------------------------|----|

| 1.1  | Motivation                                          | 1  |

| 1.2  | Research goals                                      | 4  |

| 1.3  | Dissertation overview                               | 5  |

| CHAP | TER 2: PROBLEM DESCRIPTION                          | 7  |

| 2.1  | Extreme environment frequency synthesizer overview  | 7  |

| 2.2  | Multi-modulus prescaler design considerations       | 10 |

| 2.3  | Frequency synthesizer ASIC development              | 11 |

| СНАР | TER 3: LITERATURE REVIEW                            | 12 |

| 3.1  | Introduction                                        | 12 |

| 3.2  | Silicon Germanium (SiGe) technology overview        | 12 |

| 3.3  | High-speed digital logic review                     | 14 |

| 3    | 3.1 Speed limitations of CMOS logic                 | 14 |

| 3    | 3.2 Current-mode logic (CML) review                 | 16 |

| 3.4  | Fractional-N division review                        | 20 |

| 3.5  | Prescaler prior art                                 | 23 |

| 3.5  | 5.1 High-speed prescaler prior art                  | 23 |

| 3.5  | 5.2 High-resolution prescaler prior art             | 29 |

| 3.5  | 5.3 Extreme environment capable prescaler prior art | 32 |

| 3.6  | Limitations of prescaler prior art                  | 40 |

| CHAP | TER 4: DESIGN OF THE MULTI-MODULUS PRESCALER        | 41 |

| 4.1  | Prescaler design approach                           | 41 |

| 4.2  | Multi-modulus prescaler functional description      | 41 |

| 4.2  | 2.1 4/5/6 divider design                            | 42 |

| 4.2  | 2.2 3.5-8 divider design                            | 47 |

| 4.3  | Prescaler 4/5/6 divider cell development            | 52 |

| 4.3  | 3.1 4/5/6 divider DFF                               | 53 |

| 4.3  | 3.2 4/5/6 divider combinational logic               | 54 |

| VITA  |        |                                                             | 90 |

|-------|--------|-------------------------------------------------------------|----|

| REFE  | REN    | CES                                                         | 86 |

| 6.3   | Co     | nclusion                                                    | 84 |

| 6.2   | Po     | tential directions for future work                          | 82 |

| 6.1   | Or     | iginal contributions of this research                       | 82 |

| CHAP  | TER    | 6: CONCLUSION                                               | 82 |

| 5.6   |        | escaler error-correction testing                            |    |

| 5.5   |        | sting of frequency synthesizer ASIC with embedded prescaler |    |

| 5.4   |        | Prescaler phase noise measurements                          |    |

| 5.4   |        | VCO phase noise measurements                                |    |

| 5.4   |        | escaler and VCO phase noise measurements                    |    |

| 5.3   |        | mperature and supply voltage testing                        |    |

| 5.2   |        | Prescaler input frequency locking range                     |    |

| 5.2   |        | Prescaler functionality demonstration                       |    |

| 5.2   | Ro     | om-temperature functionality testing                        |    |

| 5.1   |        | Test board and set-up description                           |    |

| 5.1   | 1.1    | Prescaler test ASIC description                             | 66 |

| 5.1   | De     | scription of multi-modulus prescaler testing                | 66 |

| ••••• | •••••• |                                                             | 66 |

|       |        | 5: TESTING AND ANALYSIS OF THE MULTI-MODULUS PRESCAI        |    |

| 4.8   |        | ncluding remarks                                            |    |

| 4.7   |        | ols used in this research                                   |    |

| 4.6   |        | ysical implementation of the multi-modulus prescaler        |    |

| 4.5   |        | 3.5-8 divider simulation results                            |    |

| 4.5   |        | 4/5/6 divider simulation results                            |    |

| 4.5   | Mι     | ulti-modulus prescaler simulations                          |    |

| 4.4   |        | 3.5-8 divider DFF                                           |    |

| 4.4   | Pre    | escaler 3.5-8 divider cell development                      | 56 |

|       |        |                                                             |    |

# LIST OF TABLES

| Table 1. Attributes required of extreme environment, precision frequency synthesizer | 4  |

|--------------------------------------------------------------------------------------|----|

| Table 2. Frequency synthesizer ASIC technical objectives                             | 7  |

| Table 3. Multi-modulus prescaler design specifications                               | 11 |

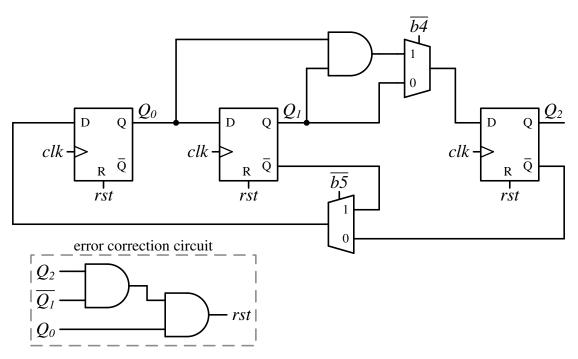

| Table 4. 4/5/6 divider state tables for each configuration                           | 45 |

| Table 5. Faulty states for each configuration of the 4/5/6 divider                   | 46 |

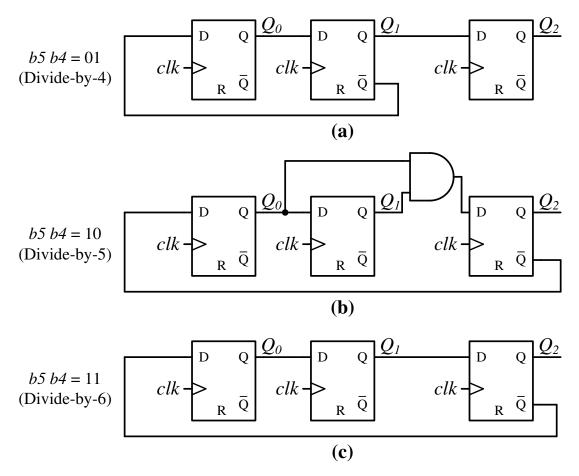

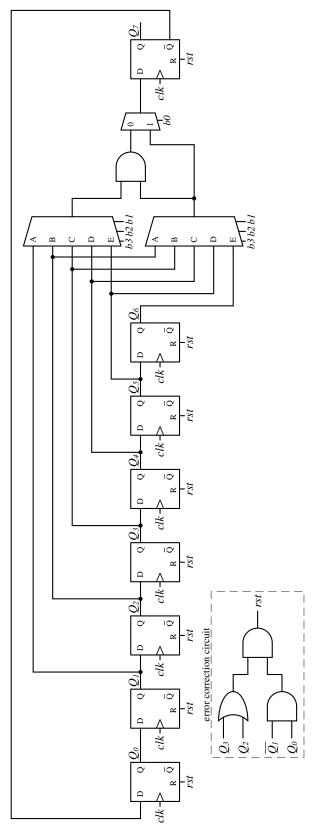

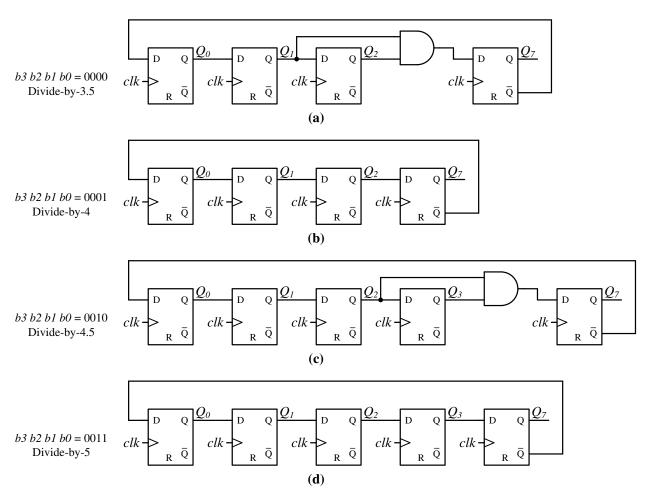

| Table 6. Divide-by-4.5 configuration example of faulty and erroneous state analysis  | 50 |

| Table 7. State table of the 3.5-8 divider from Figure 49                             | 81 |

# LIST OF FIGURES

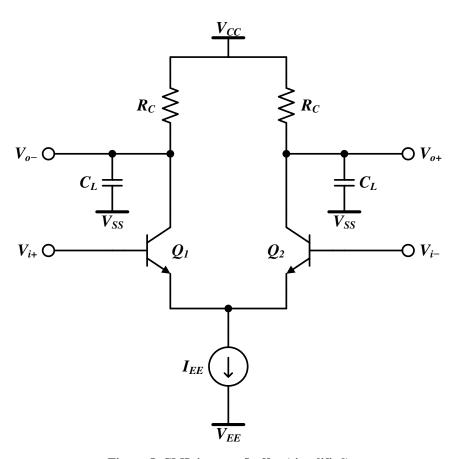

| Figure 1. Basic functionality of a phase-locked loop                                       | 1           |

|--------------------------------------------------------------------------------------------|-------------|

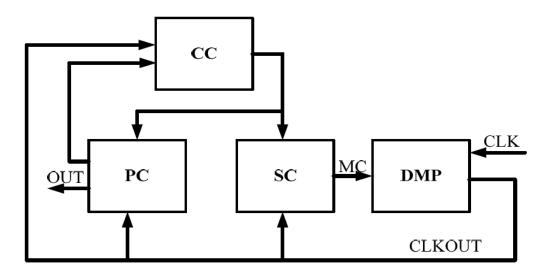

| Figure 2. Frequency synthesizer ASIC functional diagram                                    | 8           |

| Figure 3. PLL core functional diagram (simplified)                                         | 10          |

| Figure 4. Standard CMOS inverter (a) with equivalent model (b)                             | 15          |

| Figure 5. CML inverter/buffer (simplified)                                                 | 17          |

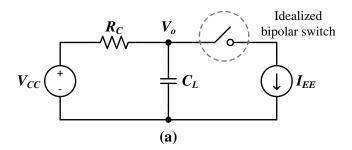

| Figure 6. CML inverter/buffer (a) equivalent model using ideal switch, (b) equivalent      | model just  |

| before output LOW to HIGH, (c) equivalent model after output LOW to HIGH                   | ł19         |

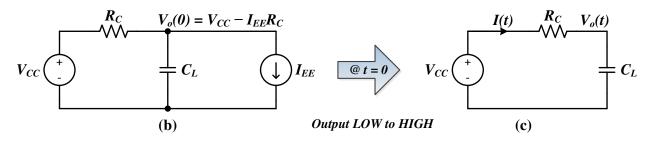

| Figure 7. Integer-N phase-locked loop                                                      | 21          |

| Figure 8. Phase-locked loop with dual-modulus prescaler                                    | 22          |

| Figure 9. D-flip-flop used in prescaler in [22]                                            | 23          |

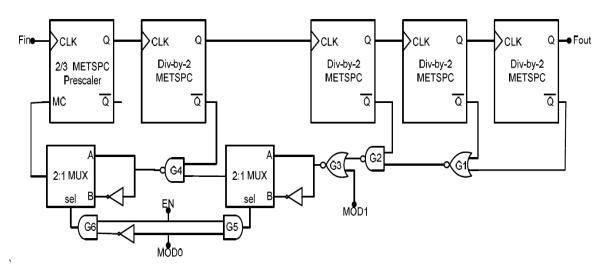

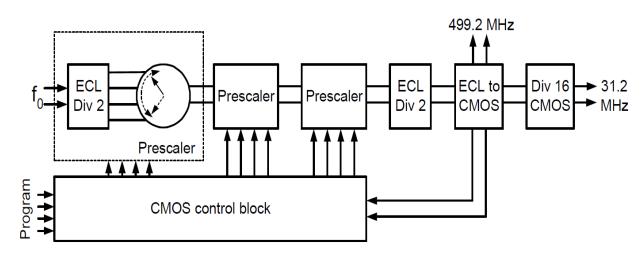

| Figure 10. Diagram of 8-modulus prescaler in [22]                                          | 24          |

| Figure 11. Diagram of divide-by-64~79 prescaler of [23]                                    | 25          |

| Figure 12. D-flip-flop designs of [23] (a) without and (b) with merged NAND gate           | 27          |

| Figure 13. Diagram of multi-modulus 32/33/39/40/47/48 prescaler of [24]                    | 28          |

| Figure 14. Diagram of frequency divider described in [25]                                  | 29          |

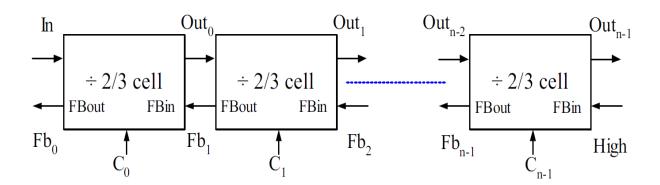

| Figure 15. Diagram of cascade-based prescaler of [26]                                      | 30          |

| Figure 16. Diagram of programmable frequency divider of [27]                               | 31          |

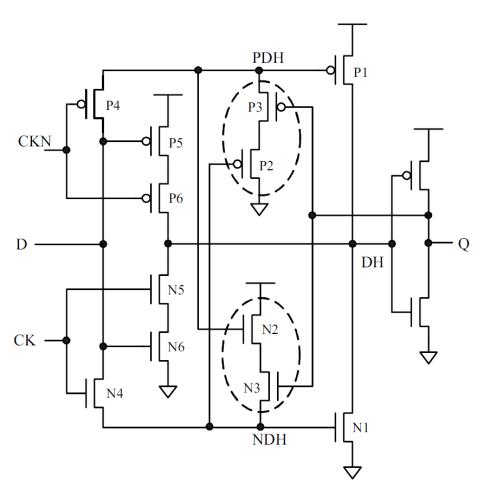

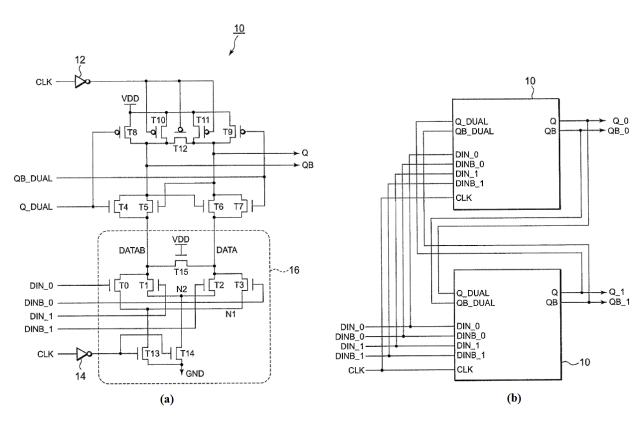

| Figure 17. SEU-tolerant latch circuit proposed in [32]                                     | 33          |

| Figure 18. SEU-tolerant divide-by-2 cell of [32]                                           | 34          |

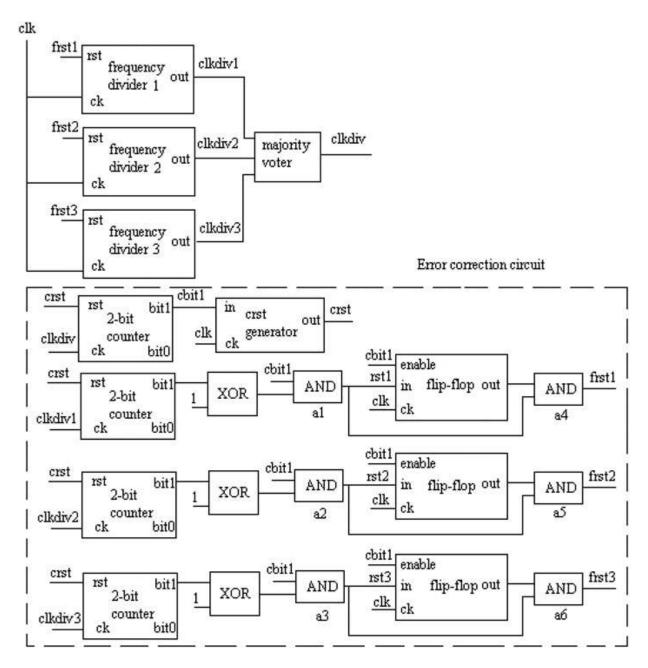

| Figure 19. SEU-tolerant frequency divider of [33]                                          | 36          |

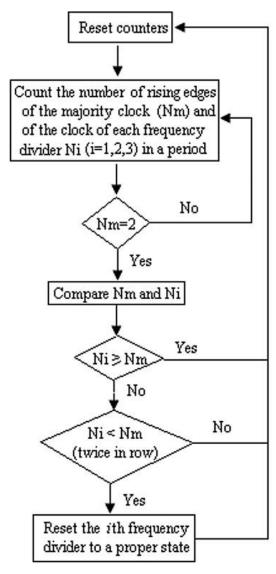

| Figure 20. State machine of the error correction circuit of [33]                           | 37          |

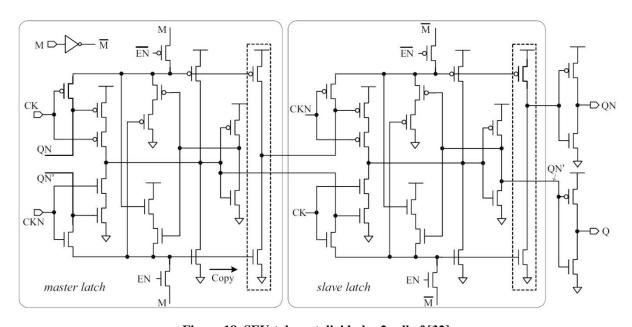

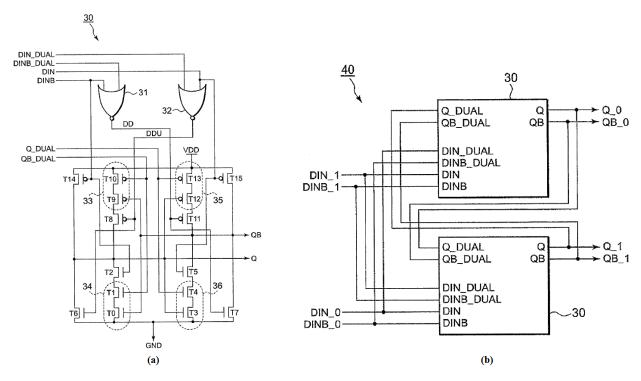

| Figure 21. Radiation-hardened master latch of [34] (a) schematic of one half of master     | r latch (b) |

| diagram of master latch using two half circuits (a)                                        | 38          |

| Figure 22. Radiation-hardened slave latch of [34] (a) schematic of one half of slave la    | tch (b)     |

| diagram of slave latch using two half circuits of (a)                                      | 39          |

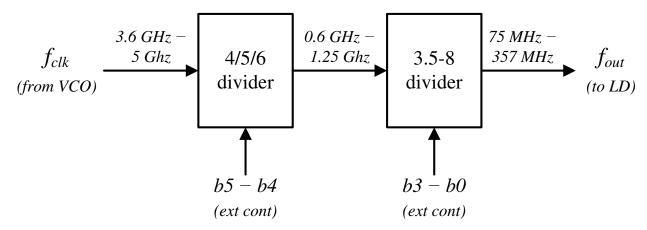

| Figure 23. Multi-modulus prescaler block diagram with external control bits b5 - b0        | 42          |

| Figure 24. 4/5/6 divider block diagram                                                     | 43          |

| Figure 25. 4/5/6 divider diagram for (a) divide-by-4, (b) divide-by-5, and (c) divide-by-5 | y-6         |

| configurations (simplified)                                                                | 44          |

| Figure 26. 3.5-8 divider block diagram                                                     | 48          |

| Figure 27. 3.5-8 divider diagram for (a) divide-by-3.5, (b) divide-by-4, (c) divide-by-4.5, and          | (d)  |

|----------------------------------------------------------------------------------------------------------|------|

| divide-by-5 configurations (simplified)                                                                  | 49   |

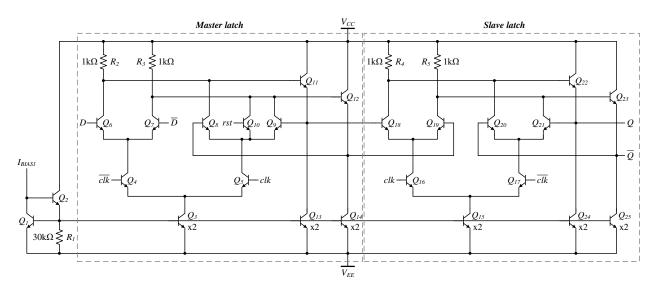

| Figure 28. DFF of 4/5/6 divider (all bipolars – npn-HBTs of 1 µm x 0.24 µm emitter area, all             |      |

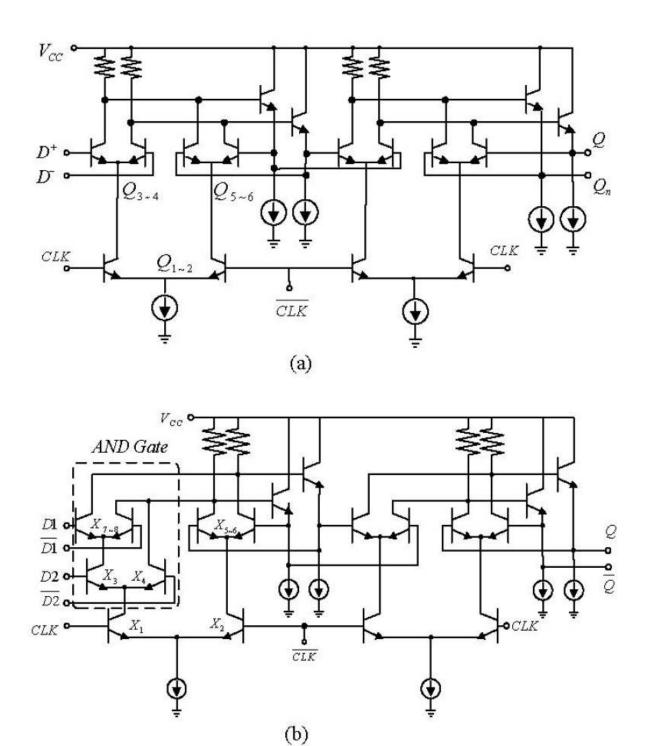

| resistors – polysilicon type, $I_{BIASI} = 100 \mu\text{A}$ )                                            | 53   |

| Figure 29. AND gate of 4/5/6 divider (all bipolars – npn-HBTs of 1 μm x 0.24 μm emitter are              | ea,  |

| all resistors – polysilicon type, $I_{BIASI} = 100 \mu\text{A}$ )                                        | 55   |

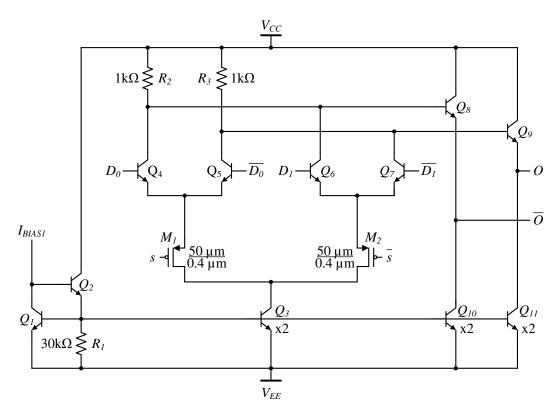

| Figure 30. Multiplexer of 4/5/6 divider (all bipolars – npn-HBTs of 1 $\mu$ m x 0.24 $\mu$ m emitter and | rea, |

| all resistors – polysilicon type , $I_{BIASI} = 100 \mu\text{A}$ , all MOSFETs – 3.3 V PFETs)            | 56   |

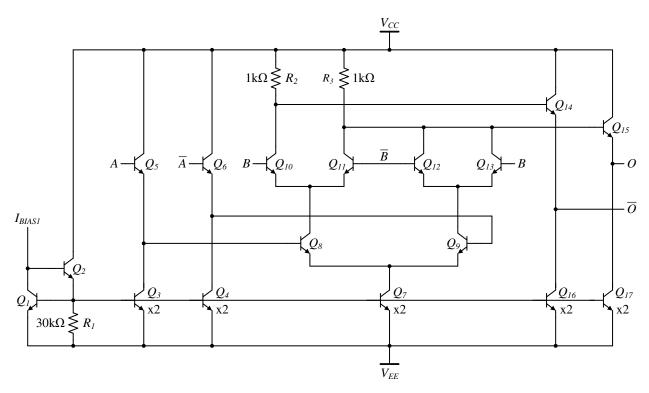

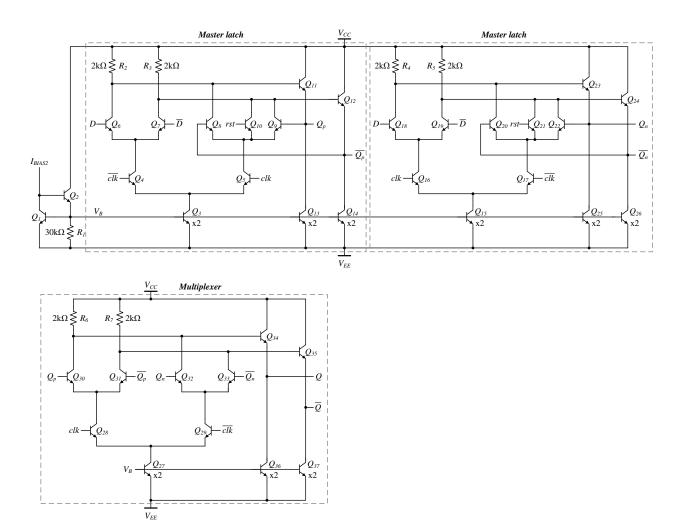

| Figure 31. DFF of 3.5-8 divider (all bipolars – npn-HBTs of 1 μm x 0.24 μm emitter area, all             |      |

| resistors – 2- $\mu$ m width, polysilicon type, $I_{BIAS2} = 50 \mu$ A)                                  | 57   |

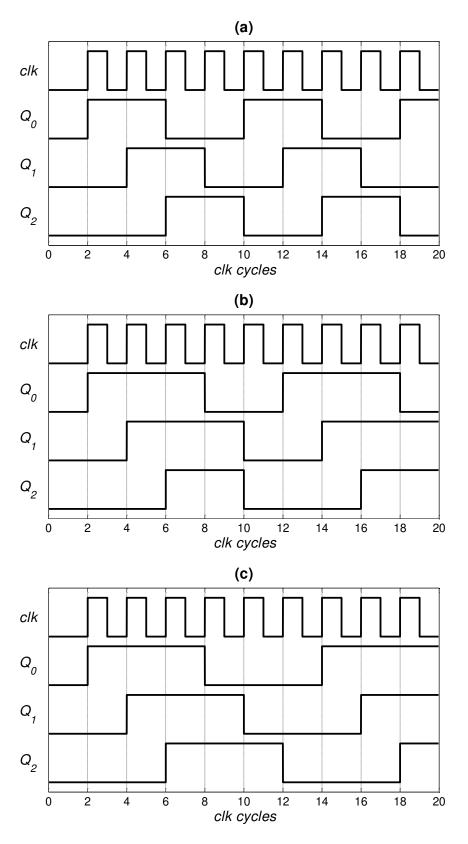

| Figure 32. 4/5/6 divider block-level simulation timing diagram for (a) divide-by-4, (b) divide-          | -by- |

| 5, and (c) divide-by-6 configurations                                                                    | 59   |

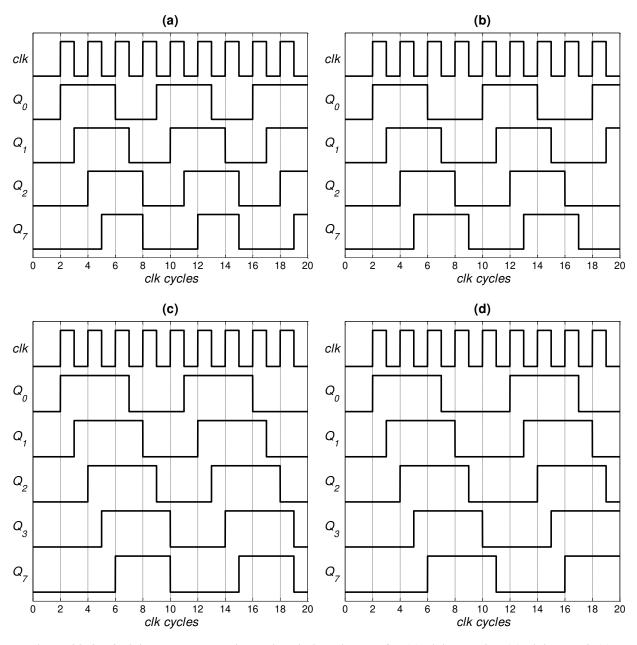

| Figure 33. 3.5-8 divider block-level simulation timing diagram for (a) divide-by-3.5, (b) divid          | le-  |

| by-4, (c) divide-by-4.5, and (d) divide-by-5 configurations                                              | 61   |

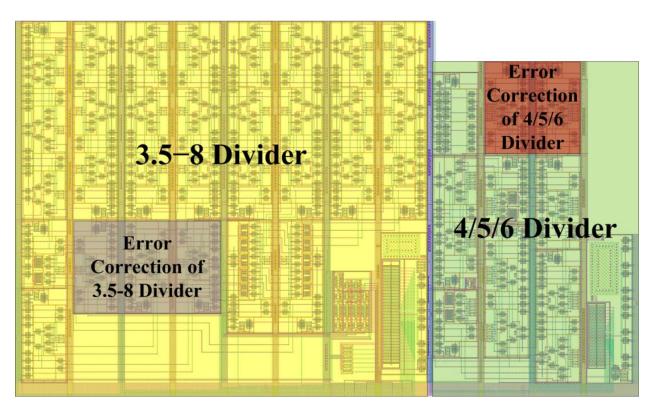

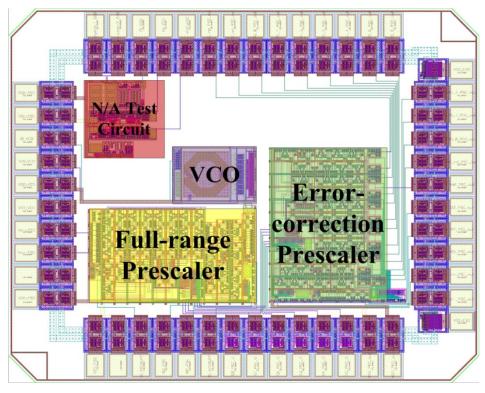

| Figure 34. Layout of complete multi-modulus prescaler (750 µm x 460 µm)                                  | 62   |

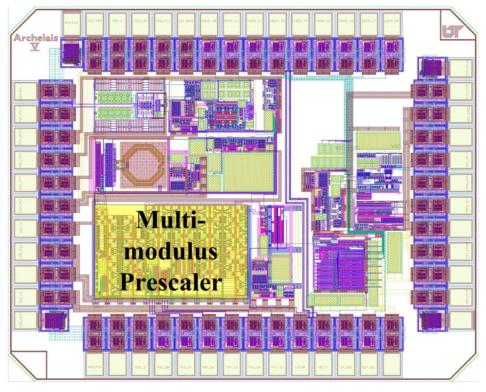

| Figure 35. Layout of frequency synthesizer ASIC, with integrated prescaler (2.2 mm x 1.8 mn              | n)   |

|                                                                                                          | 64   |

| Figure 36. Layout of prescaler test ASIC (2.2 mm x 1.8 mm)                                               | 64   |

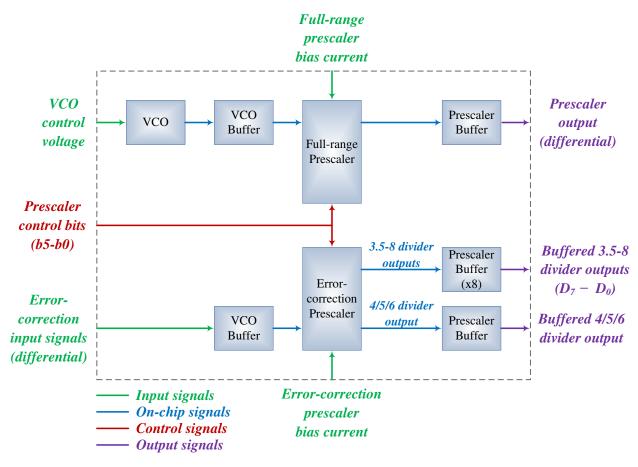

| Figure 37. Prescaler test ASIC diagram                                                                   | 67   |

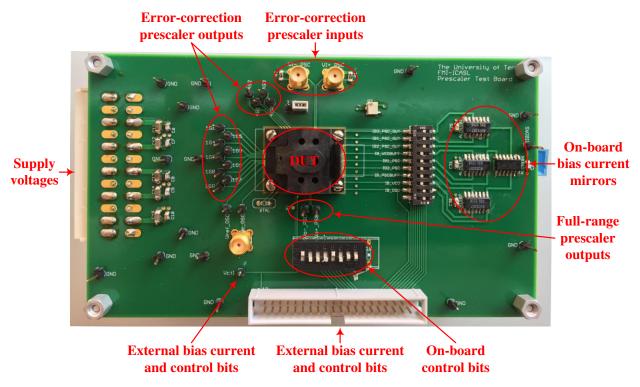

| Figure 38. Prescaler test board, 4-layer PCB design, 8 mm x 8 mm, 56-pin QFN chip socket                 | 68   |

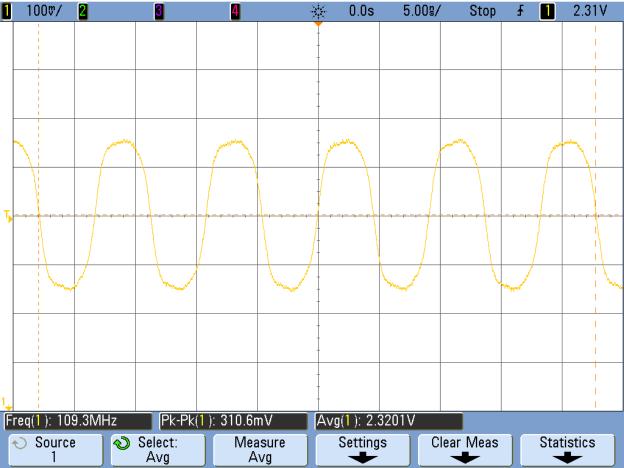

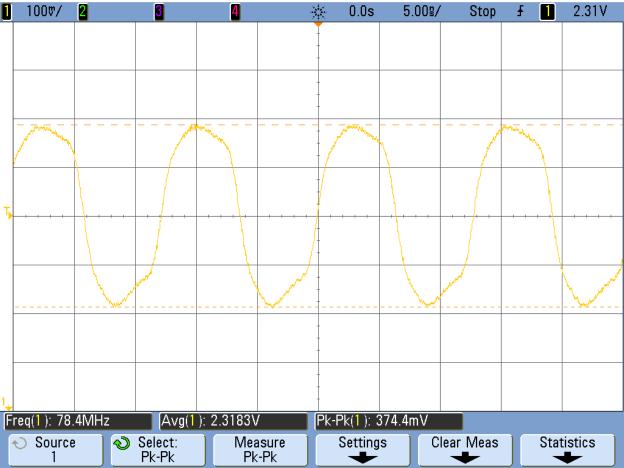

| Figure 39. Chip #1 prescaler output at room temperature driven by on-chip VCO, input                     |      |

| frequency of 5.25 GHz, prescaler division ratio $-48$ , $V_{DD} = 3.3$ V, $I_{BIAS} = 40 \mu A \dots$    | 69   |

| Figure 40. Chip #1 prescaler output at room temperature driven by on-chip VCO, input                     |      |

| frequency of 3.74 GHz, prescaler division ratio $-48$ , $V_{DD} = 3.3$ V, $I_{BIAS} = 40 \mu A \dots$    | 70   |

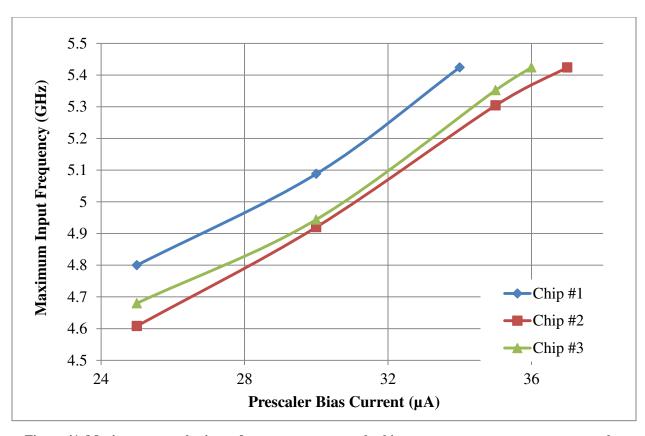

| Figure 41. Maximum prescaler input frequency over prescaler bias current, room temperature,              | ,    |

| prescaler division ratio – 48 (valid for 3.0 V to 3.6 V supply voltage range)                            | 71   |

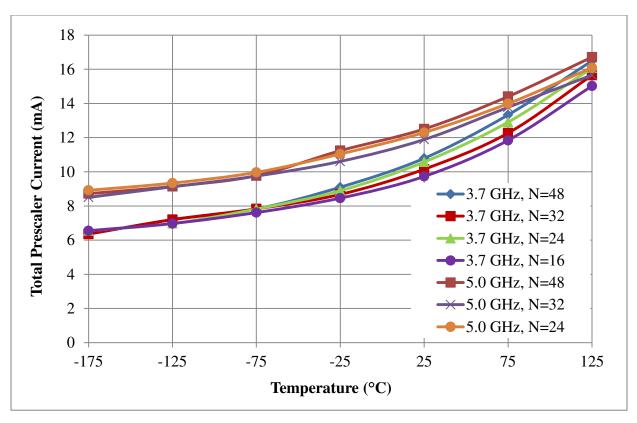

| Figure 42. Chip #2 total prescaler current consumption over temperature and division ratio (va           |      |

| for 3.0 V to 3.6 V supply voltage)                                                                       |      |

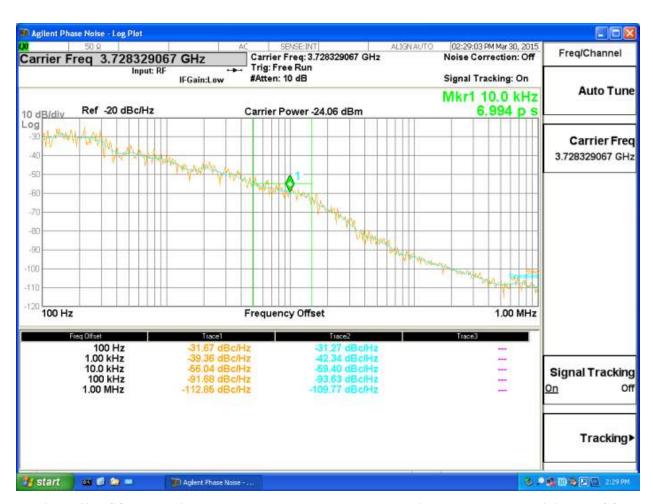

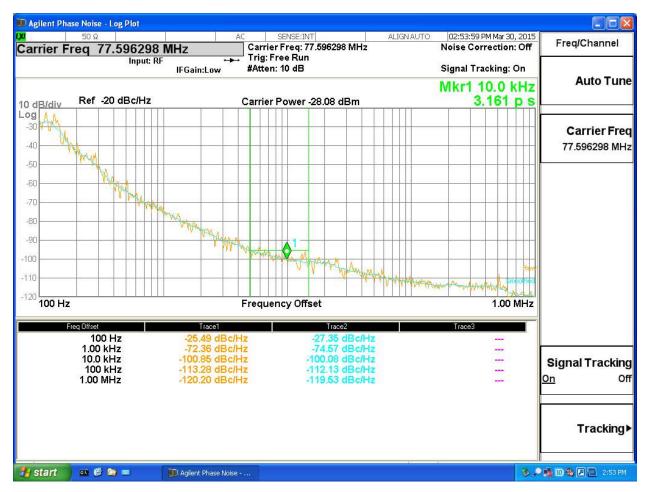

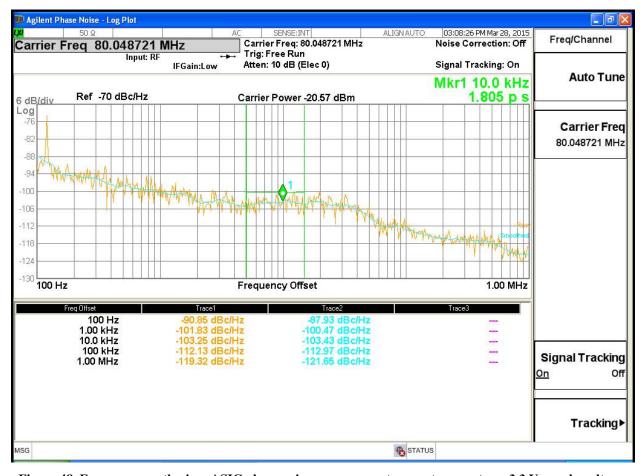

| Figure 43. VCO phase noise measurement, room temperature, nominal supply voltage, minim                  |      |

| VCO frequency                                                                                            |      |

| Figure 44. Chip #1 prescaler phase noise measurement, room temperature, 3.3 V supply voltage,       |

|-----------------------------------------------------------------------------------------------------|

| 3.7 GHz VCO frequency, prescaler division ratio – 48                                                |

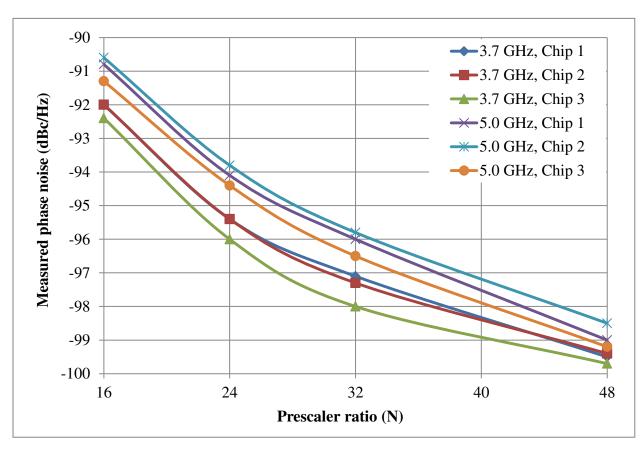

| Figure 45. Measured phase noise of prescaler driven by VCO at 10 kHz offset                         |

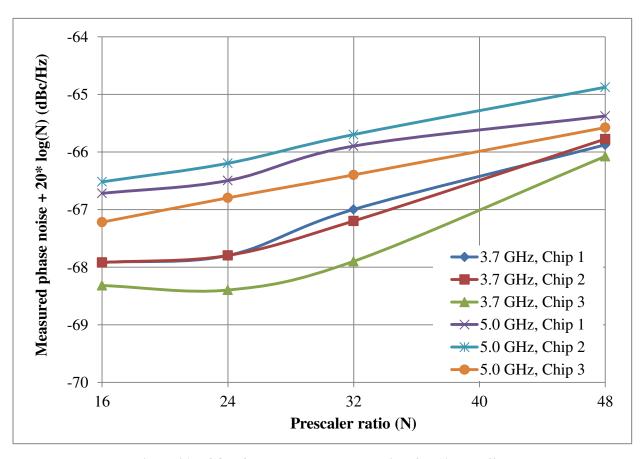

| Figure 46. VCO-referred measured phase noise of at 10 kHz offset                                    |

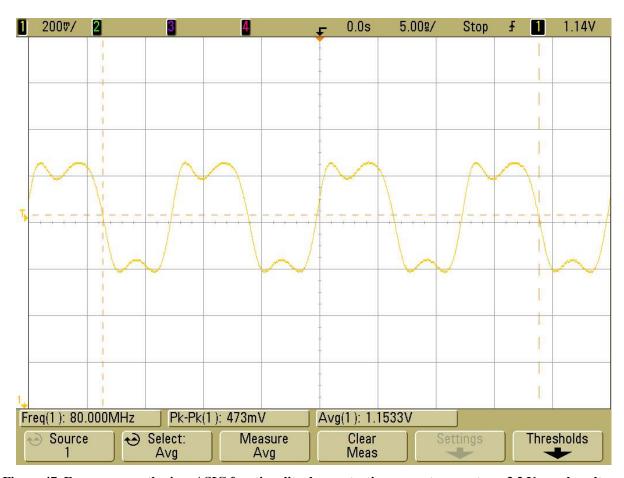

| Figure 47. Frequency synthesizer ASIC functionality demonstration, room temperature, 3.3 V          |

| supply voltage, 20 MHz crystal reference frequency, 80 MHz LVDS output (single-                     |

| ended), prescaler input (VCO) frequency of 3.84 GHz, prescaler division ratio – 48 77               |

| Figure 48. Frequency synthesizer ASIC phase noise measurement, room temperature, 3.3 V              |

| supply voltage, 20 MHz crystal reference frequency, 80 MHz output frequency, prescaler              |

| input (VCO) frequency of 3.84 GHz, prescaler division ratio – 48                                    |

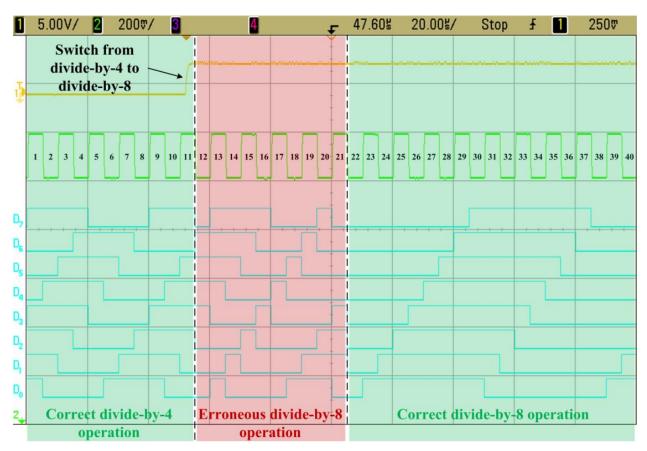

| Figure 49. Demonstration of prescaler error-correction (3.5-8 divider), top – prescaler control bit |

| (b3), middle -3.5-8 divider clock signal, bottom - 3.5-8 divider DFF digital outputs 79             |

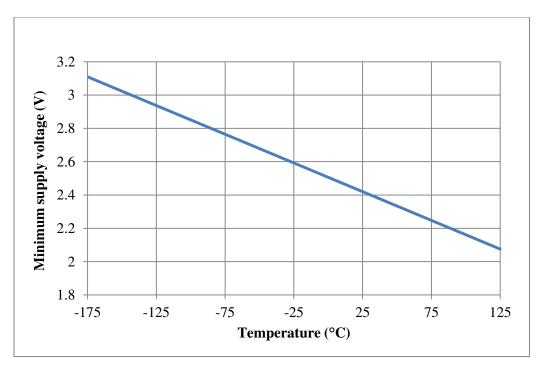

| Figure 50. Minimum supply voltage of multi-modulus prescaler (constant current bias, -1.15          |

| mV/°C base-emitter temperature coefficient)                                                         |

#### CHAPTER 1: INTRODUCTION AND GENERAL INFORMATION

#### 1.1 Motivation

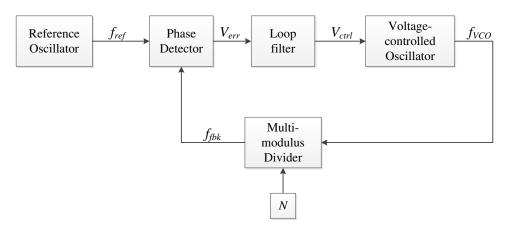

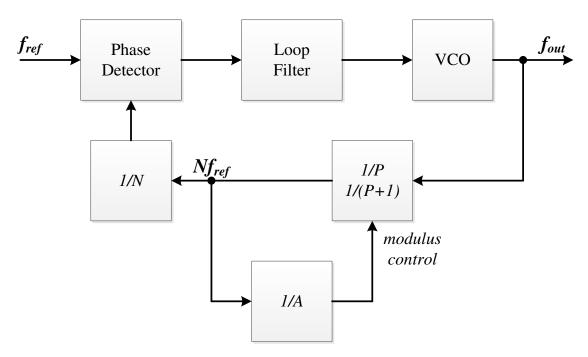

A principle requirement of many electronic systems, such as data acquisition systems, data converters, and many other systems, is the generation of a reliable clock signal. Many methods for generating such a signal have been developed over the years, with each method tailored to the specific application. Many electronic systems (particularly mixed-signal) require a very precise, low-noise clock signal. Piezo-electric crystals (quartz) can be manufactured to act as resonant LC tank circuits with a very high quality factor (Q) [1]. The high-Q parameter of quartz allows these crystals to be used to generate very low phase noise clock sources. In the time domain, phase noise manifests as jitter, or timing uncertainty associated with edge transitions of a periodic signal. One drawback to using crystal oscillator circuits as clock sources is that the oscillation frequency of these circuits cannot be changed without a physical change to the crystal. Moreover, the intrinsic quality factor of a crystal is inversely proportional to crystal resonant frequency and internal losses of the crystal limit the resonant frequency of quartz crystals to the low MHz range [1]. Therefore, there is a frequency "window" for crystal resonators before internal losses degrade performance where the maximum quality factor can be obtained. This limitation on the frequency range of crystal resonators highlights the need for a configurable system that allows user-selectable clock frequencies to be generated from a single (or set of) crystal(s). A phase-locked loop (PLL) is a well-established electronic system for accomplishing this variable frequency selection functionality [2], [3]. Figure 1 shows the basic concept of a phase-locked loop.

Figure 1. Basic functionality of a phase-locked loop

In a PLL circuit, a reference oscillator (usually a crystal oscillator) provides a reference frequency  $(f_{ref})$  for the PLL system. Another oscillator in the PLL system, a voltage-controlled oscillator (VCO), generates a second oscillation frequency ( $f_{VCO}$ ), significantly higher than the reference frequency. The phase detector, together with the feedback action of the control loop, forces the feedback frequency  $(f_{fbk})$  at the output of the multi-modulus divider to match the reference frequency. Therefore, the VCO is forced to oscillate at a frequency equal to the reference frequency multiplied by the division ratio (N) of the multi-modulus divider (provided this frequency is within the VCO tuning range). This PLL system allows the precision of the crystal resonant frequency to be extended to generate precise oscillation at frequencies other than the resonant frequency of the crystal. It is evident from the previous PLL functional description that a principle section of PLL architecture (and the section that dictates the PLL output frequency relative to the crystal frequency) is the multi-modulus divider. The set of configurable output frequencies for a given crystal frequency is determined by the available moduli of this divider. This multi-modulus divider (or prescaler) is often required to operate at very high speeds, as the nominal oscillation frequency of the VCO is usually designed to be relatively high (a desirable trait for a wide tuning range, tuning linearity, and small on-chip, passive components) [3]. It is now evident that user-configurable, precision clock generation requires an integrated, high-speed, multi-modulus divider solution.

Extreme environment applications, such as space exploration, satellite systems, and defense systems, have led to the need for the development of highly-reliable, extreme environment capable electronic systems [4], [5]. Electronics operated in space are inevitably exposed to extreme cold temperatures (often –180°C or lower) and high temperatures (often 125°C or higher) [5]. Extreme cold temperatures present several problems for electronic circuit operation, particularly precision frequency generation circuits. Reliability of semiconductor devices in extreme cold temperature is also of noted concern due to the increased generation of hot carriers that occurs at low temperatures. Specifically, the degradation of silicon MOSFET devices via hot carrier effects is a well-established phenomenon. Hot carrier injection into the oxide layer of a MOSFET can accumulate and induce transconductance degradation and permanent threshold voltage shifts [6]. Analog electronics rely on precise matching of device parameters for proper performance; threshold voltage shifts can result in drastic mismatch of these critical device parameters. Moreover, hot carrier injection and carrier trapping result can

cause damage to the oxide layer that manifests as subthreshold leakage current [6]. These effects present significant concerns regarding the long-term performance and reliability for MOSFET-based electronics operated in this cold-temperature environment (particularly analog electronics).

In addition to these extreme temperatures, extra-terrestrial environments harbor much higher levels of radiation than observed on Earth, both in terms of single-event effects (SEE) and total-ionizing dose (TID) irradiation [4]. The effects of this radiation are often catastrophic for electronics not specifically designed to tolerate such radiation. TID radiation incident upon a silicon cross-section has been demonstrated to induce electron-hole pairs in the insulating oxide layer [7], [8]. In the presence of an electric field, low-mobility holes slowly drift through the oxide layer while high-mobility electrons are quickly removed by the electric field. The result is a trapped charge of holes at the oxide-Si interface. This trapped charge causes variability in I-V characteristic of the device, particularly subthreshold leakage current and threshold voltage shifts [7] – [10]. Single-event transients (SETs) are voltage transients at a circuit node induced by an ion strike transecting a pn-junction resulting in charge deposition. SETs can be mitigated with a variety of design and layout techniques, but SETs can never be completely eliminated. Singleevent upsets (SEUs) induced by SETs are most concerning in digital systems such as dividers/prescalers. An SEU is defined as an SET-induced alteration of a logic level at a particular digital circuit node. SEUs are often responsible for bit errors in digital systems and frequently result in erroneous operation.

The design challenges associated with these extreme environments may render the use of commercial-off-the-shelf (COTS) components impossible for extra-terrestrial electronic systems, and therefore, an application-specific integrated circuit (ASIC) must be developed for this specific purpose. The development and manufacturing of an ASIC is a costly, time-consuming process that is greatly exacerbated if the ASIC is required to be capable of extreme environment operation. Therefore, whenever possible, it is highly desirable to develop scalable, adaptable ASICs for extreme environment applications. The development of a fixed frequency, non-configurable frequency synthesizer for a specific extreme environment application would offer a very low return on investment. A more attractive solution would be to develop a user-configurable frequency synthesizer ASIC that can provide a wide range of precise clock frequencies for a myriad of extreme environment applications.

Table 1. Attributes required of extreme environment, precision frequency synthesizer

| Criteria               | Description                                                                                                                  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Radiation hard         | TID radiation tolerance in excess of 1 Mrad/Si, SEL immune, SEU resistant                                                    |

| Temperature range      | Robust and fully operational from -180°C to 125°C                                                                            |

| Frequency stable       | High frequency stability, low noise attained from high-Q, extreme environment crystal resonator (developed by FMI)           |

| Configurable           | Able to generate wide range of clock frequencies from a single crystal frequency, selectable clock logic types (CMOS & LVDS) |

| Compact/self-contained | Complete system-in-a-package solution, single power supply, contains all required components, small size (under 0.7 cc)      |

| Reliable               | Able to withstand thermal cycles, robust, reliable start-up over temperature                                                 |

| System compatible      | Compatible with existing (and upcoming) supply voltage standards, compatible with existing logic standards (CMOS & LVDS)     |

| Low cost               | Lower cost than hybrid solutions using individual elements for clock source generation                                       |

A system that allows a high-Q, precision crystal to be packaged with a programmable, extreme environment capable frequency synthesizer ASIC would provide a complete, compact solution to clock generation needs for a wide range of space flight and other extreme environment applications. Presently, no such system exists. Table 1 outlines the frequency synthesizer design criteria required to meet the demands of extreme environment frequency generation.

#### 1.2 Research goals

The development of the described frequency synthesizer system was a significant undertaking that required parallel design paths. Frequency Management International (FMI) has developed the extreme environment capable, high-Q crystal resonators for use in the frequency generation system. The Integrated Circuits and Systems Laboratory (ICASL) group at the University of Tennessee was responsible for designing the extreme environment capable, configurable frequency synthesizer ASIC. Central to the design of this frequency synthesizer ASIC was the development of a high-frequency, multi-modulus divider (prescaler). This prescaler is the building block of the frequency synthesizer ASIC that allows a wide range of

user-selected output frequencies to be generated from a set of crystal frequency. This fact illustrates the importance of the prescaler design in a highly-configurable frequency generation system with a wide range of potential applications.

The focus of this dissertation is the design, implementation, and testing of such a prescaler capable supporting the described frequency synthesizer system. Moreover, this work was tasked with determining the performance requirements of such a prescaler that allowed the described frequency synthesizer system to be realized. The prescaler design is embedded as part of the frequency synthesizer ASIC as well as implemented as a discrete component on a test ASIC to allow for expanded testing of the multi-modulus prescaler and potential implementation in future, stand-alone applications. The multi-modulus prescaler design has been fully tested and characterized both as a stand-alone design and embedded as part of the frequency synthesizer ASIC.

#### 1.3 Dissertation overview

Chapter 2 of this dissertation details the problem description and outlines the specific requirements of the frequency synthesizer ASIC. Furthermore, Chapter 2 details the design requirements and outlines design challenges associated with the development of a highly-configurable prescaler for precision clock frequency generation in extreme environment applications.

Chapter 3 examines IC fabrication technology as it pertains to extreme environments and high-speed operation. A comparison between standard silicon-CMOS and silicon-germanium (SiGe) technologies is made as it pertains to the development of the described frequency synthesizer ASIC of this research work. The high-speed limitations of CMOS logic are explored, and the speed advantage of current-mode logic is examined. Fractional-N division and dual-modulus prescaler design (an important concept in highly-configurable dividers) is reviewed. Chapter 3 also explores prior art demonstrating frequency generation systems and prescaler designs (and frequency dividers in general) with specific attention paid to reports highlighting extreme environment capability or high configurability.

Chapter 4 describes the design approach of the multi-modulus prescaler of this dissertation. A functional description of the multi-modulus prescaler design is presented, and the block-level diagrams of the components of the multi-modulus prescaler are analyzed. The error correction scheme used for the dividers of the multi-modulus prescaler is described. Chapter 4

also presents schematic-level design details for the critical blocks of multi-modulus prescaler, and demonstrates the functionality of the dividers of the multi-modulus prescaler with block-level timing simulations. Lastly, Chapter 4 illustrates the physical implementation of multi-modulus prescaler as well as the physical implementation of the frequency synthesizer ASIC.

Chapter 5 describes the functionality of the prescaler test ASIC and the printed-circuit board (PCB) used to facilitate testing of the multi-modulus prescaler. The initial functionality testing of the developed multi-modulus prescaler is shown. Prescaler measurement results are presented demonstrating input frequency locking range and supply current draw over temperature and supply voltage. Phase noise and jitter measurements are shown and analyzed for both the stand-alone VCO/prescaler test structure and the entire frequency synthesizer ASIC system. Finally, the method used for testing the prescaler error correction scheme is outlined, and measurement results demonstrating error correction of the multi-modulus are presented and analyzed.

Chapter 6 summarizes the research work performed for this dissertation. The original contributions of this research as well as possible directions for future work are also discussed in Chapter 6.

#### **CHAPTER 2: PROBLEM DESCRIPTION**

## 2.1 Extreme environment frequency synthesizer overview

As mentioned in Chapter 1, the goal of this research was to design and develop a fully-integrated, extreme environment capable, multi-modulus prescaler for use in a PLL-based frequency synthesizer ASIC. To better understand the requirements of this prescaler, the operation and design requirements of the frequency synthesizer ASIC must first be examined. The frequency synthesizer system was developed with the following set of targeted, technical objectives defined in Table 2. The technical objectives defined in Table 2 were established based on experience from previous and on-going projects with space-flight application users, discussions with energy exploration users, and established requirements for military-grade electronic systems.

Table 2. Frequency synthesizer ASIC technical objectives

| Performance parameter       | Design goal  |     |

|-----------------------------|--------------|-----|

| Crystal frequency range     | 15 to 25     | MHz |

| Output frequency range      | 0.08 to 250  | MHz |

| Output frequency resolution | 10           | kHz |

| Operating temperature range | -180 to 125  | °C  |

| Supply voltage range        | 3.0 to 3.6   | V   |

| Output la cia tura          | CMOS (3.3 V) |     |

| Output logic type           | LVDS         |     |

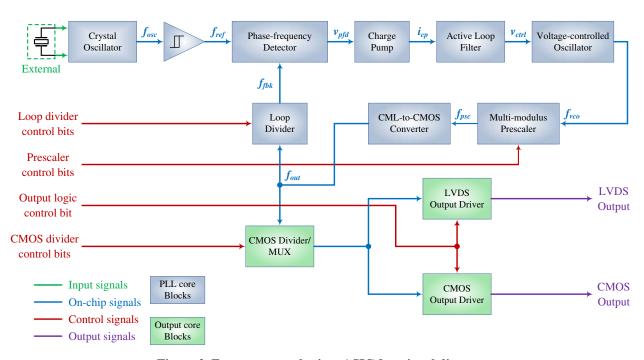

Figure 2 shows the frequency synthesizer ASIC functional block diagram; the frequency synthesizer ASIC is separated into two main sections, the PLL core and the output core. The output core serves two main functions: to allow user-controlled division of the PLL core output frequency to extend the lower end of the ASIC output frequency range, to allow user-controlled selection of the ASIC output logic type. Since the output core of the frequency synthesizer is outside of the PLL loop, any frequency division and/or signal conditioning performed in the output core will not alter the performance of the PLL core. Consequently, for the analysis of the prescaler design within the frequency synthesizer ASIC, the output core can be neglected. The subsequent analysis will be limited to the PLL core. In the PLL core, the oscillator frequency  $(f_{osc})$  is generated from the external crystal and integrated crystal oscillator. A Schmitt trigger digitizes the analog output signal of the crystal oscillator to establish the reference frequency  $(f_{ref})$ . The phase-frequency detector together with the charge pump compares the phase difference between the reference signal  $(f_{ref})$  and the feedback signal  $(f_{fbk})$  and generates a sourcing/sinking current pulse  $(i_{cp})$  for a positive/negative phase difference.

Figure 2. Frequency synthesizer ASIC functional diagram

The active loop filter reduces the bandwidth of the PLL control loop (thereby establishing the dynamic performance of the loop) and generates a stable control voltage ( $v_{ctrl}$ ) for the voltage-controlled oscillator by suppressing noise and voltage ripple from the charge-pump. This control voltage regulates the oscillation frequency of the VCO ( $f_{vco}$ ). By design, the VCO oscillation frequency is much higher than the reference frequency and must be reduced to allow the control loop to lock and reach stable operation. The prescaler provides the majority of this frequency division with high-speed, current-mode logic (CML). The CML signal of the prescaler output ( $f_{psc}$ ) is converted to CMOS logic via a CML-to-CMOS logic converter. The output of the CML-to-CMOS converter is taken as the output of the PLL core ( $f_{out}$ ). The CMOS loop divider provides the remaining frequency division and generates the feedback signal for the phase-frequency detector.

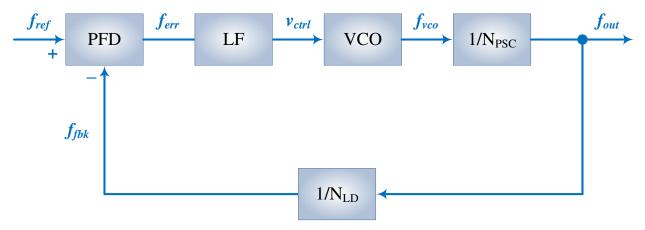

In lieu of a detailed PLL transfer function analysis, a simplified, linear approximation of the PLL control loop will be performed as this analysis is sufficient for understanding the operation of the prescaler within the PLL control loop. Shown in Figure 3 is a simplified diagram of the PLL core used for the subsequent PLL analysis. Here,  $N_{PSC}$  is the prescaler division ratio and  $N_{LD}$  is the loop divider division ratio. In this analysis, it is assumed that the loop is operating in a locked condition, and the chosen crystal determines the reference frequency,  $f_{ref}$ . Under these assumptions, the feedback frequency is forced to match the reference frequency. Therefore, we see that

$$f_{out} = f_{ref} N_{LD}$$

{2.1}.

Substituting the maximum values of output frequency (250 MHz) and crystal frequency (25 MHz) from Table 2 into {2.1} gives the maximum required loop divider ratio of 10. To limit the tuning range required of the VCO, a minimum loop divider ratio of 4 is used. Therefore, the PLL core output frequency range is 80 MHz to 250 MHz. Observing Figure 3 once more, we find that

$$f_{vco} = f_{out} N_{PSC} \tag{2.2}.$$

As mentioned in Chapter 1, there are several advantages to operating the VCO within a PLL at high frequencies. To this end, a nominal VCO frequency of 4 GHz was chosen with  $\pm 10\%$  tuning range. Substituting this nominal VCO frequency and the stated 80 MHz to 250 MHz output frequency range into  $\{2.2\}$  results in a required prescaler division ratio range of  $\sim 16$  to 48.

Figure 3. PLL core functional diagram (simplified)

## 2.2 Multi-modulus prescaler design considerations

From the analysis of the frequency synthesizer ASIC in the previous section, the performance requirements of the extreme environment, multi-modulus prescaler designed to support the frequency synthesizer ASIC can be established. The VCO tuning range, output frequency range, and output frequency resolution of the frequency synthesizer ASIC dictate the operating frequency and resolution specifications required of the multi-modulus prescaler. A summary of the design specifications of the multi-modulus prescaler are outlined in Table 3. The VCO output signal is a differential, ground-referenced, sinusoidal signal in the range of 3.6 GHz to 5 GHz. The VCO output signal must be buffered and level-shifted to the CML logic level required by the multi-modulus prescaler. To allow tuning linearity and configurability, the prescaler must be able to divide the buffered VCO signal in the range of 16 to 48 with high resolution (27 total moduli with the division range). The differential, CML output of the prescaler must be converted to a 1.8 V CMOS signal capable of operating up to at least 250 MHz. As stated in the previous sections, the prescaler must operate reliably over a temperature range of -180°C to 125°C and supply voltages from 3.0 V to 3.6 V. To be able to provide extreme environment capability, the prescaler must be TID radiation tolerant up to 1 Mrad/Si as well as SEL immune and SEU resistant. The definition of SEU resistant established for this research work is that the circuit is able to "quickly and gracefully" recover from SEUs.

Table 3. Multi-modulus prescaler design specifications

| Performance parameter       | Design specification |     |

|-----------------------------|----------------------|-----|

| Input frequency             | 3.6 to 5             | GHz |

| Output frequency            | 80 to 250            | MHz |

| Output logic                | 1.8 V CMOS           | -   |

| Division range              | 16 to 48             | -   |

| Total moduli                | 27                   | -   |

| Operating temperature range | -180 to 125          | °C  |

| Supply voltage range        | 3.0 to 3.6           | V   |

#### 2.3 Frequency synthesizer ASIC development

The frequency synthesizer ASIC was developed on a SiGe BiCMOS process. This reasoning behind this design choice will be explained in Chapter 3. The frequency synthesizer ASIC is a fully-integrated design (except for the external crystal resonator). The frequency synthesizer ASIC, along with the crystal, is configured at the packaging stage to provide a complete frequency synthesizer system-in-a-package solution. To achieve the stated TID radiation tolerance requirement, the frequency synthesizer ASIC leverages the SiGe heterojunction bipolar transistor (HBT) and avoids the use of the TID-sensitive NMOS device [9], [10]. The development of the frequency synthesizer ASIC (and therefore the prescaler) used a commercially-available, 180-nm SiGe BiCMOS fabrication process. This process offers HBT devices capable very high-speed operation which facilitated the design of the high-frequency portion of the PLL core.

### **CHAPTER 3: LITERATURE REVIEW**

#### 3.1 Introduction

Chapter 2 of this dissertation outlined the design requirements for the extreme environment capable prescaler developed for use in the frequency synthesizer ASIC. Chapter 2 states that the frequency synthesizer ASIC was developed on a 180-nm SiGe BiCMOS process. The first section of this chapter examines this technology and provides reasoning for this design choice. Additionally, this chapter reviews the limitations of lower-speed logic families (such as the well-known static CMOS logic) and explores high-speed digital logic families (such as CML). This chapter also examines methods of achieving fractional-N division, including the common dual-modulus approach. Lastly, this chapter covers a review of prior art demonstrating prescalers capable of high-speed operation, high-resolution moduli, and/or extreme environment capability.

## 3.2 Silicon Germanium (SiGe) technology overview

Bulk-silicon CMOS technology has long dominated the semiconductor market place for a number of reasons including: ease of growing a high-quality dielectric ( $SiO_2$ ); silicon can be grown in large, single crystals; silicon is capable of high levels of integration; silicon has excellent heat dissipation qualities; silicon has a wide doping range for both n- and p-type impurities, cost of bulk-silicon technology remains considerably lower than other process technologies [11]. While all of these attributes of bulk-silicon are certainly desirable for any semiconductor material used as an integrated circuit (IC) development platform, silicon has several notable limitations to consider. These limitations include: relatively low carrier mobility (both electrons and holes), low saturation velocity, and susceptibility to extreme environment effects (both temperature and radiation) [11] – [13].

Over the years, there has been considerable advancement in the area of extreme environment electronics. Developments in process technology as well as circuit design techniques have led to a wide range of extreme environment capable electronics. One such process technology that has demonstrated excellent performance in extreme environments is silicon-germanium (SiGe) bipolar-CMOS (BiCMOS) technology. SiGe BiCMOS technology leverages a heterojunction between silicon and silicon-germanium materials to form a *pn*-junction.

For extreme environment applications, the susceptibility of silicon CMOS ICs to hot-carrier and TID radiation effects is of particular concern. As previously explained, the underlying cause of the damaging effects of both hot-carrier injection and TID radiation on silicon devices is the generation and trapping of charge in an oxide layer of a device (most notably the shallow-trench isolation (STI) used to terminate the edges of the MOSFET conduction channel) [7] – [10]. Several radiation-hardening by design (RHBD) techniques have been demonstrated to be very effective in preventing this damaging trapped charge from accumulating along the STI edge. Unfortunately, these RHBD techniques (most notably annular-gate NMOS structures) invariably require design trade-offs, particularly a reduction in device speed and an increase in required chip area and power. Since SiGe HBT devices do not require this oxide layer, generation of trapped charge is not an issue in these devices. The damaging effects of low temperature operation and TID radiation observed in silicon CMOS devices are not seen in SiGe HBTs [14]. This feature of SiGe HBTs allows SiGe BiCMOS technology to provide a wide-temperature, radiation-tolerant design platform for IC development.

In addition to the extreme environment benefits of SiGe BiCMOS, SiGe HBTs are also capable of operating at much higher speeds than both silicon BJTs and silicon CMOS. Both the low carrier mobility and saturation velocity of silicon reduce speed achievable by silicon-based devices [15]. Many compounds from the III-V semiconductor family offer drastically higher motilities and saturation velocities than those of silicon; however, these compounds offer none of the benefits of silicon in terms of ease of fabrication, high-integration level, high yield, and low fabrication cost [11]. SiGe HBTs are inherently very high-speed devices and exhibit excellent performance at low temperature. In fact, many important bipolar device parameters (such as current gain and cut-off frequency) improve as temperature decreases [14], [16]. Additionally, since SiGe technology is developed from bulk-silicon CMOS technology, SiGe HBTs can be developed on existing silicon CMOS processes. SiGe HBT technology, therefore, offers operating speed performance that is competitive with that of the III-V compounds while maintaining compatibility with easy to fabricate, low-cost silicon CMOS [14]. The result is that SiGe BiCMOS processes offer a complete bulk-silicon CMOS design platform with the addition of high-speed, radiation-hard HBTs.

The previous discussion on SiGe technology highlights why SiGe BiCMOS technology is a very attractive choice for high-speed, extreme environment capable electronic systems. With no modification to the existing technology, SiGe BiCMOS has several qualities ideally-matched to the development of an extreme environment capable frequency synthesizer ASIC. The key benefits of SiGe BiCMOS technology within the scope of this research include:

- Compatibility with low-cost, high-yield silicon CMOS processes

- SiGe HBT devices are capable of very high-speed operation ( $f_T \sim 60 \text{ GHz}$ )

- SiGe HBT devices offer excellent low-temperature performance and resistance to hot-carrier injection

- SiGe HBT devices are inherently resistant to TID radiation

#### 3.3 High-speed digital logic review

Many logic families have been developed through the years from the early resistor-transistor logic (RTL) to the ubiquitous CMOS logic and to more exotic logic families such as dynamic logic. Most of these logic families focus on taking advantage of the high integration capacity and high scalability of MOSFET devices. While MOSFET devices are distinctly advantaged in these areas, bipolar devices have always been and remain capable of much higher switching speeds than comparable MOSFETs. To this end, logic circuits for high-speed applications often implement current-mode logic (CML) as opposed to CMOS or other logic families. CML is a generalized logic structure that encompasses emitter-coupled logic (ECL), positive emitter-coupled logic (PECL), and source-coupled logic (SCL). All of these logic families have specific definitions for logic levels that may not be applicable to this design effort. For this reason, the generalized term, CML, will be used throughout this dissertation.

#### 3.3.1 Speed limitations of CMOS logic

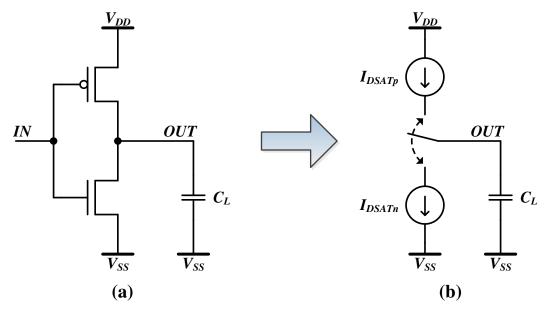

To understand why CML logic offers such a significant speed advantage over other logic families, we first examine the limiting factor in standard CMOS logic speed capability. As illustrated, the active devices in the CMOS inverter shown in Figure 4 can be modeled with switched constant current sources. In this analysis, the load capacitance includes all parasitic capacitance associated with the output of the inverter.

Figure 4. Standard CMOS inverter (a) with equivalent model (b)

The stored charge of a capacitor is a linear function of capacitor voltage as given by

$$Q = CV {3.1}.$$

The inverter propagation delay from output high to low  $(t_{phl})$  of the CMOS inverter is defined as the time required for the output voltage to fall from  $V_{DD}$  to  $\frac{1}{2}V_{DD}$ . Using this definition in {3.1}, the initial charge at the inverter output is given by

$$Q_{L(t=0)} = C_L V_{DD} {3.2}.$$

Similarly, the charge at the inverter output at time  $t = t_{phl}$  is given by

$$Q_{L(t=t_{phl})} = C_L \frac{V_{DD}}{2}$$

{3.3}.

Universally for capacitors, the total charge transferred between times  $t_1$  and  $t_2$  is a function of current flow as defined by

$$Q_{(t=t_2)} = \int_{t_1}^{t_2} I \, dt \tag{3.4}.$$

For constant current, I,  $\{3.4\}$  can be evaluated as

$$t_2 - t_1 = \frac{Q_{(t=t_2)} - Q_{(t=t_1)}}{I}$$

{3.5}.

Substituting {3.2}, {3.3}, and the saturated NMOS current source (negative current because it discharges the load capacitance) into {3.4} where  $t_1 = 0$  and  $t_2 = t_{phl}$ , we find that

$$t_{phl} = \frac{C_L \frac{V_{DD}}{2} - C_L V_{DD}}{-2I_{DSATn}} = \frac{C_L V_{DD}}{2I_{DSATn}}$$

(3.6).

Substituting the expression for NMOS saturation current into {3.6} we see that

$$t_{phl} = \frac{C_L V_{DD}}{\frac{W_n}{L_n} \mu_n C_{ox} (V_{DD} - V_{TN})^2}$$

(3.7).

A similar analysis can be performed for inverter output low to high propagation delay; however, CMOS inverters are usually designed such that NMOS and PMOS saturation currents (and therefore rising and falling propagation delays) closely match [17].

The CMOS inverter equivalent model and subsequent analysis illustrate that the propagation delay for a CMOS inverter is determined by MOSFET saturation current, load capacitance at the inverter output, and supply voltage. Because the total charge of a capacitor is proportional to capacitor voltage and the fact that CMOS logic swings the full range of supply voltage, large amounts of charge must be continually supplied and removed from the inverter load capacitance. Also, the relatively low saturation current of MOSFET devices limits the rate that this load capacitance can be charged/discharged. These factors combine to limit the speed of CMOS logic circuits. In short, static CMOS logic is most well-suited for large-scale, low power, lower-speed applications, but applications requiring high-speed digital logic will not be able leverage the benefits of CMOS logic due to the prohibitive speed limitations inherent to CMOS logic.

#### 3.3.2 Current-mode logic (CML) review

Having noted that CMOS logic speed is limited in large part because CMOS logic outputs must swing the full range of the supply rail, CML aims to improve speed by restricting the logic levels to a portion of the supply rail. Additionally, CML using BJT devices can improve on CMOS speed by replacing the relatively low speed MOSFET devices with higher-speed devices. The essential concept underlying CML logic is to use inherently high-speed bipolar devices in a differential pair configuration with a constant tail current ( $I_{EE}$ ). In CML, the input and output logic levels are defined such that the bipolar devices are never driven into the

saturation region. This is an important concept in CML design since bipolar devices exhibit slow turn-off behavior in the saturation region [18]. Figure 5 shows a simplified CML inverter/buffer with parasitic load capacitance. Using the bipolar collector current equation

$$I_C = I_S \left( e^{V_{BE}/U_T} - 1 \right)$$

{3.8}

where  $U_T$  is the thermal voltage, we can express the ratio of collector currents of Figure 5 as

$$\frac{I_{C1}}{I_{C2}} = e^{(V_{i+} - V_{i-})} / U_T$$

{3.9}.

The exponential relationship of this ratio to the input voltage difference shows that only very small input voltage difference is needed to force nearly all current through one bipolar transistor and negligible current through the other bipolar transistor. For example, an input voltage difference of only 100 mV results in a current ratio of 50 at room temperature; an input voltage difference of 200 mV results in a current ratio of over 2000.

Figure 5. CML inverter/buffer (simplified)

This current ratio is high enough to approximate the differential pair as current-steering switch (all current flows through either  $Q_1$  or  $Q_2$  at any given time). Using this approximation, the CML inverter output logic levels can be defined as

$$V_{OL} = V_{CC} - I_{EE}R_C$$

$V_{OH} = V_{CC}$  (3.10).

The differential input voltage is the same as the differential output voltage, so the differential logic levels can be defined as

$$V_{o/i+} - V_{o/i-} = V_{OH} - V_{OL} = I_{EE}R_C$$

(3.11)

and the emitter current and collector resistor are chosen to induce a relatively small voltage differential. Therefore, the common-mode voltage of the differential pair can be set to ensure that both  $Q_1$  and  $Q_2$  remain in the forward-active region throughout operation and the slow turn-off behavior of the saturation region is avoided. By restricting  $Q_1$  and  $Q_2$  to the forward-active region of operation, small-signal estimations for the cut-off frequency  $(f_T)$  of  $Q_1$  and  $Q_2$  are valid. As stated earlier in this chapter, current SiGe BiCMOS technology offers well-established HBTs with cut-off frequencies of 60 GHz or more. The high  $f_T$  of these HBT devices allows the time constant associated with the parasitic load capacitance and collector resistor to dominate the CML inverter transient response, so  $Q_1$  and  $Q_2$  can be approximated as ideal switches. Figure 6(a) shows the resulting equivalent model for one side of the differential CML inverter/buffer. Figure 6(b) shows the state of the inverter with the output LOW, just before the output transitions HIGH; Figure 6(c) shows the equivalent model of the inverter just after switching from output LOW to HIGH. From Figure 6(c), KVL reveal the time domain output voltage response is governed by

$$I(t)R_C + V_o(t) = V_{CC}$$

{3.12}.

Using the time domain expression relating capacitor current to voltage

$$I_C(t) = C \frac{dV_C(t)}{dt}$$

{3.13}

and realizing that  $V_C(t) = V_o(t)$  and  $I_C(t) = I(t)$ , {3.12} can be rearranged to show that

$$R_C C_L \frac{dV_o(t)}{dt} + V_o(t) = V_{CC}$$

{3.14}.

Figure 6. CML inverter/buffer (a) equivalent model using ideal switch, (b) equivalent model just before output LOW to HIGH, (c) equivalent model after output LOW to HIGH

Equation {3.14} is a first-order, differential equation that can be solved as

$$V_o(t) = V_{CC} + Ke^{-t/R_C C_L}$$

{3.15}

where K is an unknown constant of integration that can be found using the initial condition of the inverter output voltage shown in Figure 6(b).

$$V_{o}(0) = V_{CC} - I_{EE}R_{C} = V_{CC} + Ke^{0}$$

or {3.16}

$K = -I_{EE}R_{C}$

The final expression for the CML inverter output LOW to HIGH transient response is then

$$V_o(t) = V_{CC} - I_{EE} R_C e^{-t/R_C C_L}$$

(3.17).

Defining output LOW to HIGH propagation delay  $(t_{plh})$  as the time required for the output to swing from  $V_{OL}$  to  $(V_{OL}+V_{OH})/2$  and substituting these values into {3.17}, we arrive at

$$V_o(t_{plh}) = \frac{V_{CC} + (V_{CC} - I_{EE}R_C)}{2} = V_{CC} - I_{EE}R_Ce^{-t_{plh}/R_CC_L} \{3.18\}.$$

Solving {3.18} for the LOW to HIGH propagation delay, we find that

$$t_{plh} = R_C C_L ln2 {3.19}.$$

A similar analysis for the CML inverter output HIGH to LOW transient response can be performed to find that

$$V_o(t) = V_{CC} - I_{EE} R_C \left( 1 - e^{t/R_C C_L} \right)$$

(3.20)

Solving {3.20} for output HIGH to LOW propagation delay reveals that

$$t_p = t_{phl} = t_{plh} = R_C C_L ln2$$

{3.21}.

where  $t_p$  is defined as the average of  $t_{plh}$  and  $t_{phl}$ . In this first-order analysis, it is revealed that the CML inverter propagation delay depends only on the parasitic load capacitance and the size of the collector resistor. The dependence of the inverter propagation delay on supply voltage observed with the CMOS inverter is not seen in the CML inverter. Moreover, the propagation delay of the CML inverter is not limited by the switching speed or saturation current of the active device. Judicious choice of  $I_{EE}$  and  $R_C$  in the CML inverter design allows this logic structure to operate at speeds approaching the limit of the HBT device itself; however, static power dissipation of CML circuits is proportional to  $I_{EE}$ . In summary, the previous CML/CMOS logic comparison indicates that CML is capable of significantly higher operating speeds than CMOS, but this benefit comes at the expense static power dissipation. CMOS logic does not consume static power as observed with CML and can allow for lower power designs.

#### 3.4 Fractional-N division review

Chapter 1 of this dissertation introduced the concept of fractional-N division as a method for obtaining greater frequency resolution in frequency synthesizer designs. Other methods exist for increasing frequency resolution that include: separation of PLL loop divider and output divider, use of multiple-loop synthesizers, pulse-swallowing techniques, and others [3]. All of these techniques have distinct advantages and disadvantages that must be considered in the design of any PLL-based frequency synthesizer. This research focuses on the most common techniques for increasing frequency resolution, fractional-N division. In Figure 7, a basic, integer-N PLL structure is shown. The integer-N PLL configuration operates such that the phase-locking of the phase detector requires that  $f_{out} = Nf_{ref}$ . Therefore, the output frequency is a selectable, integer-multiple of the reference frequency. To suppress output ripple and ensure loop stability, the bandwidth of the loop must be substantially smaller than the phase detector

Figure 7. Integer-N phase-locked loop

comparison frequency,  $f_{ref}$ . If it is desired that the output frequency increments be small, then the PLL bandwidth must extremely small. This narrow bandwidth requirement opposes the benefits of rapid frequency acquisition and stabilization of VCO jitter achieved with higher loop bandwidths. It is now evident that a conflict exists in PLL design between simultaneously obtaining narrow frequency resolution and fast PLL loop response time. A useful technique for alleviating this conflict is using fractional-N division as opposed to integer-N division. A fractional-N divider narrows the output frequency resolution without compromising loop bandwidth. One method for realizing fractional-N division is the use of a dual-modulus prescaler as shown in Figure 8. The dual-modulus prescaler in Figure 8, divides by P or P+1 as dictated by the modulus control. The division ratios of the N and A counters are externally controlled. The dual-modulus prescaler can best be conceptualized as a counter that divides the VCO frequency by P for N-A cycles and by P+1 for A cycles. For example, assume that counters N and A are each externally preset to some value and the prescaler initially divides by P+1. After each cycle of the prescaler (P+1 cycles of the VCO), the N and A counters are decremented by 1. This continues until the A counter reaches zero, after which, the P counter division ratio is changed from P+1 to P. At this point, the N counter has completed A counts. The N and A counters continue to decrement with every cycle of the prescaler (P cycles of the VCO) until the N counter reaches zero, at which point, both counters and the prescaler reset and the cycle repeats. One complete cycle as described above consists of A cycles of P+1 VCO subcycles and *N*–*A* cycles of *P* VCO sub-cycles.

Figure 8. Phase-locked loop with dual-modulus prescaler

The total resulting count can be expressed as

$$N_{tot} = A(P+1) + (N-A)P = NP + A$$

{3.22}.

While this counting structure is not truly fractional-N division since  $N_{tot}$  must be a whole number, multiplying N by P allows the addition of a count, A, to effectively result in a fractional divider. Dual-modulus prescalers are not able to operate with any choice of N, P, and A; they are restricted by the limits A < P and  $N \ge A$ . These restrictions imply that  $N_{tot}$  must be greater than P(P-1) to achieve the channel spacing advertised, otherwise gaps in the channel spacing exist. This shows that a dual-modulus prescaler cannot achieve high division resolution for low-range moduli. The consequences of this point as it pertains to this dissertation will be addressed later in this chapter. Another drawback to a dual-modulus prescaler approach is that the periodicity introduced by the varying prescaler modulus appears as sidebands or spurs around the operating frequency. These sidebands and spurs can be suppressed by dithering techniques, but this usually requires complex delta-sigma techniques to avoid an increase in the noise floor. These limitations of the conventional dual-modulus prescaler design indicates the need for this research work to explore alternative methods of achieving narrowly-spaced moduli for over a low division range of 16 to 48.

## 3.5 Prescaler prior art

The previous sections of Chapter 3 highlight the need for a literature review to examine the prior art for prescaler designs. A considerable amount of literature has been published on a wide variety of prescaler designs. Many of these prescaler designs offer specifications that meet those required of this research effort, but none of the designs encompass all of the requirements for this multi-modulus prescaler design effort. The prior art applicable to such a prescaler design will now be examined, and the knowledge and design techniques of this examination will be incorporated into the development of a novel prescaler solution capable of meeting the specifications provided in Table 3. Special attention will be paid to prescaler designs with one or more of the following attributes: high-speed operation, high division resolution, and extreme environment operation capable.

### 3.5.1 High-speed prescaler prior art

Prescaler designs operating at frequencies over 40 GHz have been reported in literature [19] – [21]. These high-speed designs utilize current-mode logic with inductor peaking to achieve high switching speeds, but inductor peaking results in highly-tuned digital cells that can operate only in a narrow frequency band. Other digital design techniques have been demonstrated that allow high-speed operation without requiring highly-tuned circuits. One such example is the 21 GHz, 8-modulus prescaler CMOS design described in [22], see Figure 9.

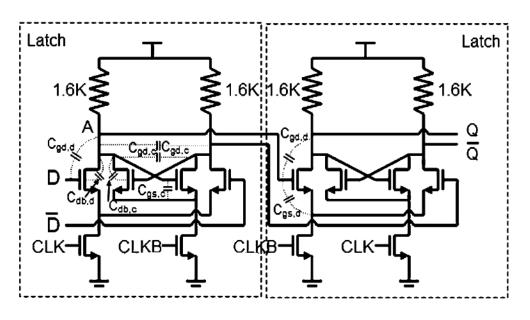

Figure 9. D-flip-flop used in prescaler in [22]

This prescaler design uses NMOS-based, CML D-flip-flops to achieve a 21-GHz maximum operating frequency. This 21-GHz prescaler design consists of a 4/5, synchronous counter and a divide-by-64, asynchronous counter. This configuration allows for external control of the prescaler division ratio in the range of 256-263 with 8 selectable output frequencies. The block diagram of the prescaler reported in [22] is shown in Figure 10. While this 21-GHz prescaler design meets the required 5 GHz operating frequency of this research, this prescaler was designed in a "stacked" configuration along with the VCO of the PLL. By stacking the VCO and prescaler, the VCO and prescaler can share current and parasitic capacitance at these critical, high-speed circuit nodes can be reduced, allowing for very high-speed designs. The drawback to this technique is that the VCO and prescaler must be designed and optimized in conjunction; therefore, the prescaler design as intellectual property (IP) cannot be used with another VCO without major redesign effort. Another tradeoff of this technique is that this VCO/prescaler design requires a significant amount of bench tuning to achieve the desired operation. As discussed in Chapters 1 and 2, this research is focused on developing a highly-configurable ASIC that (once configured at the bonding/packaging stage) requires no tuning or user configuration. Any design solution requiring post-fabrication tuning or optimizing is not viable for this research effort. Moreover, the dual-modulus approach used for this design limits the division range of this prescaler (256-263) to well outside the range required of this research.

Figure 10. Diagram of 8-modulus prescaler in [22]

Additionally, the range of division ratios for the 21-GHz prescaler design is quite restricted and will limit the range of frequency synthesizer output frequencies possible with this prescaler. Lastly, frequency synthesis using this 21-GHz prescaler is limited to a maximum output frequency determined by the maximum prescaler input frequency and the minimum prescaler division ratio, found to be 82 MHz. The 82-MHz output frequency limit for this prescaler is well below the 250 MHz maximum output frequency required for this research. Another consideration with respect to this prescaler design is the extensive use of NMOS devices in the CML D-flip-flops (the essential building block of this prescaler). NMOS devices have a well-documented sensitivity to ionizing radiation (see Chapter 1) that prohibits the use of such a design in a radiation-rich environment. Due to the sensitivity of NMOS devices to ionizing radiation, any prescaler design utilizing NMOS devices without using RHBD techniques is not viable for this research work.

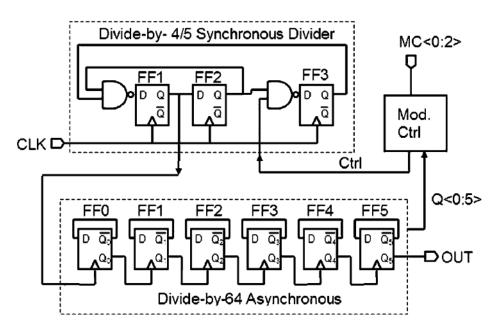

Another high-speed prescaler design that leverages HBTs instead of NMOS as the principle active device attains an 8 GHz maximum operating frequency as reported in [23].

Figure 11. Diagram of divide-by-64~79 prescaler of [23]

This prescaler uses HBT-based CML D-flip-flops to achieve this high-speed operation. This design uses a synchronous, divide-by-4/5 counter followed by a divide-by-16, asynchronous counter (Figure 11). In this configuration, division ratios of any integer in the range of 64-79 can be achieved with this prescaler design, but as with the prescaler in [22] this division range is insufficient for the goals of this research. These D-flip-flops are incorporated with merged NAND gates as shown in Figure 12. By merging the NAND gates with the D-flip-flops, the gate delay associated with a separate NAND gate is diminished and the operating frequency range is extended. The HBT-based, CML D-flip-flops used throughout this prescaler design allow for the reported 8 GHz operation. While this paper does not present any specific information on this design with respect to extreme environment reliability, the SiGe HBT has been established as an extreme environment capable device and designs leveraging HBTs could potentially take advantage of this inherent quality. Extreme environment capability notwithstanding, the division range 64-79 is insufficient (both out of required range and width of range too narrow) to allow such a design topology to be used in this research work.

Figure 12. D-flip-flop designs of [23] (a) without and (b) with merged NAND gate

High-speed prescaler designs are not necessarily limited to CML structures, and this fact is demonstrated in the work described in [24]. This paper reports a multi-modulus prescaler design using a modified, enhanced, true-single phase clock (METSPC), dynamic CMOS logic gates developed on 90-nm CMOS technology capable of operating at frequencies as high as 5 GHz. However, this paper only reports simulation data and presents no experimental results. This design consists of a divide-by-2/3, synchronous counter followed by a divide-by-16, asynchronous counter and allows for divisions by 32/33/39/40/47/48. The prescaler described in [24] is demonstrated in Figure 13. As with the previous prescaler designs examined, this prescaler is subject to a narrow division range, in addition to widely-spaced moduli. As with the prescaler described in [22], this prescaler leverages NMOS devices throughout and is therefore potentially sensitive to ionizing radiation.

Figure 13. Diagram of multi-modulus 32/33/39/40/47/48 prescaler of [24]

#### 3.5.2 High-resolution prescaler prior art

From the review of high-speed prescaler prior art, we saw that these prescaler designs have relatively narrow division ranges. These dual-modulus designs utilize a synchronous, dual-modulus divider followed by an asynchronous divider. As explained in section 3.4, this architecture cannot provide narrowly-spaced division over a low range of moduli. From Chapter 2, this research requires the design of prescaler capable of narrowly-spaced moduli from 16 to 48. A conventional, dual-modulus structure is, therefore, not viable for this prescaler and other avenues must be explored.

To illustrate the previous point, the frequency divider described in [25] is now examined. This frequency divider is composed of a 32/33 synchronous dual-modulus prescaler, a 5-bit swallow counter, an asynchronous 11-bit programmable counter, and a control circuit as seen in Figure 14. This frequency divider is arranged in the dual-modulus configuration seen previously and is capable of operating at clock frequencies from 0.5 to 3.5 GHz. The 11-bit programmable counter and the 5-bit pulse swallow counter allow this divider configuration to achieve an extremely wide range of moduli, from 1024 to 65536. A consequence of this wide division range is that the minimum division ratio must be quite high. This example of the frequency divider topology of [25] illustrates the point that a conventional dual-modulus prescaler approach (or any resolution narrowing method that uses varying moduli) is not well-suited for the development of a high-resolution frequency divider for a low range of moduli.

Figure 14. Diagram of frequency divider described in [25]

The prescaler described in [26] describes a multi-modulus prescaler design used to generate narrowly-spaced moduli over a low-range. The prescaler of [26] was developed using a 0.35-µm SiGe BiCMOS process. A maximum operating frequency of 4.6 GHz was achieved by leveraging high-speed, ECL D-latches as the principle building block. As opposed to the dualmodulus approach seen in the previous examples, this design cascades a series of divide-by-2/3 cells as illustrated in Figure 15. For this design, each control signal  $C_n$  is used to control the modulus of each stage divide-by-2/3 cell. A feedback signal, generated in the subsequent stage of each cell, is used to ensure that each cell divides by 3 only once during the prescaler cycle. This work used six divide-by-2/3 cells configured as seen in Figure 15, which results in a division range of 64 to 127. This range of moduli is much closer to the range required of the prescaler for this research work (16 to 48). Using five 2/3 cells would allow a prescaler to attain moduli of 16 to 31, but this division range is still not adequate for the prescaler design of this work. Another tradeoff to consider with this design is that the input frequency to each stage changes drastically for different configurations. To maintain adequate input operating frequency of all stages of the cascade-based prescaler for all division configurations, each cell must either be biased for the highest input frequency possible (wastes power for all other configurations) or an adaptive bias scheme must be used (adds complexity, uses more power and space). The cascaded prescaler structure used in the precaler of [26] is not a complete solution to the prescaler design challenge of this research work but shows promise as tool for the development of a complete solution.

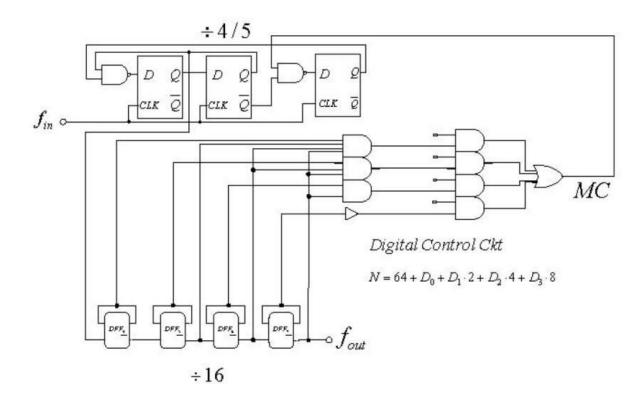

Figure 15. Diagram of cascade-based prescaler of [26]

Another promising prescaler design was described in [27]. This prescaler was developed on a 0.25-µm BiCMOS process and consists of two main parts, the ECL programmable divider and the CMOS divide-by-16 divider (see Figure 16). A maximum input frequency of 12.8 GHz was reported for this prescaler for a range of moduli from 128 to 368. Just as with the prescaler described in [26], the programmable divider part of [27] is a cascade division cells, however, [27] implements triple-modulus dividers for these cells as opposed to dual-modulus dividers. These triple-modulus dividers are capable of division by 1, 2, or 3. The programmable part of the prescaler of [27] cascades three of these triple-modulus prescalers, and the result is a programmable divider capable of division from 9 to 23. If four such prescalers were cascaded, a division range of 17 to 47 would be possible (very close to the range required of this research work). As with the prescaler of [26], the input frequency of each stage is a function of the division ratio, and the resulting biasing considerations apply to [27] as well.

The prescaler of [27] shows that the use of cascaded, triple-modulus divider cells allows for narrowly-spaced division over a low range of divisors, which is the goal of this research work. A prescaler composed of cascaded, multi-modulus dividers is a departure from the much more common, dual-modulus prescaler approach. However, the cascaded, multi-modulus divider approach does not impose the low-range frequency resolution design challenges seen in varying moduli approaches.

Figure 16. Diagram of programmable frequency divider of [27]

Other high-resolution prescaler designs have been demonstrated in literature. The oddmodulus divider described in [28] is capable of operating at frequencies as high as 7 GHz and division by odd-moduli through the use of current-switchable, CML D-flip-flops. The resulting D-flip-flop triggers on both positive and negative clock edges, which enables division by oddmoduli. However, this prescaler is designed to be implemented for a fixed modulus and does not allow for external configuration. Another design leveraging double-edge triggering (DET) is reported in [29]. The design of [29] modifies a conventional divide-by-128/129 prescaler by using DET DFFs to implement a divide-by-64/64.5. This modification allows the PLL output to be taken directly from the VCO output instead of passing through a divide-by-2 cell. Therefore, the operating frequency of the modified VCO and prescaler is reduced by two, which reduces the power consumption. However, the PLL of [29] is designed to operate at a fixed frequency, and consequently, the prescaler of this design is not configurable. In [30], a dual-modulus prescaler design using an imbalanced phase-switching technique is reported. This technique relies on the fact that 50% duty cycle is not required for proper operation of edge-triggered DFFs. As long as the triggering-edges occur at the correct time and set-up and hold times are not violated, the prescaler will operate properly. Lastly, [31] reports a "time-borrowing" technique for designing multi-modulus prescalers. The first section of this prescaler uses divide-by-2 cells to generate four 90°-spaced clock phases. A phase selector is then used to switch between these phases as dictated by a phase-switching control logic circuit. By shifting this phase for a single clock cycle, the instantaneous divide ratio can be reduced by one. This technique achieves the same end result as conventional dual-modulus prescalers, where a divider provides division-by-N for some amount of cycles, then division-by-N-1 for the remaining number of cycles. All of the high-resolution prescaler design techniques reviewed provided valuable insights into achieving a prescaler capable of meeting the requirements of this research work.

# 3.5.3 Extreme environment capable prescaler prior art