# UNIVERSIDADE DE SÃO PAULO Instituto de Ciências Matemáticas e de Computação

A hardware/software codesign for the chemical reactivity of BRAMS

### Carlos Alberto Oliveira de Souza Junior

Dissertação de Mestrado do Programa de Pós-Graduação em Ciências de Computação e Matemática Computacional (PPG-CCMC)

| SERVIÇO DE PÓS-GRADUAÇÃO DO ICMC-USP |

|--------------------------------------|

| Data de Depósito:                    |

| Assinatura:                          |

### Carlos Alberto Oliveira de Souza Junior

A hardware/software codesign for the chemical reactivity of BRAMS

Master dissertation submitted to the Instituto de Ciências Matemáticas e de Computação – ICMC-USP, in partial fulfillment of the requirements for the degree of the Master Program in Computer Science and Computational Mathematics. *FINAL VERSION*

Concentration Area: Computer Science and

Computational Mathematics

Advisor: Prof. Dr. Eduardo Marques

USP – São Carlos August 2017

# Ficha catalográfica elaborada pela Biblioteca Prof. Achille Bassi e Seção Técnica de Informática, ICMC/USP, com os dados fornecidos pelo(a) autor(a)

Souza Junior, Carlos Alberto Oliveira de

A hardware/software codesign for the chemical reactivity of BRAMS / Carlos Alberto Oliveira de Souza Junior; orientador Eduardo Marques. -- São Carlos, 2017.

109 p.

Dissertação (Mestrado - Programa de Pós-Graduação em Ciências de Computação e Matemática Computacional) -- Instituto de Ciências Matemáticas e de Computação, Universidade de São Paulo, 2017.

1. Hardware. 2. FPGA. 3. OpenCL. 4. Codesign. 5. Heterogeneous-computing. I. Marques, Eduardo, orient. II. Título.

### Carlos Alberto Oliveira de Souza Junior

# Um coprojeto de hardware/software para a reatividade química do BRAMS

Dissertação apresentada ao Instituto de Ciências Matemáticas e de Computação – ICMC-USP, como parte dos requisitos para obtenção do título de Mestre em Ciências – Ciências de Computação e Matemática Computacional. *VERSÃO REVISADA*

Área de Concentração: Ciências de Computação e

Matemática Computacional

Orientador: Prof. Dr. Eduardo Marques

USP – São Carlos Agosto de 2017

# ACKNOWLEDGEMENTS

Firstly, I thank God for being able to fulfill a dream, for giving me health and introducing me wonderful people who supported me to walk through this path. One of them is my advisor, Prof. Eduardo Marques, who is not only wise and patient but also a great friend who has always been available to help me to overcome the obstacles in the way.

My sincere gratitude to all my undergraduate professors, in special, I thank Professors Evanise Caldas, Fábio Hernandes, and Mauro Mulati. My friends Lucas Lorenzetti and Paulo Urio for sharing the dull and funny moments. To my new friends from LCR (Erinaldo, Marcilyanne, and Rafael), who were very welcoming to me. I would also like to thank CNPq for their financial support.

Finally, I am deeply thankful to my family. In particular my parents, my grandparents and my sister Kelly, even with the distance they were always close to me in my thoughts. I love you all, and without your support, this dream would not come true.

# **ABSTRACT**

OLIVEIRA DE SOUZA JUNIOR, C. A. A hardware/software codesign for the chemical reactivity of BRAMS . 2017. 109 f. Master dissertation (Master student Program in Computer Science and Computational Mathematics) – Instituto de Ciências Matemáticas e de Computação (ICMC/USP), São Carlos – SP.

Several critical human activities depend on the weather forecasting. Some of them are transportation, health, work, safety, and agriculture. Such activities require computational solutions for weather forecasting through numerical models. These numerical models must be accurate and allow the computers to process them quickly. In this project, we aim at migrating a small part of the software of the weather forecasting model of Brazil, BRAMS — Brazilian developments on the Regional Atmospheric Modelling System — to a heterogeneous system composed of Xeon (Intel) processors coupled to a reprogrammable circuit (FPGA) via PCIe bus. According to the studies in the literature, the chemical equation from the mass continuity equation is the most computationally demanding part. This term calculates several linear systems Ax = b. Thus, we implemented such equations in hardware and provided a portable and highly parallel design in OpenCL language. The OpenCL framework also allowed us to couple our circuit to BRAMS legacy code in Fortran90. Although the development tools present several problems, the designed solution has shown to be viable with the exploration of parallel techniques. However, the performance was below of what we expected.

**Keywords:** Hardware, FPGA, OpenCL, codesign, heterogeneous-computing.

# **RESUMO**

OLIVEIRA DE SOUZA JUNIOR, C. A. A hardware/software codesign for the chemical reactivity of BRAMS . 2017. 109 f. Dissertação (Mestrado em Ciências – Ciências de Computação e Matemática Computacional) – Instituto de Ciências Matemáticas e de Computação (ICMC/USP), São Carlos – SP.

Várias atividades humanas dependem da previsão do tempo. Algumas delas são transporte, saúde, trabalho, segurança e agricultura. Tais atividades exigem solucões computacionais para previsão do tempo através de modelos numéricos. Estes modelos numéricos devem ser precisos e ágeis para serem processados no computador. Este projeto visa portar uma pequena parte do software do modelo de previsão de tempo do Brasil, o BRAMS — *Brazilian developments on the Regional Atmospheric Modelling System* — para uma arquitetura heterogênea composta por processadores Xeon (Intel) acoplados a um circuito reprogramável em FPGA via barramento PCIe. De acordo com os estudos, o termo da química da equação de continuidade da massa é o termo mais caro computacionalmente. Este termo calcula várias equações lineares do tipo Ax = b. Deste modo, este trabalho implementou estas equações em hardware, provendo um ćodigo portável e paralelo na linguagem OpenCL. O framework OpenCL também nos permitiu acoplar o código legado do BRAMS em Fortran90 junto com o hardware desenvolvido. Embora as ferramentas de desenvolvimento tenham apresentado vários problemas, a solução implementada mostrou-se viável com a exploração de técnicas de paralelismo. Entretando sua perfomance ficou muito aquém do desejado.

Palavras-chave: Hardware, FPGA, OpenCL, coprojeto, computação-heterogênea.

# LIST OF FIGURES

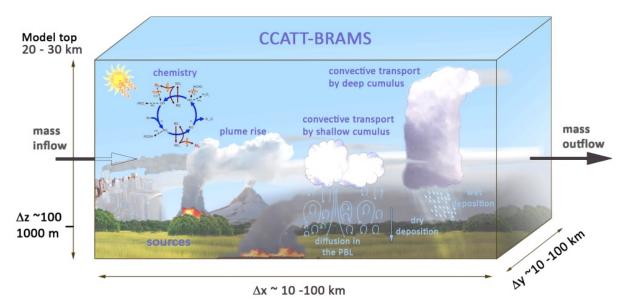

| Figure 1 –  | Simulation of CCAlT-BRAMS system, figure from (LONGO et al., 2013).                                                                                                                                                                                                                                                              | 31  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2 –  | Rosenbrock Method.                                                                                                                                                                                                                                                                                                               | 33  |

| Figure 3 –  | Jacobi Method algorithm.                                                                                                                                                                                                                                                                                                         | 37  |

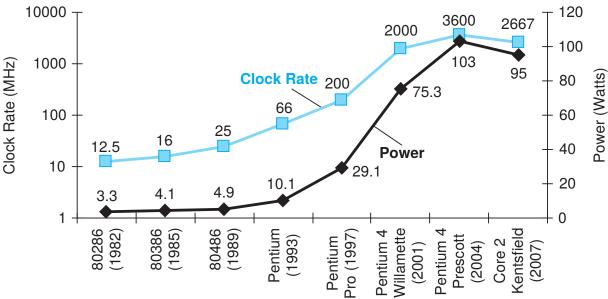

| Figure 4 –  | Clock rate and power increase of eight generations of Intel microprocessors, figure from (PATTERSON; HENNESSY, 2012)                                                                                                                                                                                                             | 38  |

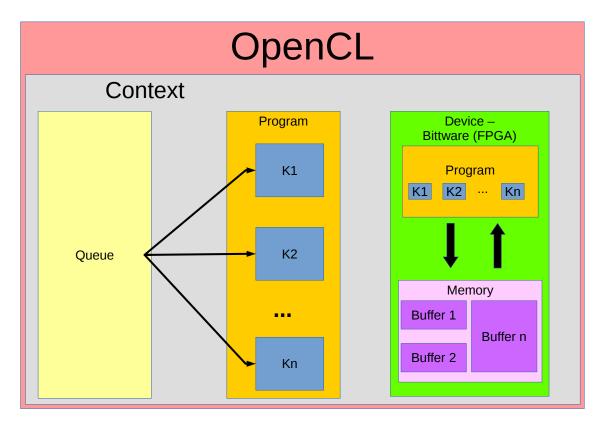

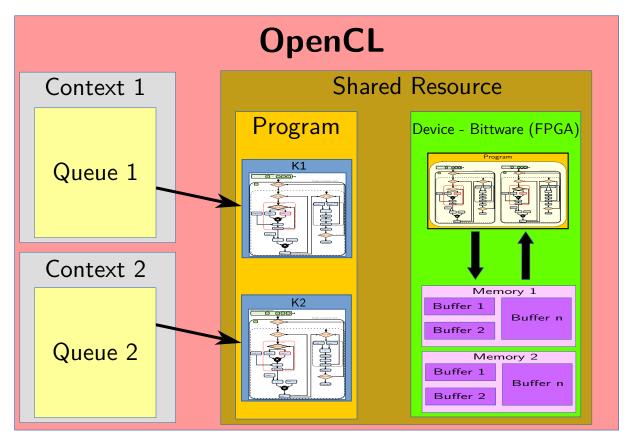

| Figure 5 –  | OpenCL Data Structures – Consider Program as a single data structure; we replicated it to make the understanding easier.                                                                                                                                                                                                         | 40  |

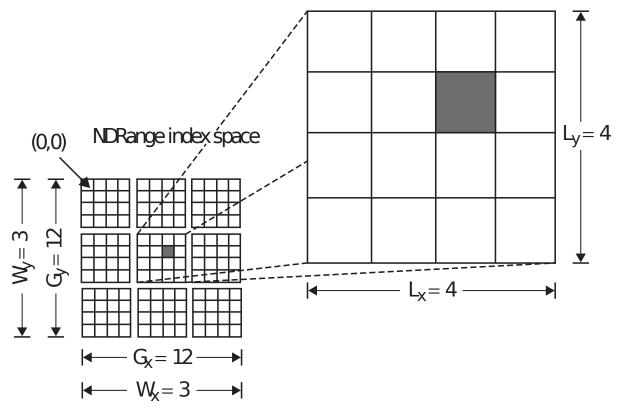

| Figure 6 –  | An example of how the global IDs, local IDs, and work-group indices are related for a two-dimensional NDRange. For this figure, we have the following indices: the shaded block has a global ID of $(g_x, g_y) = (6,5)$ , a work-group ID of $(w_x, w_y) = (1,1)$ plus a local ID of $(l_x, l_y) = (2,1)$ , figure from (MUNSHI, | 4.1 |

| E' 7        | 2009)                                                                                                                                                                                                                                                                                                                            | 41  |

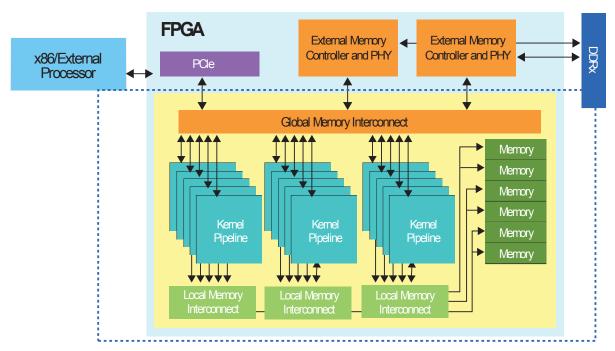

| Figure / –  | Components from OpenCL system on Intel FPGAs, figure from (ALTERA, 2013)                                                                                                                                                                                                                                                         | 42  |

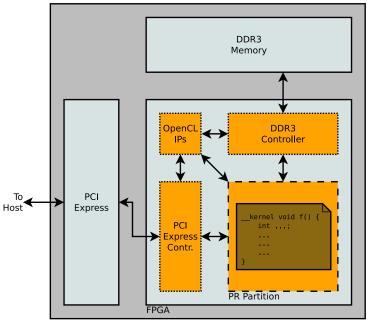

| Figure 8 –  | Partitioning of the FPGA. PCIe, DDR3 controller and IPs are every project of OpenCL, so only the remaining is available for the kernels, figure granted by André Perina                                                                                                                                                          | 42  |

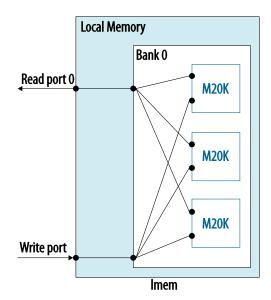

| Figure 0    | Implementation of local memory with three M20K blocks, figure from (IN-                                                                                                                                                                                                                                                          | 42  |

| rigule 9 –  |                                                                                                                                                                                                                                                                                                                                  | 43  |

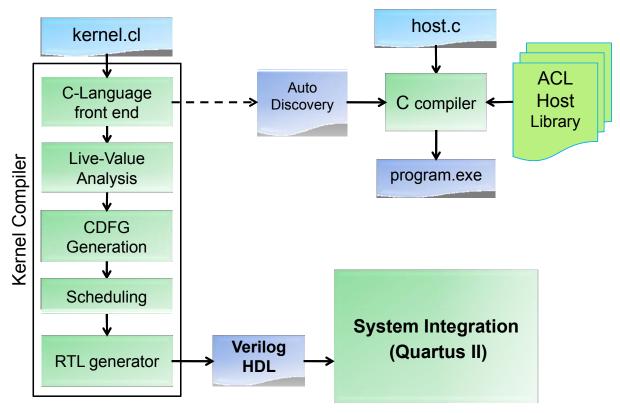

| Figure 10 – |                                                                                                                                                                                                                                                                                                                                  | 44  |

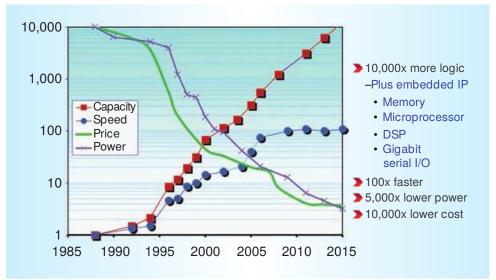

| Figure 11 – | Xilinx field-programmable gate array (FPGA) progression. (Price and power are per logic cell.), figure from (AHMAD <i>et al.</i> , 2016)                                                                                                                                                                                         | 45  |

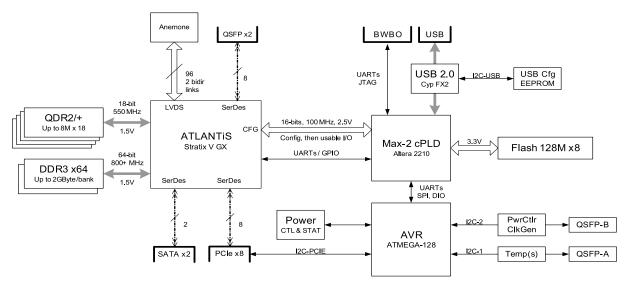

| Figure 12 – | Top-Level Component Implementation Block Diagram, figure from (BITTWARE                                                                                                                                                                                                                                                          | ,   |

|             | 2015).                                                                                                                                                                                                                                                                                                                           | 46  |

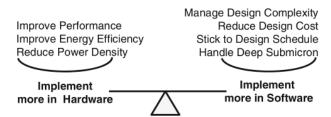

| Figure 13 – | Driving factors in hardware/software codesign, figure from (SCHAUMONT, 2012)                                                                                                                                                                                                                                                     | 48  |

| Figure 14 – | Speedup compared to CPU versions. The <i>x</i> dimension stands for matrix size, and <i>y</i> dimension speedup in FPGA                                                                                                                                                                                                          | 50  |

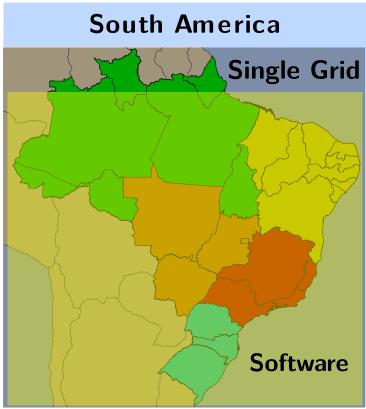

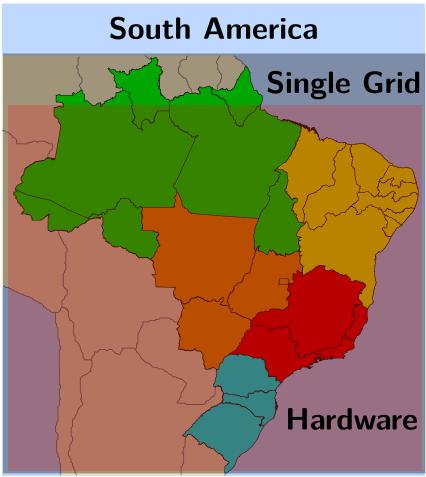

| Figure 15 – | Generic representation of BRAMS system with a single process. In this figure, we present BRAMS over the South America with a single grid, yellow                                                                                                                                                                                 |     |

|             | square represents Sparse1.3 running for all the points over the grid                                                                                                                                                                                                                                                             | 56  |

| Figure 16 – Generic representation of BRAMS system with MPI processes. In this figure 16 – Generic representation of BRAMS system with MPI processes. In this figure 16 – Generic representation of BRAMS system with MPI processes. In this figure 16 – Generic representation of BRAMS system with MPI processes. In this figure 16 – Generic representation of BRAMS system with MPI processes. In this figure 16 – Generic representation of BRAMS system with MPI processes. In this figure 16 – Generic representation of BRAMS system with MPI processes. In this figure 16 – Generic representation of BRAMS system with MPI processes. In this figure 16 – Generic representation of BRAMS system with MPI processes. In this figure 16 – Generic representation of BRAMS system with MPI processes. In this figure 16 – Generic representation of BRAMS system with America with a single grid distribution over N processes, each process executes Sparse 1.3 for its set of points of the process of the | ited         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| grid. The shaded areas are the ghost zones, i.e. the shared data area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56           |

| Figure 17 – Generic representation of BRAMS coupled to the Jacobi method in Hardy In this figure, we present BRAMS over the South America with a single red square represents Jacobi hardware circuit. Such circuit computes all points over the grid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | grid,<br>the |

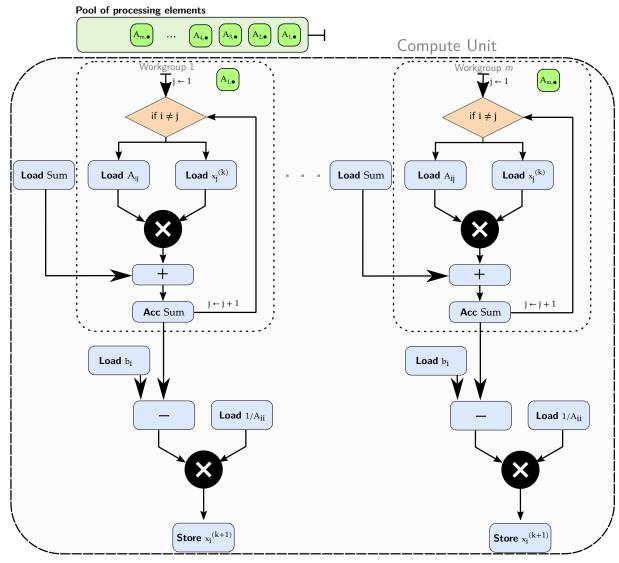

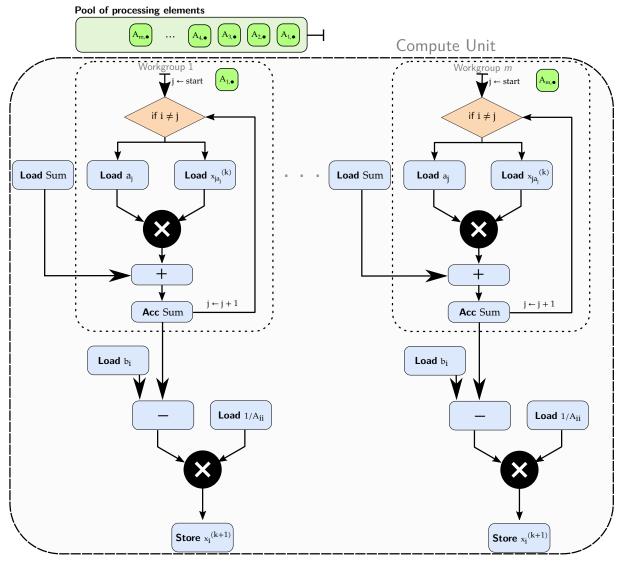

| Figure 18 – Schematic of Jacobi method with multiple threads with dense representations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

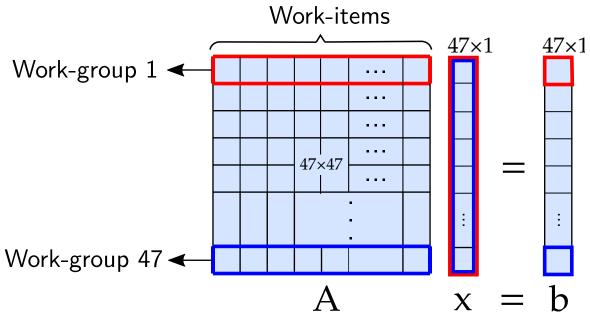

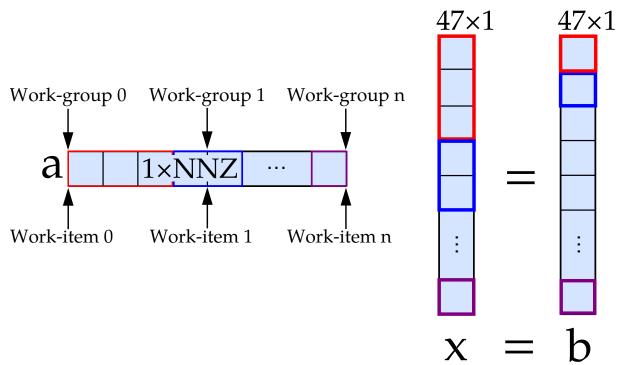

| Figure 19 – Each color represents one work-group, each work-group has 47 work-it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

| According to the verilog, two work-groups are executing at the same time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

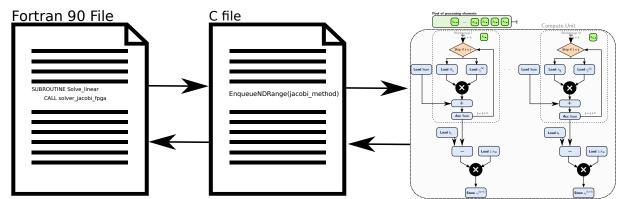

| Figure 20 – Interoperability of BRAMS and OpenCL. Fortran calls a function from the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |

| host, which in turn is responsible to manage the device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

| Figure 21 – Schematic of Jacobi method with multiple threads with sparse represent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |

| Figure 22 – Each color represents one work-group, each work-group has one work-i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

| In this manner, the number of work-items is equal to the number of work-g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |

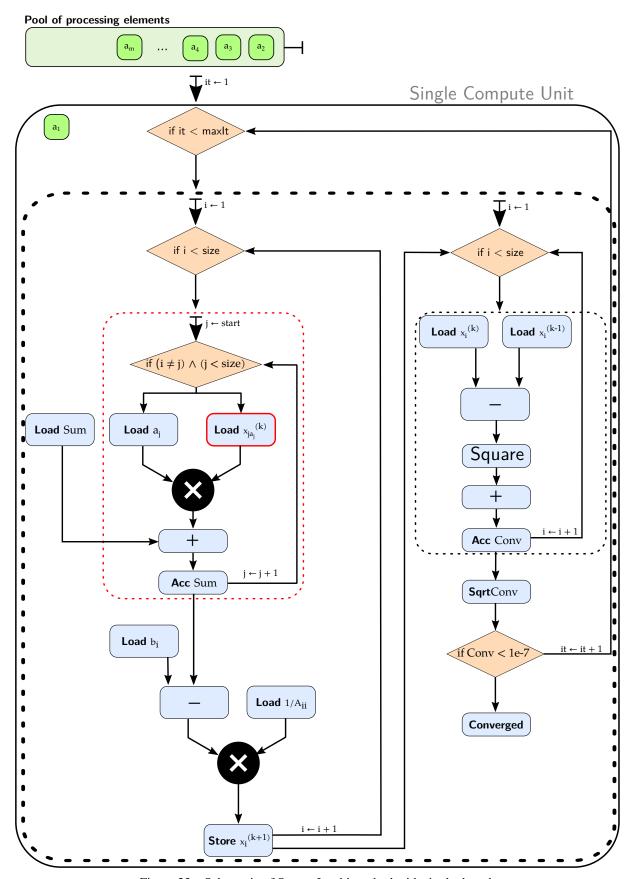

| Figure 23 – Schematic of Sparse Jacobi method with single thread                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 66           |

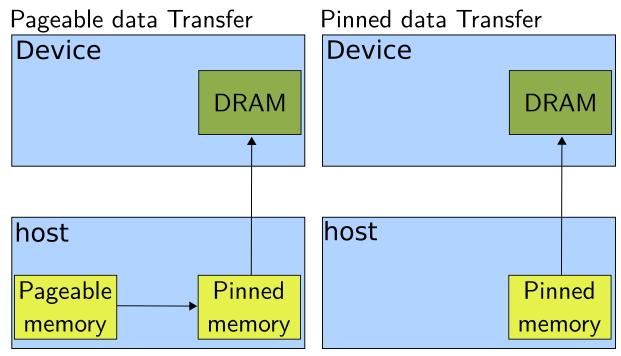

| Figure 24 – How pageable and pinned memory data transfer work, based on Harris (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2012). 67    |

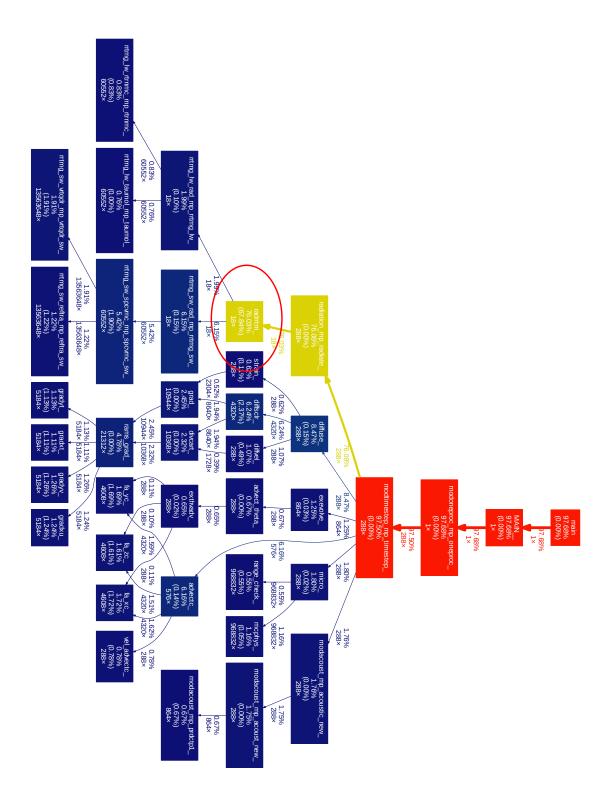

| Figure 25 – Call Graph for BRAMS with chemical module disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70           |

| Figure 26 – Call Graph for BRAMS with chemical module enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 71           |

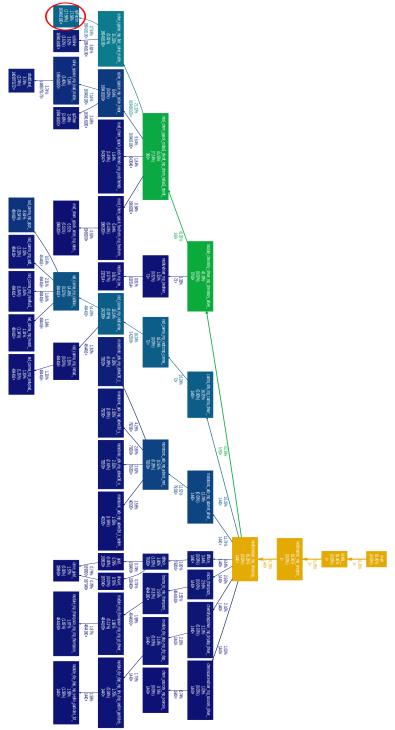

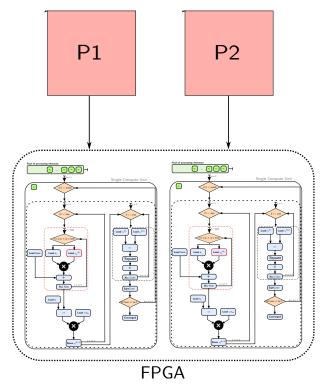

| Figure 27 – Each MPI process accesses a copy of the kernel (an FPGA circuit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72           |

| Figure 28 - OpenCL data structures - Program, Device and Memory buffers are sha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ared         |

| among MPI processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73           |

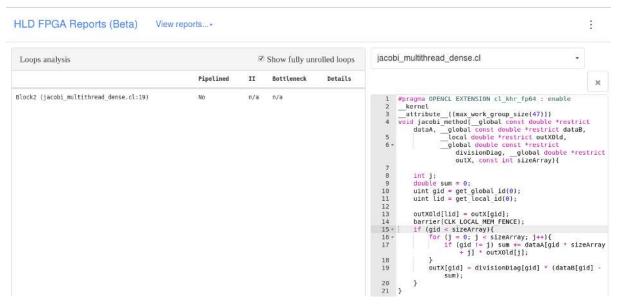

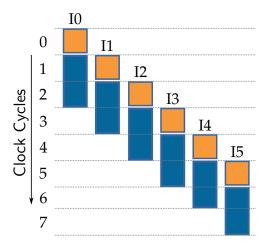

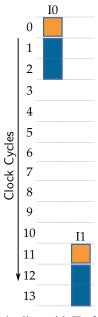

| Figure 29 – Pipeline report for Jacobi multi-threaded dense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 74           |

| Figure 30 - CPU communicates with FPGA for every iteration. CPU sends to the FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 'GA          |

| the initial data, after FPGA processing it, the FPGA returns the result to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | the          |

| CPU, which in turn computes the vector norm and decides if it sends and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

| data or computes another iteration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |

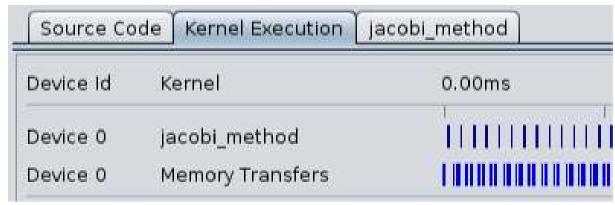

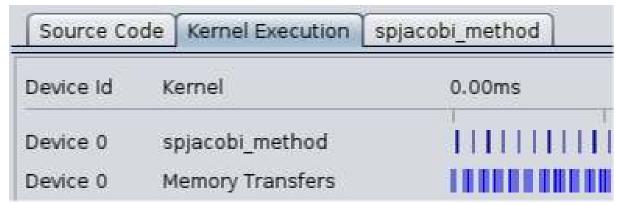

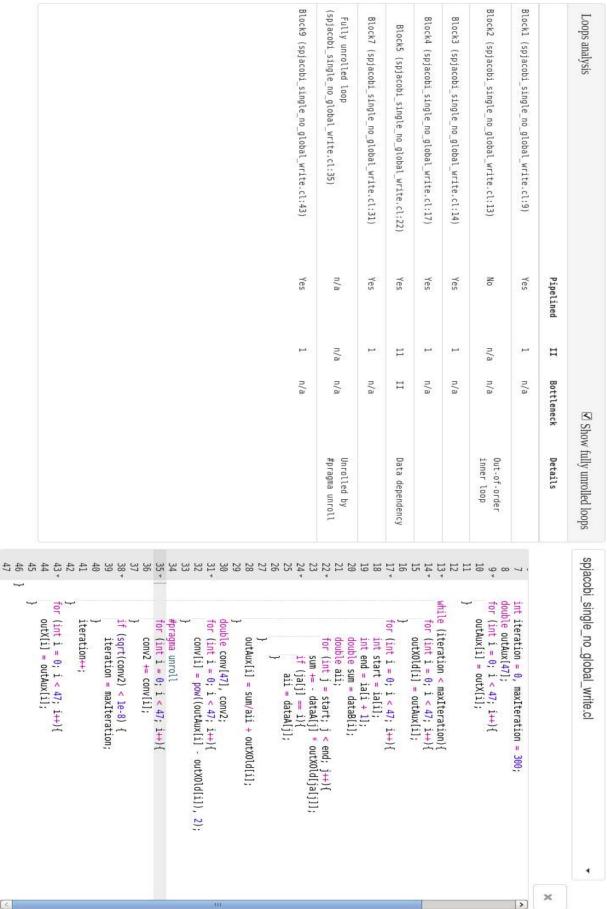

| Figure 31 – Communication and execution time with Intel FPGA SDK profiling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |

| kernels. Note that there is much more communication than computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

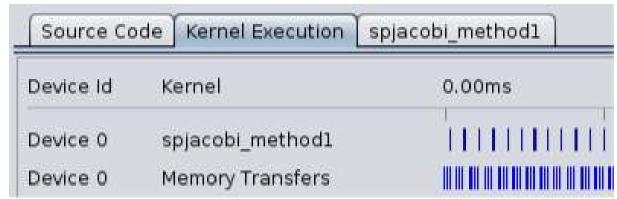

| Figure 32 – Efficiency of Jacobi multi-threaded dense with Intel FPGA SDK profiling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |

| kernels. The red line points that the global memory reads (line 22) are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

| bottleneck of the application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |

| Figure 33 – Statistics of Jacobi multi-threaded dense with Intel FPGA SDK profiling kernels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

| Figure 34 – Efficiency of Jacobi multi-threaded sparse with Intel FPGA SDK profi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

| for kernels. Sparse format causes a severe drop of performance when sar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |