# Florida International University FIU Digital Commons

FIU Electronic Theses and Dissertations

University Graduate School

3-25-2016

# A High Performance Advanced Encryption Standard (AES) Encrypted On-Chip Bus Architecture for Internet-of-Things (IoT) Systemon-Chips (SoC)

Xiaokun Yang Florida International University, xyang001@fiu.edu

### **DOI:** 10.25148/etd.FIDC000248

Follow this and additional works at: https://digitalcommons.fiu.edu/etd

C Part of the <u>Computer and Systems Architecture Commons</u>, <u>Digital Circuits Commons</u>, <u>Hardware Systems Commons</u>, and the <u>VLSI and Circuits</u>, <u>Embedded and Hardware Systems</u> <u>Commons</u>

#### **Recommended** Citation

Yang, Xiaokun, "A High Performance Advanced Encryption Standard (AES) Encrypted On-Chip Bus Architecture for Internet-of-Things (IoT) System-on-Chips (SoC)" (2016). *FIU Electronic Theses and Dissertations*. 2477. https://digitalcommons.fiu.edu/etd/2477

This work is brought to you for free and open access by the University Graduate School at FIU Digital Commons. It has been accepted for inclusion in FIU Electronic Theses and Dissertations by an authorized administrator of FIU Digital Commons. For more information, please contact dcc@fu.edu.

## FLORIDA INTERNATIONAL UNIVERSITY

Miami, Florida

# A HIGH PERFORMANCE ADVANCED ENCRYPTION STANDARD (AES) ENCRYPTED ON-CHIP BUS ARCHITECTURE FOR INTERNET-OF-THINGS (IOT) SYSTEM-ON-CHIPS (SOC)

A dissertation submitted in partial fulfillment of the

requirements for the degree of

## DOCTOR OF PHILOSOPHY

in

# ELECTRICAL ENGINEERING

by

Xiaokun Yang

2016

# To: Interim Dean Ranu Jung College of Engineering and Computing

This dissertation, written by Xiaokun Yang, and entitled A High Performance Advanced Encryption Standard (AES) Encrypted On-Chip Bus Architecture for Internet-of-Things (IoT) System-on-Chips (SoC), having been approved in respect to style and intellectual content, is referred to you for judgment.

We have read this dissertation and recommend that it be approved.

Gang Quan

Hai Deng

Deng Pan

Malek Adjouadi

Jean H. Andrian, Major Professor

Date of Defense: March 25, 2016

The dissertation of Xiaokun Yang is approved.

Interim Dean Ranu Jung College of Engineering and Computing

Andrés G. Gil Vice President for Research and Economic Development and Dean of the University Graduate School

Florida International University, 2016

© Copyright 2016 by Xiaokun Yang All rights reserved.

# DEDICATION

I dedicate this dissertation to my wife and my parents. Without their encourage, understanding, and most of all love, the completion of this work would not have been possible.

#### ACKNOWLEDGMENTS

First and foremost, I am grateful to my major advisor, Dr. Jean H. Andrian, for being friendly, caring, supportive, and help in numerous ways. Without his support, I could not have done what I was able to do. He was very generous in sharing his experiences on electrical and computer engineering, academic life and beyond. He is not only my adviser, but also, a friend inspiring me for the rest of my life.

Next, I would like to thank the members of my committee, Dr. Gang Quan, Dr. Hai Deng, Dr. Deng Pan, and Dr. Malek Adjouadi, for their support and suggestions in improving the quality of this dissertation. It is truly honored to have such great fantastic and knowledgeable professors serving as my committee members.

I would also like to thank all the lab mates and members at the Wireless Communications and Networking Laboratory for creating an amazing working environment, and thank my friends, Dr. Tianyi Wang and Dr. Nansong Wu, for their assistance on work related to my research.

Furthermore, I would also like to acknowledge the research support provided from the Department of Electrical and Computer Engineering at Florida International University, and the dissertation year fellowship from the graduate school during my dissertation research.

Finally, I want to thank my family for their unconditional love, faith, and encouragement.

# ABSTRACT OF THE DISSERTATION A HIGH PERFORMANCE ADVANCED ENCRYPTION STANDARD (AES) ENCRYPTED ON-CHIP BUS ARCHITECTURE FOR INTERNET-OF-THINGS (IOT) SYSTEM-ON-CHIPS (SOC)

by

Xiaokun Yang Florida International University, 2016 Miami, Florida Professor Jean H. Andrian, Major Professor

With industry expectations of billions of Internet-connected things, commonly referred to as the IoT, we see a growing demand for high-performance on-chip bus architectures with the following attributes: small scale, low energy, high security, and highly configurable structures for integration, verification, and performance estimation.

Our research thus mainly focuses on addressing these key problems and finding the balance among all these requirements that often work against each other. First of all, we proposed a low-cost and low-power System-on-Chips (SoCs) architecture (IBUS) that can frame data transfers differently. The IBUS protocol provides two novel transfer modes the block and state modes, and is also backward compatible with the conventional linear mode. In order to evaluate the bus performance automatically and accurately, we also proposed an evaluation methodology based on the standard circuit design flow. Experimental results show that the IBUS based design uses the least hardware resource and reduces energy consumption to a half of an AMBA Advanced High-Performance Bus (AHB) and Advanced eXensible Interface (AXI). Additionally, the valid bandwidth of the IBUS based design is 2.3 and 1.6 times, respectively, compared with the AHB and AXI based implementations. As IoT advances, privacy and security issues become top tier concerns in addition to the high performance requirement of embedded chips. To leverage limited resources for tiny size chips and overhead cost for complex security mechanisms, we further proposed an advanced IBUS architecture to provide a structural support for the block-based AES algorithm. Our results show that the IBUS based AES-encrypted design costs less in terms of hardware resource and dynamic energy (60.2%), and achieves higher throughput ( $\times$ 1.6) compared with AXI.

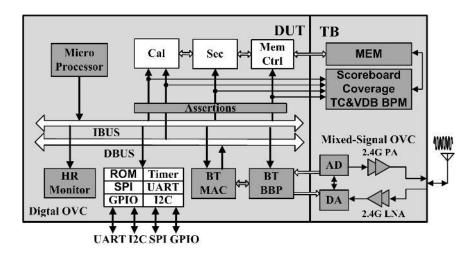

Effectively dealing with the automation in design and verification for mixedsignal integrated circuits is a critical problem, particularly when the bus architecture is new. Therefore, we further proposed a configurable and synthesizable IBUS design methodology. The flexible structure, together with bus wrappers, direct memory access (DMA), AES engine, memory controller, several mixed-signal verification intellectual properties (VIPs), and bus performance models (BPMs), forms the basic for integrated circuit design, allowing engineers to integrate application-specific modules and other peripherals to create complex SoCs.

# TABLE OF CONTENTS

| CHAPTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PAGE |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1    |

| 1.1 High Performance On-Chip Bus Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| 1.2 High Security On-Chip Bus Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| 1.3 Verification And Performance Evaluation Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| 1.3.1     Design Automation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 1.4 The Research Problems And Our Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 1.5     Structure Of The Dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| 2. BACKGROUND AND RELATED WORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17   |

| 2.1 Related Work On High Performance On-Chip Bus Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| 2.1.1 High Performance Bus Protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| 2.1.1       Ingli l'enformatice Dus l'hotocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| 2.2 Related Work On Hardware Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| 2.2       Iterated work on nardware becunty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 2.2.1       Oryptosystems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| 2.3 Related Work On Verification and Performance Evaluation Methodolo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| 2.3.1 Integrated Circuit Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 00   |

| 2.3.2 Verification Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| 2.3.3       Verification Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 2.3.4 Mixed-Signal Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 2.4 Related Work On Computer Aided Design Automation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| 2.4.1 IP Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| 2.4.2 Flexible Verification Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| 2.4.3 Automatic Performance Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| 2.5         Summary         Su |      |

| 3. IBUS Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42   |

| 3.1 Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 3.2 IBUS Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| 3.2.1 IBUS Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| 3.2.2 IBUS Transfer Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| 3.2.3 Linear and Block Transfer Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| 3.3 Analytical Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| 3.3.1 Transfer Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| 3.3.2 Wire Efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| 3.3.3 Valid Data Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| 3.3.4 Dynamic Energy and Dynamic Energy Efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| 3.4 Hardware Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 3.4.1 RTL Design and Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| 3.4.1     RTE Design and Vermeaton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| Sine End Ford Interjoid I I I I I I I I I I I I I I I I I I I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 00   |

| 3.5                  | Experimental and Modeling Results                                       | 63       |

|----------------------|-------------------------------------------------------------------------|----------|

| 3.6                  | Summary                                                                 | 65       |

| 4. F                 | Performance Evaluation Methodology                                      | 67       |

| 4.1                  | Related Work                                                            | 67       |

| 4.2                  | State Transfer Introduction                                             | 71       |

| 4.2<br>4.3           | Static Performance Analysis                                             | 71       |

| 4.3<br>4.3.1         |                                                                         | 75 75    |

| 4.3.1<br>4.3.2       |                                                                         | 75<br>76 |

| 4.3. <i>2</i><br>4.4 |                                                                         | 70<br>78 |

|                      | Performance Evaluation Methodology                                      |          |

| 4.4.1                |                                                                         | 79       |

| 4.4.2                |                                                                         | 81       |

| 4.4.3                |                                                                         | 84       |

| 4.5                  | A Case Study: Applying The Methodology To Evaluate AHB, AXI4 and        |          |

|                      | ASBUS performance                                                       | 86       |

| 4.5.1                |                                                                         | 87       |

| 4.5.2                |                                                                         | 87       |

| 4.5.3                |                                                                         | 90       |

| 4.5.4                | Experimental Results                                                    | 95       |

| 4.6                  | Summary                                                                 | 98       |

|                      |                                                                         |          |

|                      | an Advanced AES-Encrypted IBUS Architecture                             |          |

| 5.1                  | Related Work                                                            |          |

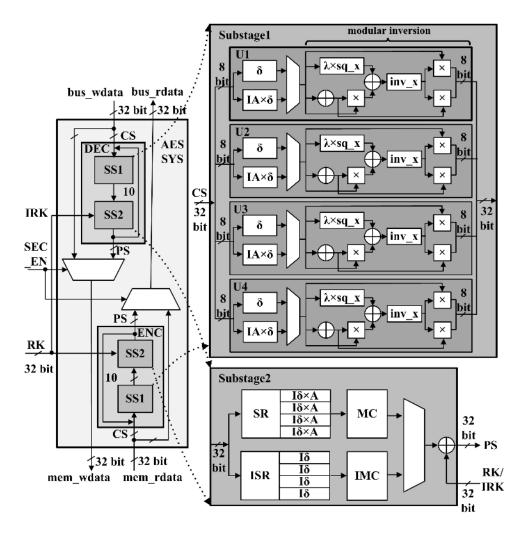

| 5.2                  | AES-Encrypted Circuit                                                   |          |

| 5.2.1                |                                                                         |          |

| 5.2.2                |                                                                         |          |

| 5.2.3                | AES Circuit Performance Analysis                                        | 111      |

| 5.3                  | AES-Encrypted IBUS Protocol                                             | 112      |

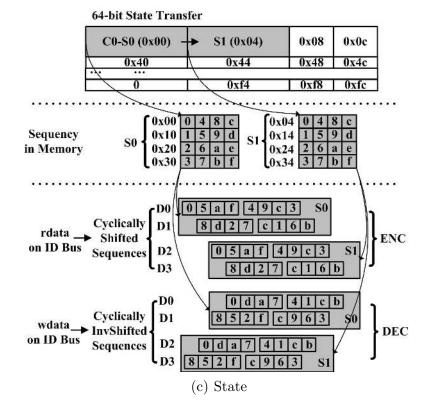

| 5.3.1                | State Transfer Mode                                                     | 112      |

| 5.3.2                | Transfer Latency Models                                                 | 120      |

| 5.3.3                | Static Performance Analysis                                             | 124      |

| 5.4                  | Hardware Implementation                                                 | 126      |

| 5.4.1                | RTL Design and Verification                                             | 127      |

| 5.4.2                | Area and Power Analysis                                                 | 131      |

| 5.5                  | Experimental Results                                                    |          |

| 5.6                  | Summary                                                                 |          |

|                      |                                                                         |          |

|                      | Configurable and Synthesizable IBUS Architecture for Integrating Indus- |          |

| $\mathbf{t}$         | rial Standard IPs                                                       | 139      |

| 6.1                  | Related Work $\ldots$                                                   | 139      |

| 6.2                  | IBUS Architecture                                                       | 141      |

| 6.2.1                | IBUS Structure                                                          | 142      |

| 6.2.2                | IBUS Protocol                                                           | 143      |

| 6.3 IBUS SoC Integration                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.3.1 AXI and IBUS Static Analysis                                                                                                                               |

| 6.3.2 Integration Configuration                                                                                                                                  |

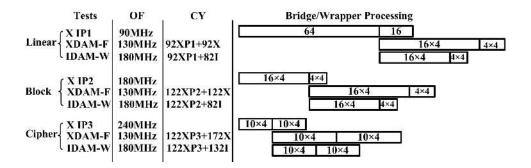

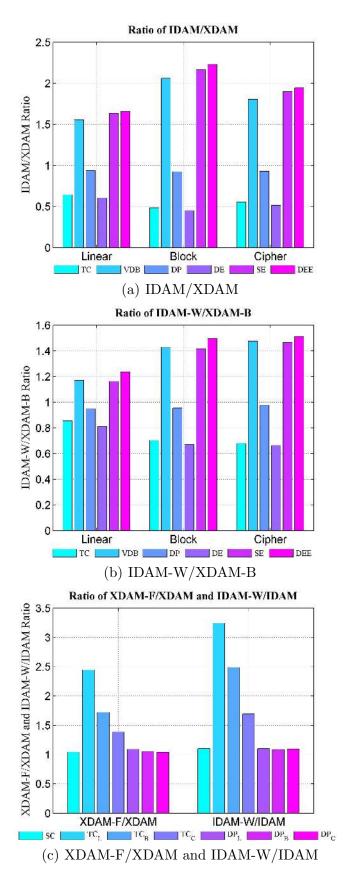

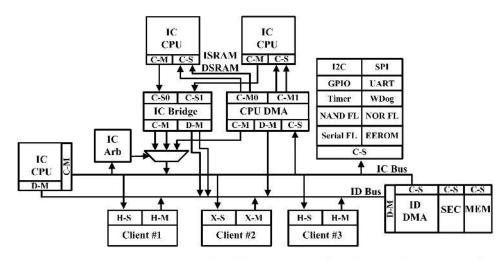

| 6.4 Case Studies and Experimental Results                                                                                                                        |

| 6.4.1 SoC Environment                                                                                                                                            |

| 6.4.2 IBUS Structure Configuration                                                                                                                               |

| 6.5 IBUS Performance Analysis                                                                                                                                    |

| 6.5.1 Implementation Flow $\ldots \ldots \ldots$ |

| 6.5.2 Performance Analysis                                                                                                                                       |

| 6.6 Summary                                                                                                                                                      |

| 7. CONCLUSIONS AND FUTURE WORK                                                                                                                                   |

| 7.1 Summary                                                                                                                                                      |

| 7.1         Summary                                                                                                                                              |

| 7.2 Future work                                                                                                                                                  |

| BIBLIOGRAPHY                                                                                                                                                     |

| VITA                                                                                                                                                             |

| TAB | LE PAGE                                  | £ |

|-----|------------------------------------------|---|

| 3.1 | 32-bit IC Bus Signal                     | 5 |

| 3.2 | 32-bit ID Bus Signal                     | 3 |

| 3.3 | Resource Comparison                      | 9 |

| 3.4 | Power Comparison                         | 1 |

| 3.5 | Experimental Performance Metrics         | 3 |

| 3.6 | Model Performance Metrics                | 4 |

| 4.1 | Resource Cost                            | 5 |

| 4.2 | Power Report                             | 3 |

| 4.3 | Experimental Results                     | 5 |

| 4.4 | Modeling Results                         | 3 |

| 5.1 | AES ENC/DEC Gate Count and Critical Path | 1 |

| 5.2 | Modeling Performance Comparison          | 3 |

| 5.3 | Resource Comparison                      | 2 |

| 5.4 | Power Consumption                        | 3 |

| 5.5 | Experimental Results Comparison          | 4 |

| 6.1 | Wrapper Configuration                    | 1 |

| 6.2 | Performance Evaluation                   | 5 |

# LIST OF TABLES

# LIST OF FIGURES

| FIGU | URE                                                          | PA | GE |

|------|--------------------------------------------------------------|----|----|

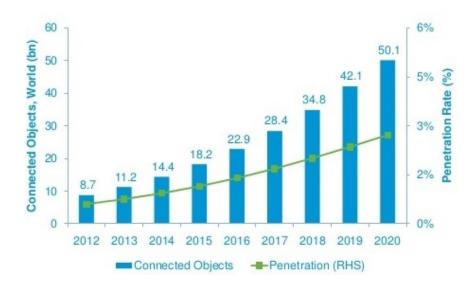

| 1.1  | Number of Internet-Connected Things [11]                     | •  | 2  |

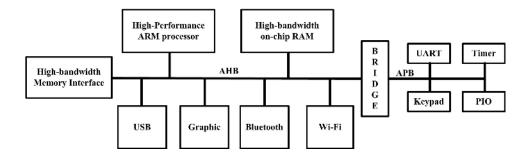

| 1.2  | A Typical AMBA Architecture [1].                             | •  | 3  |

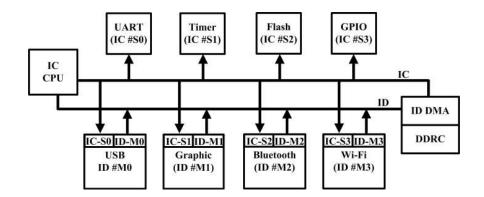

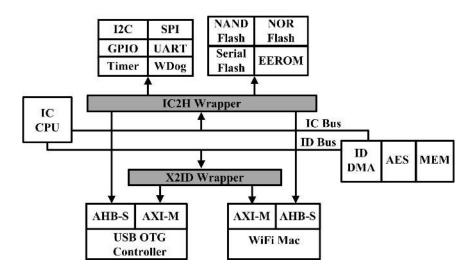

| 1.3  | A Typical IBUS Architecture.                                 | •  | 4  |

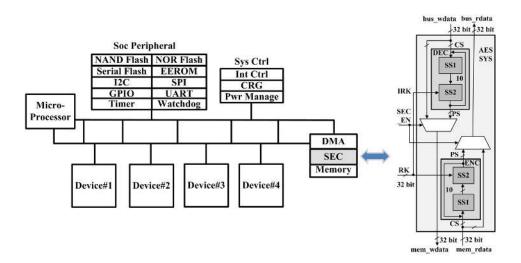

| 1.4  | A Typical IBUS Architecture with an AES Engine.              | •  | 6  |

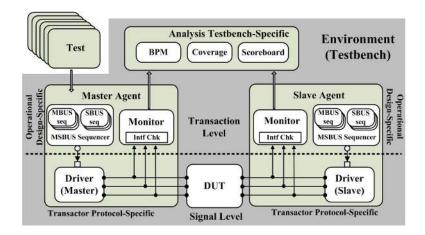

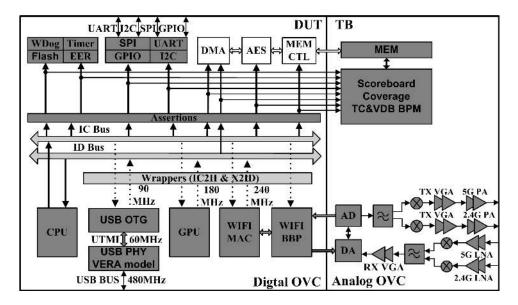

| 1.5  | Mixed-Signal OVC                                             | •  | 8  |

| 1.6  | Connecting Speed of Things [11].                             | •  | 13 |

| 2.1  | Pseudo Code for the AES Algorithm                            | •  | 26 |

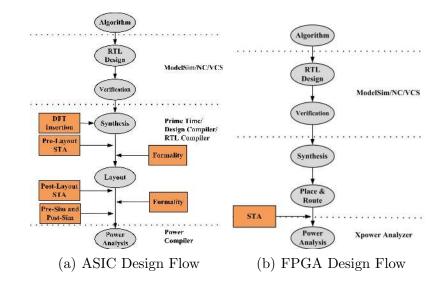

| 2.2  | Integrated Circuit Design Flow                               | •  | 31 |

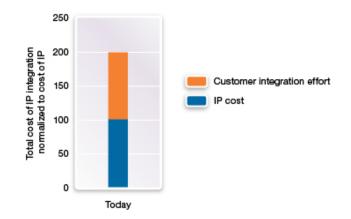

| 2.3  | The effort to integrate is similar to the cost of IP. $[73]$ | •  | 38 |

| 3.1  | IBUS Architecture.                                           | •  | 45 |

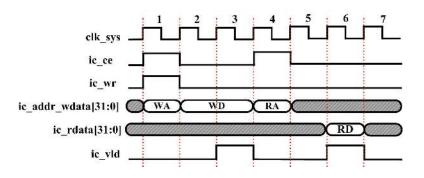

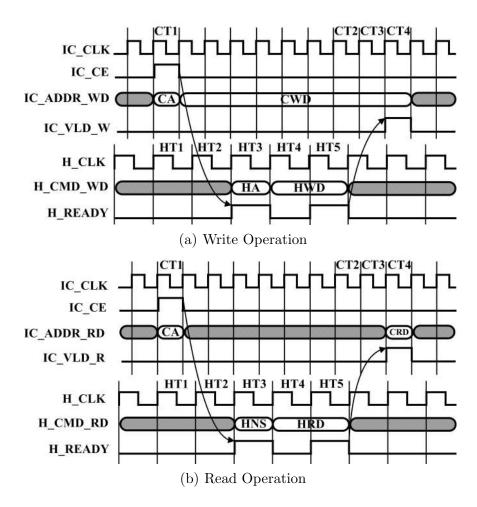

| 3.2  | IC Bus Protocol.                                             | •  | 48 |

| 3.3  | ID Bus Protocol.                                             | •  | 49 |

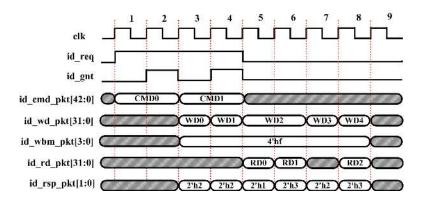

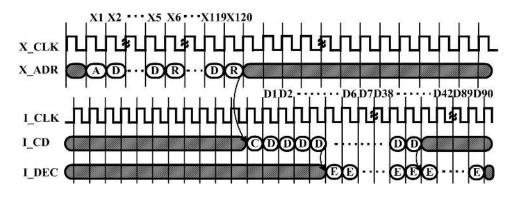

| 3.4  | ID bus Block Transfer.                                       | •  | 50 |

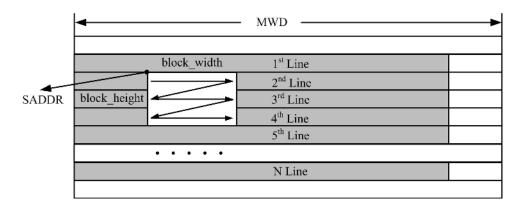

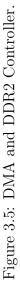

| 3.5  | DMA and DDR2 Controller.                                     | •  | 55 |

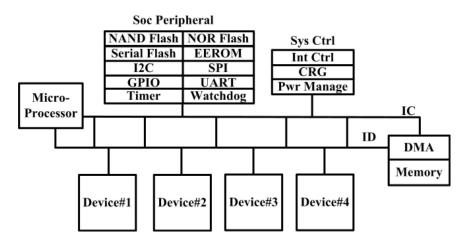

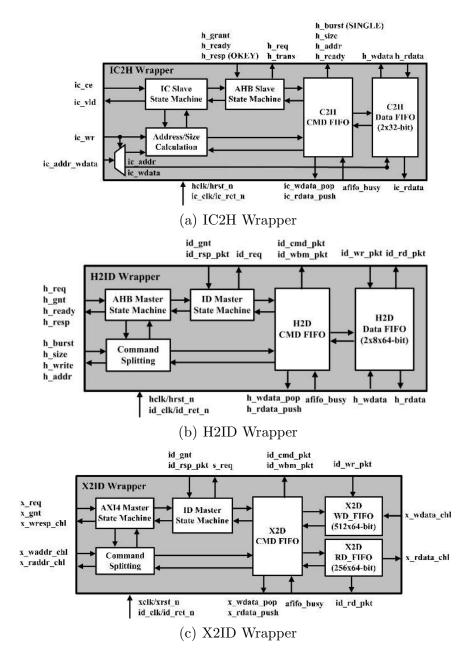

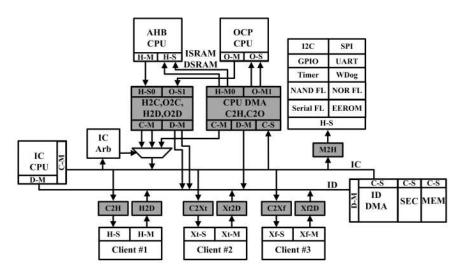

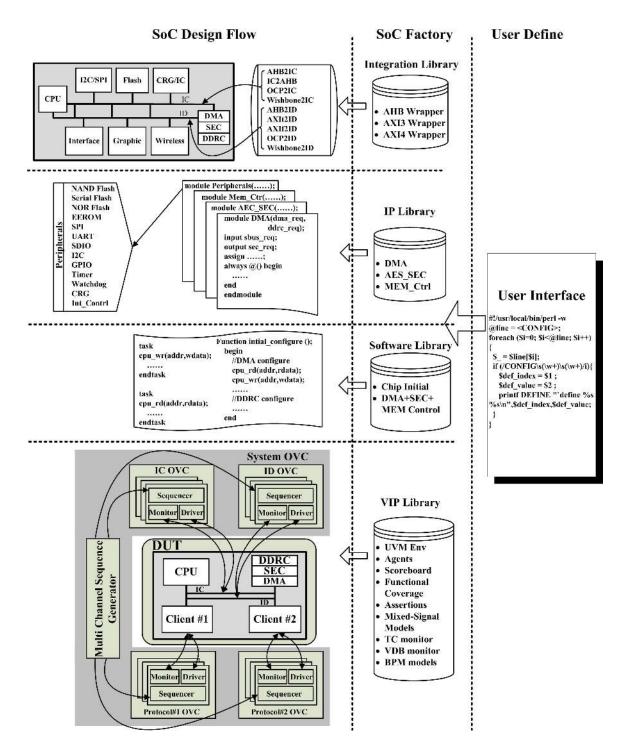

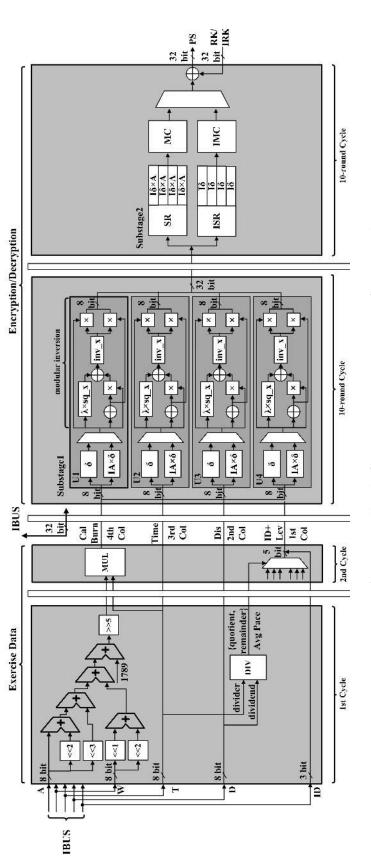

| 3.6  | A Typical IBUS-Based SoC.                                    | •  | 57 |

| 3.7  | An Example of AHB and IBUS Transfers.                        | •  | 58 |

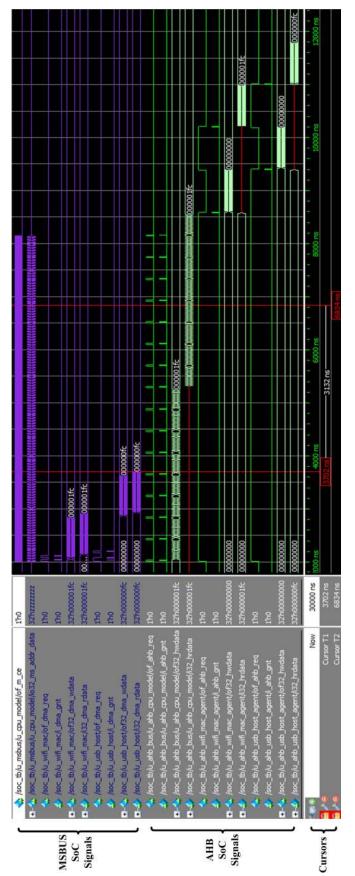

| 3.8  | Synthesis Schematics.                                        | •  | 60 |

| 3.9  | Resource Costs.                                              | •  | 61 |

| 3.10 | Power Consumption                                            | •  | 62 |

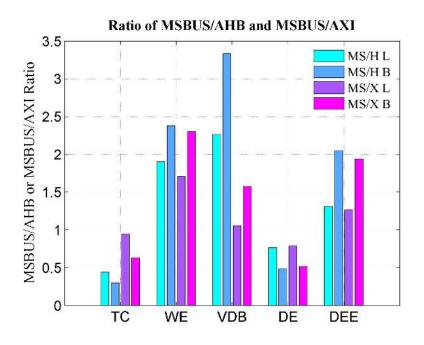

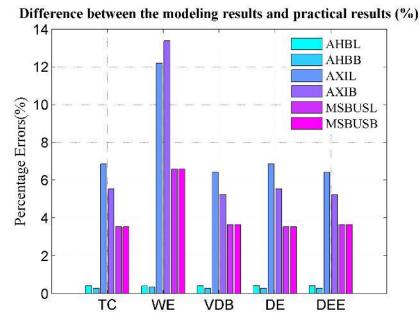

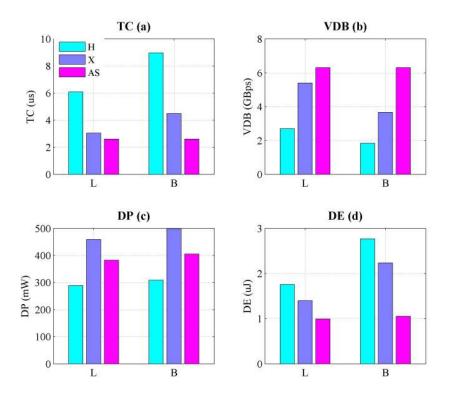

| 3.11 | Performance Ratio of IBUS/AHB and IBUS/AXI                   | •  | 64 |

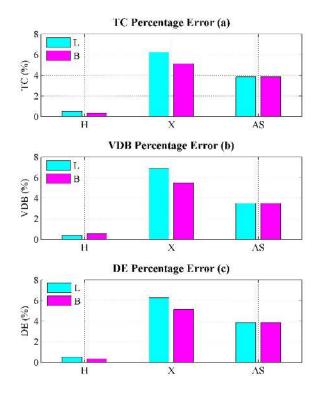

| 3.12 | Performance Model Error.                                     | •  | 65 |

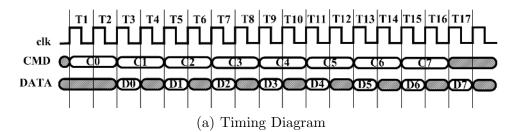

| 4.1  | An Example of the Linear Transfer                            | •  | 73 |

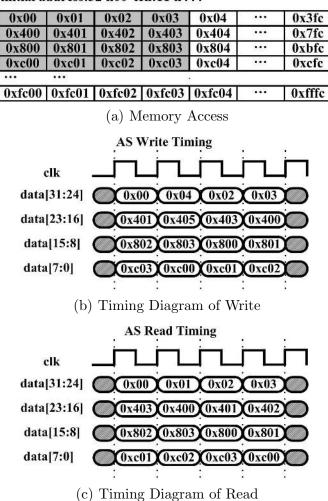

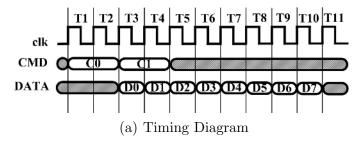

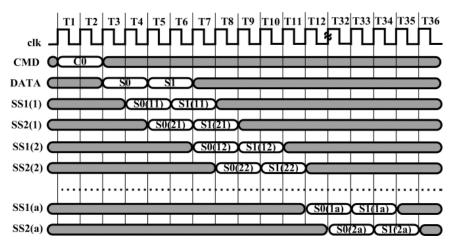

| 4.2  | An Example of the AS Transfer                                | •  | 74 |

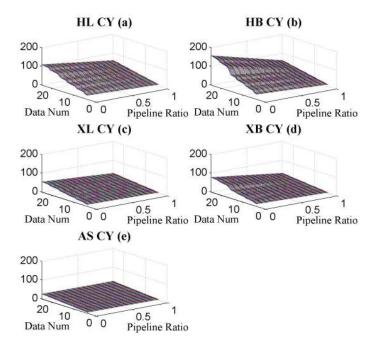

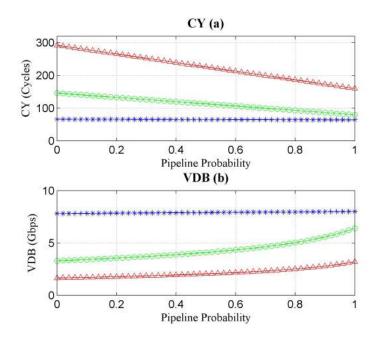

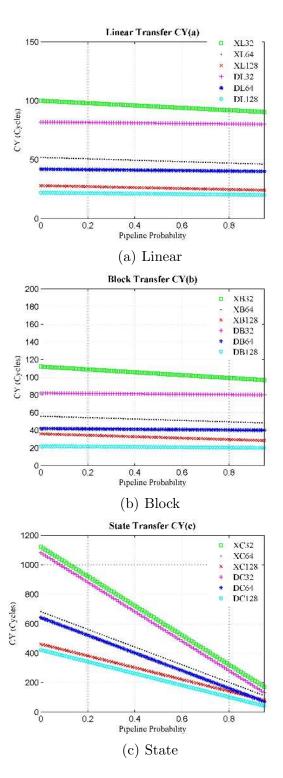

| 4.3  | CY Comparison.                                               | •  | 77 |

| 4.4                                                                                                                                           | Performance Evaluation (AHB(), AXI4(O), ASBUS (*)) $\dots \dots $                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

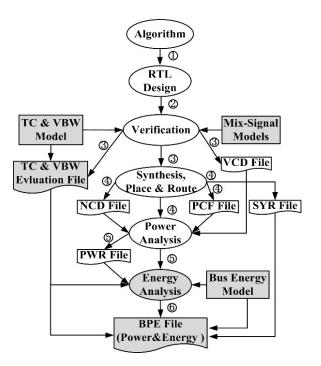

| 4.5                                                                                                                                           | Hardware Implementation Flow                                                                                                                                                                                                                                                                                                                                                                                                                   |

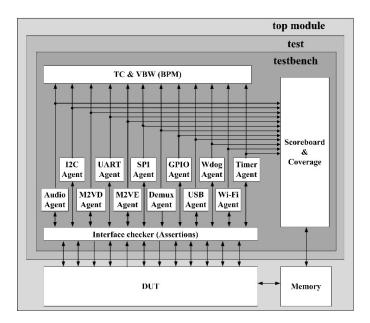

| 4.6                                                                                                                                           | Verification Environment                                                                                                                                                                                                                                                                                                                                                                                                                       |

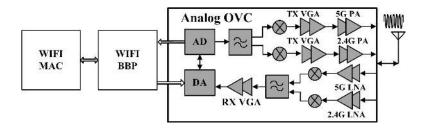

| 4.7                                                                                                                                           | Wi-Fi Model                                                                                                                                                                                                                                                                                                                                                                                                                                    |

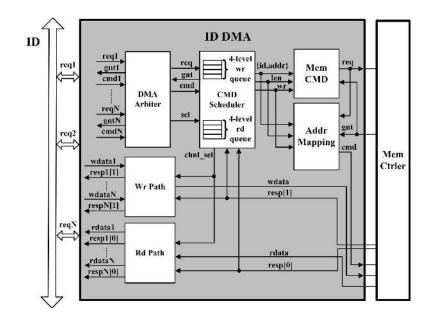

| 4.8                                                                                                                                           | ID DMA Structure                                                                                                                                                                                                                                                                                                                                                                                                                               |

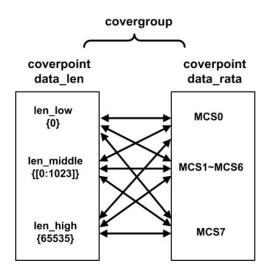

| 4.9                                                                                                                                           | Cover Group                                                                                                                                                                                                                                                                                                                                                                                                                                    |

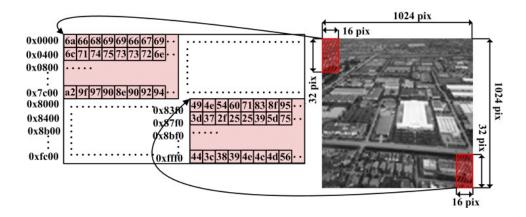

| 4.10                                                                                                                                          | Interleaving Block Test Case                                                                                                                                                                                                                                                                                                                                                                                                                   |

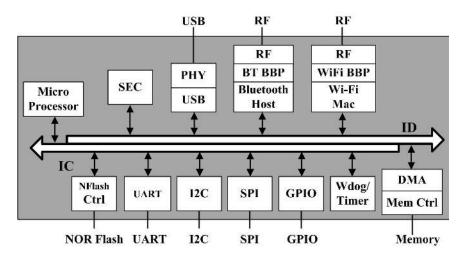

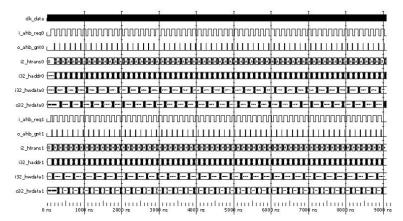

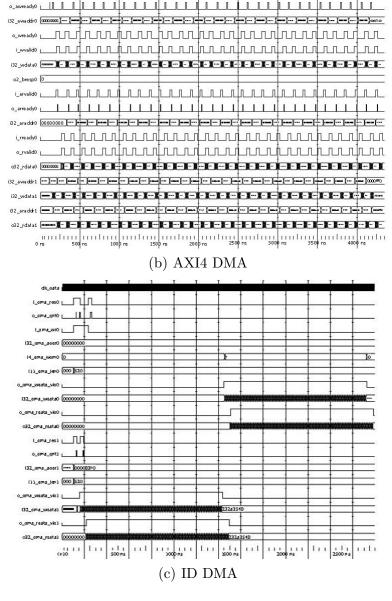

| 4.11                                                                                                                                          | Timing Diagrams of the Linear Tests                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.12                                                                                                                                          | Timing Diagrams of the Block Tests                                                                                                                                                                                                                                                                                                                                                                                                             |

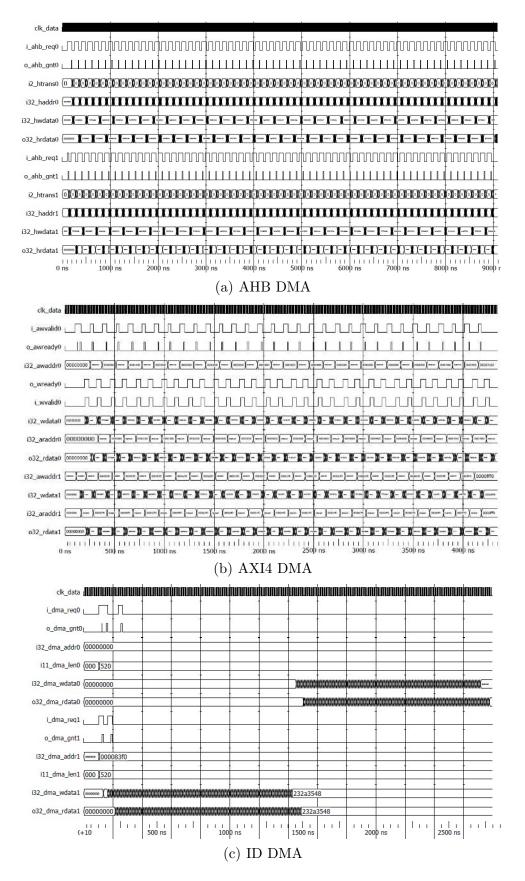

| 4.13                                                                                                                                          | 802.11a RF Waveform                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.14                                                                                                                                          | I2C-BUS Controller Code Coverage                                                                                                                                                                                                                                                                                                                                                                                                               |

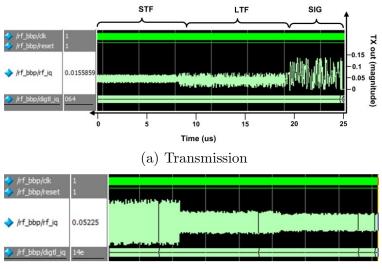

| 4.15                                                                                                                                          | Bus Performance Evaluation Reports                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.16                                                                                                                                          | Performance Comparison                                                                                                                                                                                                                                                                                                                                                                                                                         |

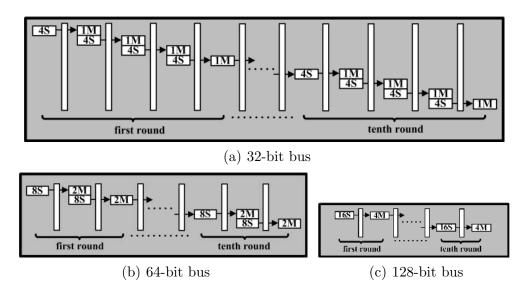

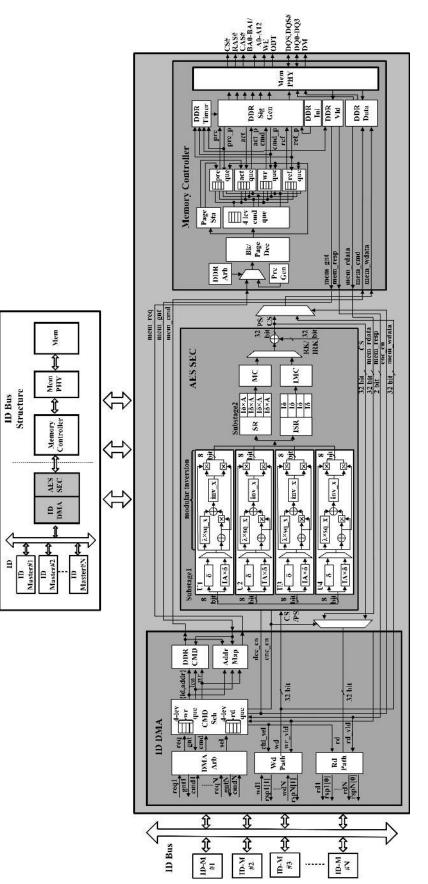

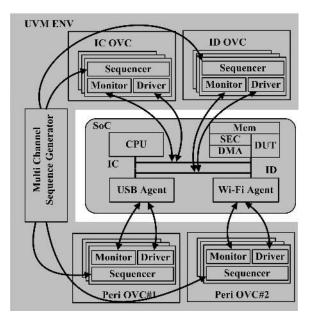

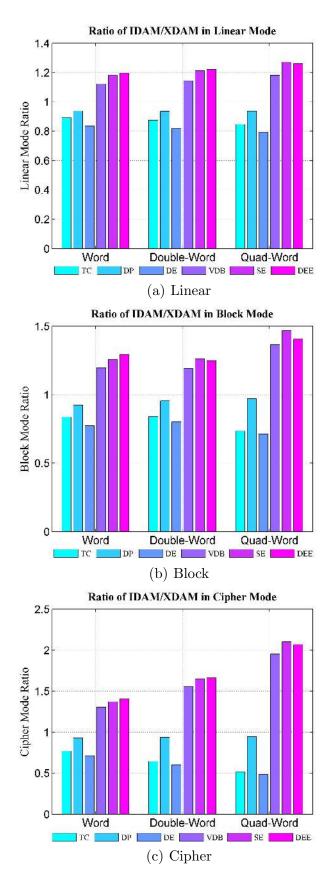

|                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                |