Received March 11, 2020, accepted March 20, 2020, date of publication April 1, 2020, date of current version April 15, 2020. *Digital Object Identifier 10.1109/ACCESS.2020.2984800*

# A High-Precision Bandgap Reference With a V-Curve Correction Circuit

CHANG-CHI LEE<sup>®</sup>, HOU-MING CHEN, CHI-CHANG LU<sup>®</sup>, BO-YI LEE, HSIEN-CHI HUANG, HE-SHENG FU, AND YONG-XIN LIN

Department of Electrical Engineering, National Formosa University, Huwei 632, Taiwan Corresponding author: Hou-Ming Chen (jchen99@nfu.edu.tw)

This work was supported by the Ministry of Science and Technology under Grant MOST 108-2221-E-150-039.

**ABSTRACT** In this study, a precision bandgap reference with a v-curve correction (VCC) circuit is presented. The proposed VCC circuit generates a correction voltage to reduce the temperature drift of the reference voltage and achieves a low temperature coefficient (TC) in a wide temperature range. The proposed bandgap reference was designed and fabricated using a standard TSMC 0.18- $\mu$ m 1P6M CMOS technology with an active area of 0.0139 mm<sup>2</sup>. The measured results show that the proposed bandgap reference achieves a TC of 1.9–5.28 ppm/°C over a temperature range of -40 °C to 140 °C at a supply voltage of 1.8 V. In addition, the circuit demonstrated a line regulation of 0.033 %/V for supply voltages of 1.2 – 1.8 V at room temperature.

**INDEX TERMS** Bandgap reference, line regulation, temperature coefficient (TC), temperature drift, v-curve correction (VCC) circuit.

#### I. INTRODUCTION

Bandgap references are essential building blocks in analog and mixed-signal circuits, such as linear regulators, A/D converters, D/A converters, and power converters for their high precision and temperature independence [1]–[17]. An accurate reference voltage must be stabilized over supply voltage and temperature variations. To achieve a low temperature coefficient (TC) over a wide temperature range, several curvature-correction techniques have been developed. Zhou et al. [7] realized exponential curvature compensation and logarithmic curvature compensation to reduce the temperature drift of a reference voltage. Andreou et al. [8] proposed a complementary-to-absolute-temperature (CTAT) current to fine-tune a curvature correction and thus achieve a new level of performance. Ma and Yu [10] proposed an opposite high-order curvature compensation by using MOS transistors operating in a weak inversion region for cancelling nonlinear temperature dependence. These cited bandgap references had an improvement in TC over wide temperature ranges.

In this study, a bandgap reference with an innovative v-curve correction (VCC) circuit is proposed and demonstrated; it effectively reduces the variation in the reference

The associate editor coordinating the review of this manuscript and approving it for publication was Artur Antonyan<sup>(1)</sup>.

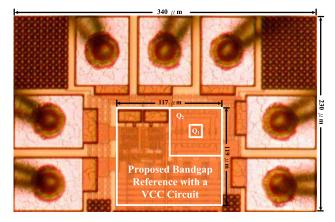

voltage and obtains a low TC in a wide temperature range. The proposed VCC circuit generates an opposite curvature correction to compensate the curvature of the reference voltage. The proposed bandgap reference occupies an area of 117 × 119  $\mu$ m<sup>2</sup> in a standard TSMC 0.18- $\mu$ m 1P6M CMOS process. The experimental results indicate that an average TC of 3.66 ppm/°C is realized over a temperature range of 180 °C and a line regulation of 0.033 %/V is achieved from a supply of 1.2 to 1.8 V.

# II. PROPOSED BANDGAP REFERENCE WITH A V-CURVE CORRECTION CIRCUIT

A temperature-independent voltage is often designed by combining a positive-TC voltage, a negative-TC voltage, and appropriate weight. Two opposite-TC voltages ( $V_{PT}$  and  $V_{NT}$ ) can be achieved by using temperature characteristics of bipolar junction transistors, as discussed in related studies [2]–[14]. However, the curvature of a temperature-independent voltage is often presented in concave and convex. In this study, a VCC circuit is proposed to improve the curvature of a reference voltage in a wide temperature range.

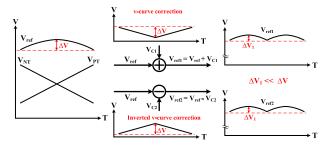

Fig. 1 shows two design compensations of the proposed VCC circuit for convex curvature voltage; addition of a v-curve correction voltage or subtraction of an inverted v-curve correction voltage. The same compensation methods

**FIGURE 1.** Compensation design of the proposed v-curve correction technique.

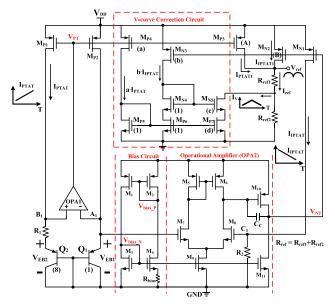

**FIGURE 2.** Complete circuit of the proposed bandgap reference with a v-curve correction circuit.

can also be implemented on the concave curvature voltage. The complete circuit of the proposed bandgap reference comprises a low-voltage bandgap reference and a VCC circuit as shown in Fig. 2. The low-voltage bandgap reference [4], [6], [8] provides a reference voltage below 1V. The proposed VCC circuit generates a correction voltage having opposite-curvature curves to effectively reduce the temperature drift of a reference voltage. The detailed fundamentals and analysis of the proposed bandgap reference are described as follows.

# A. LOW-VOLTAGE BANDGAP REFERENCE CIRCUIT

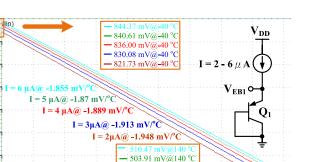

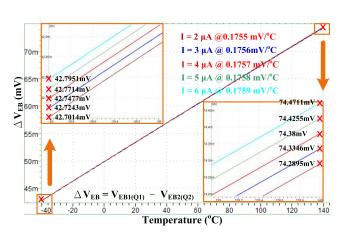

The low-voltage bandgap reference [4], [6], [8] comprises two bipolar transistors (Q<sub>1</sub> and Q<sub>2</sub>), two operational amplifiers (OPA1 and OPA2), three resistors (R<sub>1</sub>, R<sub>2</sub> and R<sub>ref</sub>), and a current mirror circuit (M<sub>N1</sub>, M<sub>N2</sub>, and M<sub>P1</sub> – M<sub>P3</sub>). The area ratio of Q<sub>1</sub> and Q<sub>2</sub> is 1:8 to obtain the best possible layout matching. The emitter-base junction voltage V<sub>EB1</sub> of Q<sub>1</sub> was simulated at different operating currents (2–6  $\mu$ A) over a temperature range of 180 °C (-40 ° C to 140 °C). The simulation result indicated a negative TC of –1.855 to –1.948 mV/°C as shown in Fig. 3. The difference ( $\Delta V_{EB}$ ) in the

495.90 mV@140 °C 485.58 mV@140 °C

471.06 mV@140 °C

**IEEE**Access

<u>0 20 40 60 80</u> Temperature (°C)

FIGURE 3. Temperature dependence of the emitter-base junction

voltage V<sub>EB1</sub> at different operating currents.

**FIGURE 4.** Temperature dependence of  $\Delta V_{EB}$ .

750r 700r

650

600r

550

500r

V<sub>EB1</sub>

two junction voltages (V<sub>EB1</sub> and V<sub>EB2</sub>) has a TC of approximately 0.175 mV/°C, as shown in Fig. 4. Thus, the negative TC of  $V_{EB1}$  can be canceled by the positive TC of  $\Delta V_{EB}$ amplified about ten times. The amplifier OPA1 maintains an equal voltage at nodes A<sub>1</sub> and B<sub>1</sub>, and a proportionalto-absolute-temperature (PTAT) current I<sub>PTAT</sub> is realized through R<sub>1</sub> and Q<sub>2</sub>. The amplifier OPA2 gives an equal negative-TC voltage at nodes A<sub>1</sub> and C<sub>1</sub>, and a negative-TC current I<sub>IPTAT</sub> is generated from M<sub>N1</sub> to R<sub>2</sub>. Thus, a temperature-independent current I<sub>ref</sub> can be achieved by combining two opposite-TC currents, I<sub>PTAT1</sub> and I<sub>IPTAT1</sub>, which are designed by adjusting the size ratios of the current mirror circuit. Thus, a reference voltage of less than 1 V is provided by multiplying I<sub>ref</sub> and R<sub>ref</sub>, as described in (1).

$$V_{ref} = \left(\frac{A \cdot \Delta V_{EB}}{R_1} + \frac{B \cdot V_{EB1}}{R_2}\right) \cdot \left(R_{ref1} + R_{ref2}\right)$$

$$= (A \cdot I_{PTAT} + B \cdot I_{IPTAT}) \cdot \left(R_{ref1} + R_{ref2}\right)$$

$$= (I_{PTAT1} + I_{IPTAT1}) \cdot R_{ref} = I_{ref} \cdot R_{ref}$$

(1)

Both OPA1 and OPA2 are implemented using a two-stage amplifier with an n-channel input pair in the proposed bandgap reference. The gate voltage of  $M_7$  is carefully considered because the emitter-base junction voltage  $V_{EB1}$  falls

**FIGURE 5.** Post-layout simulation results of (a) two opposite-TC currents (*I*<sub>*PTAT*1</sub> and *I*<sub>*IPTAT*1</sub>), (b) temperature slopes of two opposite-TC voltages and (c) reference voltage.

to 503.91 mV at  $5\mu A$  at the highest temperature (140 °C) as shown in Fig. 3. The gate voltage of M<sub>7</sub> is given by

**FIGURE 6.** (a) Design concept, (b) temperature boundary and (c) magnitude of the compensation current.

$V_{GS7} + V_{DS9} \approx 0.5$  V. Furthermore, if the amplifier with an n-channel input pair is replaced with an amplifier with a p-channel input pair, the supply voltage is limited by  $V_{EB1}$  at a low temperature. The minimum supply voltage of the amplifier with a p-channel input pair is evaluated by  $V_{EB1} + V_{SG} + V_{SD} \approx 1.35$  V.

#### **B. PROPOSED V-CURVE CORRECTION CIRCUIT**

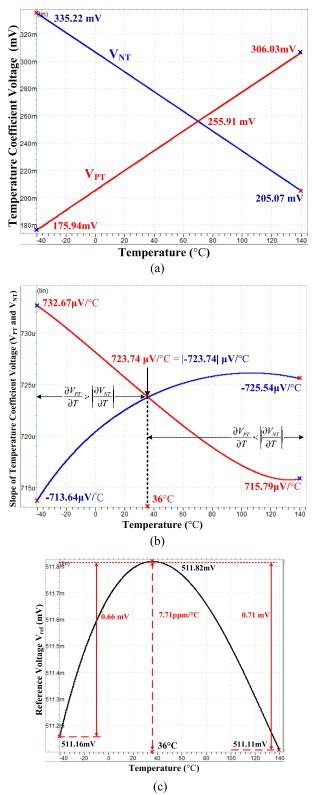

The simulation results show two opposite-TC voltages (VPT and  $V_{NT}$ ), temperature slopes of two opposite-TC voltages and the reference voltage of the low-voltage bandgap reference over a temperature range of 180 °C (-40 °C to 140 °C), as shown in Fig. 5. In a temperature range of -40 °C to 140 °C, the positive-TC voltage VPT is from 175.94 mV to 306.03 mV and the negative-TC voltage  $V_{NT}$ is from 335.22 mV to 205.07 mV. To analyze the variations of temperature slopes, we take the derivative of two opposite-TC voltages with respect to T as shown in Fig. 5(b). Because the temperature slope  $(732.67 - 723.74 \ \mu V/^{\circ}C)$  of the positive-TC voltage  $V_{PT}$  is larger than the temperature slope ( $-713.64 - 723.74 \,\mu \text{V}/^{\circ}\text{C}$ ) of the negative-TC voltage V<sub>NT</sub> between -40 °C to 36 °C, a positive-TC voltage is achieved from 511.16 to 511.82 mV. Furthermore, because the temperature slope (723.74 – 715.79  $\mu$ V/°C) of V<sub>PT</sub> is lower than the temperature slope  $(-723.74 - 725.54 \,\mu\text{V/}^{\circ}\text{C})$ of V<sub>NT</sub> between 36 °C to 140 °C, a negative-TC voltage is achieved from 511.82 to 511.11 mV. The TC of the reference voltage with a convex curvature is 7.71 ppm/°C, which is formed by combining the opposite-TC voltages as shown in Fig. 5(c). In this study, an inverted VCC circuit is proposed to effectively reduce the variation in reference voltage with a convex curvature under a wide temperature range. The proposed VCC circuit only uses seven transistors  $(M_{N3}-M_{N5})$ and  $M_{P4}$ – $M_{P7}$ ) and its operation is discussed as follows.

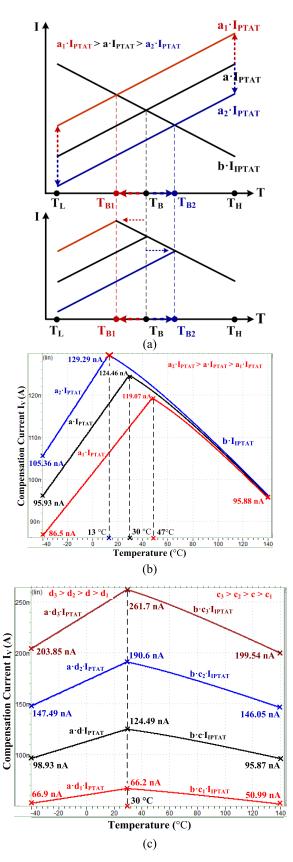

First, two compensation ranges are determined by adjusting the mirrored currents  $a \cdot I_{PTAT}$  and  $b \cdot I_{IPTAT}$ . When the negative-TC current  $b \cdot I_{IPTAT}$  is larger than the positive-TC current  $a \cdot I_{PTAT}$  between T<sub>L</sub> and T<sub>B</sub>, the transistor  $M_{N3}$  operates in the triode region and  $a \cdot I_{PTAT}$  is a dominant current through  $M_{N3}$ ,  $M_{N4}$ , and  $M_{P6}$ . However, when  $b \cdot I_{IPTAT}$  is smaller than  $a \cdot I_{PTAT}$  between T<sub>B</sub> and T<sub>H</sub>, the operation of the transistor  $M_{P6}$  is changed from the saturation region to the triode region and  $b \cdot I_{IPTAT}$  grows into a dominative current, as shown in Fig. 6. Furthermore, the temperature boundary of the two compensation ranges can be shifted for different temperature drifts of reference voltage. If the positive-TC current  $a \cdot I_{PTAT}$  is raised to  $a_1 \cdot I_{PTAT}$  in the fixed current  $b \cdot I_{IPTAT}$ , the temperature boundary shifts from T<sub>B</sub> to  $T_{B1}$ , as shown in Fig. 6(a). However, if  $a \cdot I_{PTAT}$  is reduced to  $a_2 \cdot I_{PTAT}$ , the temperature boundary shifts to T<sub>B2</sub>. In a similar design, the temperature boundary can be moved by adjusting the negative-TC current  $b \cdot I_{IPTAT}$  at a fixed current  $a \cdot I_{PTAT}$ . Fig. 6(b) shows simulation results for three different compensation boundaries (13 °C, 30 °C and 47 °C) that are designed by adjusting the mirrored current  $a \cdot I_{PTAT}$ . Moreover, the magnitude of a compensation current is determined

by adjusting the size ratios of the transistors  $M_{N4}$ ,  $M_{N5}$ ,  $M_{P6}$ , and  $M_{P7}$  for different reference voltage variations, as shown in Fig. 6(c). The proposed reference voltage with a v-curve correction voltage is given as follows:

$$V_{ref} = \left(\frac{A \cdot \Delta V_{EB}}{R_1} + \frac{B \cdot V_{EB1}}{R_2}\right) \cdot R_{ref}$$

$$- \left(\frac{a \cdot d \cdot \Delta V_{EB}}{R_1} + \frac{b \cdot c \cdot V_{EB1}}{R_2}\right) \cdot R_{ref2}$$

$$= (A \cdot I_{PTAT} + B \cdot I_{IPTAT}) \cdot R_{ref}$$

$$- (a \cdot d \cdot I_{PTAT} + b \cdot c \cdot I_{IPTAT}) \cdot R_{ref2}$$

$$= (I_{PTAT1} + I_{IPTAT1}) \cdot R_{ref}$$

$$- (a \cdot d \cdot I_{PTAT} + b \cdot c \cdot I_{IPTAT}) \cdot R_{ref2}$$

$$= I_{ref} \cdot R_{ref} - (a \cdot d \cdot I_{PTAT} + b \cdot c \cdot I_{IPTAT}) \cdot R_{ref2}$$

(2)

The resistor  $R_{ref2}$  is only part of the output resistor  $R_{ref}$ , as shown in Fig. 2. The transistors  $M_{N5}$  and  $M_{P7}$  drain an inverted v-curve current  $I_V$  from the resistor  $R_{ref2}$ . This operation is similar to the addition of v-curve current to the

FIGURE 7. Post-layout simulation results of (a) an inverted v-curve correction current and (b) the corrected reference voltage.

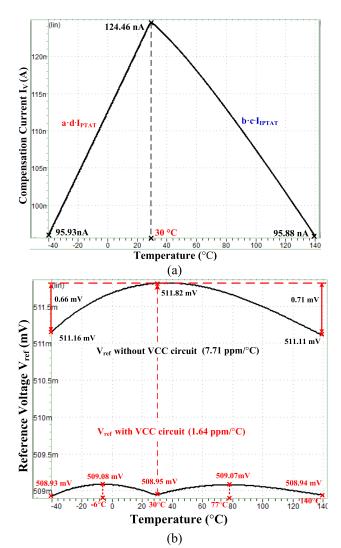

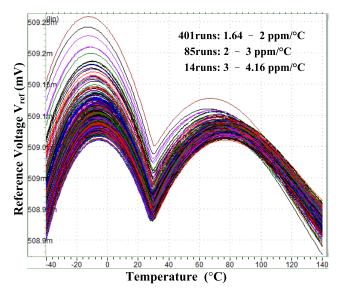

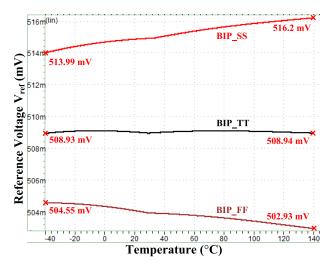

reference voltage for convex-curvature correction. Fig. 7 shows the simulation results of an inverted v-curve compensation current, the uncorrected reference voltage and the corrected reference voltage over a temperature range of 180 °C (-40 °C to 140 °C). An inverted v-curve compensation current (95.88 – 124.46 nA) multiplied by resistor  $R_{ref2}$  to correct the voltage variation (0.71 mV) of the reference voltage. Compared with the simulation results of the low-voltage bandgap reference, the TC of the proposed reference voltage exhibits a 78.8 % reduction, from 7.71 to 1.64 ppm/°C, as shown in Fig. 7(b). The variation of the reference voltage is decreased from 0.66 to 0.15 mV in the temperature range -40 °C to 30 °C. A voltage variation of 0.71 mV is reduced to 0.13 mV in the range 30 °C to 140 °C. The reference voltage is less than 1.74 to 2.89 mV after compensation, which is caused by the inverted v-curve compensation current drawn from the output. To analyze process variations and mismatches, 500 runs of post-layout Monte Carlo simulations were performed and the results are shown in Fig. 8. Of the total runs, 401 runs achieved a TC of less 2 ppm/°C, with a minimum of 1.64 ppm/°C. Fig. 9 presents the simulation results of the proposed reference voltage in the BJT corners.

FIGURE 8. TC for 500 runs of the Monte Carlo simulations.

### **III. EXPERIMENTAL AND COMPARISON RESULTS**

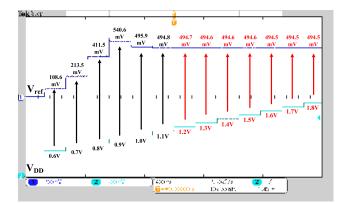

The proposed bandgap reference with a VCC circuit was fabricated using a standard TSMC 0.18- $\mu$ m 1P6M CMOS technology. Fig. 10 depicts a physical micrograph of the proposed bandgap reference chip. The active chip area was 117 × 119  $\mu$ m<sup>2</sup>.  $V_{ref}$  of the bandgap reference as a function of the supply voltage was measured using a programmable voltage source and an oscilloscope. Fig. 11 shows the  $V_{ref}$ at each step voltage, which was measured by applying a staircase sweep voltage ranging from 0.6 to 1.8 V at room temperature. The experimental result indicates a constant voltage of 494.5 mV with a 0.2 mV variation under a 0.6 V

FIGURE 9. Simulation results of the proposed reference voltage in the BJT corners.

FIGURE 10. Physical micrograph of the proposed bandgap reference chip.

FIGURE 11. Measured output voltage at each step voltage from 0.6 to 1.8 V.

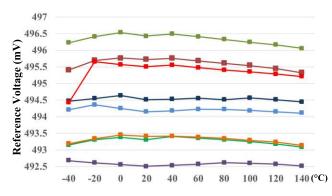

supply voltage variation. Thus, the line regulation of the proposed bandgap reference was 0.033 %/V across a voltage supply of 1.2–1.8 V. The TC of  $V_{ref}$  was measured in a programmable temperature chamber. Fig. 12 shows the  $V_{ref}$  and TC distribution, which were measured from  $-40 \,^{\circ}$ C to  $140 \,^{\circ}$ C

| Specifications                  | 2012 [8]<br>IEEE JSSC | 2014 [10]<br>IEEE TCAS-I | 2015 [11]<br>IEEE TCAS-I | 2017 [16]<br>IEEE TCAS-I | 2019 [17]<br>IEEE TCAS-I | This work   |

|---------------------------------|-----------------------|--------------------------|--------------------------|--------------------------|--------------------------|-------------|

| Supply Voltage(V)               | 2.5                   | 1.2                      | 1.2                      | 1.8                      | 3.3                      | 1.8         |

| Current Consumption(µA)         | 38                    | 36                       | 120                      | 28                       | 94                       | 26.3        |

| Reference Voltage(mV)           | 617.7                 | 767                      | 735                      | 547                      | 2470                     | 494.5       |

| Best TC(ppm/°C)                 | 3.9                   | 3.4                      | 4.2                      | 3.05                     | 0.9                      | 1.9         |

| Average TC(ppm/°C)              | 4.9                   | 4.91                     | 9.3                      | 6.11                     | 3                        | 3.66        |

| Standard Deviation ( $\sigma$ ) | N/A                   | N/A                      | N/A                      | N/A                      | 1.87 mV                  | 0.018mV     |

| Temp Range(°C)                  | -15 to 150            | -40 to 120               | -40 to 120               | -40 to 140               | -45 to 125               | -40 to 140  |

| Line Regulation(%/V)            | 0.039                 | 0.054                    | N/A                      | 0.08                     | N/A                      | 0.033       |

| PSRR (dB)                       | N/A                   | -84@400 Hz               | -30@100 kHz              | N/A                      | -83@dc                   | -68@566 Hz  |

| Active Area(mm <sup>2</sup> )   | 0.102                 | 0.036                    | 0.063                    | 0.0094                   | 0.0616                   | 0.0139      |

| Trimming                        | YES                   | YES                      | NO                       | NO                       | YES                      | NO          |

| Technology                      | CMOS 0.35µm           | CMOS 0.18µm              | CMOS 0.13µm              | CMOS 0.18µm              | CMOS 0.35µm              | CMOS 0.18µm |

TABLE 1. Comparisons of the proposed bandgap reference.

FIGURE 12. Measured temperature dependence of the reference voltage at a supply voltage of 1.8 V.

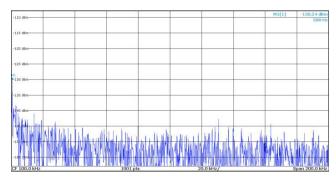

FIGURE 13. Measured noise spectrum of the proposed bandgap reference at room temperature.

at a 1.8 V supply voltage. The experimental results demonstrate that the proposed bandgap reference achieved a TC of 1.9–5.28 ppm/°C over a 180 °C temperature range in eight samples. The average TC was approximately 3.66 ppm/°C. The measurement results of the reference voltage differ from the simulation results by 12.45 – 16.45 mV, and these errors are mainly due to the process variation of the resistance. After measuring the output resistance  $R_{ref}$ , it is found that the output resistance is  $0.9k\Omega$  less than the expected design resistance. Table 1 compares the performance of the bandgap reference described in this study to those of previous bandgap references [8]–[12]. Fig. 13 shows the measured noise spectrum of the reference voltage  $V_{ref}$  without a decoupling capacitor from 1 Hz and 200 kHz. The results of using the signal and spectrum analyzer (R&S FSW8) prove that the highest noise density of -130.24 dBm was at 500 Hz.

## **IV. CONCLUSION**

In this study, a precision bandgap reference was fabricated using a standard CMOS 0.18- $\mu$ m process. The chip area of the bandgap reference with test pads was  $0.078 \text{ mm}^2$ . The experimental results confirmed that the proposed VCC reduces the variation of the reference voltage over a wide temperature range and has a temperature coefficient improvement of 72.5%. The designed v-curve correction voltage can effectively reduce the temperature drift of the reference voltage. The best TC of the proposed bandgap reference was 1.9 ppm/°C in a temperature range of -40 °C to 140 °C with a 1.8 V supply voltage. The measured output voltage achieved a 0.2-mV variation from a supply voltage of 1.2-1.8 V at room temperature. Therefore, the proposed bandgap is suitable for advanced CMOS circuits.

#### ACKNOWLEDGMENT

The authors would like to thank the Taiwan Semiconductor Research Institute for technical support.

#### REFERENCES

- A. Bakker and J. Huijsing, *High-Accuracy CMOS Smart Temperature* Sensors. New York, NY, USA: Springer, 2001.

- [2] K. Nang Leung and P. K. T. Mok, "A sub-1-V 15-ppm/°C CMOS bandgap voltage reference without requiring low threshold voltage device," *IEEE J. Solid-State Circuits*, vol. 37, no. 4, pp. 526–530, Apr. 2002.

- [3] K. Nang Leung, P. K. T. Mok, and C. Yat Leung, "A 2-V 23-μA 5.3-ppm/°C curvature-compensated CMOS bandgap voltage reference," *IEEE J. Solid-State Circuits*, vol. 38, no. 3, pp. 561–564, Mar. 2003.

- [4] S. Jinggang, C. Zhiliang, and S. Bingxue, "A 1 V supply area effective CMOS bandgap reference," in *Proc. 5th Int. Conf. ASIC (ICASIC)*, Oct. 2003, pp. 619–622.

- [5] X. Ming, Y.-Q. Ma, Z.-K. Zhou, and B. Zhang, "A high-precision compensated CMOS bandgap voltage reference without resistors," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 57, no. 10, pp. 767–771, Oct. 2010.

- [6] J. H. Li, X. B. Zhang, and M. Y. Yu, "A 1.2-v piecewise curvature-corrected bandgap reference in 0.5μm CMOS process," *IEEE Trans. Very Large Scale Integr*(VLSI) Syst., vol. 19, no. 6, pp. 1118–1122, Jun. 2011.

- [7] Z. K. Zhou, Y. Shi, Z. Huang, P. S. Zhu, Y. Q. Ma, Y. C. Wang, Z. Chen, X. Ming, and B. Zhang, "A 1.6-v 25-μA 5-ppm/°C curvature-compensated bandgap reference," *IEEE Trans. Circuits Syst. I, Reg. Papers, Reg. Papers*, vol. 59, no. 4, pp. 677–684, Apr. 2012.

- [8] C. M. Andreou, S. Koudounas, and J. Georgiou, "A novel Wide-Temperature-range, 3.9 ppm/°C CMOS bandgap reference circuit," *IEEE J. Solid-State Circuits*, vol. 47, no. 2, pp. 574–581, Feb. 2012.

- [9] Y. Osaki, T. Hirose, N. Kuroki, and M. Numa, "1.2-V supply, 100-nW, 1.09-V bandgap and 0.7-V supply, 52.5-nW, 0.55-V subbandgap reference circuits for nanowatt CMOS LSIs," *IEEE J. Solid-State Circuits*, vol. 48, no. 6, pp. 1530–1538, Jun. 2013.

- [10] B. Ma and F. Yu, "A novel 1.2–V 4.5-ppm/°C curvature-compensated CMOS bandgap reference," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 61, no. 4, pp. 1026–1035, Apr. 2014.

- [11] Q. Duan and J. Roh, "A 1.2-v 4.2-ppm/°C high-order curvaturecompensated CMOS bandgap reference," *IEEE Trans. Circuits Syst. I, Reg. Papers, Reg. Papers*, vol. 62, no. 3, pp. 662–670, Mar. 2015.

- [12] J. Jiang, W. Shu, and J. S. Chang, "A 5.6 ppm/°C temperature coefficient, 87-dB PSRR, Sub-1-V voltage reference in 65-nm CMOS exploiting the zero-temperature-coefficient point," *IEEE J. Solid-State Circuits*, vol. 52, no. 3, pp. 623–633, Mar. 2017.

- [13] P. Malcovati, F. Maloberti, C. Fiocchi, and M. Pruzzi, "Curvaturecompensated BiCMOS bandgap with 1-V supply voltage," *IEEE J. Solid-State Circuits*, vol. 36, no. 7, pp. 1076–1081, Jul. 2001.

- [14] A. Becker-Gomez, T. L. Viswanathan, and T. R. Viswanathan, "A Low-Supply-Voltage CMOS sub-bandgap reference," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 55, no. 7, pp. 609–613, Jul. 2008.

- [15] J.-M. Redoute and M. Steyaert, "Kuijk bandgap voltage reference with high immunity to EMI," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 57, no. 2, pp. 75–79, Feb. 2010.

- [16] H.-M. Chen, C.-C. Lee, S.-H. Jheng, W.-C. Chen, and B.-Y. Lee, "A Sub-1 ppm/°C precision bandgap reference with adjusted-temperature-curvature compensation," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 6, pp. 1308–1317, Jun. 2017.

- [17] L. Liu, X. Liao, and J. Mu, "A 3.6 μV<sub>rms</sub> noise, 3 ppm/°C TC bandgap reference with Offset/noise suppression and five-piece linear compensation," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 10, pp. 3786–3796, Oct. 2019.

**HOU-MING CHEN** received the B.S. degree in electronics engineering from Feng Chia University, in 2001, the M.S. degree in electrical engineering from Dayeh University, in 2003, and the Ph.D. degree in electrical engineering from National Chung Hsing University, Taiwan, in 2009. He is currently an Associate Professor with the Department of Electrical Engineering, National Formosa University, Huwei, Taiwan. He has published more than 30 technical journals

and conference papers. His current research interests include low power circuits design, analog circuits design, and power management IC design.

**CHI-CHANG LU** received the B.S. and M.S. degrees in electrical engineering from National Tsing Hua University, Hsinchu, Taiwan, in 1990 and 1992, respectively, and the Ph.D. degree from the National Yunlin University of Science and Technology, Yunlin, Taiwan, in 2005. He is currently an Associate Professor with the Department of Electrical Engineering, National Formosa University, Huwei, Taiwan. His main research interest is in the design of mixed-signal integrated circuits.

**BO-YI LEE** was born in Taoyuan, Taiwan, in 1993. He received the B.S. and M.S. degrees in electrical engineering from National Formosa University, Huwei, Taiwan, in 2016 and 2018, respectively. His research interests include voltage references, power management IC design, and power electronic converters.

**HSIEN-CHI HUANG** was born in Taoyuan, Taiwan, in 1992. He received the B.S. and M.S. degrees in electrical engineering from National Formosa University, Huwei, Taiwan, in 2015 and 2017, respectively. His research interests include voltage references, power management IC design, and power electronic converters.

**HE-SHENG FU** was born in Yunlin, Taiwan, in 1996. He received the B.S. degree in electrical engineering from National Formosa University, Huwei, Taiwan, in 2018, where he is currently pursuing the M.S. degree with the Department of Electrical Engineering. His research interests include voltage references and linear regulators.

**CHANG-CHI LEE** was born in Yunlin, Taiwan, in 1959. He received the M.S. degree in electrical engineering from National Formosa University, Huwei, Taiwan, in 2015, where he is currently pursuing the Ph.D. degree in power electronics and IC designs with the Department of Electro-Optical Engineering. His research interests include power electronics and power management IC design.

**YONG-XIN LIN** was born in Yilan, Taiwan, in 1995. He received the B.S. degree in electrical engineering from National Formosa University, Huwei, Taiwan, in 2018, where he is currently pursuing the M.S. degree with the Department of Electrical Engineering. His research interests include voltage references and power electronic converters.